# Intelligent Architectures for Intelligent Machines

Onur Mutlu <u>omutlu@gmail.com</u> <u>https://people.inf.ethz.ch/omutlu</u>

20 November 2019

Khalifa System on Chip Center Open House Keynote

SAFARI

ETH zürich

# Computing is Bottlenecked by Data

## Data is Key for AI, ML, Genomics, ...

Important workloads are all data intensive

They require rapid and efficient processing of large amounts of data

- Data is increasing

- □ We can generate more than we can process

## Data is Key for Future Workloads

### **In-memory Databases**

[Mao+, EuroSys'12; Clapp+ (**Intel**), IISWC'15]

### **In-Memory Data Analytics**

[Clapp+ (**Intel**), IISWC'15; Awan+, BDCloud'15]

**Graph/Tree Processing** [Xu+, IISWC'12; Umuroglu+, FPL'15]

**Datacenter Workloads** [Kanev+ (**Google**), ISCA'15]

## Data Overwhelms Modern Machines

### **In-memory Databases**

### **Graph/Tree Processing**

## Data → performance & energy bottleneck

## In-Memory Data Analytics

[Clapp+ (**Intel**), IISWC'15; Awan+, BDCloud'15]

**Datacenter Workloads** [Kanev+ (**Google**), ISCA'15]

## Data is Key for Future Workloads

Chrome

**Google's web browser**

## **TensorFlow Mobile**

Google's machine learning framework

**Google's video codec**

## Data Overwhelms Modern Machines

## Data → performance & energy bottleneck

**Google's video codec**

## Data is Key for Future Workloads

http://www.economist.com/news/21631808-so-much-genetic-data-so-many-uses-genes-unzipped

## Data → performance & energy bottleneck

| reau4: | COCITCCAT |

|--------|-----------|

| read5: | CCATGACGC |

| read6: | TTCCATGAC |

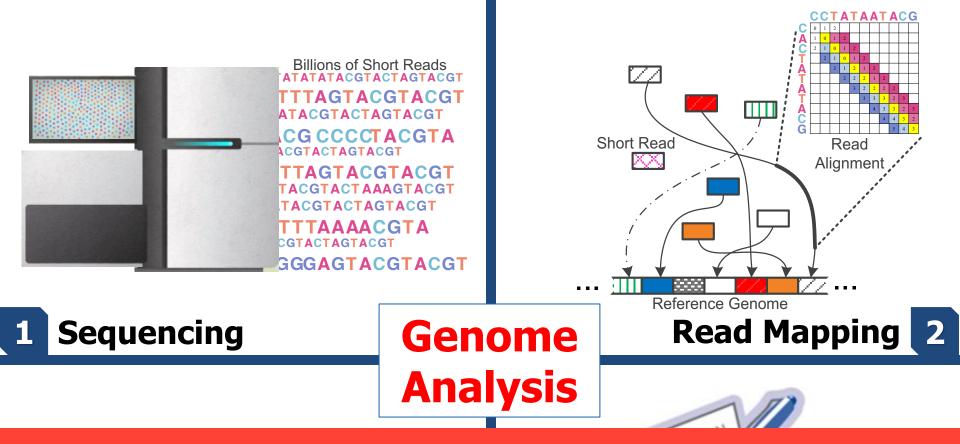

## 3 Variant Calling

## **Scientific Discovery 4**

# New Genome Sequencing Technologies

## Nanopore sequencing technology and tools for genome assembly: computational analysis of the current state, bottlenecks and future directions

Damla Senol Cali 🖾, Jeremie S Kim, Saugata Ghose, Can Alkan, Onur Mutlu

Briefings in Bioinformatics, bby017, https://doi.org/10.1093/bib/bby017Published:02 April 2018Article history ▼

**Oxford Nanopore MinION**

## Data → performance & energy bottleneck

## Data Overwhelms Modern Machines ...

Storage/memory capability

Communication capability

Computation capability

Greatly impacts robustness, energy, performance, cost

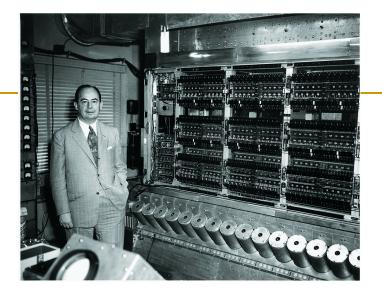

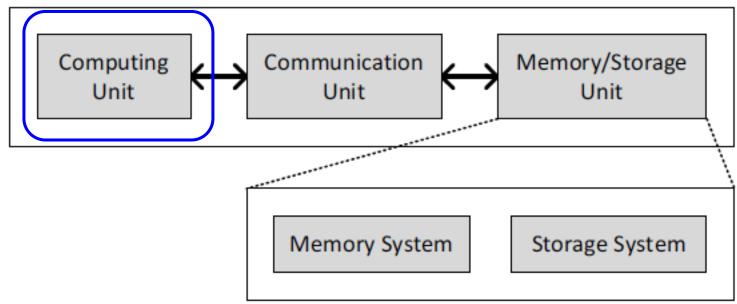

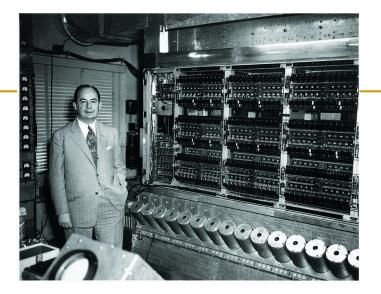

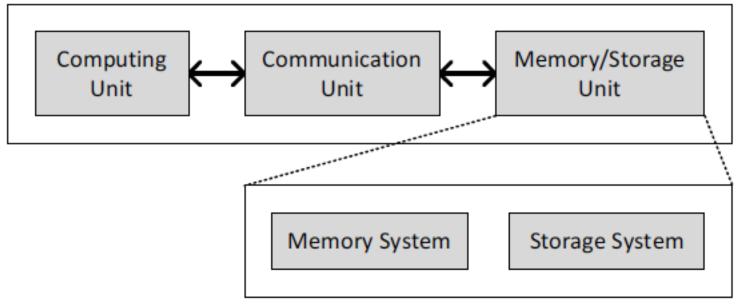

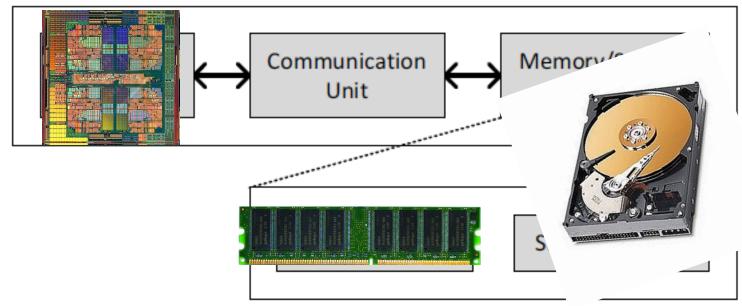

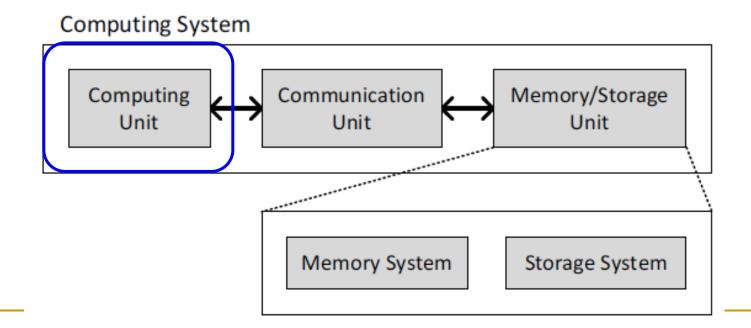

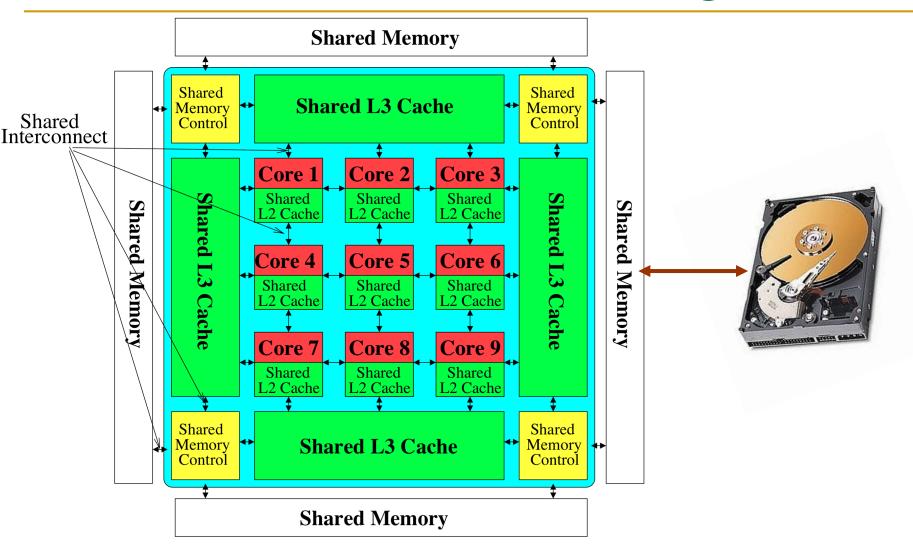

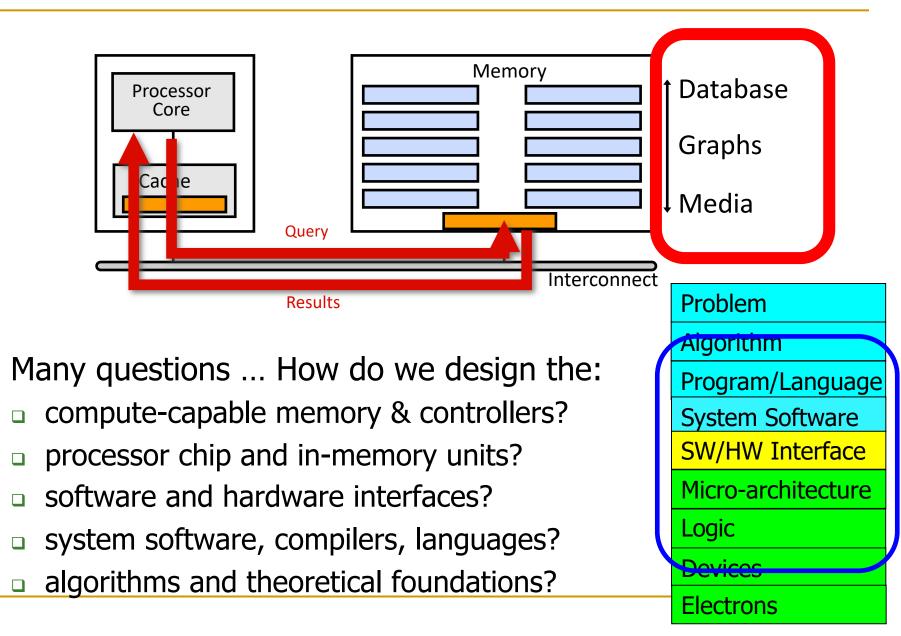

# A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

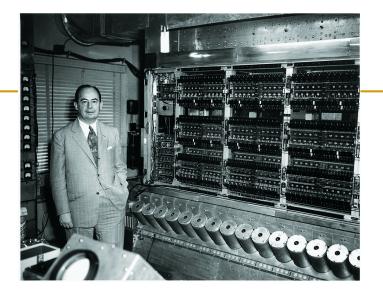

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

### Computing System

Image source: https://lbsitbytes2010.wordpress.com/2013/03/29/john-von-neumann-roll-no-15/

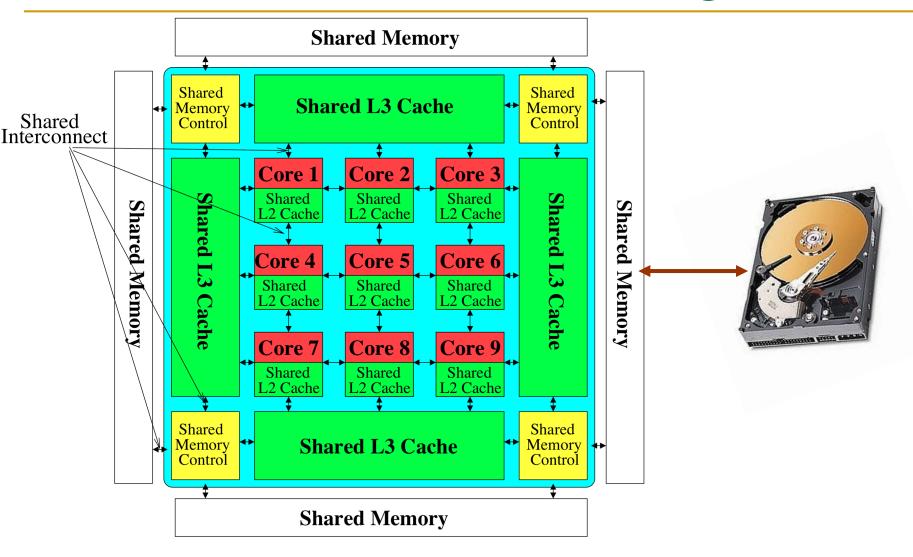

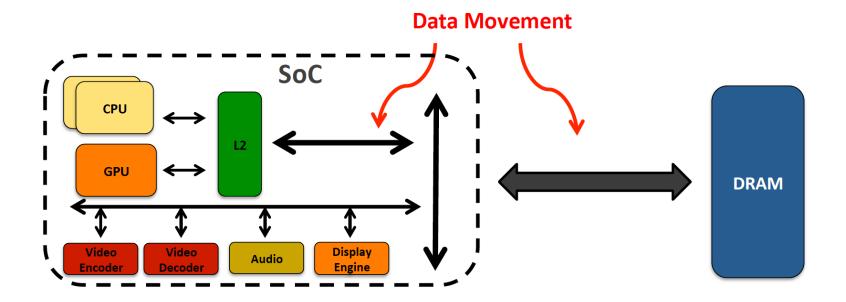

# Perils of Processor-Centric Design

### Most of the system is dedicated to storing and moving data

## Data Overwhelms Modern Machines

## Data → performance & energy bottleneck

**Google's video codec**

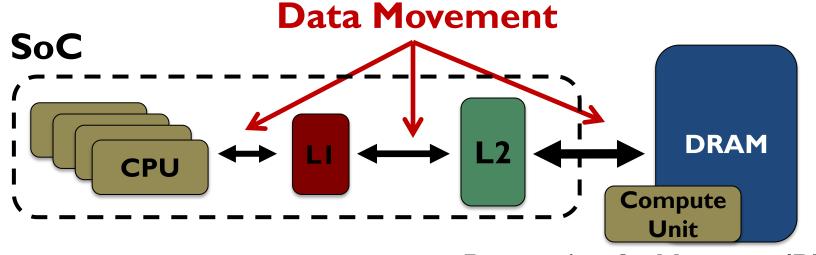

## Data Movement Overwhelms Modern Machines

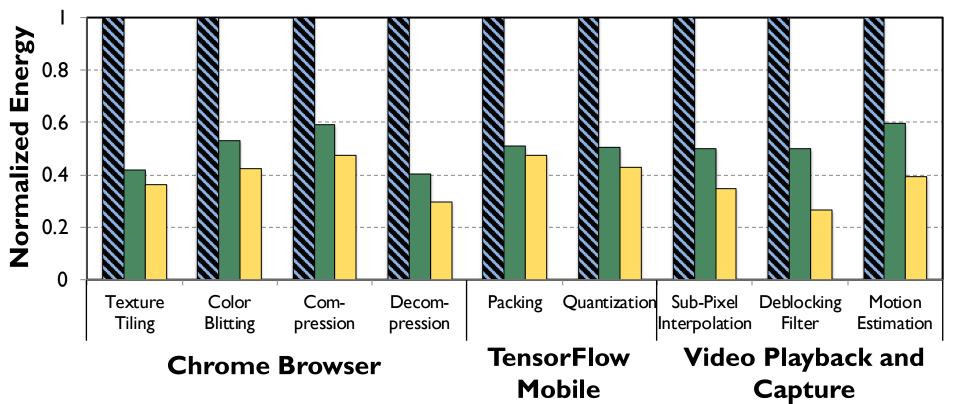

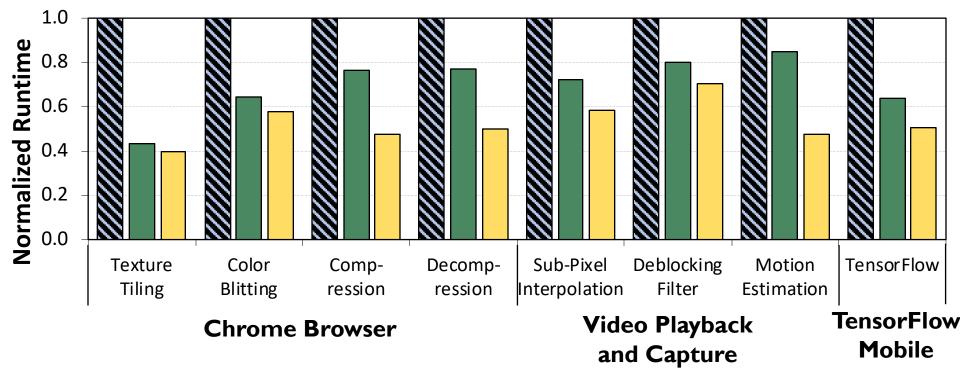

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the <u>23rd International Conference on Architectural Support for Programming</u> <u>Languages and Operating Systems</u> (ASPLOS), Williamsburg, VA, USA, March 2018.

# 62.7% of the total system energy is spent on data movement

## Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup>Saugata Ghose<sup>1</sup>Youngsok Kim<sup>2</sup>Rachata Ausavarungnirun<sup>1</sup>Eric Shiu<sup>3</sup>Rahul Thakur<sup>3</sup>Daehyun Kim<sup>4,3</sup>Aki Kuusela<sup>3</sup>Allan Knies<sup>3</sup>Parthasarathy Ranganathan<sup>3</sup>Onur Mutlu<sup>5,1</sup>15

# An Intelligent Architecture Handles Data Well

## How to Handle Data Well

- Ensure data does not overwhelm the components

- via intelligent algorithms

- via intelligent architectures

- via whole system designs: algorithm-architecture-devices

Take advantage of vast amounts of data and metadata

to improve architectural & system-level decisions

Understand and exploit properties of (different) data

to improve algorithms & architectures in various metrics

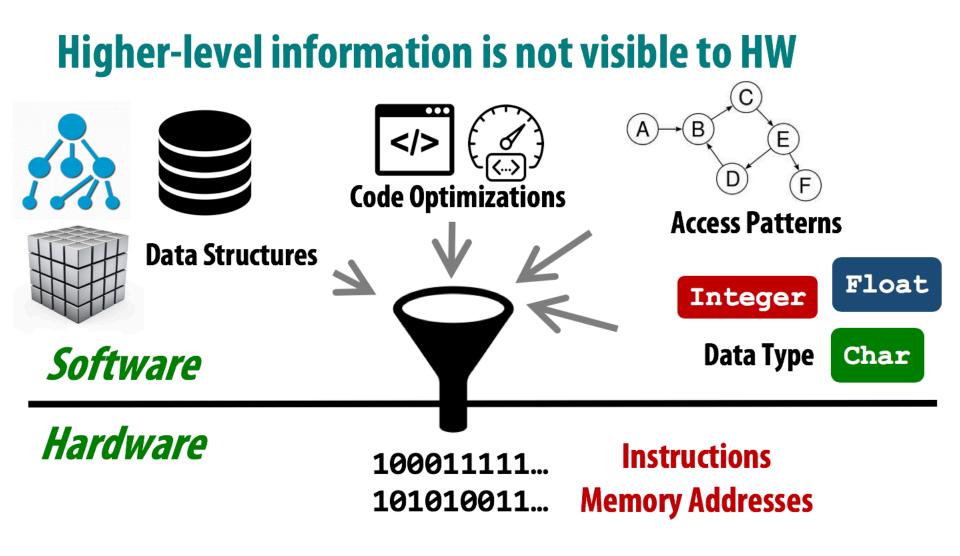

# Corollaries: Architectures Today ...

- Architectures are terrible at dealing with data

- Designed to mainly store and move data vs. to compute

- □ They are processor-centric as opposed to **data-centric**

- Architectures are terrible at taking advantage of vast amounts of data (and metadata) available to them

- Designed to make simple decisions, ignoring lots of data

- □ They make human-driven decisions vs. **data-driven** decisions

- Architectures are terrible at knowing and exploiting different properties of application data

- Designed to treat all data as the same

- They make component-aware decisions vs. data-aware

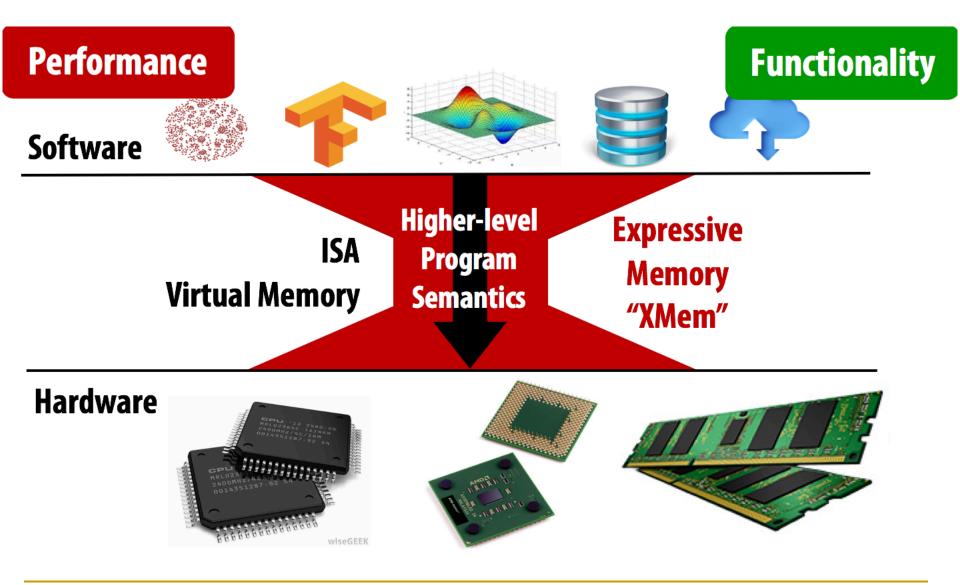

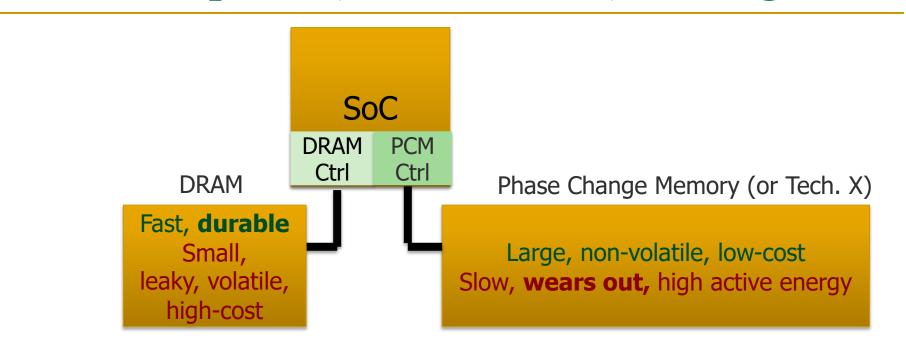

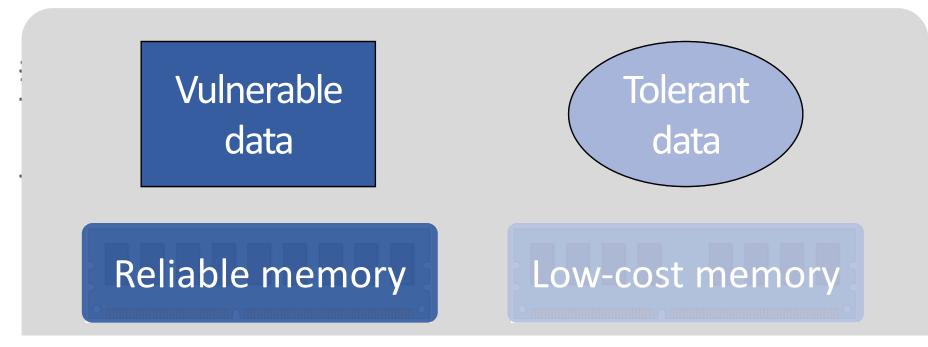

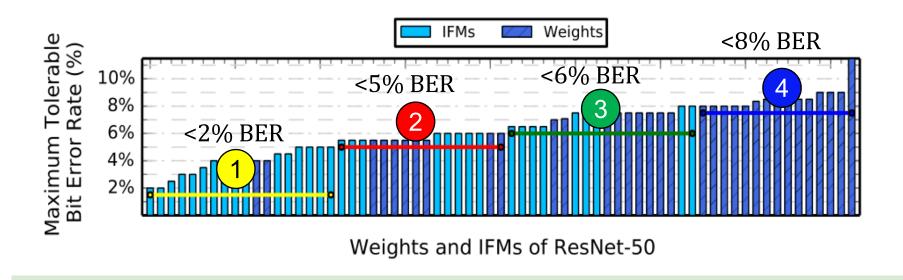

# Data-Centric (Memory-Centric) Architectures

# Low Latency Data Access

## Data-Centric Architectures: Properties

## Process data where it resides (where it makes sense)

Processing in and near memory structures

## Low-latency & low-energy data access

- Low latency memory

- Low energy memory

## Low-cost data storage & processing

High capacity memory at low cost: hybrid memory, compression

## Intelligent data management

Intelligent controllers handling robustness, security, cost, scaling

# Low-Latency & Low-Energy Data Access

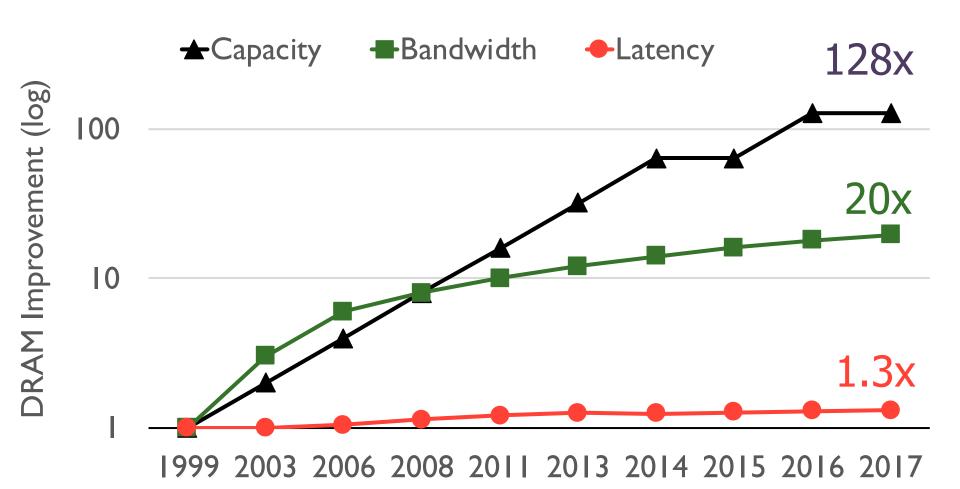

## Main Memory Latency Lags Behind

Memory latency remains almost constant

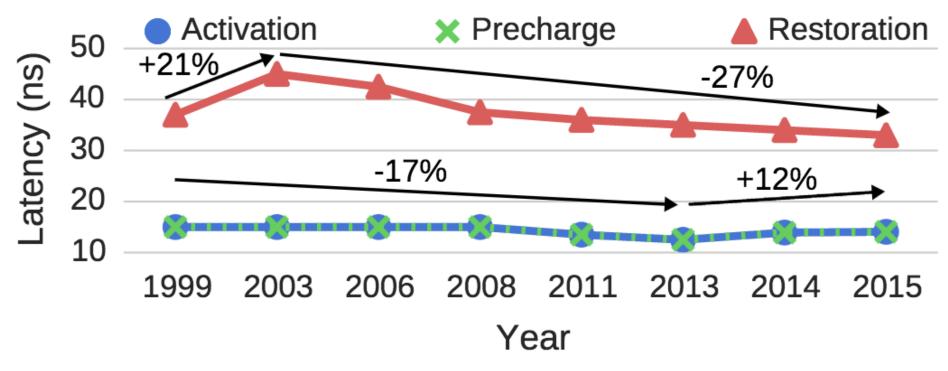

## A Closer Look ...

Figure 1: DRAM latency trends over time [20, 21, 23, 51].

Chang+, "<u>Understanding Latency Variation in Modern DRAM Chips: Experimental</u> Characterization, Analysis, and Optimization"," SIGMETRICS 2016.

### **In-memory Databases**

[Mao+, EuroSys'12; Clapp+ (**Intel**), IISWC'15]

### **In-Memory Data Analytics**

[Clapp+ (**Intel**), IISWC'15; Awan+, BDCloud'15]

**Graph/Tree Processing** [Xu+, IISWC'12; Umuroglu+, FPL'15]

**Datacenter Workloads** [Kanev+ (**Google**), ISCA'15]

**In-memory Databases**

**Graph/Tree Processing**

Long memory latency -> performance bottleneck

### In-Memory Data Analytics

[Clapp+ (**Intel**), IISWC'15; Awan+, BDCloud'15]

SAFARI

**Datacenter Workloads** [Kanev+ (**Google**), ISCA'15]

Chrome

**Google's web browser**

## **TensorFlow Mobile**

Google's machine learning framework

**Google's video codec**

## Long memory latency $\rightarrow$ performance bottleneck

VP9 VouTube Video Playback

**Google's video codec**

# New DRAM Types Increase Latency!

Saugata Ghose, Tianshi Li, Nastaran Hajinazar, Damla Senol Cali, and Onur Mutlu,

### "Demystifying Workload–DRAM Interactions: An Experimental Study"

Proceedings of the ACM International Conference on Measurement and Modeling of Computer Systems (SIGMETRICS), Phoenix, AZ, USA, June 2019. [Preliminary arXiv Version]

[Abstract]

[Slides (pptx) (pdf)]

## **Demystifying Complex Workload–DRAM Interactions: An Experimental Study**

Tianshi Li<sup>†</sup> Saugata Ghose<sup>†</sup> Nastaran Hajinazar<sup>‡†</sup> Damla Senol Cali<sup>†</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>Simon Fraser University

<sup>§</sup>ETH Zürich

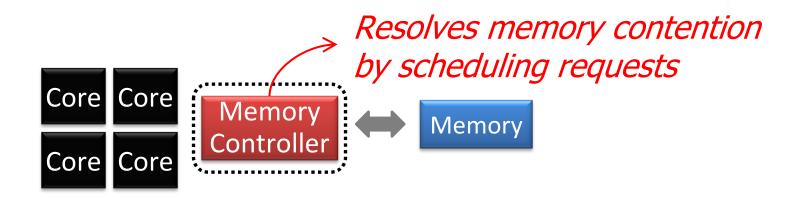

## The Memory Latency Problem

- High memory latency is a significant limiter of system performance and energy-efficiency

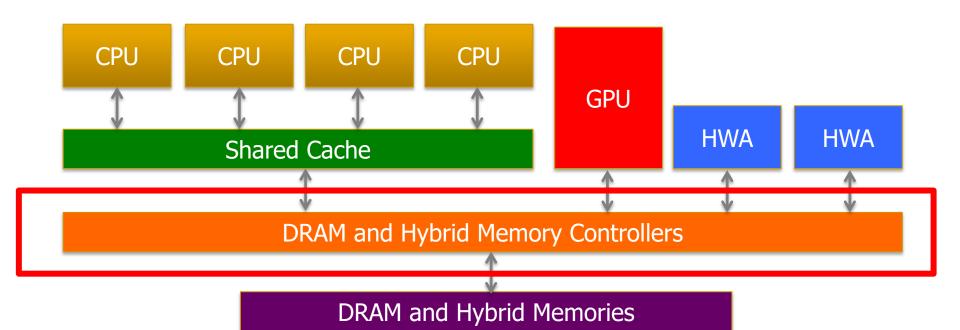

- It is becoming increasingly so with higher memory contention in multi-core and heterogeneous architectures

- Exacerbating the bandwidth need

- Exacerbating the QoS problem

- It increases processor design complexity due to the mechanisms incorporated to tolerate memory latency

Retrospective: Conventional Latency Tolerance Techniques

- Caching [initially by Wilkes, 1965]

- Widely used, simple, effective, but inefficient, passive

- Not all applications/phases exhibit temporal or spatial locality

Prefetching [initially in IBM 360/91 1967]

# None of These Fundamentally Reduce Memory Latency

ongoing research effort

- Out-of-order execution [initially by Tomasulo, 1967]

- Tolerates cache misses that cannot be prefetched

- Requires extensive hardware resources for tolerating long latencies

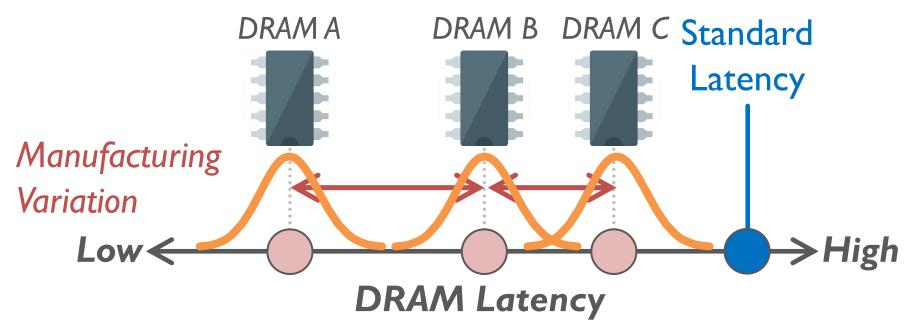

# Two Major Sources of Latency Inefficiency

- Modern DRAM is **not** designed for low latency

Main focus is cost-per-bit (capacity)

- Modern DRAM latency is determined by worst case conditions and worst case devices

- Much of memory latency is unnecessary

# Our Goal: Reduce Memory Latency at the Source of the Problem

# Why is Memory Latency High?

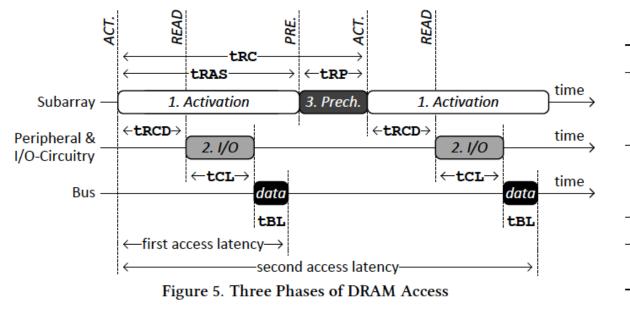

- DRAM latency: Delay as specified in DRAM standards

- Doesn't reflect true DRAM device latency

- Imperfect manufacturing process  $\rightarrow$  latency variation

- High standard latency chosen to increase yield

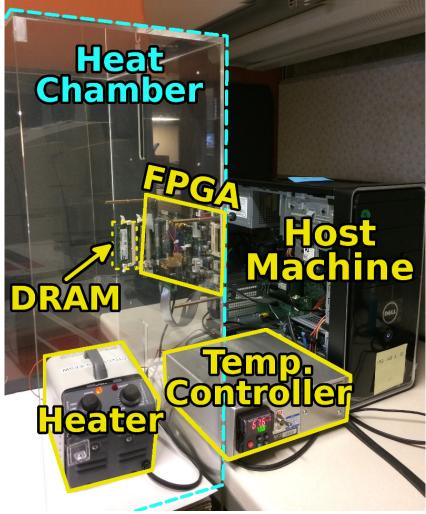

## Adaptive-Latency DRAM

- Key idea

- Optimize DRAM timing parameters online

- Two components

- DRAM manufacturer provides multiple sets of reliable DRAM timing parameters at different temperatures for each DIMM

- System monitors DRAM temperature & uses appropriate DRAM timing parameters

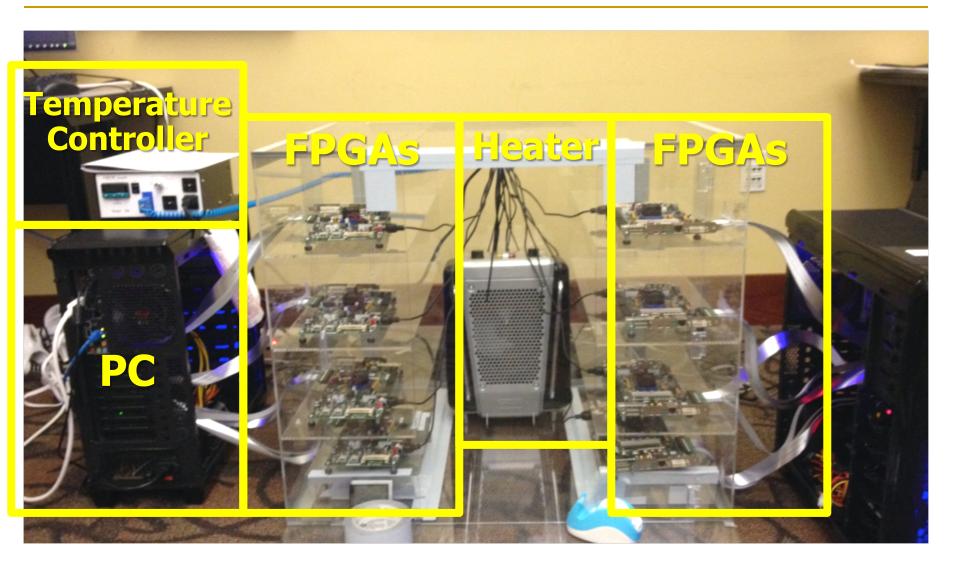

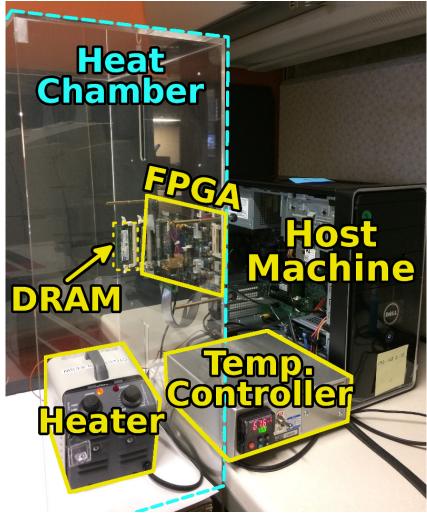

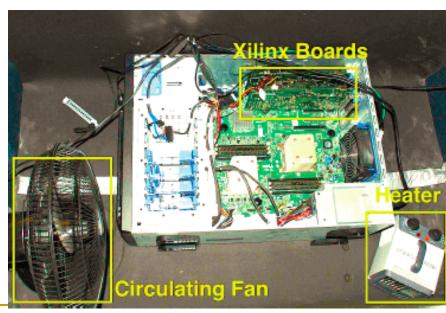

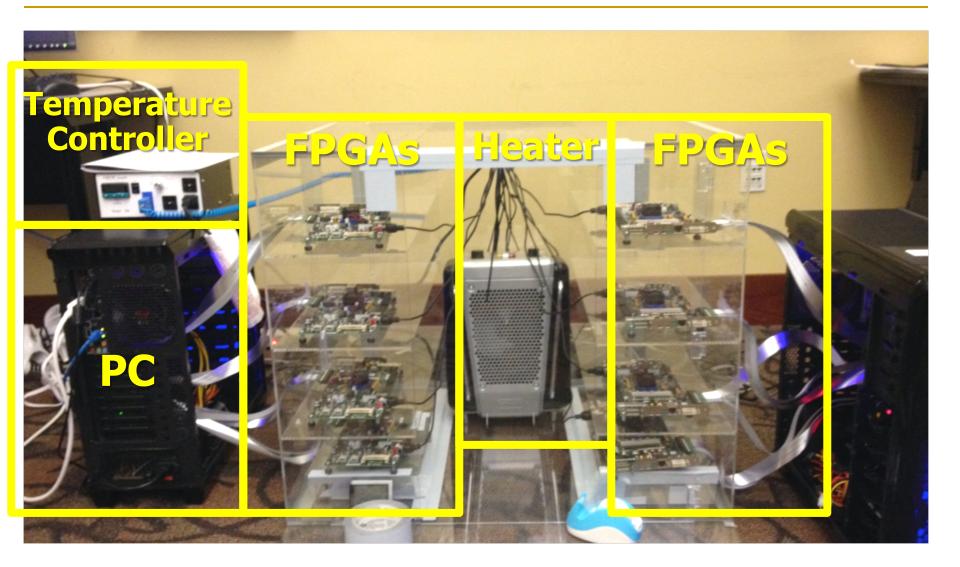

## Infrastructures to Understand Such Issues

## **SAFARI**

Kim+, "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," ISCA 2014.

## SoftMC: Open Source DRAM Infrastructure

Hasan Hassan et al., "<u>SoftMC: A</u> <u>Flexible and Practical Open-</u> <u>Source Infrastructure for</u> <u>Enabling Experimental DRAM</u> <u>Studies</u>," HPCA 2017.

- Flexible

- Easy to Use (C++ API)

- Open-source

github.com/CMU-SAFARI/SoftMC

#### <u>https://github.com/CMU-SAFARI/SoftMC</u>

## SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

Hasan Hassan<sup>1,2,3</sup> Nandita Vijaykumar<sup>3</sup> Samira Khan<sup>4,3</sup> Saugata Ghose<sup>3</sup> Kevin Chang<sup>3</sup> Gennady Pekhimenko<sup>5,3</sup> Donghyuk Lee<sup>6,3</sup> Oguz Ergin<sup>2</sup> Onur Mutlu<sup>1,3</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>TOBB University of Economics & Technology <sup>3</sup>Carnegie Mellon University <sup>4</sup>University of Virginia <sup>5</sup>Microsoft Research <sup>6</sup>NVIDIA Research

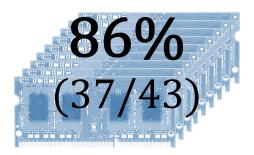

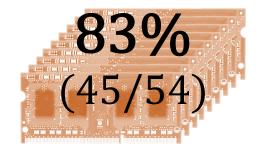

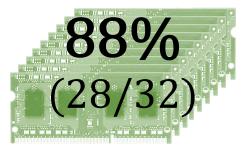

# Latency Reduction Summary of 115 DIMMs

- Latency reduction for read & write (55°C)

- Read Latency: **32.7%**

- Write Latency: 55.1%

- Latency reduction for each timing parameter (55°C)

- Sensing: 17.3%

- Restore: **37.3%** (read), **54.8%** (write)

- Precharge: **35.2%**

**SAFARI** Lee+, "Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case," HPCA 38 2015.

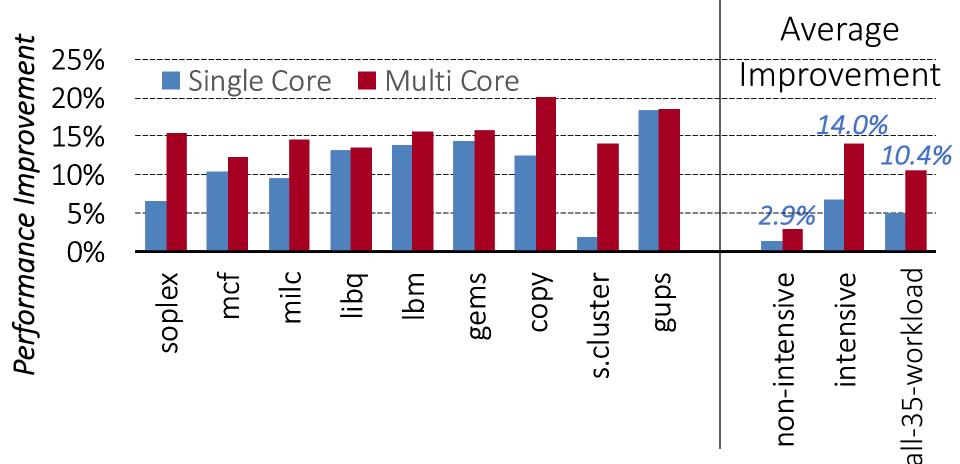

# AL-DRAM: Real-System Performance

AL-DRAM provides high performance on memory-intensive workloads

# Reducing Latency Also Reduces Energy

- AL-DRAM reduces DRAM power consumption

- Major reason: reduction in row activation time

## More on Adaptive-Latency DRAM

Donghyuk Lee, Yoongu Kim, Gennady Pekhimenko, Samira Khan, Vivek Seshadri, Kevin Chang, and Onur Mutlu,

<u>"Adaptive-Latency DRAM: Optimizing DRAM Timing for</u> <u>the Common-Case"</u>

*Proceedings of the 21st International Symposium on High-Performance Computer Architecture (HPCA)*, Bay Area, CA, February 2015.

[Slides (pptx) (pdf)] [Full data sets]

#### Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case

Donghyuk LeeYoongu KimGennady PekhimenkoSamira KhanVivek SeshadriKevin ChangOnur Mutlu

Carnegie Mellon University

# Tackling the Fixed Latency Mindset

- Reliable operation latency is actually very heterogeneous

Across temperatures, chips, parts of a chip, voltage levels, ...

- Idea: Dynamically find out and use the lowest latency one can reliably access a memory location with

- Adaptive-Latency DRAM [HPCA 2015]

- Flexible-Latency DRAM [SIGMETRICS 2016]

- Design-Induced Variation-Aware DRAM [SIGMETRICS 2017]

- Voltron [SIGMETRICS 2017]

- DRAM Latency PUF [HPCA 2018]

- DRAM Latency True Random Number Generator [HPCA 2019]

•••

We would like to find sources of latency heterogeneity and exploit them to minimize latency (or create other benefits)

5AFARI

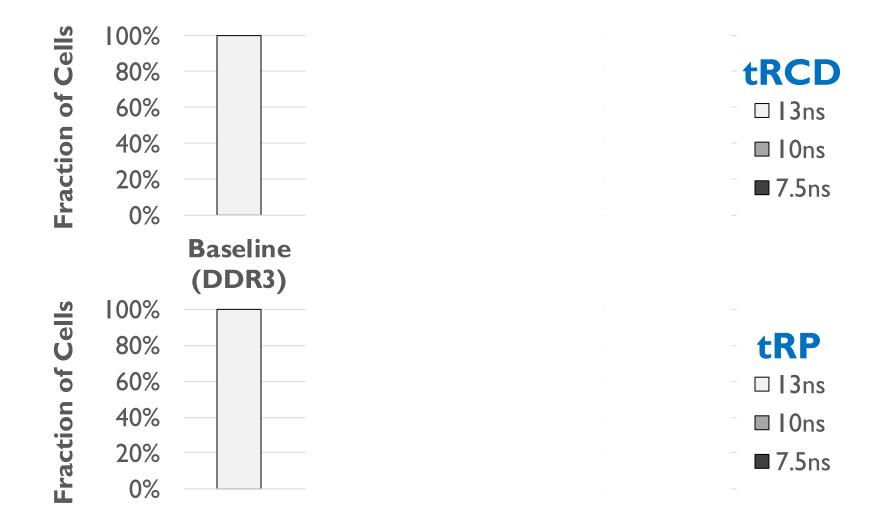

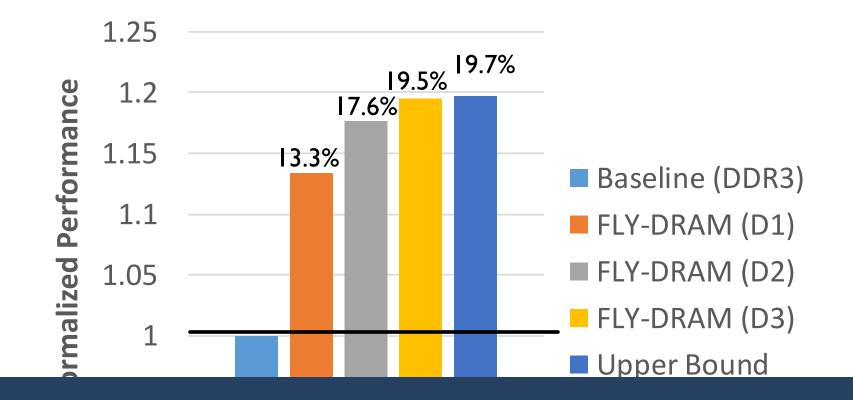

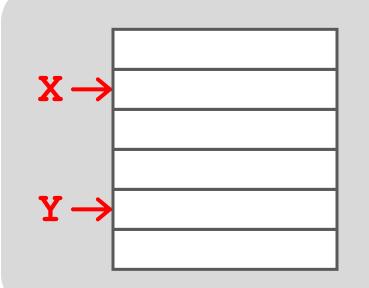

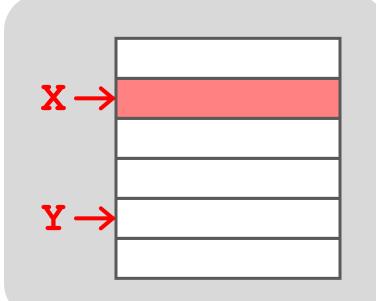

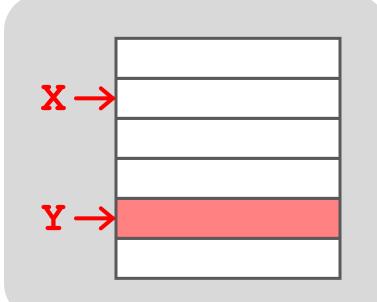

# FLY-DRAM: Reducing DRAM Latency

- **Observation:** DRAM timing errors (slow DRAM cells) are concentrated on certain DRAM regions

- Flexible-LatencY (FLY) DRAM

- A software-transparent design that reduces latency

- Key idea:

- I) Divide memory into regions of different latencies

- 2) Memory controller: Use lower latency for regions without slow cells; higher latency for other regions

Chang+, "Understanding Latency Variation in Modern DRAM Chips: Experimental Characterization, Analysis, and Optimization"," SIGMETRICS 2016.

# **FLY-DRAM Configurations**

Chang+, "Understanding Latency Variation in Modern DRAM Chips: Experimental Characterization, Analysis, and Optimization"," SIGMETRICS 2016.

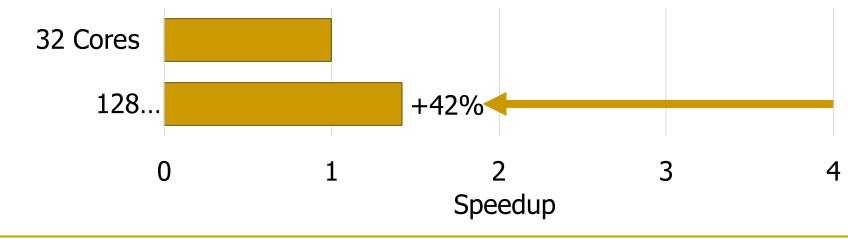

## **FLY-DRAM Performance Results**

## FLY-DRAM improves performance by exploiting spatial latency variation in DRAM

Chang+, "Understanding Latency Variation in Modern DRAM Chips: Experimental Characterization, Analysis, and Optimization"," SIGMETRICS 2016.

## Analysis of Latency Variation in DRAM Chips

- Kevin Chang, Abhijith Kashyap, Hasan Hassan, Samira Khan, Kevin Hsieh, Donghyuk Lee, Saugata Ghose, Gennady Pekhimenko, Tianshi Li, and Onur Mutlu,

- "Understanding Latency Variation in Modern DRAM Chips: Experimental Characterization, Analysis, and Optimization" Proceedings of the <u>ACM International Conference on Measurement and</u>

<u>Modeling of Computer Systems</u> (**SIGMETRICS**), Antibes Juan-Les-Pins, France, June 2016.

[Slides (pptx) (pdf)]

Source Code

## Understanding Latency Variation in Modern DRAM Chips: Experimental Characterization, Analysis, and Optimization

Kevin K. Chang<sup>1</sup> Abhijith Kashyap<sup>1</sup> Hasan Hassan<sup>1,2</sup> Saugata Ghose<sup>1</sup> Kevin Hsieh<sup>1</sup> Donghyuk Lee<sup>1</sup> Tianshi Li<sup>1,3</sup> Gennady Pekhimenko<sup>1</sup> Samira Khan<sup>4</sup> Onur Mutlu<sup>5,1</sup> <sup>1</sup>Carnegie Mellon University <sup>2</sup>TOBB ETÜ <sup>3</sup>Peking University <sup>4</sup>University of Virginia <sup>5</sup>ETH Zürich SAFARI

## Design-Induced Latency Variation in DRAM

- Donghyuk Lee, Samira Khan, Lavanya Subramanian, Saugata Ghose, Rachata Ausavarungnirun, Gennady Pekhimenko, Vivek Seshadri, and Onur Mutlu,

- "Design-Induced Latency Variation in Modern DRAM Chips: Characterization, Analysis, and Latency Reduction Mechanisms" Proceedings of the <u>ACM International Conference on Measurement and</u> <u>Modeling of Computer Systems</u> (SIGMETRICS), Urbana-Champaign, IL, USA, June 2017.

#### Design-Induced Latency Variation in Modern DRAM Chips: Characterization, Analysis, and Latency Reduction Mechanisms

Donghyuk Lee, NVIDIA and Carnegie Mellon University

Samira Khan, University of Virginia

Lavanya Subramanian, Saugata Ghose, Rachata Ausavarungnirun, Carnegie Mellon University

Gennady Pekhimenko, Vivek Seshadri, Microsoft Research

Onur Mutlu, ETH Zürich and Carnegie Mellon University

# Solar-DRAM: Exploiting Spatial Variation

Jeremie S. Kim, Minesh Patel, Hasan Hassan, and Onur Mutlu, "Solar-DRAM: Reducing DRAM Access Latency by Exploiting the Variation in Local Bitlines" Proceedings of the <u>36th IEEE International Conference on Computer</u> Design (ICCD), Orlando, FL, USA, October 2018.

## Solar-DRAM: Reducing DRAM Access Latency by Exploiting the Variation in Local Bitlines

Jeremie S. Kim<sup>‡§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§‡</sup> <sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

## DRAM Latency PUFs

Jeremie S. Kim, Minesh Patel, Hasan Hassan, and <u>Onur Mutlu</u>, <u>"The DRAM Latency PUF: Quickly Evaluating Physical Unclonable</u> <u>Functions by Exploiting the Latency-Reliability Tradeoff in</u> <u>Modern DRAM Devices</u>"

Proceedings of the <u>24th International Symposium on High-Performance</u> <u>Computer Architecture</u> (**HPCA**), Vienna, Austria, February 2018. [Lightning Talk Video] [Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

### The DRAM Latency PUF:

Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern Commodity DRAM Devices

> Jeremie S. Kim<sup>†§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§†</sup> <sup>†</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

## DRAM Latency True Random Number Generator

Jeremie S. Kim, Minesh Patel, Hasan Hassan, Lois Orosa, and Onur Mutlu, "D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput" Proceedings of the <u>25th International Symposium on High-Performance</u> <u>Computer Architecture</u> (HPCA), Washington, DC, USA, February 2019.

## D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

Jeremie S. Kim<sup>‡§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§‡</sup> <sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

# ChargeCache: Exploiting Access Patterns

Hasan Hassan, Gennady Pekhimenko, Nandita Vijaykumar, Vivek Seshadri, Donghyuk Lee, Oguz Ergin, and Onur Mutlu, "ChargeCache: Reducing DRAM Latency by Exploiting Row Access Locality"

Proceedings of the <u>22nd International Symposium on High-</u>

*Performance Computer Architecture (HPCA)*, Barcelona, Spain, March 2016. [Slides (pptx) (pdf)]

[Source Code]

## ChargeCache: Reducing DRAM Latency by Exploiting Row Access Locality

Hasan Hassan<sup>†</sup>\*, Gennady Pekhimenko<sup>†</sup>, Nandita Vijaykumar<sup>†</sup> Vivek Seshadri<sup>†</sup>, Donghyuk Lee<sup>†</sup>, Oguz Ergin<sup>\*</sup>, Onur Mutlu<sup>†</sup>

<sup>†</sup>*Carnegie Mellon University*

\* TOBB University of Economics & Technology

## Exploiting Subarray Level Parallelism

Yoongu Kim, Vivek Seshadri, Donghyuk Lee, Jamie Liu, and Onur Mutlu,

<u>"A Case for Exploiting Subarray-Level Parallelism</u>

(SALP) in DRAM"

Proceedings of the <u>39th International Symposium on</u> <u>Computer Architecture</u> (**ISCA**), Portland, OR, June 2012. <u>Slides (pptx)</u>

#### A Case for Exploiting Subarray-Level Parallelism (SALP) in DRAM

Yoongu Kim

Vivek Seshadri Donghyuk Lee Carnegie Mellon University

Jamie Liu

**Onur** Mutlu

# Tiered-Latency DRAM

Donghyuk Lee, Yoongu Kim, Vivek Seshadri, Jamie Liu, Lavanya Subramanian, and Onur Mutlu,

"Tiered-Latency DRAM: A Low Latency and Low Cost

DRAM Architecture"

Proceedings of the 19th International Symposium on High-Performance Computer Architecture (HPCA), Shenzhen, China, February 2013. Slides (pptx)

#### Tiered-Latency DRAM: A Low Latency and Low Cost DRAM Architecture

Donghyuk Lee Yoongu Kim Vivek Seshadri Jamie Liu Lavanya Subramanian Onur Mutlu Carnegie Mellon University

## LISA: Low-cost Inter-linked Subarrays

Kevin K. Chang, Prashant J. Nair, Saugata Ghose, Donghyuk Lee, Moinuddin K. Qureshi, and Onur Mutlu, "Low-Cost Inter-Linked Subarrays (LISA): Enabling Fast Inter-Subarray Data Movement in DRAM" Proceedings of the <u>22nd International Symposium on High-</u> Performance Computer Architecture (HPCA), Barcelona, Spain, March 2016.

[Slides (pptx) (pdf)] [Source Code]

## Low-Cost Inter-Linked Subarrays (LISA): Enabling Fast Inter-Subarray Data Movement in DRAM

Kevin K. Chang<sup>†</sup>, Prashant J. Nair<sup>\*</sup>, Donghyuk Lee<sup>†</sup>, Saugata Ghose<sup>†</sup>, Moinuddin K. Qureshi<sup>\*</sup>, and Onur Mutlu<sup>†</sup> <sup>†</sup>Carnegie Mellon University <sup>\*</sup>Georgia Institute of Technology

## The CROW Substrate for DRAM

Hasan Hassan, Minesh Patel, Jeremie S. Kim, A. Giray Yaglikci, Nandita Vijaykumar, Nika Mansourighiasi, Saugata Ghose, and Onur Mutlu,

"CROW: A Low-Cost Substrate for Improving DRAM Performance, Energy Efficiency, and Reliability" Proceedings of the <u>46th International Symposium on Computer</u> <u>Architecture</u> (ISCA), Phoenix, AZ, USA, June 2019.

## CROW: A Low-Cost Substrate for Improving DRAM Performance, Energy Efficiency, and Reliability

Hasan Hassan<sup>†</sup>Minesh Patel<sup>†</sup>Jeremie S. Kim<sup>†§</sup>A. Giray Yaglikci<sup>†</sup>Nandita Vijaykumar<sup>†§</sup>Nika Mansouri Ghiasi<sup>†</sup>Saugata Ghose<sup>§</sup>Onur Mutlu<sup>†§</sup>

<sup>†</sup>*ETH Zürich* <sup>§</sup>*Carnegie Mellon University*

## Reducing Refresh Latency

Anup Das, Hasan Hassan, and Onur Mutlu, "VRL-DRAM: Improving DRAM Performance via Variable Refresh Latency" Proceedings of the <u>55th Design Automation</u> <u>Conference</u> (DAC), San Francisco, CA, USA, June 2018.

## VRL-DRAM: Improving DRAM Performance via Variable Refresh Latency

Anup Das Drexel University Philadelphia, PA, USA anup.das@drexel.edu Hasan Hassan ETH Zürich Zürich, Switzerland hhasan@ethz.ch Onur Mutlu ETH Zürich Zürich, Switzerland omutlu@gmail.com

# Parallelizing Refreshes and Accesses

Kevin Chang, Donghyuk Lee, Zeshan Chishti, Alaa Alameldeen, Chris Wilkerson, Yoongu Kim, and Onur Mutlu,

"Improving DRAM Performance by Parallelizing Refreshes with Accesses"

Proceedings of the <u>20th International Symposium on High-Performance</u> Computer Architecture (HPCA), Orlando, FL, February 2014.

[Summary] [Slides (pptx) (pdf)]

SAFARI

## Reducing Performance Impact of DRAM Refresh by Parallelizing Refreshes with Accesses

Kevin Kai-Wei Chang Donghyuk Lee Zeshan Chishti† Alaa R. Alameldeen† Chris Wilkerson† Yoongu Kim Onur Mutlu Carnegie Mellon University †Intel Labs

# Eliminating Refreshes

Jamie Liu, Ben Jaiyen, Richard Veras, and Onur Mutlu, "RAIDR: Retention-Aware Intelligent DRAM Refresh" Proceedings of the <u>39th International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2012. <u>Slides (pdf)</u>

## **RAIDR: Retention-Aware Intelligent DRAM Refresh**

Jamie Liu Ben Jaiyen Richard Veras Onur Mutlu Carnegie Mellon University

## Analysis of Latency-Voltage in DRAM Chips

Kevin Chang, A. Giray Yaglikci, Saugata Ghose, Aditya Agrawal, Niladrish Chatterjee, Abhijith Kashyap, Donghyuk Lee, Mike O'Connor, Hasan Hassan, and Onur Mutlu,

<u>"Understanding Reduced-Voltage Operation in Modern DRAM</u> <u>Devices: Experimental Characterization, Analysis, and</u> <u>Mechanisms"</u> *Proceedings of the <u>ACM International Conference on Measurement and</u> <u>Modeling of Computer Systems</u> (SIGMETRICS), Urbana-Champaign, IL, USA, June 2017.*

#### Understanding Reduced-Voltage Operation in Modern DRAM Chips: Characterization, Analysis, and Mechanisms

Kevin K. Chang<sup>†</sup> Abdullah Giray Yağlıkçı<sup>†</sup> Saugata Ghose<sup>†</sup> Aditya Agrawal<sup>¶</sup> Niladrish Chatterjee<sup>¶</sup> Abhijith Kashyap<sup>†</sup> Donghyuk Lee<sup>¶</sup> Mike O'Connor<sup>¶,‡</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§,†</sup>

<sup>†</sup>Carnegie Mellon University <sup>¶</sup>NVIDIA <sup>‡</sup>The University of Texas at Austin <sup>§</sup>ETH Zürich

# VAMPIRE DRAM Power Model

Saugata Ghose, A. Giray Yaglikci, Raghav Gupta, Donghyuk Lee, Kais Kudrolli, William X. Liu, Hasan Hassan, Kevin K. Chang, Niladrish Chatterjee, Aditya Agrawal, Mike O'Connor, and Onur Mutlu,

"What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study"

Proceedings of the <u>ACM International Conference on Measurement and</u> <u>Modeling of Computer Systems</u> (**SIGMETRICS**), Irvine, CA, USA, June 2018. [<u>Abstract</u>]

## What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study

Saugata Ghose<sup>†</sup> Abdullah Giray Yağlıkçı<sup>‡†</sup> Raghav Gupta<sup>†</sup> Donghyuk Lee<sup>§</sup> Kais Kudrolli<sup>†</sup> William X. Liu<sup>†</sup> Hasan Hassan<sup>‡</sup> Kevin K. Chang<sup>†</sup> Niladrish Chatterjee<sup>§</sup> Aditya Agrawal<sup>§</sup> Mike O'Connor<sup>§¶</sup> Onur Mutlu<sup>‡†</sup> <sup>†</sup>Carnegie Mellon University <sup>‡</sup>ETH Zürich <sup>§</sup>NVIDIA <sup>¶</sup>University of Texas at Austin

# We Can Reduce Memory Latency with Change of Mindset

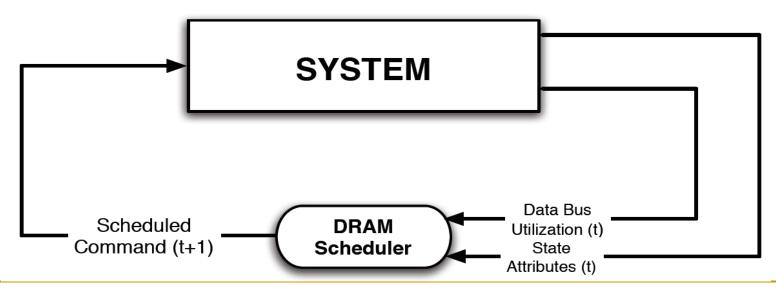

# Main Memory Needs Intelligent Controllers to Reduce Latency

## Data-Centric Architectures: Properties

Process data where it resides (where it makes sense)

Processing in and near memory structures

### Low-latency and low-energy data access

- Low latency memory

- □ Low energy memory

#### Low-cost data storage and processing

High capacity memory at low cost: hybrid memory, compression

#### Intelligent data management

Intelligent controllers handling robustness, security, cost

# Processing Data Where It Makes Sense

## Why In-Memory Computation Today?

- Push from Technology

- DRAM Scaling at jeopardy

- $\rightarrow$  Controllers close to DRAM

- $\rightarrow$  Industry open to new memory architectures

## Why In-Memory Computation Today?

## Memory Scaling Issues Were Real

Onur Mutlu,

"Memory Scaling: A Systems Architecture Perspective"

Proceedings of the <u>5th International Memory</u> Workshop (IMW), Monterey, CA, May 2013. <u>Slides</u> (pptx) (pdf)

EETimes Reprint

## Memory Scaling: A Systems Architecture Perspective

Onur Mutlu Carnegie Mellon University onur@cmu.edu http://users.ece.cmu.edu/~omutlu/

#### https://people.inf.ethz.ch/omutlu/pub/memory-scaling\_memcon13.pdf

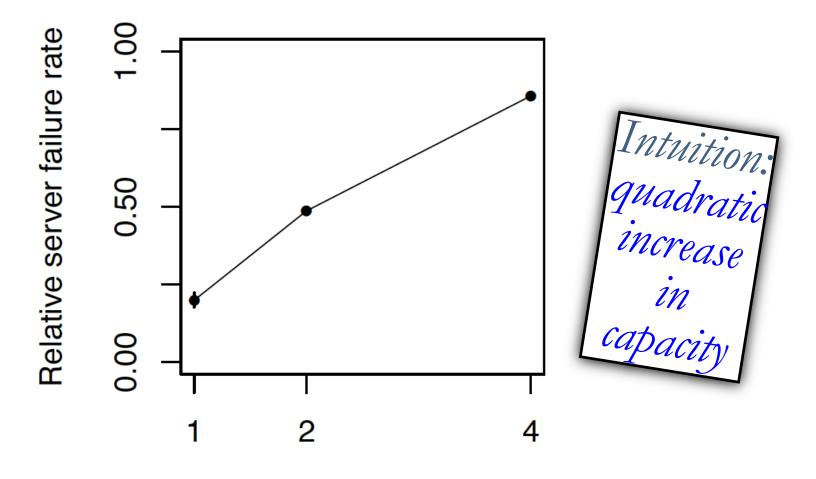

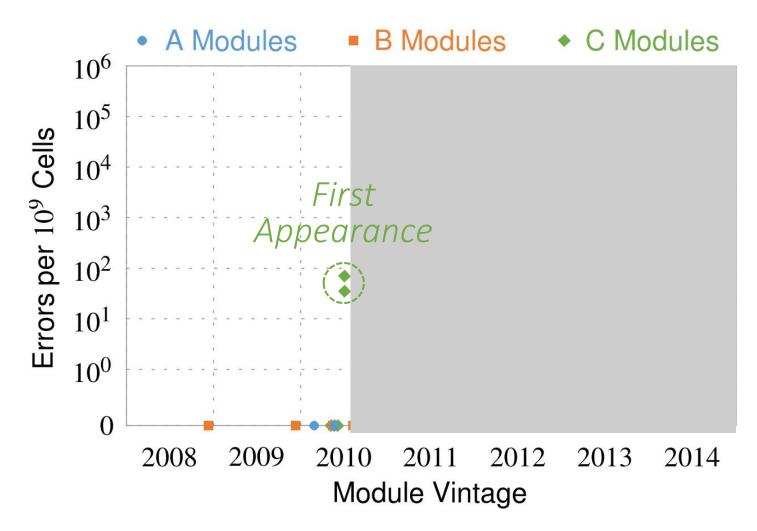

## As Memory Scales, It Becomes Unreliable

- Data from all of Facebook's servers worldwide

- Meza+, "Revisiting Memory Errors in Large-Scale Production Data Centers," DSN'15.

Chip density (Gb)

# Large-Scale Failure Analysis of DRAM Chips

- Analysis and modeling of memory errors found in all of Facebook's server fleet

- Justin Meza, Qiang Wu, Sanjeev Kumar, and Onur Mutlu, <u>"Revisiting Memory Errors in Large-Scale Production Data</u> <u>Centers: Analysis and Modeling of New Trends from the Field"</u> *Proceedings of the <u>45th Annual IEEE/IFIP International Conference on</u> <u>Dependable Systems and Networks</u> (DSN), Rio de Janeiro, Brazil, June 2015. [Slides (pptx) (pdf)] [DRAM Error Model]*

Revisiting Memory Errors in Large-Scale Production Data Centers: Analysis and Modeling of New Trends from the Field

Justin Meza Qiang Wu\* Sanjeev Kumar\* Onur Mutlu

Carnegie Mellon University \* Facebook, Inc.

## Infrastructures to Understand Such Issues

Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors (Kim et al., ISCA 2014)

Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case (Lee et al., HPCA 2015)

AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems (Qureshi et al., DSN 2015) An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms (Liu et al., ISCA 2013)

The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study (Khan et al., SIGMETRICS 2014)

## Infrastructures to Understand Such Issues

#### SAFARI

Kim+, "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," ISCA 2014.

## SoftMC: Open Source DRAM Infrastructure

Hasan Hassan et al., "<u>SoftMC: A</u> <u>Flexible and Practical Open-</u> <u>Source Infrastructure for</u> <u>Enabling Experimental DRAM</u> <u>Studies</u>," HPCA 2017.

- Flexible

- Easy to Use (C++ API)

- Open-source

github.com/CMU-SAFARI/SoftMC

#### <u>https://github.com/CMU-SAFARI/SoftMC</u>

#### SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

Hasan Hassan<sup>1,2,3</sup> Nandita Vijaykumar<sup>3</sup> Samira Khan<sup>4,3</sup> Saugata Ghose<sup>3</sup> Kevin Chang<sup>3</sup> Gennady Pekhimenko<sup>5,3</sup> Donghyuk Lee<sup>6,3</sup> Oguz Ergin<sup>2</sup> Onur Mutlu<sup>1,3</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>TOBB University of Economics & Technology <sup>3</sup>Carnegie Mellon University <sup>4</sup>University of Virginia <sup>5</sup>Microsoft Research <sup>6</sup>NVIDIA Research

#### Data Retention in Memory [Liu et al., ISCA 2013]

Retention Time Profile of DRAM looks like this:

# 64-128ms >256ms

Location dependent Stored value pattern dependent Time dependent

#### SAFARI

## Main Memory Needs Intelligent Controllers

## More on DRAM Refresh (I)

Jamie Liu, Ben Jaiyen, Richard Veras, and Onur Mutlu, "RAIDR: Retention-Aware Intelligent DRAM Refresh" Proceedings of the <u>39th International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2012. <u>Slides (pdf)</u>

#### **RAIDR: Retention-Aware Intelligent DRAM Refresh**

Jamie Liu Ben Jaiyen Richard Veras Onur Mutlu Carnegie Mellon University

#### More on DRAM Refresh (II)

chris.wilkerson@intel.com

Jamie Liu, Ben Jaiyen, Yoongu Kim, Chris Wilkerson, and <u>Onur Mutlu</u>,

"An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms" Proceedings of the <u>40th International Symposium on Computer Architecture</u> (ISCA), Tel-Aviv, Israel, June 2013. <u>Slides (ppt)</u> <u>Slides (pdf)</u>

#### An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms

Jamie Liu\* Ben Jaiyen<sup>\*</sup> Yoongu Kim Carnegie Mellon University Carnegie Mellon University Carnegie Mellon University 5000 Forbes Ave. 5000 Forbes Ave. 5000 Forbes Ave. Pittsburgh, PA 15213 Pittsburgh, PA 15213 Pittsburgh, PA 15213 bjaiyen@alumni.cmu.edu jamiel@alumni.cmu.edu yoonguk@ece.cmu.edu Chris Wilkerson Onur Mutlu Intel Corporation Carnegie Mellon University 2200 Mission College Blvd. 5000 Forbes Ave. Santa Clara, CA 95054 Pittsburgh, PA 15213

onur@cmu.edu

## More on DRAM Refresh (III)

Samira Khan, Donghyuk Lee, Yoongu Kim, Alaa Alameldeen, Chris Wilkerson, and Onur Mutlu, "The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study" Proceedings of the <u>ACM International Conference on Measurement and</u> Modeling of Computer Systems (SIGMETRICS), Austin, TX, June 2014. [Slides] (pptx) (pdf)] [Poster (pptx) (pdf)] [Full data sets]

#### The Efficacy of Error Mitigation Techniques for DRAM **Retention Failures: A Comparative Experimental Study**

Samira Khan<sup>†</sup>\* samirakhan@cmu.edu

Donghyuk Lee<sup>†</sup> donghyuk1@cmu.edu

Chris Wilkerson\*

Yoongu Kim<sup>†</sup> yoongukim@cmu.edu

Alaa R. Alameldeen\* alaa.r.alameldeen@intel.com chris.wilkerson@intel.com

Onur Mutlu<sup>†</sup> onur@cmu.edu

\*Intel Labs <sup>†</sup>Carnegie Mellon University

#### SAFARI

#### More on DRAM Refresh (IV)

Moinuddin Qureshi, Dae Hyun Kim, Samira Khan, Prashant Nair, and Onur Mutlu, "AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM <u>Systems</u>" Proceedings of the <u>45th Annual IEEE/IFIP International Conference on</u> <u>Dependable Systems and Networks</u> (DSN), Rio de Janeiro, Brazil, June 2015. [Slides (pptx) (pdf)]

#### AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems

Moinuddin K. Qureshi<sup>†</sup> Dae-Hyun Kim<sup>†</sup> <sup>†</sup>Georgia Institute of Technology {*moin, dhkim, pnair6*}@*ece.gatech.edu*  Samira Khan<sup>‡</sup>

Prashant J. Nair<sup>†</sup> Onur Mutlu<sup>‡</sup> <sup>‡</sup>Carnegie Mellon University

{samirakhan, onur}@cmu.edu

## More on DRAM Refresh (V)

Samira Khan, Donghyuk Lee, and Onur Mutlu, "PARBOR: An Efficient System-Level Technique to Detect Data-Dependent Failures in DRAM" Proceedings of the <u>45th Annual IEEE/IFIP International Conference on</u> Dependable Systems and Networks (DSN), Toulouse, France, June 2016. [Slides (pptx) (pdf)]

#### PARBOR: An Efficient System-Level Technique to Detect Data-Dependent Failures in DRAM

Samira Khan<sup>\*</sup> Donghyuk Lee<sup>†‡</sup> Onur Mutlu<sup>\*†</sup> \*University of Virginia <sup>†</sup>Carnegie Mellon University <sup>‡</sup>Nvidia \*ETH Zürich

## More on DRAM Refresh (VI)

Samira Khan, Chris Wilkerson, Zhe Wang, Alaa R. Alameldeen, Donghyuk Lee, and Onur Mutlu,

"Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content"

Proceedings of the <u>50th International Symposium on Microarchitecture</u> (MICRO), Boston, MA, USA, October 2017.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Poster (pptx) (pdf)]

#### Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content

Samira Khan<sup>\*</sup> Chris Wilkerson<sup>†</sup> Zhe Wang<sup>†</sup> Alaa R. Alameldeen<sup>†</sup> Donghyuk Lee<sup>‡</sup> Onur Mutlu<sup>\*</sup> <sup>\*</sup>University of Virginia <sup>†</sup>Intel Labs <sup>‡</sup>Nvidia Research <sup>\*</sup>ETH Zürich

#### **SAFARI**

#### More on DRAM Refresh (VII)

- Minesh Patel, Jeremie S. Kim, and Onur Mutlu,

"The Reach Profiler (REAPER): Enabling the Mitigation of DRAM Retention Failures via Profiling at Aggressive Conditions"

Proceedings of the <u>44th International Symposium on Computer</u> Architecture (ISCA), Toronto, Canada, June 2017.

[Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

- First experimental analysis of (mobile) LPDDR4 chips

- Analyzes the complex tradeoff space of retention time profiling

- Idea: enable fast and robust profiling at higher refresh intervals & temperatures

#### The Reach Profiler (REAPER): Enabling the Mitigation of DRAM Retention Failures via Profiling at Aggressive Conditions

Minesh Patel<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> Onur Mutlu<sup>§‡</sup> <sup>§</sup>ETH Zürich <sup>‡</sup>Carnegie Mellon University

### More on DRAM Refresh (VIII)

Minesh Patel, Jeremie S. Kim, Hasan Hassan, and Onur Mutlu, "Understanding and Modeling On-Die Error Correction in Modern DRAM: An Experimental Study Using Real Devices" Proceedings of the <u>49th Annual IEEE/IFIP International Conference on</u> Dependable Systems and Networks (DSN), Portland, OR, USA, June 2019. [Source Code for EINSim, the Error Inference Simulator] Best paper session.

#### Understanding and Modeling On-Die Error Correction in Modern DRAM: An Experimental Study Using Real Devices

Minesh Patel<sup>†</sup> Jeremie S. Kim<sup>‡†</sup> Hasan Hassan<sup>†</sup> Onur Mutlu<sup>†‡</sup>  $^{\dagger}ETH Z \ddot{u}rich$  <sup>‡</sup>Carnegie Mellon University

#### Memory Scaling Issues Are Real

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

<u>IEEE Transactions on Computer-Aided Design of Integrated</u>

<u>Circuits and Systems</u> (TCAD) Special Issue on Top Picks in

Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

## RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> <sup>§</sup>ETH Zürich <sup>‡</sup>Carnegie Mellon University A Curious Discovery [Kim et al., ISCA 2014]

## One can predictably induce errors in most DRAM memory chips

#### The Story of RowHammer

- One can predictably induce bit flips in commodity DRAM chips

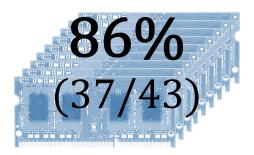

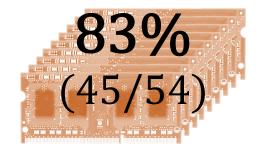

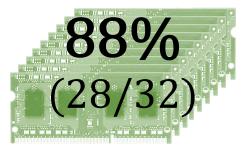

>80% of the tested DRAM chips are vulnerable

- First example of how a simple hardware failure mechanism can create a widespread system security vulnerability

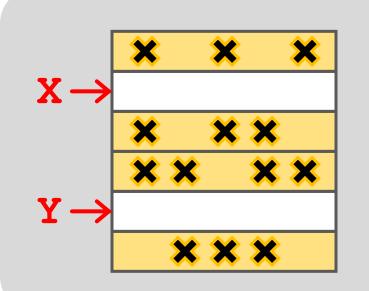

#### Modern DRAM is Prone to Disturbance Errors

Repeatedly reading a row enough times (before memory gets refreshed) induces disturbance errors in adjacent rows in most real DRAM chips you can buy today

Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors, (Kim et al., ISCA 2014)

## Most DRAM Modules Are Vulnerable

A company B company

**C** company

| Up to               | Up to               | Up to               |

|---------------------|---------------------|---------------------|

| 1.0×10 <sup>7</sup> | 2.7×10 <sup>6</sup> | 3.3×10 <sup>5</sup> |

| errors              | errors              | errors              |

Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors, (Kim et al., ISCA 2014)

## Most DRAM Modules Are Vulnerable

A company B company

**C** company

| Up to               | Up to               | Up to               |

|---------------------|---------------------|---------------------|

| 1.0×10 <sup>7</sup> | 2.7×10 <sup>6</sup> | 3.3×10 <sup>5</sup> |

| errors              | errors              | errors              |

Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors, (Kim et al., ISCA 2014)

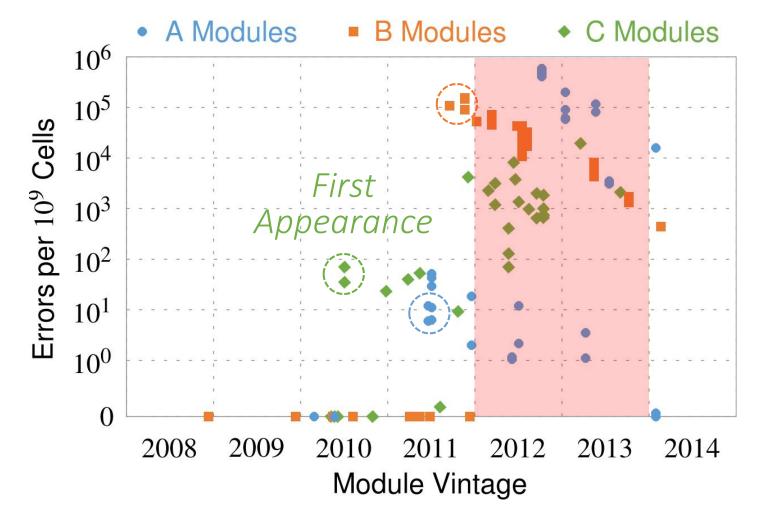

## Recent DRAM Is More Vulnerable

## Recent DRAM Is More Vulnerable

## Recent DRAM Is More Vulnerable

All modules from 2012–2013 are vulnerable

loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop

- Avoid *cache hits* Flush X from cache

- Avoid *row hits* to X

Read Y in another row

loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop

loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop

loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop

## Observed Errors in Real Systems

| CPU Architecture          | Errors | Access-Rate |

|---------------------------|--------|-------------|

| Intel Haswell (2013)      | 22.9K  | 12.3M/sec   |

| Intel Ivy Bridge (2012)   | 20.7K  | 11.7M/sec   |

| Intel Sandy Bridge (2011) | 16.1K  | 11.6M/sec   |

| AMD Piledriver (2012)     | 59     | 6.1M/sec    |

#### A real reliability & security issue

Kim+, "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," ISCA 2014.

#### One Can Take Over an Otherwise-Secure System

#### Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Abstract. Memory isolation is a key property of a reliable and secure computing system — an access to one memory address should not have unintended side effects on data stored in other addresses. However, as DRAM process technology

## Project Zero

<u>Flipping Bits in Memory Without Accessing Them:</u> <u>An Experimental Study of DRAM Disturbance Errors</u> (Kim et al., ISCA 2014)

News and updates from the Project Zero team at Google

Exploiting the DRAM rowhammer bug to gain kernel privileges (Seaborn, 2015)

Monday, March 9, 2015

Exploiting the DRAM rowhammer bug to gain kernel privileges

### RowHammer Security Attack Example

- "Rowhammer" is a problem with some recent DRAM devices in which repeatedly accessing a row of memory can cause bit flips in adjacent rows (Kim et al., ISCA 2014).

- Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors (Kim et al., ISCA 2014)

- We tested a selection of laptops and found that a subset of them exhibited the problem.

- We built two working privilege escalation exploits that use this effect.

- Exploiting the DRAM rowhammer bug to gain kernel privileges (Seaborn+, 2015)

- One exploit uses rowhammer-induced bit flips to gain kernel privileges on x86-64 Linux when run as an unprivileged userland process.

- When run on a machine vulnerable to the rowhammer problem, the process was able to induce bit flips in page table entries (PTEs).

- It was able to use this to gain write access to its own page table, and hence gain read-write access to all of physical memory.

#### Exploiting the DRAM rowhammer bug to gain kernel privileges (Seaborn & Dullien, 2015) $^{100}$

### Security Implications

#### Security Implications

It's like breaking into an apartment by repeatedly slamming a neighbor's door until the vibrations open the door you were after

## More Security Implications (I)

#### "We can gain unrestricted access to systems of website visitors."

Not there yet, but ...

ROOT privileges for web apps!

Daniel Gruss (@lavados), Clémentine Maurice (@BloodyTangerine), December 28, 2015 - 32c3, Hamburg, Germany

Rowhammer.js: A Remote Software-Induced Fault Attack in JavaScript (DIMVA'16)

Source: https://lab.dsst.io/32c3-slides/7197.html

29

#### More Security Implications (II)

"Can gain control of a smart phone deterministically"

## Hammer And Root

# androids Millions of Androids

Drammer: Deterministic Rowhammer Attacks on Mobile Platforms, CCS'16<sup>104</sup>

Source: https://fossbytes.com/drammer-rowhammer-attack-android-root-devices/

## More Security Implications (III)

Using an integrated GPU in a mobile system to remotely escalate privilege via the WebGL interface

ars TECHNICA

BIZ & IT TECH SCIENCE POLICY CARS GAMING & CULTURE

####

## Drive-by Rowhammer attack uses GPU to compromise an Android phone

JavaScript based GLitch pwns browsers by flipping bits inside memory chips.

DAN GOODIN - 5/3/2018, 12:00 PM

#### Grand Pwning Unit: Accelerating Microarchitectural Attacks with the GPU

Pietro Frigo Vrije Universiteit Amsterdam p.frigo@vu.nl Cristiano Giuffrida Vrije Universiteit Amsterdam giuffrida@cs.vu.nl Herbert Bos Vrije Universiteit Amsterdam herbertb@cs.vu.nl Kaveh Razavi Vrije Universiteit Amsterdam kaveh@cs.vu.nl

## More Security Implications (IV)

#### Rowhammer over RDMA (I)

ars TECHNICA

BIZ & IT TECH SCIENCE POLICY CARS GAMING & CULTURE

THROWHAMMER —

# Packets over a LAN are all it takes to trigger serious Rowhammer bit flips

The bar for exploiting potentially serious DDR weakness keeps getting lower.

DAN GOODIN - 5/10/2018, 5:26 PM

#### **Throwhammer: Rowhammer Attacks over the Network and Defenses**

Andrei Tatar VU Amsterdam Radhesh Krishnan VU Amsterdam Elias Athanasopoulos University of Cyprus

Herbert Bos VU Amsterdam Kaveh Razavi VU Amsterdam Cristiano Giuffrida VU Amsterdam

#### More Security Implications (V)

Rowhammer over RDMA (II)

## Security in a serious way

Nethammer—Exploiting DRAM Rowhammer Bug Through Network Requests

#### Nethammer: Inducing Rowhammer Faults through Network Requests

Moritz Lipp Graz University of Technology

Daniel Gruss Graz University of Technology Misiker Tadesse Aga University of Michigan

Clémentine Maurice Univ Rennes, CNRS, IRISA

Lukas Lamster Graz University of Technology Michael Schwarz Graz University of Technology

Lukas Raab Graz University of Technology

#### More Security Implications?

# Memory Scaling Issues Are Real

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

"Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors"

Proceedings of the <u>41st International Symposium on Computer</u>

<u>Architecture</u> (ISCA), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data]

### Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly<sup>\*</sup> Jeremie Kim<sup>1</sup> Chris Fallin<sup>\*</sup> Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup> <sup>1</sup>Carnegie Mellon University <sup>2</sup>Intel Labs

### More on RowHammer

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

IEEE Transactions on Computer-Aided Design of Integrated

Circuits and Systems (TCAD) Special Issue on Top Picks in

Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

# RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> <sup>§</sup>ETH Zürich <sup>‡</sup>Carnegie Mellon University

# Apple's Patch for RowHammer

#### https://support.apple.com/en-gb/HT204934

Available for: OS X Mountain Lion v10.8.5, OS X Mavericks v10.9.5

Impact: A malicious application may induce memory corruption to escalate privileges

Description: A disturbance error, also known as Rowhammer, exists with some DDR3 RAM that could have led to memory corruption. This issue was mitigated by increasing memory refresh rates.

CVE-ID

CVE-2015-3693 : Mark Seaborn and Thomas Dullien of Google, working from original research by Yoongu Kim et al (2014)

HP, Lenovo, and other vendors released similar patches

# **Our Solution to RowHammer**

- PARA: <u>Probabilistic Adjacent Row Activation</u>

- Key Idea

- After closing a row, we activate (i.e., refresh) one of its neighbors with a low probability: p = 0.005

- Reliability Guarantee

- When p=0.005, errors in one year:  $9.4 \times 10^{-14}$

- By adjusting the value of p, we can vary the strength of protection against errors

# Advantages of PARA

- PARA refreshes rows infrequently

- Low power

- Low performance-overhead

- Average slowdown: 0.20% (for 29 benchmarks)

- Maximum slowdown: 0.75%

- PARA is stateless

- Low cost

- Low complexity

- PARA is an effective and low-overhead solution to prevent disturbance errors

# Requirements for PARA

- If implemented in DRAM chip (done today)

- Enough slack in timing and refresh parameters

- Plenty of slack today:

- Lee et al., "Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common Case," HPCA 2015.

- Chang et al., "Understanding Latency Variation in Modern DRAM Chips," SIGMETRICS 2016.

- Lee et al., "Design-Induced Latency Variation in Modern DRAM Chips," SIGMETRICS 2017.

- Chang et al., "Understanding Reduced-Voltage Operation in Modern DRAM Devices," SIGMETRICS 2017.

- Ghose et al., "What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study," SIGMETRICS 2018.

- If implemented in memory controller

- Better coordination between memory controller and DRAM

- Memory controller should know which rows are physically adjacent

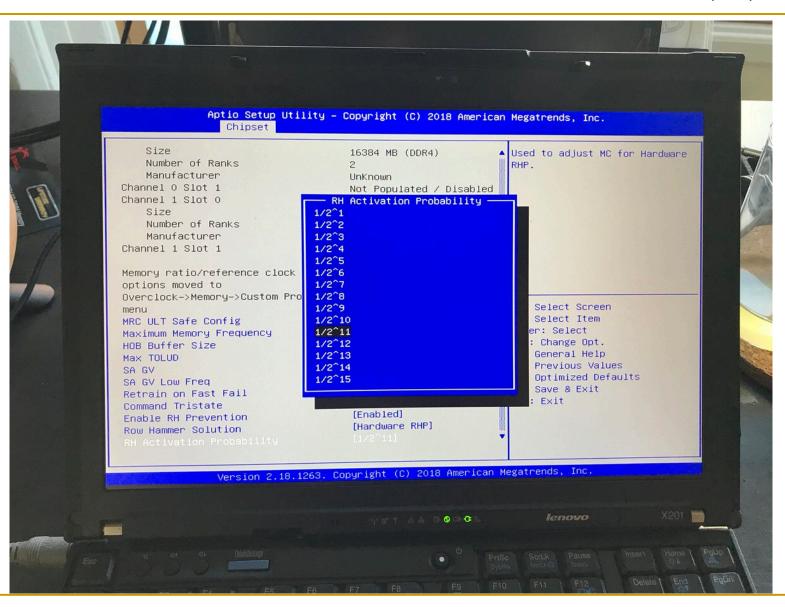

# Probabilistic Activation in Real Life (I)

| Aptio Setup Utili<br>Chipset                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ty – Copyright (C) 2018 Ameri                                                                                                      | can Megatrends, Inc.                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel O Slot O<br>Size<br>Number of Ranks<br>Manufacturer<br>Channel O Slot 1<br>Channel 1 Slot O<br>Size<br>Number of Ranks<br>Manufacturer<br>Channel 1 Slot 1<br>Memory ratio/reference clock<br>options moved to<br>Overclock->Memory->Custom Profi<br>menu<br>MRC ULT Safe Config<br>Maximum Memory Frequency<br>HOB Buffer Size<br>Max TOLUD<br>SA GV<br>SA GV<br>SA GV Low Freq<br>Retrain on Fast Fail<br>Command Tristate<br>Enable RH Prevention<br>Row Hammer Solution | [Disabled]<br>[Auto]<br>[Auto]<br>[Dynamic]<br>[Enabled]<br>[MRC default]<br>[Enabled]<br>[Enabled]<br>[Enabled]<br>[Hardware RHP] | ed<br>++: Select Screen<br>1: Select Item<br>Enter: Select<br>+/-: Change Opt.<br>F1: General Help<br>F2: Previous Values<br>F3: Optimized Defaults<br>F4: Save & Exit<br>ESC: Exit |

| Version 2.18.126                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53. Copyright (C) 2018 America                                                                                                     | an Megatrends, Inc.                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    | lenovo X201 🔛                                                                                                                                                                       |

**SAFARI**

https://twitter.com/isislovecruft/status/1021939922754723841

# Probabilistic Activation in Real Life (II)

**SAFARI**

https://twitter.com/isislovecruft/status/1021939922754723841

## More on RowHammer Analysis

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

"Flipping Bits in Memory Without Accessing Them: An

Experimental Study of DRAM Disturbance Errors"

Proceedings of the <u>41st International Symposium on Computer</u>

<u>Architecture</u> (ISCA), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data]

### Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly<sup>\*</sup> Jeremie Kim<sup>1</sup> Chris Fallin<sup>\*</sup> Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup> <sup>1</sup>Carnegie Mellon University <sup>2</sup>Intel Labs

# Future of Memory Reliability

# Onur Mutlu, "The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser" Invited Paper in Proceedings of the Design, Automation, and Test in Europe Conference (DATE), Lausanne, Switzerland, March 2017. [Slides (pptx) (pdf)]

#### The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser

Onur Mutlu ETH Zürich onur.mutlu@inf.ethz.ch https://people.inf.ethz.ch/omutlu

SAFARI https://people.inf.ethz.ch/omutlu/pub/rowhammer-and-other-memory-issues date17.pdf 118

# A RowHammer Retrospective

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

IEEE Transactions on Computer-Aided Design of Integrated

Circuits and Systems (TCAD) Special Issue on Top Picks in

Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

# RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> <sup>§</sup>ETH Zürich <sup>‡</sup>Carnegie Mellon University

# Main Memory Needs Intelligent Controllers

# Why In-Memory Computation Today?

- Pull from Systems and Applications

- Data access is a major system and application bottleneck

- Systems are energy limited

- Data movement much more energy-hungry than computation

#### SAFARI

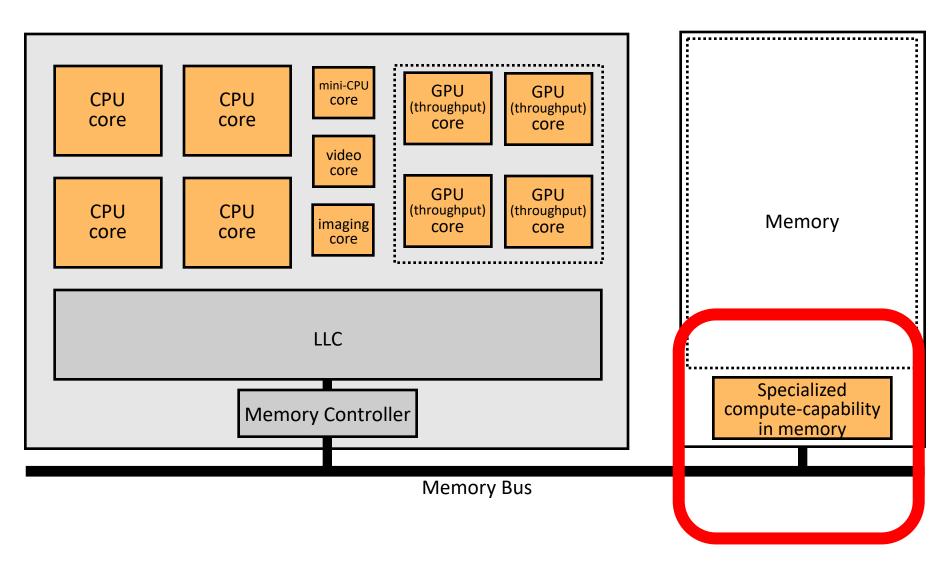

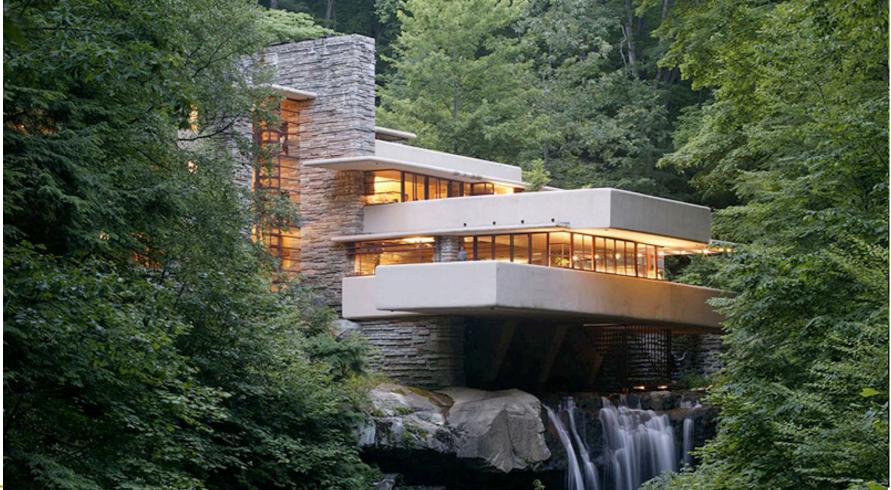

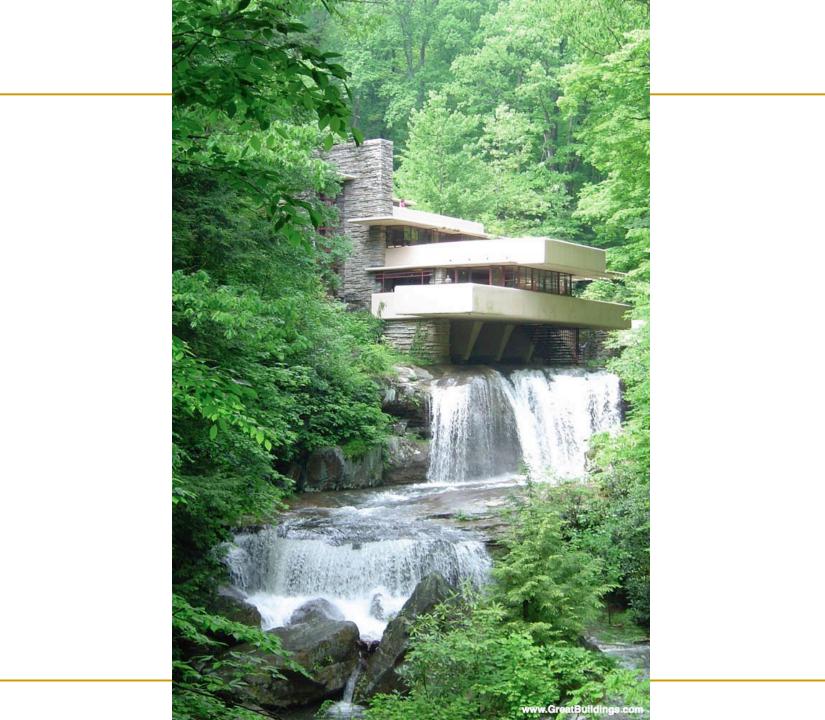

### Do We Want This?

SAFARI Source

Source: V. Milutinovic

### Or This?

Challenge and Opportunity for Future

# High Performance, Energy Efficient, Sustainable

Data access is the major performance and energy bottleneck

# Our current design principles cause great energy waste (and great performance loss)

# Processing of data is performed far away from the data

# A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### **Computing System**

Image source: https://lbsitbytes2010.wordpress.com/2013/03/29/john-von-neumann-roll-no-15/

# A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### **Computing System**

Image source: https://lbsitbytes2010.wordpress.com/2013/03/29/john-von-neumann-roll-no-15/

# Today's Computing Systems

- Are overwhelmingly processor centric

- All data processed in the processor  $\rightarrow$  at great system cost

- Processor is heavily optimized and is considered the master

- Data storage units are dumb and are largely unoptimized (except for some that are on the processor die)

I expect that over the coming decade memory subsystem design will be the *only* important design issue for microprocessors.

#### "It's the Memory, Stupid!" (Richard Sites, MPR, 1996)

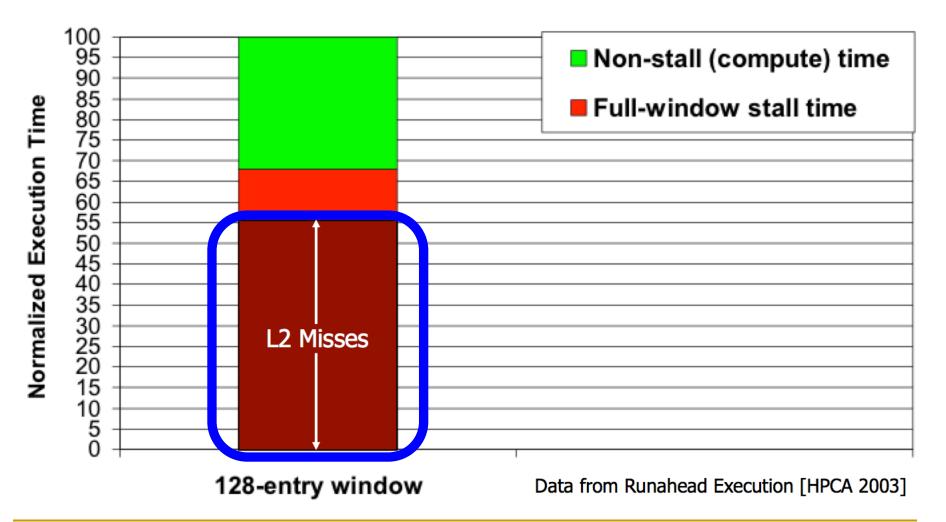

Mutlu+, "Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-Order Processors," HPCA 2003.

# The Performance Perspective

Onur Mutlu, Jared Stark, Chris Wilkerson, and Yale N. Patt, "Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors" Proceedings of the <u>9th International Symposium on High-Performance</u> <u>Computer Architecture</u> (HPCA), pages 129-140, Anaheim, CA, February 2003. <u>Slides (pdf)</u>

#### **Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors**

Onur Mutlu § Jared Stark † Chris Wilkerson ‡ Yale N. Patt §

§ECE Department The University of Texas at Austin {onur,patt}@ece.utexas.edu †Microprocessor Research Intel Labs jared.w.stark@intel.com

Desktop Platforms Group Intel Corporation chris.wilkerson@intel.com

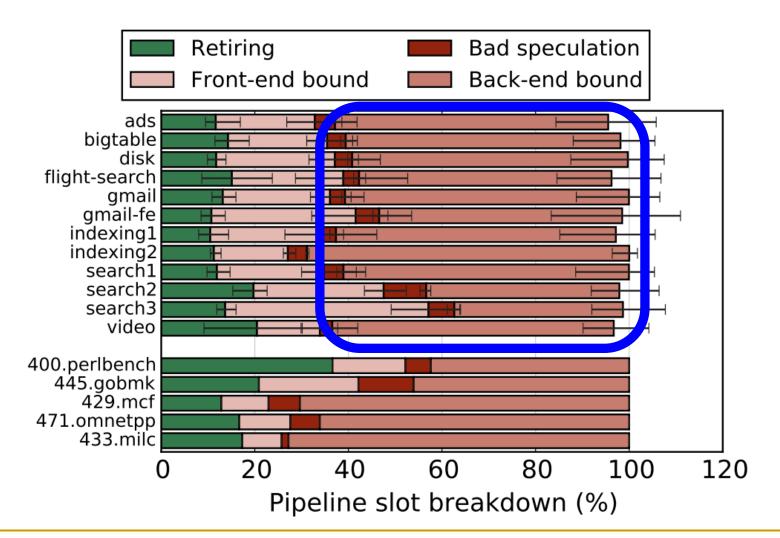

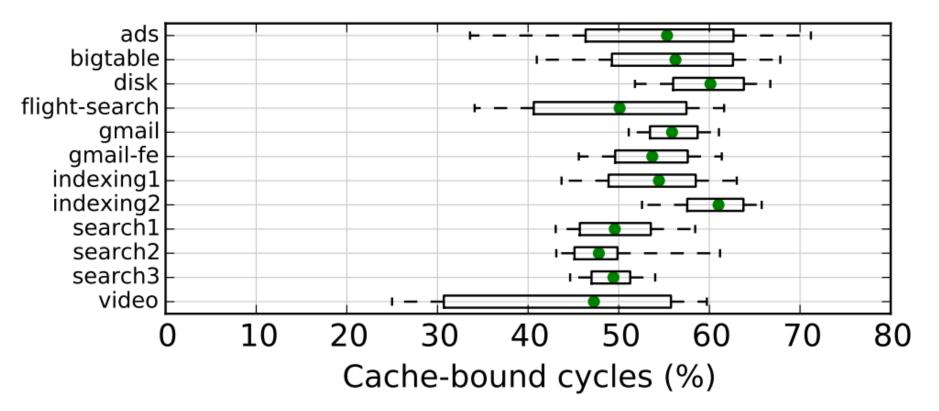

# The Performance Perspective (Today)

All of Google's Data Center Workloads (2015):

Kanev+, "Profiling a Warehouse-Scale Computer," ISCA 2015.

# The Performance Perspective (Today)

All of Google's Data Center Workloads (2015):

#### Figure 11: Half of cycles are spent stalled on caches.

# Perils of Processor-Centric Design

#### Grossly-imbalanced systems

- Processing done only in **one place**

- Everything else just stores and moves data: data moves a lot

- $\rightarrow$  Energy inefficient

- $\rightarrow$  Low performance

- $\rightarrow$  Complex

- Overly complex and bloated processor (and accelerators)

- To tolerate data access from memory

- Complex hierarchies and mechanisms

- $\rightarrow$  Energy inefficient

- $\rightarrow$  Low performance

- $\rightarrow$  Complex

# Perils of Processor-Centric Design

#### Most of the system is dedicated to storing and moving data

# The Energy Perspective

#### SAFARI

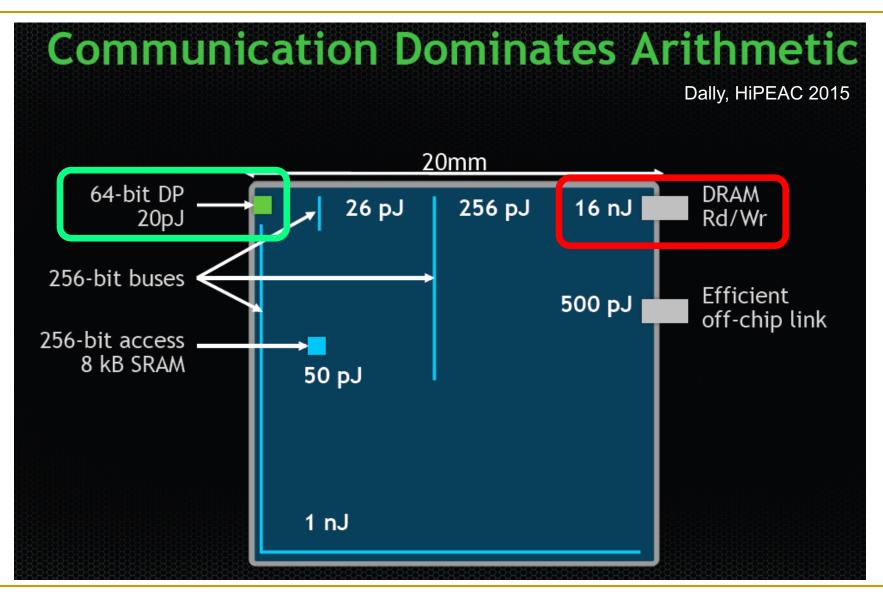

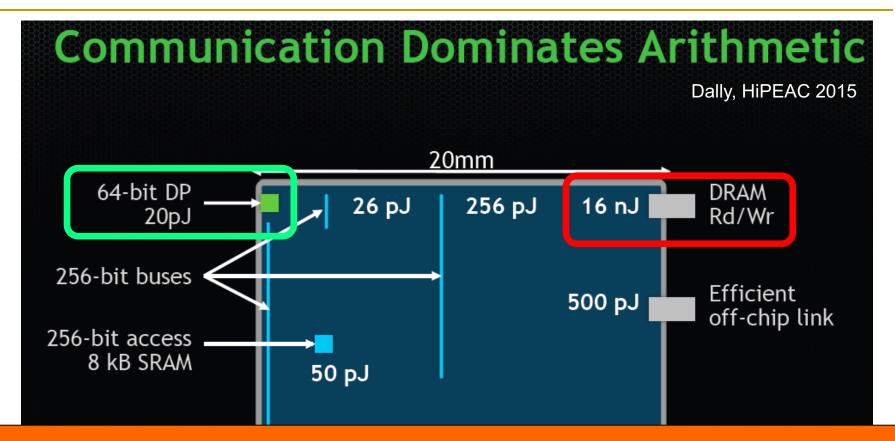

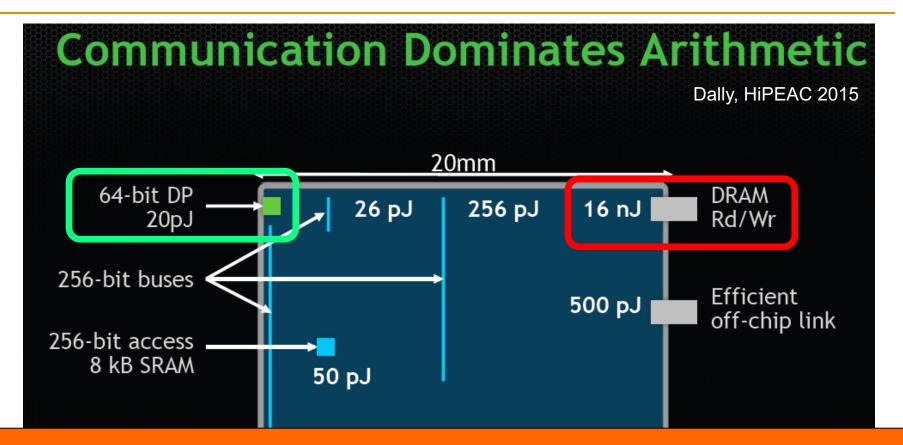

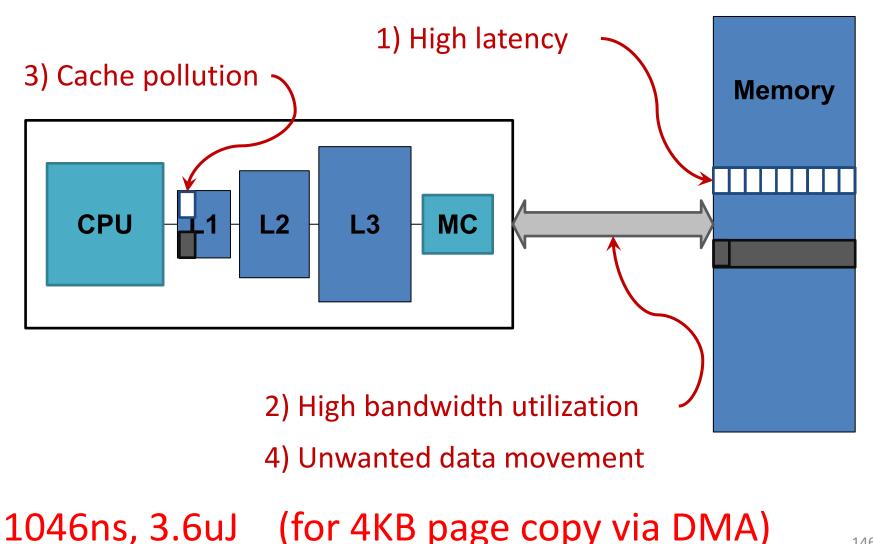

# Data Movement vs. Computation Energy

# A memory access consumes ~100-1000X the energy of a complex addition

# Data Movement vs. Computation Energy

Data movement is a major system energy bottleneck

- Comprises 41% of mobile system energy during web browsing [2]

- Costs ~115 times as much energy as an ADD operation [1, 2]

[1]: Reducing data Movement Energy via Online Data Clustering and Encoding (MICRO'16)

[2]: Quantifying the energy cost of data movement for emerging smart phone workloads on mobile platforms (IISWC'14)

#### SAFARI

# Energy Waste in Mobile Devices

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the <u>23rd International Conference on Architectural Support for Programming</u> <u>Languages and Operating Systems</u> (ASPLOS), Williamsburg, VA, USA, March 2018.

# 62.7% of the total system energy is spent on data movement

### Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup>Saugata Ghose<sup>1</sup>Youngsok Kim<sup>2</sup>Rachata Ausavarungnirun<sup>1</sup>Eric Shiu<sup>3</sup>Rahul Thakur<sup>3</sup>Daehyun Kim<sup>4,3</sup>Aki Kuusela<sup>3</sup>Allan Knies<sup>3</sup>Parthasarathy Ranganathan<sup>3</sup>Onur Mutlu<sup>5,1</sup>139

# We Do Not Want to Move Data!

# A memory access consumes ~100-1000X the energy of a complex addition

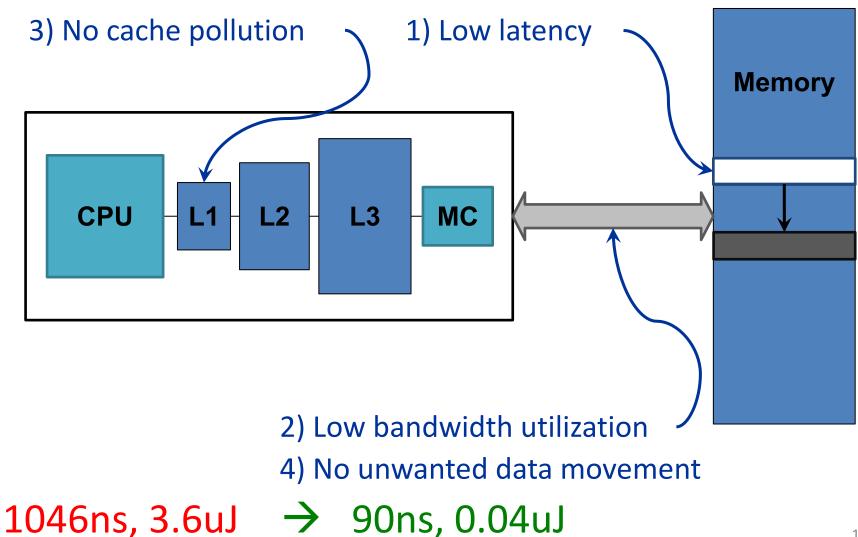

# We Need A Paradigm Shift To ...

Enable computation with minimal data movement

Compute where it makes sense (where data resides)

Make computing architectures more data-centric

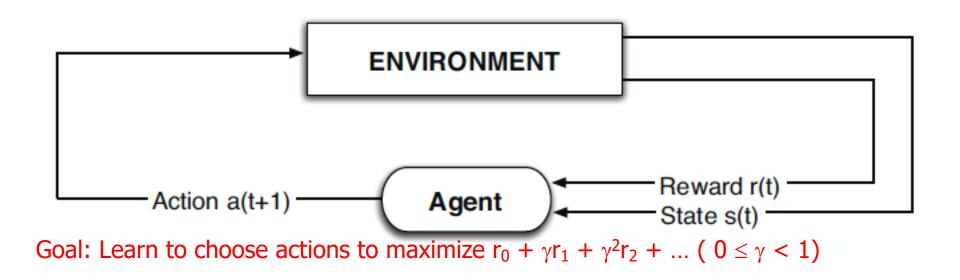

# Goal: Processing Inside Memory

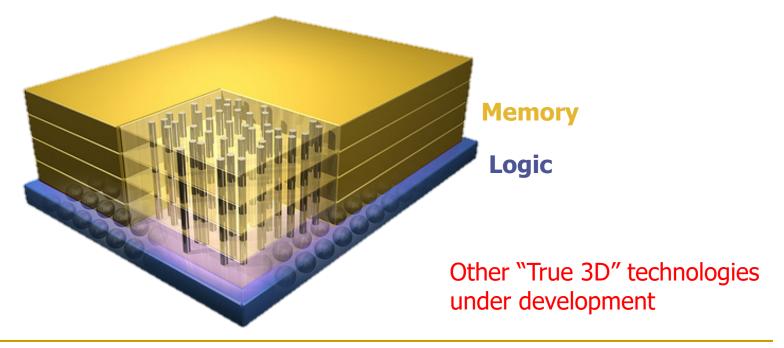

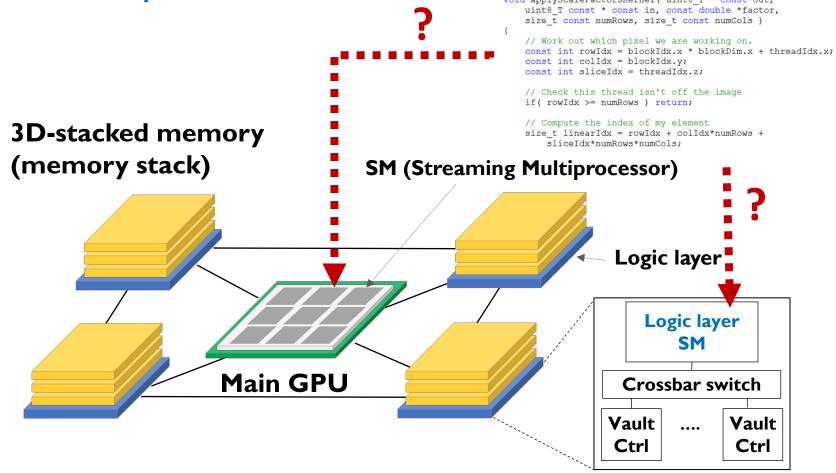

# Processing in Memory: Two Approaches

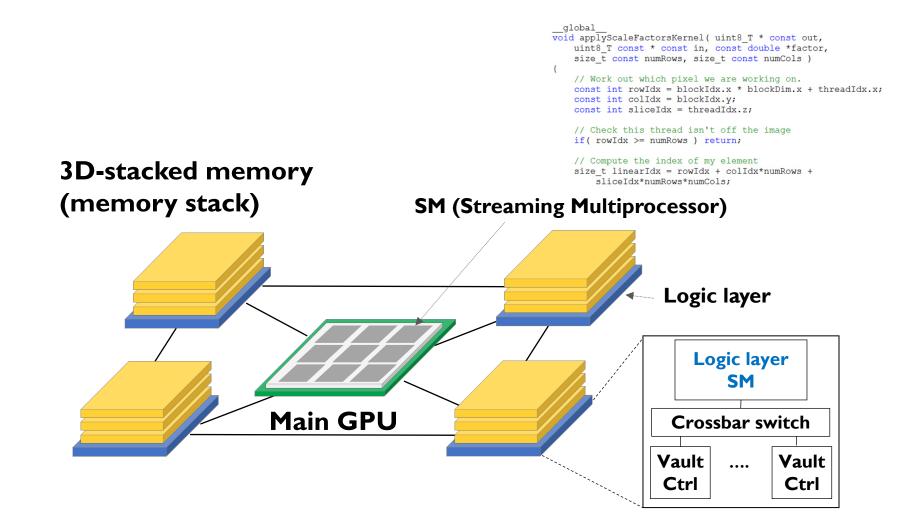

Minimally changing memory chips

Exploiting 3D-stacked memory

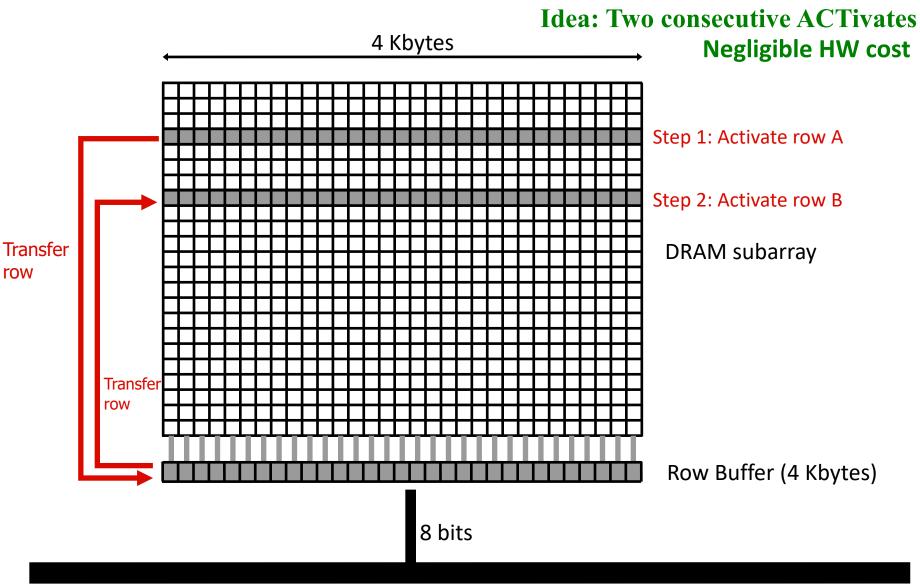

# Approach 1: Minimally Changing Memory

- DRAM has great capability to perform bulk data movement and computation internally with small changes

- Can exploit internal connectivity to move data

- Can exploit analog computation capability

• Examples: RowClone, In-DRAM AND/OR, Gather/Scatter DRAM

- <u>RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data</u> (Seshadri et al., MICRO 2013)

- □ Fast Bulk Bitwise AND and OR in DRAM (Seshadri et al., IEEE CAL 2015)

- <u>Gather-Scatter DRAM: In-DRAM Address Translation to Improve the Spatial</u> <u>Locality of Non-unit Strided Accesses</u> (Seshadri et al., MICRO 2015)

- <u>"Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity</u> <u>DRAM Technology</u>" (Seshadri et al., MICRO 2017)

#### SAFARI

## Starting Simple: Data Copy and Initialization

memmove & memcpy: 5% cycles in Google's datacenter [Kanev+ ISCA'15]

## VM Cloning Deduplication

Many more

## Page Migration

Today's Systems: Bulk Data Copy

Future Systems: In-Memory Copy

## RowClone: In-DRAM Row Copy

Data Bus

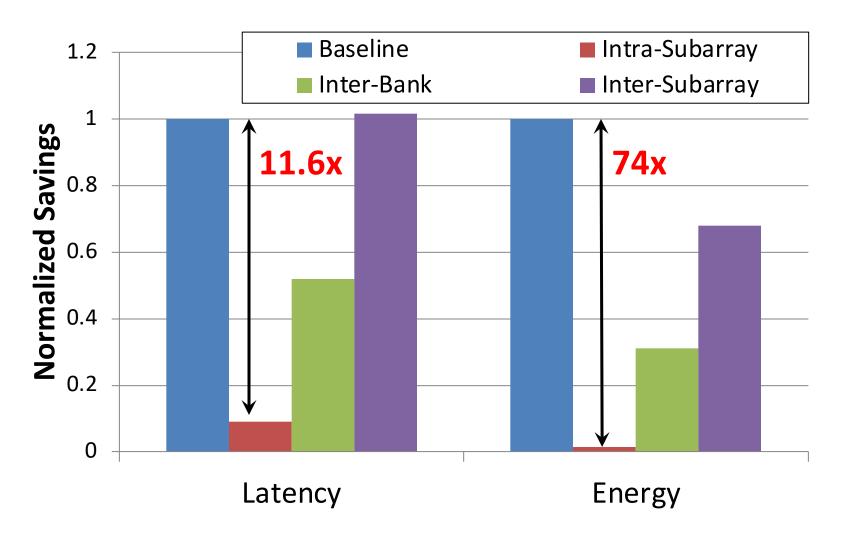

## RowClone: Latency and Energy Savings

Seshadri et al., "RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data," MICRO 2013.

### More on RowClone

Vivek Seshadri, Yoongu Kim, Chris Fallin, Donghyuk Lee, Rachata Ausavarungnirun, Gennady Pekhimenko, Yixin Luo, Onur Mutlu, Michael A. Kozuch, Phillip B. Gibbons, and Todd C. Mowry,

"RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization" Proceedings of the <u>46th International Symposium on Microarchitecture</u>

(*MICRO*), Davis, CA, December 2013. [<u>Slides (pptx) (pdf)</u>] [<u>Lightning Session</u> <u>Slides (pptx) (pdf)</u>] [<u>Poster (pptx) (pdf)</u>]

#### RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization

Vivek Seshadri Yoongu Kim Chris Fallin\* Donghyuk Lee vseshadr@cs.cmu.edu yoongukim@cmu.edu cfallin@c1f.net donghyuk1@cmu.edu Rachata Ausavarungnirun Gennady Pekhimenko Yixin Luo rachata@cmu.edu gpekhime@cs.cmu.edu yixinluo@andrew.cmu.edu Onur Mutlu Phillip B. Gibbons<sup>†</sup> Michael A. Kozuch<sup>†</sup> Todd C. Mowry onur@cmu.edu phillip.b.gibbons@intel.com michael.a.kozuch@intel.com tcm@cs.cmu.edu Carnegie Mellon University <sup>†</sup>Intel Pittsburgh

## Memory as an Accelerator

#### Memory similar to a "conventional" accelerator

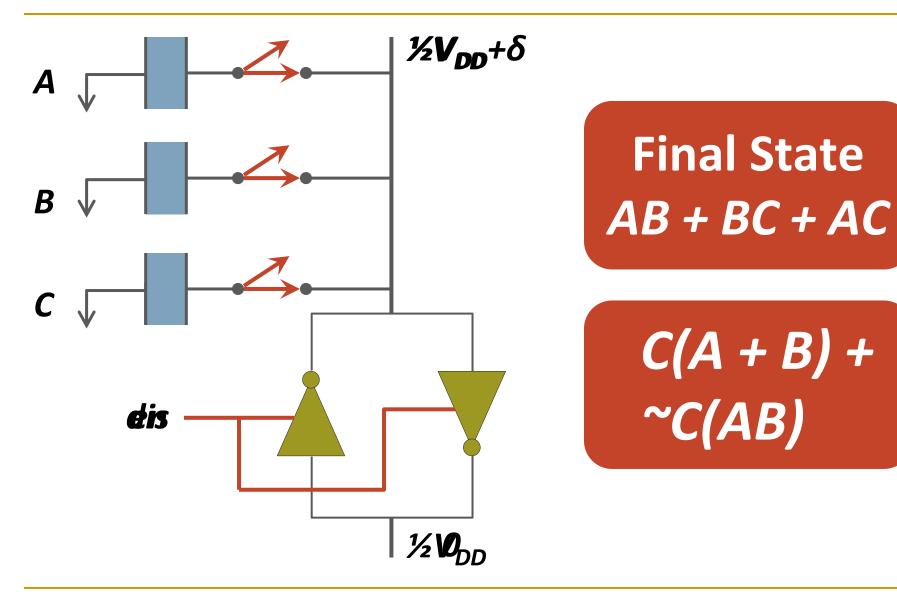

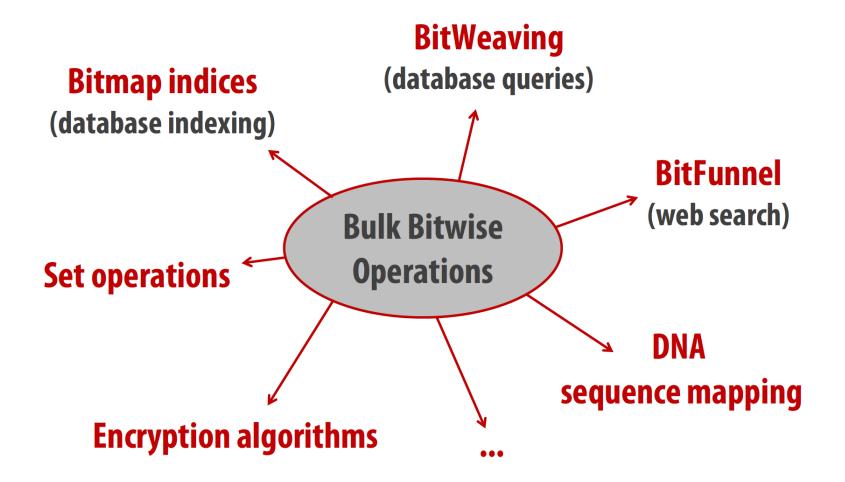

## In-Memory Bulk Bitwise Operations

- We can support in-DRAM COPY, ZERO, AND, OR, NOT, MAJ

- At low cost

- Using analog computation capability of DRAM

- Idea: activating multiple rows performs computation

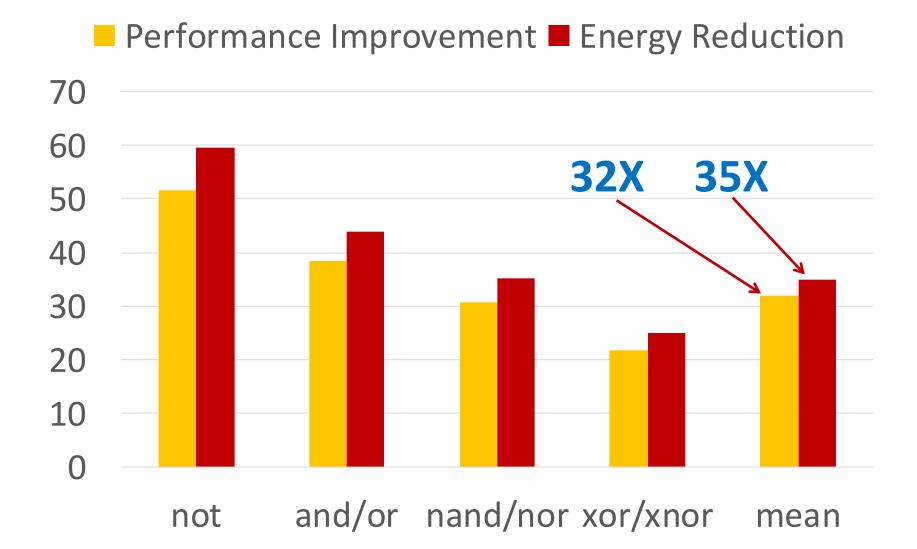

- 30-60X performance and energy improvement

- Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology," MICRO 2017.

- New memory technologies enable even more opportunities

- Memristors, resistive RAM, phase change mem, STT-MRAM, ...

- Can operate on data with minimal movement

## In-DRAM AND/OR: Triple Row Activation

Seshadri+, "Fast Bulk Bitwise AND and OR in DRAM", IEEE CAL 2015.

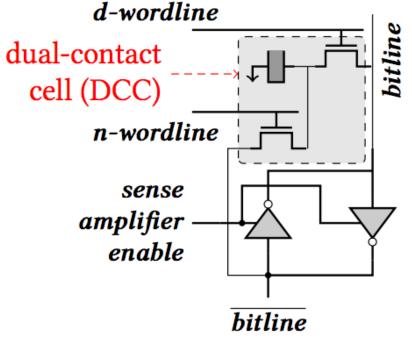

## In-DRAM NOT: Dual Contact Cell

Figure 5: A dual-contact cell connected to both ends of a sense amplifier Idea: Feed the negated value in the sense amplifier into a special row

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

## Ambit vs. DDR3: Performance and Energy

## Bulk Bitwise Operations in Workloads

[1] Li and Patel, BitWeaving, SIGMOD 2013[2] Goodwin+, BitFunnel, SIGIR 2017

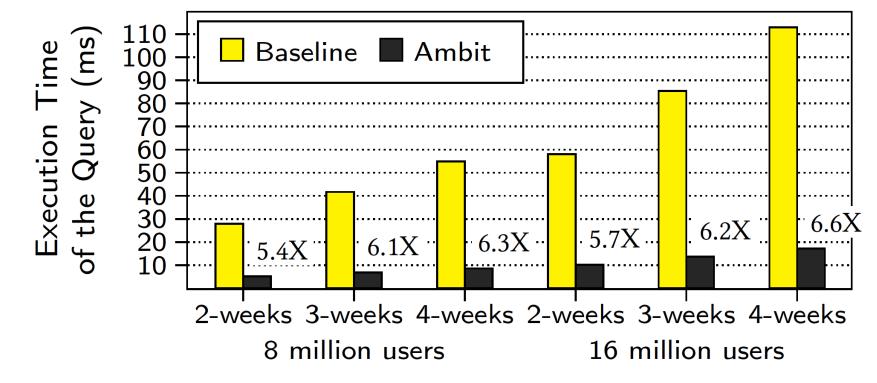

## Performance: Bitmap Index on Ambit

Figure 10: Bitmap index performance. The value above each bar indicates the reduction in execution time due to Ambit.

**>5.4-6.6X Performance Improvement**

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

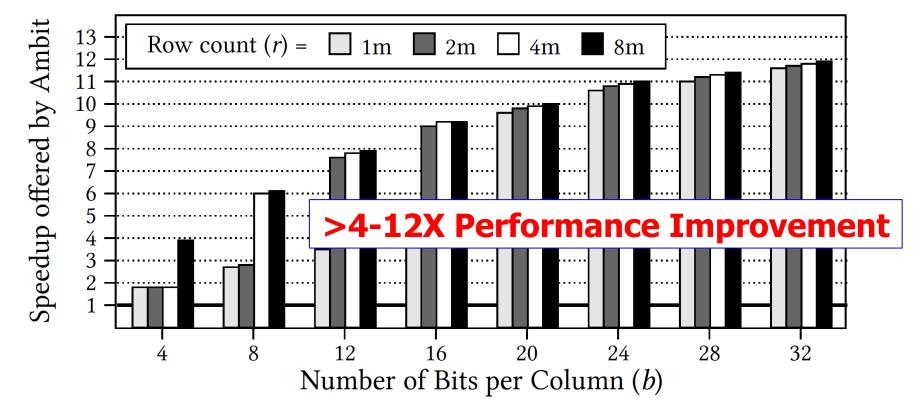

## Performance: BitWeaving on Ambit

#### `select count(\*) from T where c1 <= val <= c2`</pre>

## Figure 11: Speedup offered by Ambit over baseline CPU with SIMD for BitWeaving

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

### More on Ambit

Vivek Seshadri et al., "<u>Ambit: In-Memory Accelerator</u> for Bulk Bitwise Operations Using Commodity DRAM <u>Technology</u>," MICRO 2017.

#### Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology

Vivek Seshadri<sup>1,5</sup> Donghyuk Lee<sup>2,5</sup> Thomas Mullins<sup>3,5</sup> Hasan Hassan<sup>4</sup> Amirali Boroumand<sup>5</sup> Jeremie Kim<sup>4,5</sup> Michael A. Kozuch<sup>3</sup> Onur Mutlu<sup>4,5</sup> Phillip B. Gibbons<sup>5</sup> Todd C. Mowry<sup>5</sup>

<sup>1</sup>Microsoft Research India <sup>2</sup>NVIDIA Research <sup>3</sup>Intel <sup>4</sup>ETH Zürich <sup>5</sup>Carnegie Mellon University

### In-DRAM Bulk Bitwise Execution

Vivek Seshadri and Onur Mutlu,

<u>"In-DRAM Bulk Bitwise Execution Engine"</u> *Invited Book Chapter in Advances in Computers*, to appear in 2020.

[Preliminary arXiv version]

#### In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu ETH Zürich onur.mutlu@inf.ethz.ch

## Sounds Good, No?

## **Review from ISCA 2016**

Paper summary

- The paper proposes to extend DRAM to include bulk, bit-wise logical

- operations directly between rows within the DRAM.

Strengths

- Very clever/novel idea.

- Great potential speedup and efficiency gains.

#### Weaknesses

- Probably won't ever be built. Not practical to assume DRAM manufacturers with change DRAM in this way.

#### **Another Review from ISCA 2016**

**Strengths**

The proposed mechanisms effectively exploit the operation of the DRAM to perform efficient bitwise operations across entire rows of the DRAM.

Weaknesses

This requires a modification to the DRAM that will only help this type of bitwise operation. It seems unlikely that something like that will be adopted.

## Yet Another Review

#### Yet Another Review from ISCA 2016

- Weaknesses

- The core novelty of Buddy RAM is almost all circuits-related (by exploiting sense amps). I do not find architectural innovation even though the circuits technique benefits architecturally by mitigating memory bandwidth and relieving cache resources within a subarray. The only related part is the new ISA support for bitwise operations at DRAM side and its induced issue on cache coherence.

#### **Acknowle** gments

We thank the reviewers of ISCA 2016/2017, MICRO 2016/2017, and HPCA 2017 for their valuable comments. We

- There are many other similar examples from reviews...

For many other papers...

- And, we are not even talking about JEDEC yet...

- How do we fix the mindset problem?

- By doing more research, education, implementation in alternative processing paradigms

#### We need to work on enabling the better future...

# We Need to Fix the Reviewer Accountability Problem

# Main Memory Needs Intelligent Controllers

# Our Community Needs Accountable Reviewers

#### ComputeDRAM: In-Memory Compute Using Off-the-Shelf DRAMs

Fei Gao feig@princeton.edu Department of Electrical Engineering Princeton University Georgios Tziantzioulis georgios.tziantzioulis@princeton.edu Department of Electrical Engineering Princeton University David Wentzlaff wentzlaf@princeton.edu Department of Electrical Engineering Princeton University

#### SAFARI

https://parallel.princeton.edu/papers/micro19-gao.pdf

#### Pinatubo: A Processing-in-Memory Architecture for Bulk Bitwise Operations in Emerging Non-volatile Memories

Shuangchen Li<sup>1</sup>; Cong Xu<sup>2</sup>, Qiaosha Zou<sup>1,5</sup>, Jishen Zhao<sup>3</sup>, Yu Lu<sup>4</sup>, and Yuan Xie<sup>1</sup>

University of California, Santa Barbara<sup>1</sup>, Hewlett Packard Labs<sup>2</sup> University of California, Santa Cruz<sup>3</sup>, Qualcomm Inc.<sup>4</sup>, Huawei Technologies Inc.<sup>5</sup> {shuangchenli, yuanxie}ece.ucsb.edu<sup>1</sup>

### Aside: A Recommended Book

#### WILEY PROFESSIONAL COMPUTING

Raj Jain

#### THE ART OF COMPUTER SYSTEMS PERFORMANCE ANALYSIS

Techniques for Experimental Design, Measurement, Simulation, and Modeling

WILEY

Raj Jain, "The Art of Computer Systems Performance Analysis," Wiley, 1991.

DECISION MAKER'S GAMES

161

#### . DECISION MAKER'S GAMES

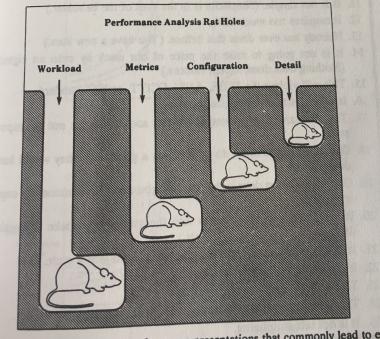

Even if the performance analysis is correctly done and presented, it may not be enough to persuade your audience—the decision makers—to follow your recommendations. The list shown in Box 10.2 is a compilation of reasons for rejection heard at various performance analysis presentations. You can use the list by presenting it immediately and pointing out that the reason for rejection is not new and that the analysis deserves more consideration. Also, the list is helpful in getting the competing proposals rejected!

There is no clear end of an analysis. Any analysis can be rejected simply on the grounds that the problem needs more analysis. This is the first reason listed in Box 10.2. The second most common reason for rejection of an analysis and for endless debate is the workload. Since workloads are always based on the past measurements, their applicability to the current or future environment can always be questioned. Actually workload is one of the four areas of discussion that lead a performance presentation into an endless debate. These "rat holes" and their relative sizes in terms of time consumed are shown in Figure 10.26. Presenting this cartoon at the beginning of a presentation helps to avoid these areas.

FIGURE 10.26 Four issues in performance presentations that commonly lead to endless discussion. Raj Jain, "The Art of Computer Systems Performance Analysis," Wiley, 1991.

| <ul> <li>Box 10.2 (Relative understanding of the workload.</li> <li>You need a better understanding of the workload.</li> <li>It improves performance only for long I/O's, packets, jobs, and files, and most of the I/O's, packets, jobs, and files, but who cares for the performance of short I/O's, packets, jobs, and files, its the long ones that impact the system.</li> <li>It needs too much memory/CPU/bandwidth and memory/CPU/band. width isn't free.</li> <li>It needs too much memory/CPU/bandwidth and memory/CPU/band. width is cheap.</li> <li>There is no point in making the networks (similarly, CPUs/disky/) faster; our CPUs/disks (any component other than the one being discussed) aren't fast enough to use them.</li> <li>It improves the performance by a factor of x, but it doesn't really matter at the user level because everything else is so slow.</li> <li>It is going to increase the complexity and cost.</li> <li>Let us keep it simple stupid (and your idea is not stupid).</li> <li>It is not simple. (Simplicity is in the eyes of the beholder.)</li> <li>It requires too much state.</li> <li>Nobody has ever done that before. (You have a new idea.)</li> <li>It is not going to raise the price of our stock by even an eighth. (Nothing ever does, except rumors.)</li> <li>This will violate the IEEE, ANSI, CCITT, or ISO standard.</li> <li>It may violate some future standard.</li> <li>Our competition does it this way and you don't make money by copping others.</li> <li>It will introduce randomness into the system and make debuggit difficult.</li> <li>It is too deterministic; it may lead the system into a cycle.</li> <li>It's not interoperable.</li> <li>This impacts hardware.</li> <li>Why to have a the system into a cycle.</li> <li>We have a bardware.</li> <li>Why to have a bardware.</li> </ul> | B   | Box 10.2 Reasons for Not Accepting the Results of an Analysis          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------|

| <ol> <li>You need a better marce only for long I/O's, packets, jobs, and files,<br/>and most of the I/O's, packets, jobs, and files are short.<br/>and most of the I/O's, packets, jobs, and files, jobs, and files,<br/>but who cares for the performance of short I/O's, packets, jobs, and files,<br/>but who cares for the performance of short I/O's, packets, jobs, and<br/>files; its the long ones that impact the system.</li> <li>It needs too much memory/CPU/bandwidth and memory/CPU/band.<br/>width isn't free.</li> <li>It only saves us memory/CPU/bandwidth and memory/CPU/band.<br/>width is cheap.</li> <li>There is no point in making the networks (similarly, CPUs/disks/)<br/>faster; our CPUs/disks (any component other than the one being dis<br/>cussed) aren't fast enough to use them.</li> <li>It improves the performance by a factor of x, but it doesn't really<br/>matter at the user level because everything else is so slow.</li> <li>It is going to increase the complexity and cost.</li> <li>Let us keep it simple stupid (and your idea is not stupid).</li> <li>It is not simple. (Simplicity is in the eyes of the beholder.)</li> <li>It requires too much state.</li> <li>Nobody has ever done that before. (You have a new idea.)</li> <li>It is not going to raise the price of our stock by even an eighth.<br/>(Nothing ever does, except rumors.)</li> <li>This will violate the IEEE, ANSI, CCITT, or ISO standard.</li> <li>It may violate some future standard.</li> <li>The standard says nothing about this and so it must not be import<br/>tant.</li> <li>Our competition does it this way and you don't make money by copping others.</li> <li>It will introduce randomness into the system and make debuggin<br/>difficult.</li> <li>It is too deterministic; it may lead the system into a cycle.</li> <li>It's not interoperable.</li> <li>This impacts hardware.</li> <li>This impacts hardware.</li> </ol>                                                                                     | 100 | 1. This needs more analysis                                            |

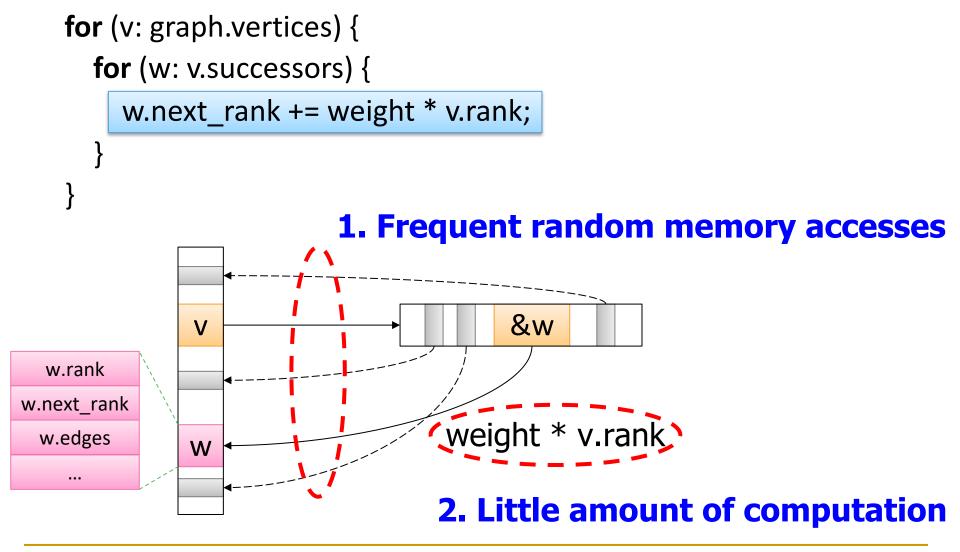

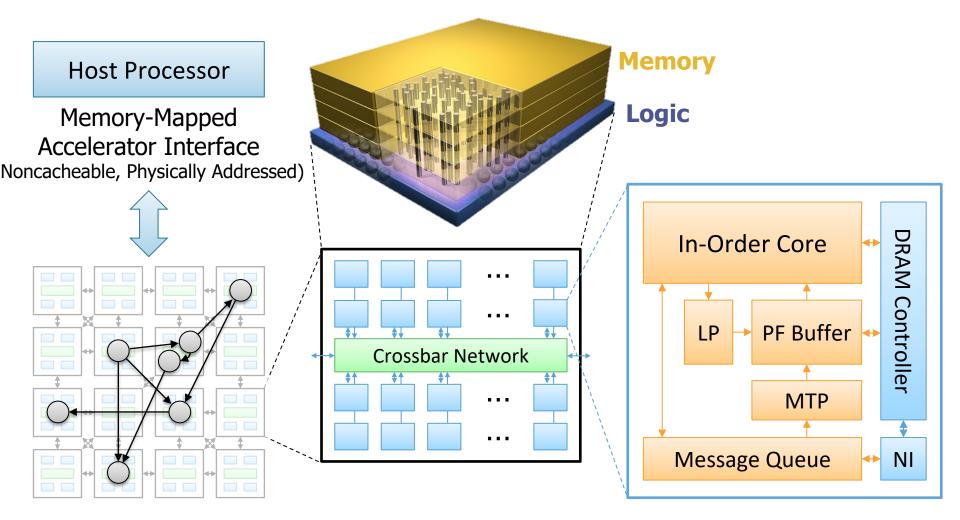

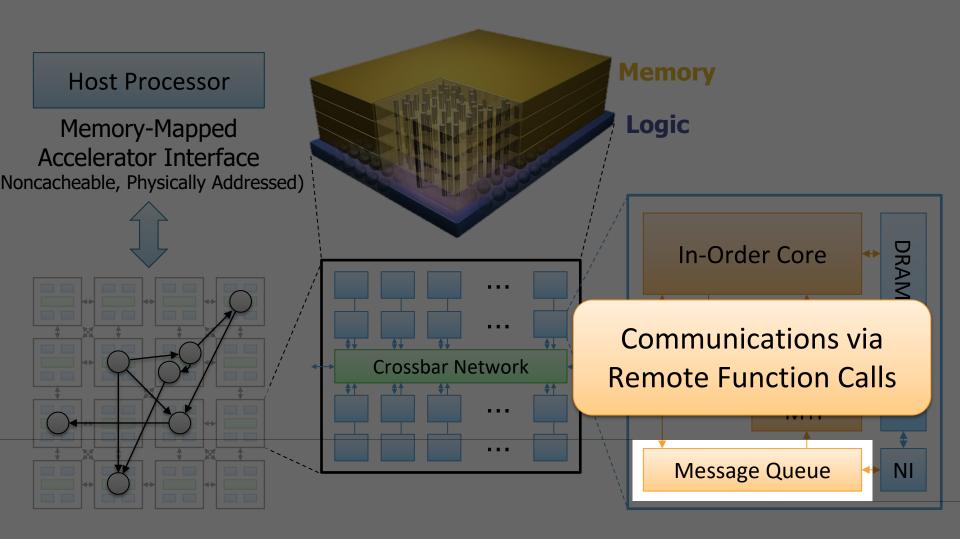

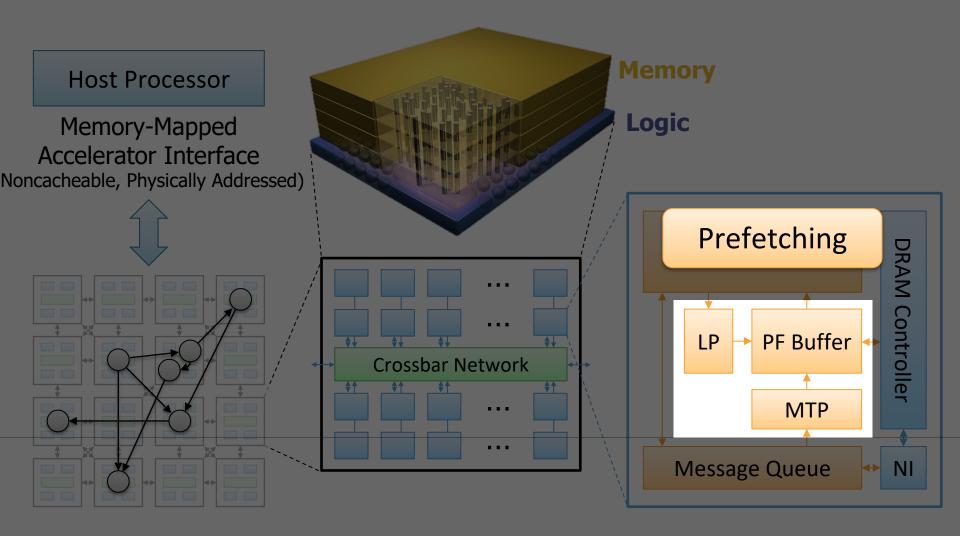

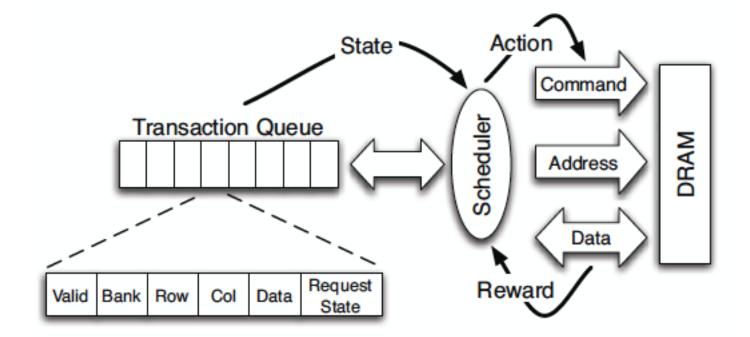

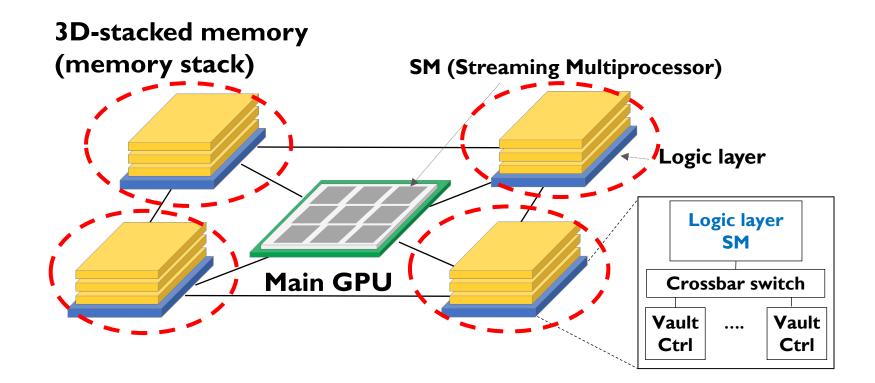

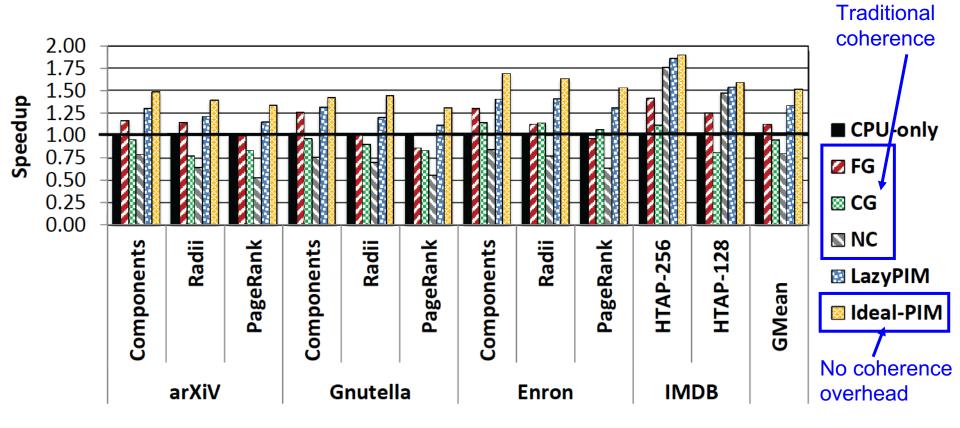

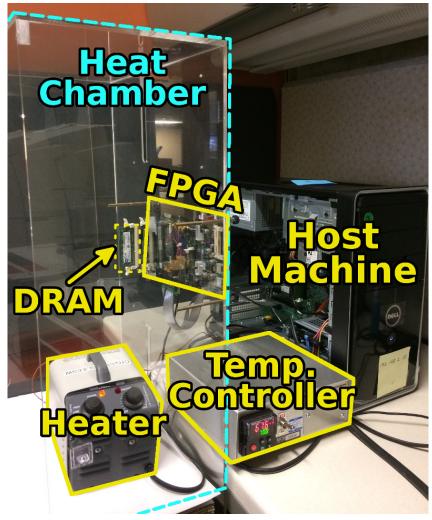

| <ul> <li>and more performance only for short I/O's, packets, jobs, and files, but who cares for the performance of short I/O's, packets, jobs, and files, its the long ones that impact the system.</li> <li>5. It needs too much memory/CPU/bandwidth and memory/CPU/band, width isn't free.</li> <li>6. It only saves us memory/CPU/bandwidth and memory/CPU/band, width is cheap.</li> <li>7. There is no point in making the networks (similarly, CPUs/disks/) faster; our CPUs/disks (any component other than the one being discussed) aren't fast enough to use them.</li> <li>8. It improves the performance by a factor of x, but it doesn't really matter at the user level because everything else is so slow.</li> <li>9. It is going to increase the complexity and cost.</li> <li>10. Let us keep it simple stupid (and your idea is not stupid).</li> <li>11. It is not simple. (Simplicity is in the eyes of the beholder.)</li> <li>12. It requires too much state.</li> <li>13. Nobody has ever done that before. (You have a new idea.)</li> <li>14. It is not going to raise the price of our stock by even an eighth. (Nothing ever does, except rumors.)</li> <li>15. This will violate the IEEE, ANSI, CCITT, or ISO standard.</li> <li>16. It may violate some future standard.</li> <li>17. The standard says nothing about this and so it must not be important.</li> <li>18. Our competition does it this way and you don't make money by coping others.</li> <li>20. It will introduce randomness into the system and make debugglid difficult.</li> <li>21. It is to deterministic; it may lead the system into a cycle.</li> <li>22. It's not interoperable.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |     | 2. You need a better under only for long I/O's, packets in             |