Heterogeneous stream processor

The core project was done in collaboration with two bachelor students:

Georg Teufelberger (Master Thesis, ETH Zurich) and Neil Stern (Bachelor Thesis, ETH Zurich), who made great contribution to the project’s infrastructure!

I am also grateful to Andrea Lattuada for extremely helpful feedback and discussions about the functionality of Timely Dataflow.

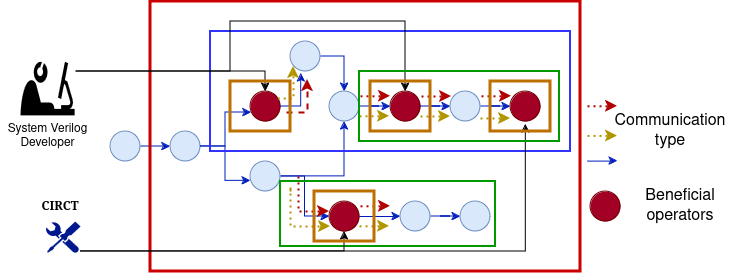

This project aims to expand possibilities of exisitng stream processors in heterogeneous environment:

- What are the abstractions necessary to introduce heterogeneity inside a system?

- How can we enable different batch sizes and not loos performance?

- How do we distribute load?

This project first tackles the problem of not supporting small batches in heterogeneous environment

GitHub Timely Dataflow on FPGA is the mirror of the project for Timely on FPGA. This version was tested only with Xilinx DMA subsystem IP or with Enzian cache coherent interconnect.

There exists a separate version that was tested with an ealier Xilinx SDAccel toolchain for OpenCL-based offloading, but it is not publicly published.

The repository contains branches with asynchronous mode, synchronous mode and different test graphs, and the currently supported branch timely_together which is a synchronous mode for different data transfer sizes and single-threaded execution.

The support for multi-threaded execution is coming soon!

Interconnect competition and Inverse problem will address other parts of this diagram.

The FPGA part of this project is not open source yet.