# Enzian: a Research Computer

Timothy Roscoe, David Cock Systems Group ETH Zurich Department of Computer Science

#### What This Talk is About

- The challenge of relevant academic systems software research in an age of custom and reconfigurable hardware.

- Our response: build a computer designed for academic research

- A variety of use-cases

- Methodological issues and wider ramifications

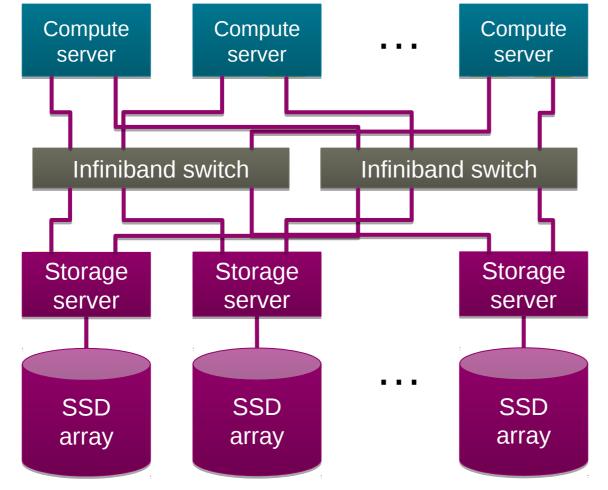

# Typical Rack-Scale Architecture (in research, at least)

FDR ~ 56Gb/s

- Q. Message latency in this network?

- A.  $\sim 0.7 \mu s$ , or  $\sim 10$  LLC misses.

- ⇒ need to think of this as *one big machine*

# But it's not typical!

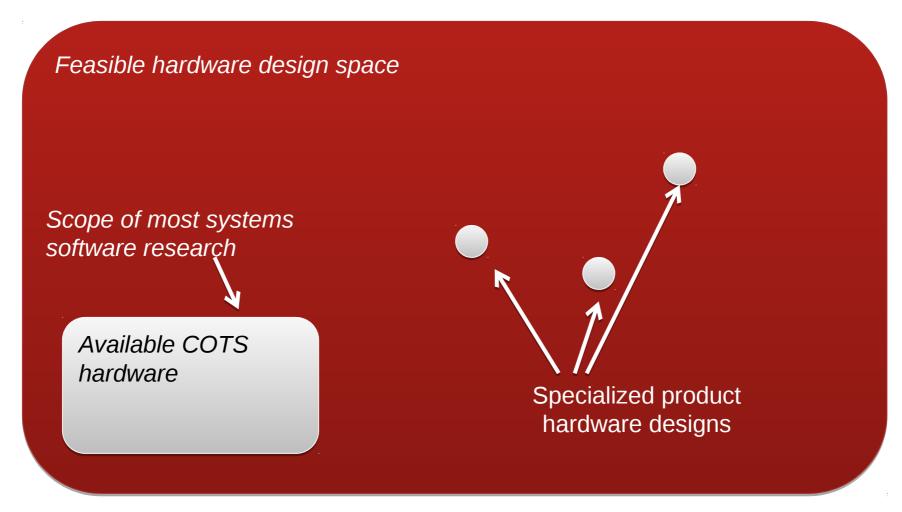

#### The Challenge for Systems Software Research

#### Challenges

#### Challenge 1: Getting the hardware

- Often developed by \*aaS companies

- Fear of support costs

#### Challenge 2: Getting the documentation

- Documentation non-existent or proprietary

- Lending is legally easier than releasing documentation

# Challenge 3: The big decisions have already been made

- Custom hardware is built with an application and mode of use already in mind

- Hardware probably never tested outside a narrow envelope

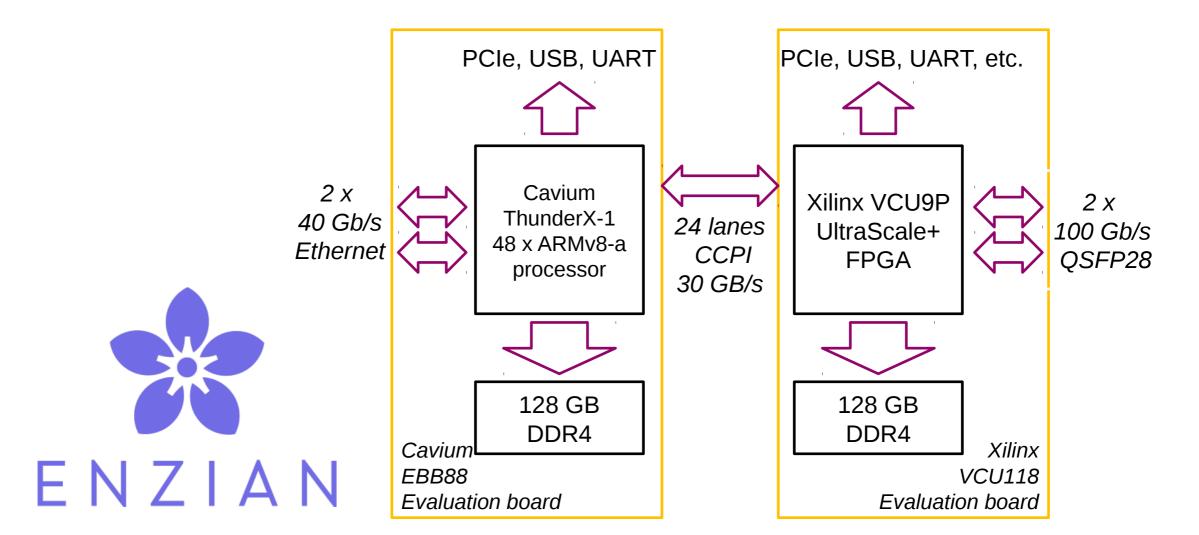

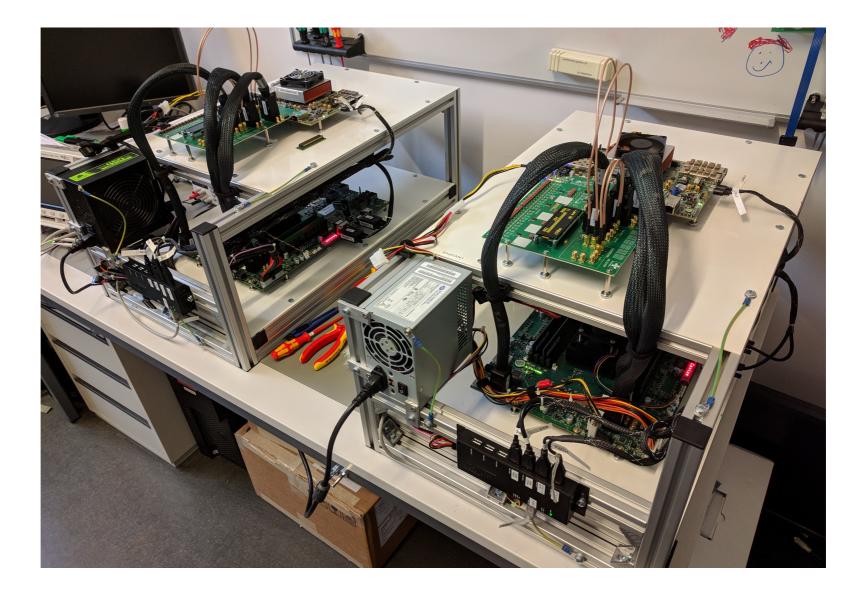

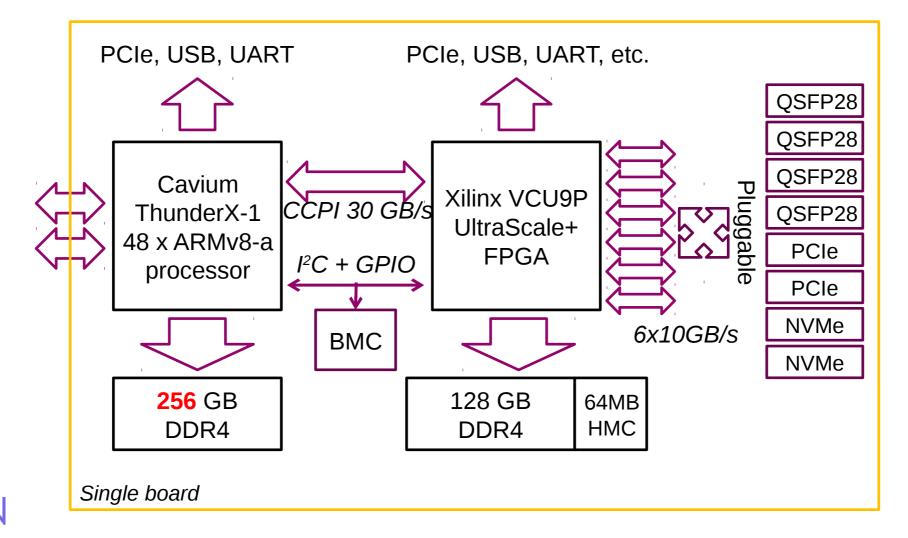

#### Enzian v2

#### Enzian v2

#### Enzian v2

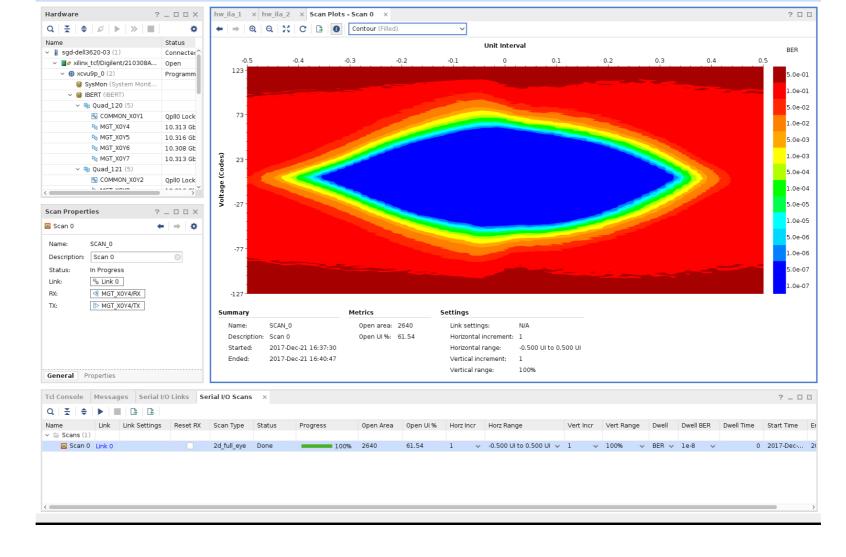

HARDWARE MANAGER - sgd-dell3620-03/xilinx tcf/Digilent/210308A1C4D7

? X

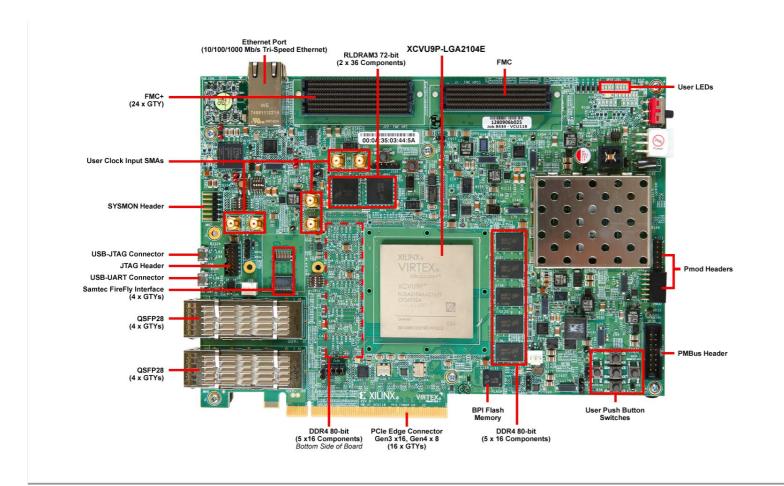

# Enzian v3 (2018, Design Contract Awarded)

# RESEARCH APPLICATIONS (THAT WE'VE THOUGHT OF)

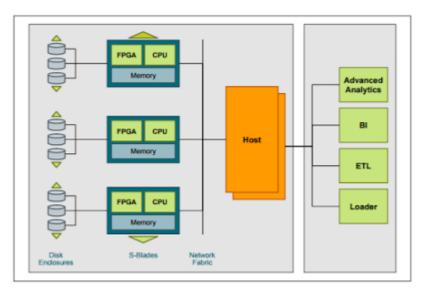

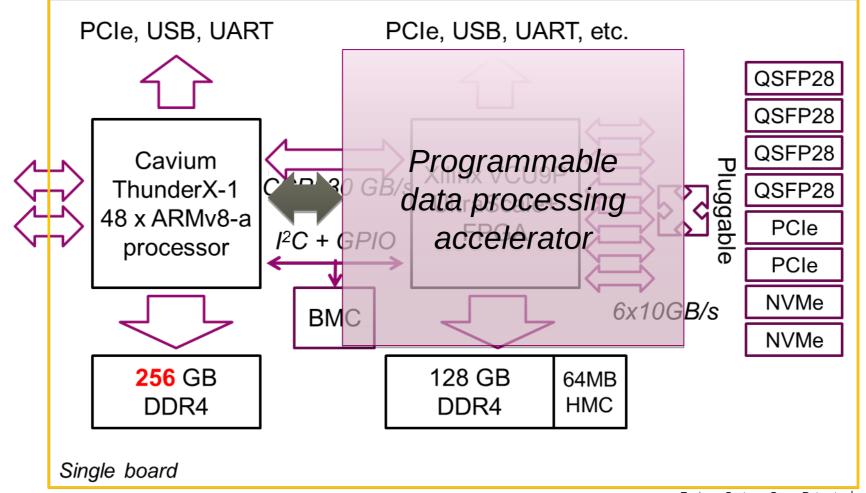

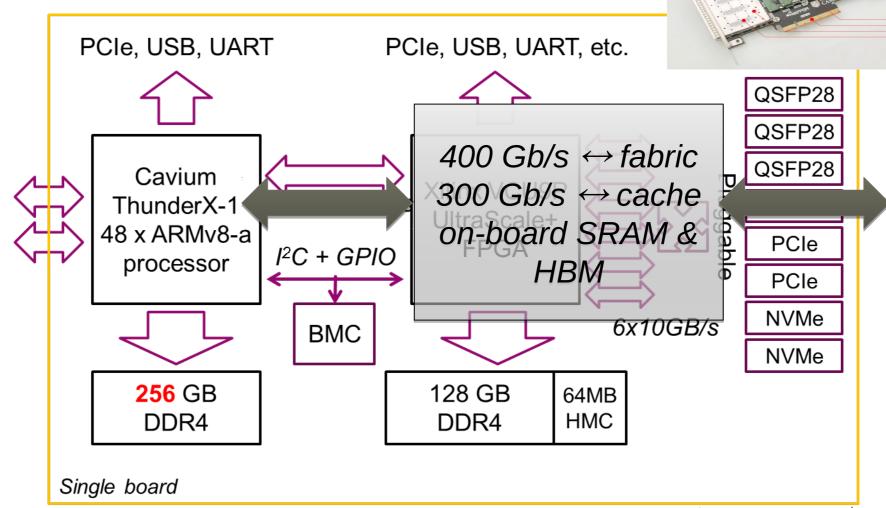

#### **Accelerator Design**

#### The Next NetFPGA

ETH Zurich

#### **Remote Memory**

| 14

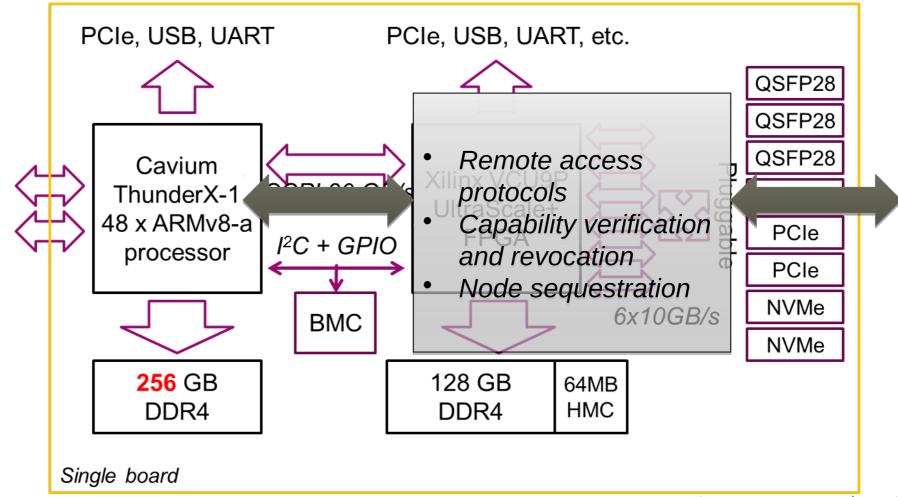

# **POSSIBLE IMPLICATIONS**

#### **Claiming Validity**

- 1. This *is* the platform

- Why is this platform a valid design point?

- How to meaningfully compare with others?

- 2. Emulating a *possible new* platform design

- What would this mean if built from scratch?

- What is the cost/benefit?

#### **Methodological Questions**

- Application use-cases, e.g.:

- NFV applications & control/data plane design

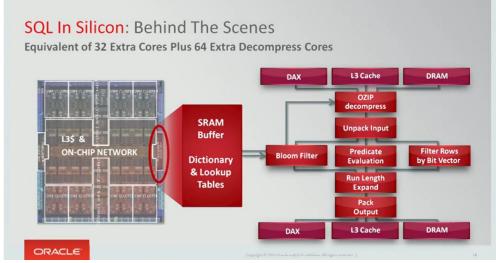

- Database design exploiting hardware accelerators

- Systems use-cases, e.g.:

- Accelerator interface design

- OS support for closely-coupled FPGAs

#### **Higher Goal: Research Amplification**

- Seed the research community

- Remove major barrier to innovation in academia

- Precedents:

- PlanetLab

- Berkeley Unix

- NetFPGA

- Intel's DPDK

- •

#### **Summary: COTS Hardware is Unrealistic**

- All the product action uses custom hardware

- Vendors can build almost anything

- What to build is an economic question

- ⇒ not something we can answer

- We needs overengineered research platforms

- Our goal should be to deliver options and techniques

# **Questions?**

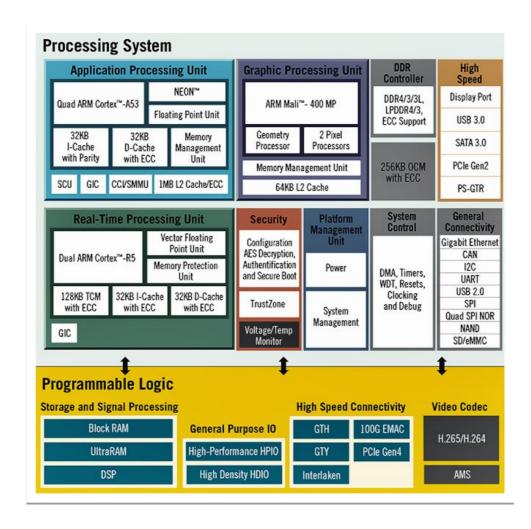

#### Xilinx Ultrascale+ MPSoC

#### **Evaluation Boards**

Can't take fullsystem approach

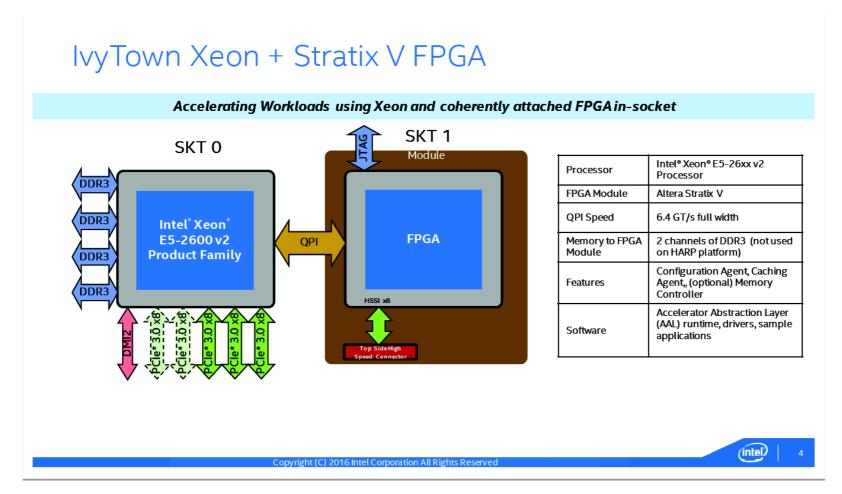

#### **Intel HARP Program**