# MODELING OF CONDITIONAL INDEX CHANGES

by

Matthias Krebs

A Thesis Submitted to the Faculty of the

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

In Partial Fulfillment of the Requirements For the Degree of

MASTER OF SCIENCE

In the Graduate College

THE UNIVERSITY OF ARIZONA

$1 \ 9 \ 9 \ 7$

## STATEMENT BY AUTHOR

This thesis has been submitted in partial fulfillment of requirements for an advanced degree at The University of Arizona and is deposited in the University Library to be made available to borrowers under rules of the Library.

Brief quotations from this thesis are allowable without special permission, provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the head of the Department of Electrical and Computer Engineering or the Dean of the Graduate College when in his or her judgment the proposed use of the material is in the interest of scholarship. In all other instances, however, permission must be obtained by the author.

SIGNED: Matthias Kels

## APPROVAL BY THESIS DIRECTOR

This thesis has been approved on the date shown below:

Such = . (e)

Dr. François E. Cellier Professor of Electrical and Computer Engineering

Date

# **ACKNOWLEDGMENTS**

I would like to thank my advisor, Professor François E. Cellier, for his great support, guidance, and encouragement throughout this thesis. This degree would have been impossible for me without his support. His willingness to spend so many hours in the lab working on the completion of this project was greatly appreciated. I am truly fortunate to have worked on a project with such an extremely knowledgeable and helpful individual. Furthermore I am deeply grateful for the possibility to hear his courses that extended my knowledge in an extraordinary way.

# TABLE OF CONTENTS

| LIS           | о та | F FIG  | URES                                                  | 8  |

|---------------|------|--------|-------------------------------------------------------|----|

| LIS           | о тб | F TAI  | BLES                                                  | 11 |

| $\mathbf{AB}$ | STR  | ACT    |                                                       | 12 |

| $\mathbf{PR}$ | EFA  | CE     |                                                       | 13 |

| 1.            | Intr | oducti | on                                                    | 14 |

|               | 1.1. | The P  | roblem Statement                                      | 14 |

|               | 1.2. | Basic  | Concepts                                              | 14 |

|               |      | 1.2.1. | Model Descriptions                                    | 16 |

|               |      |        |                                                       | 16 |

|               |      |        | - J <b>1</b> J (- )                                   | 17 |

|               |      | 1.2.2. |                                                       | 18 |

|               |      |        |                                                       | 18 |

|               |      |        | 0 1                                                   | 19 |

|               |      | 1.2.3. | 0 1 1                                                 | 21 |

|               |      |        |                                                       | 21 |

|               |      |        | 0                                                     | 22 |

|               |      |        | 0                                                     | 26 |

|               | 1.3. | Switch | Elements                                              | 26 |

| <b>2.</b>     | Gra  | phical | Tools and Representations Used Throughout This Thesis | 41 |

|               | 2.1. | Graph  | ical Modeling Tools                                   | 42 |

|               |      | 2.1.1. | Bond Graphs                                           | 42 |

|               |      |        | 2.1.1.1. Bond Graph Modeling                          | 42 |

|               |      |        | 2.1.1.2. Bond Graph Causality                         | 46 |

|               | 2.2. | Graph  | ical Methods to Represent Algebraic Structures        | 51 |

|               |      | 2.2.1. | Bipartite Graphs                                      | 52 |

|               |      | 2.2.2. | Dependence Graphs                                     | 54 |

|               |      | 2.2.3. | 1 I                                                   | 55 |

|               |      | 2.2.4. | Modified Dependence Graphs for Time Derivatives       | 57 |

| 3. First Unsuccessful Attempts at Solving the Problem |      |                                                                                          |     |

|-------------------------------------------------------|------|------------------------------------------------------------------------------------------|-----|

|                                                       | 3.1. | The Example Circuit                                                                      | 59  |

|                                                       |      | 3.1.1. Bond Graph Causalities for the Example Circuit                                    | 61  |

|                                                       |      | 3.1.2. DAE Indices for the Example Circuit                                               | 63  |

|                                                       | 3.2. | The Task to be Accomplished                                                              | 64  |

|                                                       | 3.3. | An Inductive Approach                                                                    | 65  |

|                                                       | 3.4. | The Permutation Approach                                                                 | 65  |

|                                                       | 3.5. | The Direct Approach                                                                      | 67  |

|                                                       |      | 3.5.1. The Two Basic Possibilities                                                       | 75  |

|                                                       |      | 3.5.2. General Considerations About Loops in the Modified Depen-<br>dence Graph Notation | 76  |

|                                                       |      | 3.5.3. Examples for Requirements in Ring Structures                                      | 80  |

| 4.                                                    | Cor  | nditions for the Example Circuit and Conclusions                                         | 86  |

|                                                       | 4.1. | Conditions for Possibility A                                                             | 92  |

|                                                       |      | 4.1.1. Requirements for Loop 2 in Possibility A                                          | 93  |

|                                                       |      | 4.1.2. Conditions for Loop 2 in Possibility A                                            | 94  |

|                                                       |      | 4.1.3. Requirements for Loop 1 in Possibility A                                          | 94  |

|                                                       |      | 4.1.4. Conditions for Loop 1 in Possibility A                                            | 94  |

|                                                       |      | 4.1.5. Result of Combined Conditions for Possibility A                                   | 94  |

|                                                       | 4.2. | Conditions for Possibility B                                                             | 95  |

|                                                       |      | 4.2.1. Requirements for Loop 2 in Possibility B                                          | 96  |

|                                                       |      | 4.2.2. Conditions for Loop 2 in Possibility B                                            | 96  |

|                                                       |      | 4.2.3. Requirements for Loop 1 in Possibility B                                          | 96  |

|                                                       |      | 4.2.4. Conditions for Loop 1 in Possibility B                                            | 99  |

|                                                       |      | 4.2.5. Result of Combined Conditions for Possibility B                                   | 99  |

|                                                       | 4.3. | Verification of the Method                                                               | 99  |

|                                                       |      | 1 1 U                                                                                    | 102 |

|                                                       |      | 1 0                                                                                      | 105 |

|                                                       |      | 4.3.3. Requirements for Both Loops in Possibility B                                      | 107 |

|                                                       |      | 4.3.4. Conditions for Both Loops in Possibility B                                        | 109 |

|                                                       | 4.4. | Conclusions                                                                              | 109 |

| 5.                                                    | The  | . 0                                                                                      | 112 |

|                                                       | 5.1. |                                                                                          | 112 |

|                                                       | 5.2. |                                                                                          | 113 |

|                                                       |      | 5.2.1. The Equation System                                                               | 114 |

|    | 5.2.2. Dependence Graph Considerations                                                                           | 115  |

|----|------------------------------------------------------------------------------------------------------------------|------|

|    | 5.2.3. Determinant and Singular Step Sizes                                                                       | 120  |

|    | 5.2.4. Using the Equation System in a Simulation                                                                 | 123  |

|    | 5.3. Elimination of Restrictions on Bond Graph Causalities for Inductor                                          |      |

|    | and Capacitor Elements                                                                                           | 125  |

|    | 5.3.1. New Possibilities for Assigning Bond Graph Causalities for the                                            |      |

|    | Example Circuit                                                                                                  | 127  |

|    | 5.3.2. Remaining Causality Requirements                                                                          | 128  |

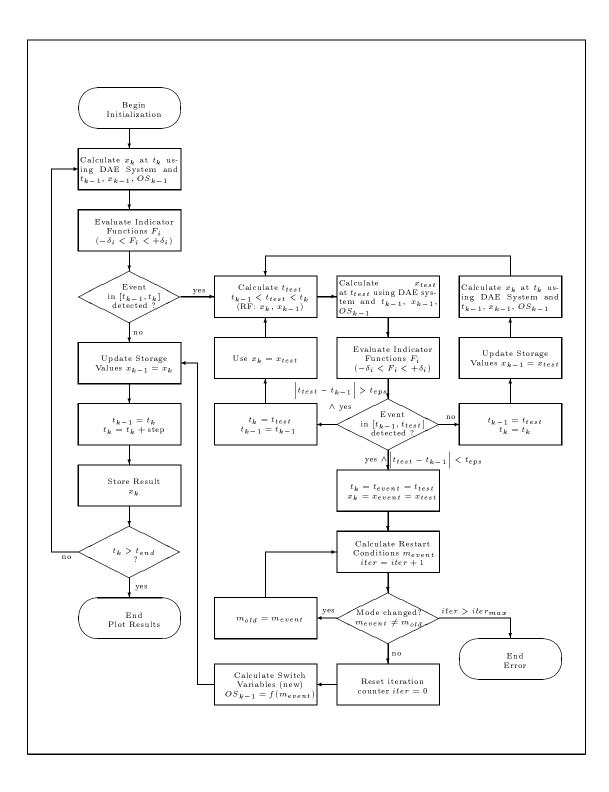

|    | 5.4. Necessary Simulation Steps                                                                                  | 130  |

|    | 5.4.1. Event Detection $\ldots$ | 133  |

|    | 5.4.2. Event Calculation                                                                                         | 135  |

|    | 5.4.3. Evaluating Results of Events                                                                              | 136  |

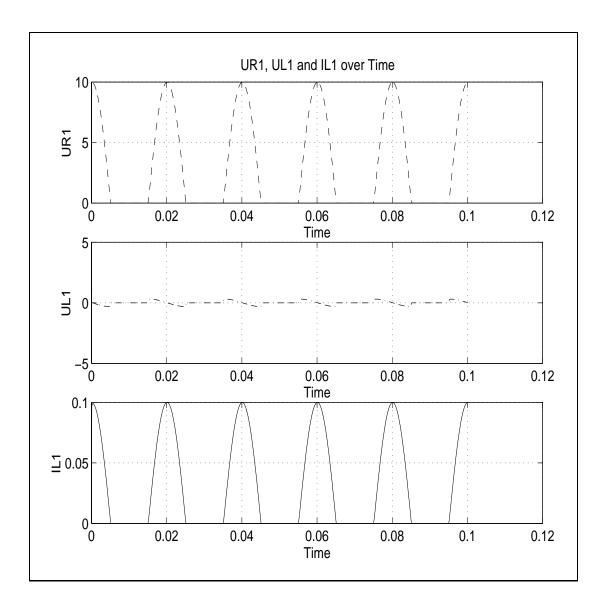

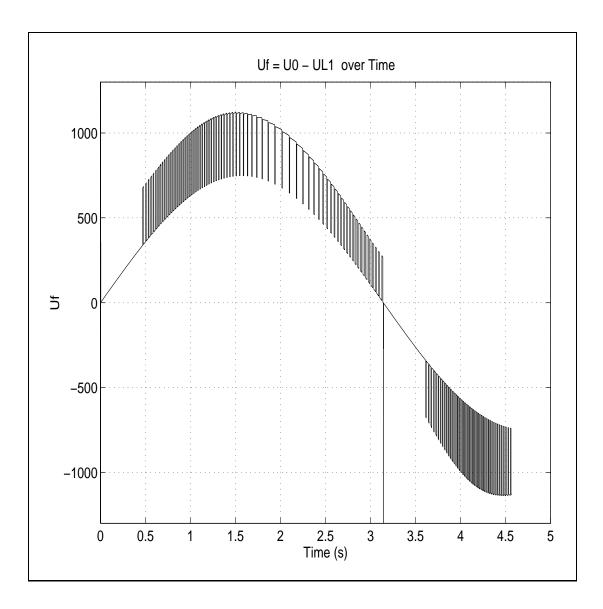

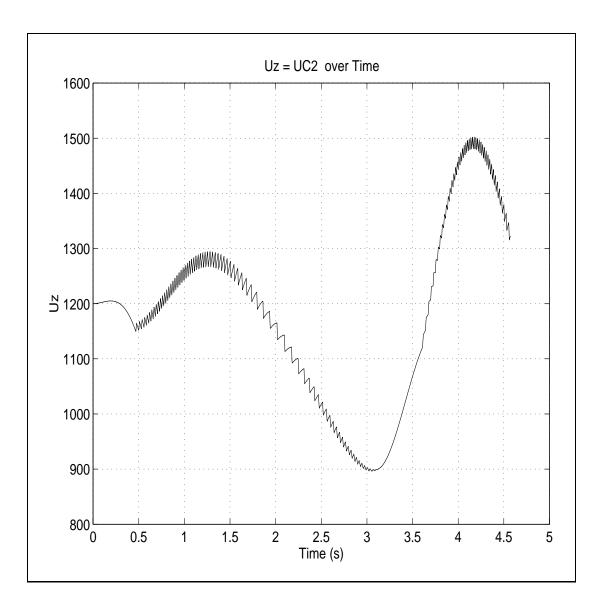

|    | 5.5. Results for the Example Circuit                                                                             | 136  |

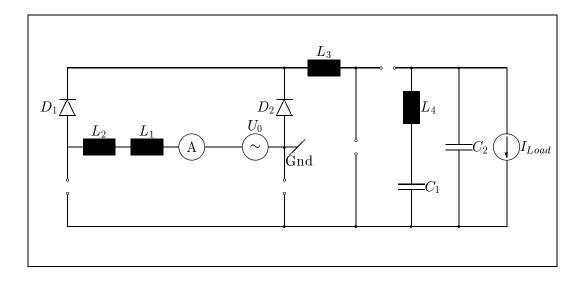

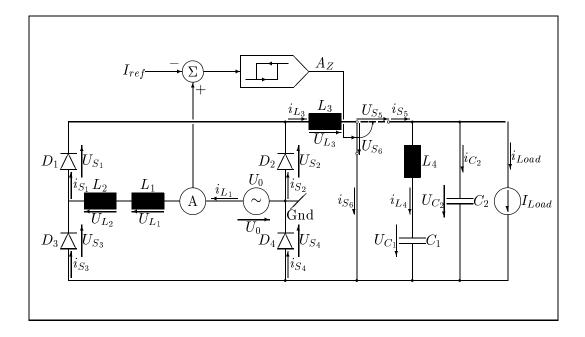

| 6. | The SCR Circuit for Train Speed Control                                                                          | 145  |

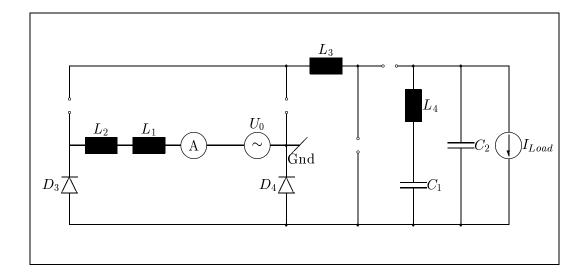

|    | 6.1. Ordinary Two Quadrant Rectifier                                                                             | 145  |

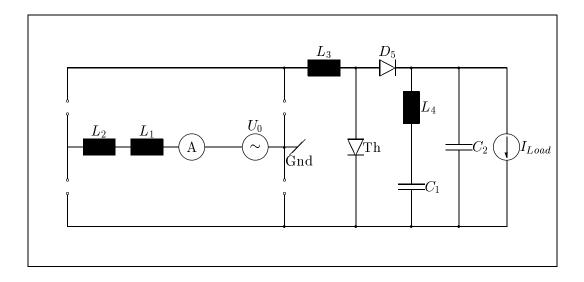

|    | 6.2. The SCR Circuit                                                                                             | 151  |

|    | 6.3. The Equation System                                                                                         | 156  |

|    | 6.3.1. The Cases Causing Singularities                                                                           | 159  |

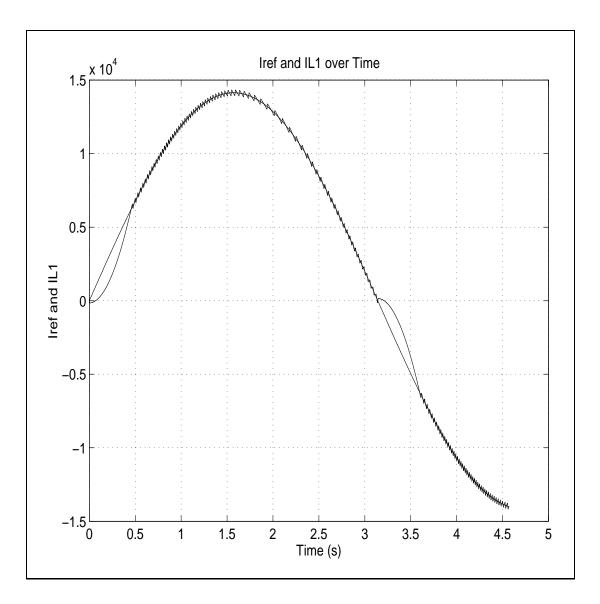

|    | 6.4. Simulation Results                                                                                          | 162  |

| 7. | Discussion                                                                                                       | 167  |

|    | 7.1. Comparison with PSpice                                                                                      | 169  |

|    | 7.2. Issues for Further Research                                                                                 | 169  |

| ЪΓ | EFERENCES                                                                                                        | 1/71 |

| RE |                                                                                                                  | 171  |

# LIST OF FIGURES

| 1.1.  | Example circuit                                  |

|-------|--------------------------------------------------|

| 1.2.  | Higher Index Problem23                           |

| 1.3.  | Switch–Inductor example circuit                  |

| 1.4.  | Half-wave rectifier circuit                      |

| 1.5.  | Ideal Diode Characteristics                      |

| 1.6.  | Inductive load circuit                           |

| 2.1.  | A bond                                           |

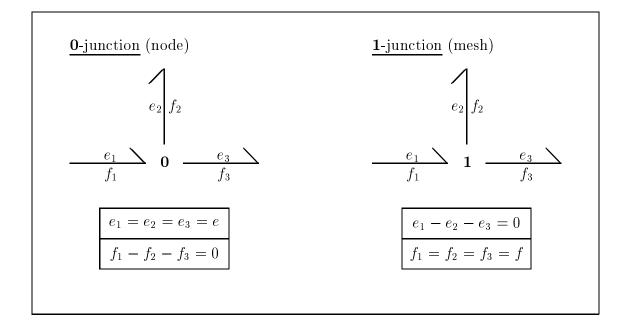

| 2.2.  | Types of Junctions 43                            |

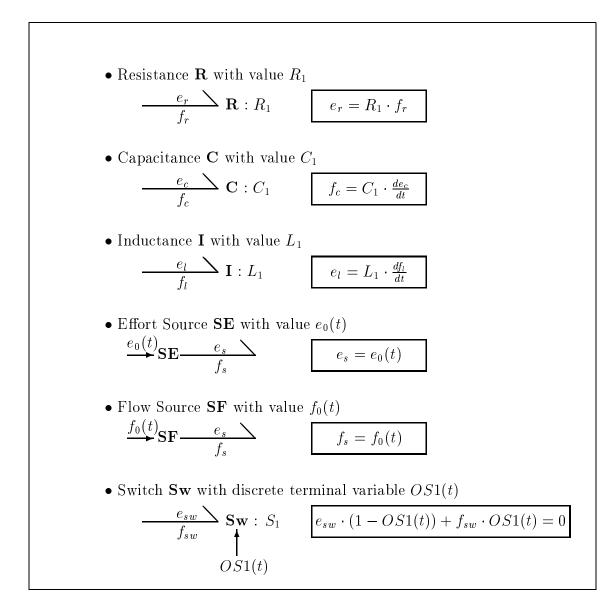

| 2.3.  | Bond Elements for Circuit Theory 45              |

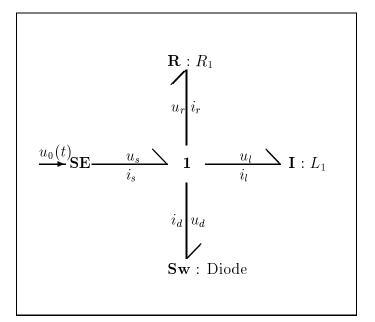

| 2.4.  | Bond Graph Inductive Load 46                     |

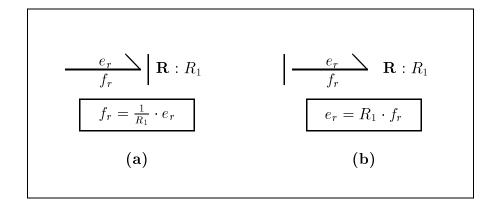

| 2.5.  | Resistor Causalities                             |

| 2.6.  | Required Element Causalities                     |

| 2.7.  | Required Junction Causalities                    |

| 2.8.  | Bond Graph with Causality                        |

| 2.9.  | Bipartite Graph                                  |

| 2.10. | Dependence Graph                                 |

|       | Modified Dependence Graph 56                     |

|       | For Derivatives Modified Dependence Graph        |

| 3.1.  | Detailed example circuit                         |

| 3.2.  | Example 2                                        |

| 3.3.  | Bond Graph Causality (a) for Example 1           |

| 3.4.  | Bond Graph Causality (b) for Example 1           |

| 3.5.  | Detailed Bond Graph for Example 1                |

| 3.6.  | Dependence Graph for Example 1                   |

| 3.7.  | Dependence Graph for $n_1 = n_2 = n_3 = n_4 = 0$ |

| 3.8.  | Dependence Graph Example (a)                     |

| 3.9.  | Dependence Graph Example (b)                     |

| 3.10. | Dependence Graph Example (c)                     |

|       | Dependence Graph Example (d)                     |

|       | Dependence Graph Example (e)                     |

| 4.1.  | Modified Dependence Graph Notation               |

| 4.2. Variable Convention in Modified Dependence Graph | 87  |

|-------------------------------------------------------|-----|

| 4.3. Modified Dependence Graph Possibility A Loop 2   | 93  |

| 4.4. Modified Dependence Graph Possibility A Loop 1   | 95  |

| 4.5. Modified Dependence Graph Possibility B Loop 2   | 97  |

| 4.6. Modified Dependence Graph Possibility B Loop 1   | 98  |

| 4.7. Detailed Example 2                               | 100 |

| 4.8. Detailed Bond Graph for Example 2                | 101 |

| 4.9. Dependence Graph for Example 2                   | 103 |

| 4.10. Example 2 MDG Possibility A Loop 2              | 104 |

| 4.11. Example 2 MDG Possibility A Loop 1              | 105 |

| 4.12. Example 2 MDG Possibility B Loop 2              | 107 |

| 4.13. Example 2 MDG Possibility B Loop 1              | 108 |

| 5.1. Dependence Graph for Example 1 with BDF          | 116 |

| 5.2. Loop 2 for Example 1 with BDF                    | 117 |

| 5.3. Loop 1 for Example 1 with BDF                    | 117 |

| 5.4. Inductor Causalities with BDF                    | 126 |

| 5.5. Capacitor Causalities with BDF                   | 127 |

| 5.6. Bond Graph Causality (c) for Example 1           | 129 |

| 5.7. Bond Graph Causality (d) for Example 1           | 129 |

| 5.8. Simulation Flow Diagram                          | 131 |

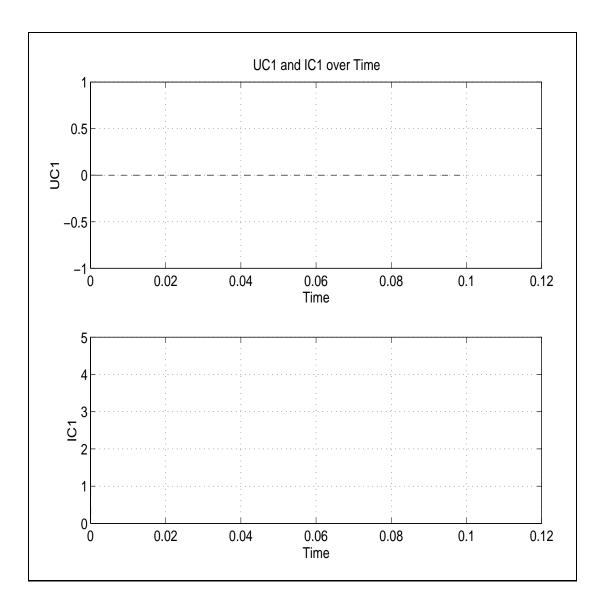

| 5.9. Simulation Results Example $(1)$                 | 140 |

| 5.10. Simulation Results Example $(2)$                | 141 |

| 5.11. Simulation Results Example $(3)$                | 142 |

| 5.12. Simulation Results Example $(4)$                | 143 |

| 5.13. Simulation Results Example $(5)$                | 144 |

| 6.1. Two Quadrant Rectifier Circuit                   | 145 |

| 6.2. Bond Graph (1) Two Quadrant Rectifier            | 150 |

| 6.3. Bond Graph (2) Two Quadrant Rectifier            | 152 |

| 6.4. Bond Graph (3) Two Quadrant Rectifier            | 153 |

| 6.5. SCR Circuit for Train Speed Control (1)          | 154 |

| 6.6. SCR Circuit for Train Speed Control (2)          | 156 |

| 6.7. Singular Cases SCR Circuit (1)                   | 160 |

| 6.8. Singular Cases SCR Circuit (2)                   | 160 |

| 6.9. Singular Cases SCR Circuit (3)                   | 161 |

| 6.10. Singular Cases SCR Circuit (4)                  | 161 |

|                                                       |     |

| 6.11. SCR Circuit for Train Speed Control (3) | 163 |

|-----------------------------------------------|-----|

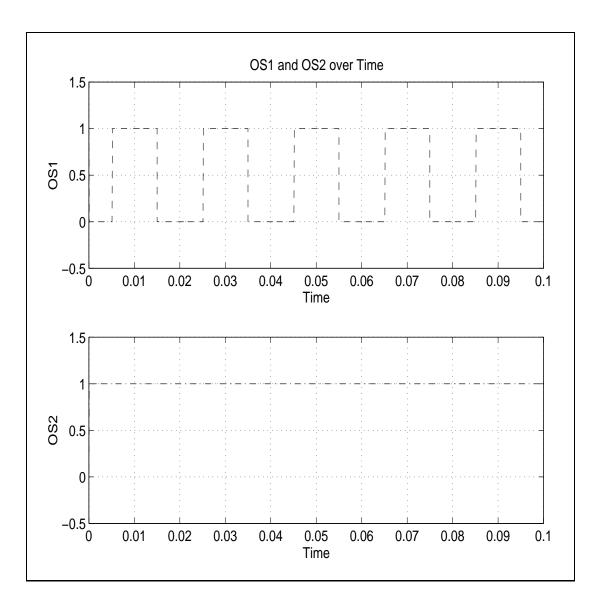

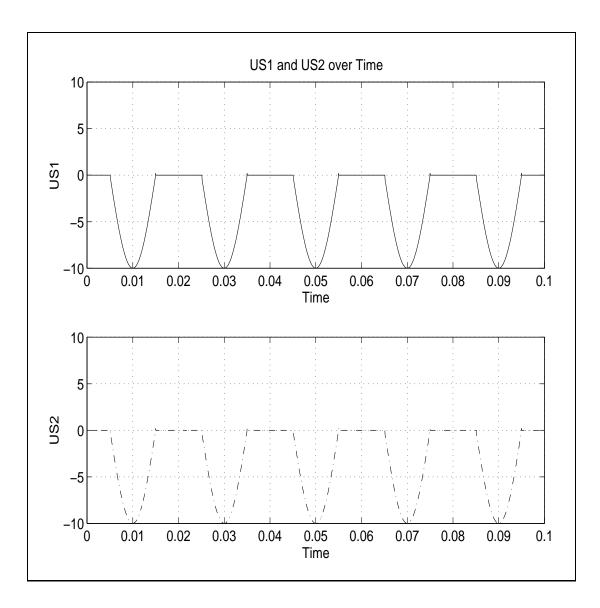

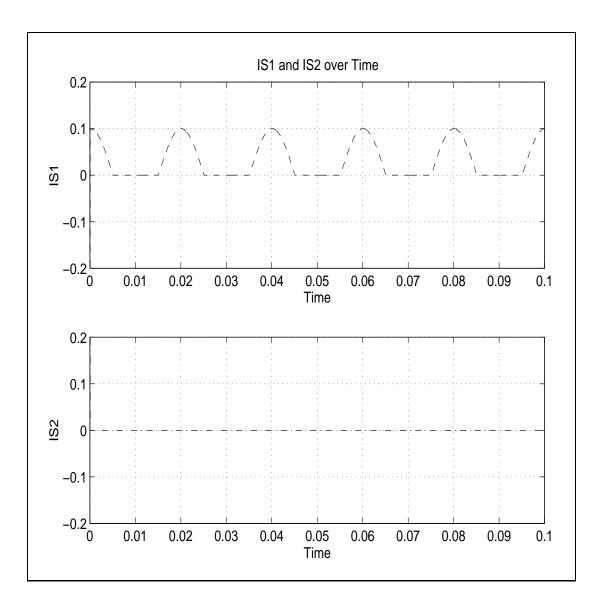

| 6.12. Simulation Results SCR Circuit (1)      | 164 |

| 6.13. Simulation Results SCR Circuit (2)      | 165 |

| 6.14. Simulation Results SCR Circuit (3)      | 166 |

# LIST OF TABLES

| 1.1. | Index of a DAE System                      | 21  |

|------|--------------------------------------------|-----|

| 2.1. | Conclusions Causality Strokes Assignment   | 50  |

| 3.1. | DAE Indices for Example Circuit            | 63  |

| 4.1. | Conditions for Loop 2 in Possibility A     | 94  |

| 4.2. | Conditions for Loop 1 in Possibility A     | 96  |

| 4.3. | Conditions for Loop 2 in Possibility B     | 97  |

| 4.4. | Conditions for Loop 1 in Possibility B     | 99  |

| 4.5. | Conditions for Both Loops in Possibility A | 106 |

| 4.6. | Conditions for Both Loops in Possibility B | 110 |

| 6.1. | Values for System Determinant              | 148 |

| 6.2. | Circuit Operation Modes                    | 155 |

| 6.3. | Singular Cases SCR Circuit                 | 159 |

# ABSTRACT

An electrical circuit containing switch elements represents a variable structure system. Ideal switch element can be described by a switch equation using a discrete variable to specify the switch position. The causality of an ideal switch element cannot be fixed. However non-ideal switches used to prevent the causality problem often cause artificial stiffness in the resulting differential equation model.

The idea for resolving the causality assignment problem was to modify Pantelides' index reduction algorithm to a form suitable for conditional index changes. However, a fairly simple counterexample shows that pure modifications of switch equations cannot solve the causality problem.

However, the previous analysis resulted in a new idea, the use of *implicit difference* formulae that are widely used in commercial DAE solvers. The new approach solves the problems associated with index changes. Yet, the concept still has remaining problems caused by the ideal nature of switches.

## PREFACE

The topic of this thesis is to find an algorithm, probably graph-theoretical, that recognizes conditional index changes in a model and performs the necessary formulae manipulations in extension of the Pantelides algorithm. The first part of this thesis is concerned with graphical methods that were used. The second part uses these graphical methods to find restrictions for the parameter set used to describe the modification problem. These restrictions result in contradictions for two identified possibilities of seemingly promising solutions in a simple example. The analysis proves that there cannot exist any solution to the problem using an extended Pantelides algorithm. The idea for a different approach was then borne, and the subsequent part of the thesis shows how the problem can indeed be solved by using Difference Formulae. Then follows the description of the complete solution for the simple example, as well as a more complicated example containing six switches that is characterized by 64 possible switch combinations. This second example exhibits some cases where the simulation still does not work. In the sequel these cases are examined to unveil the reasons that explain the singularities.

# CHAPTER 1

# Introduction

## 1.1 The Problem Statement

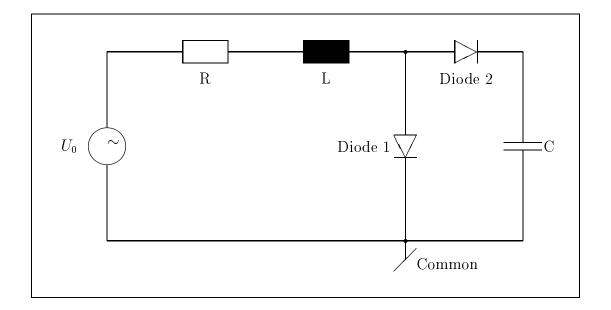

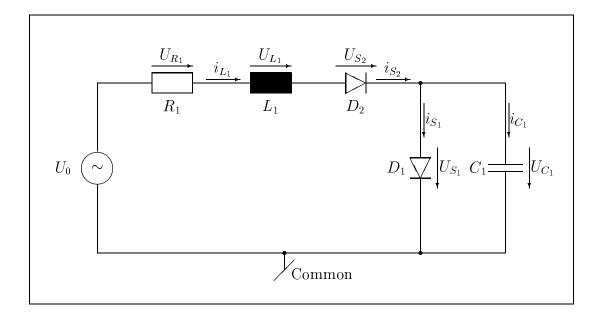

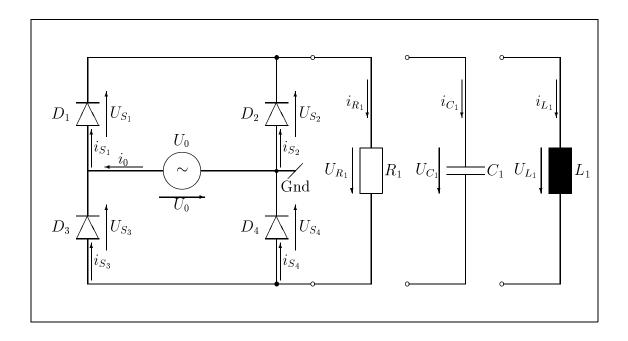

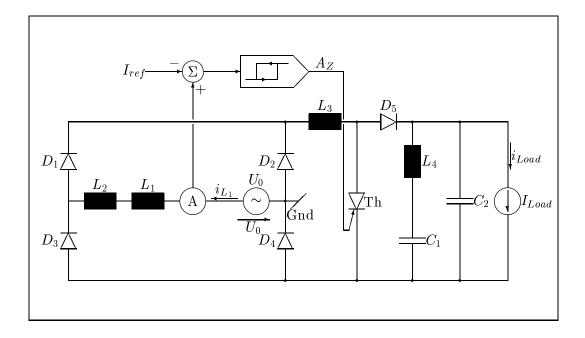

Find an algorithm, probably graph-theoretical, that recognizes conditional index changes in a model and performs the necessary formulae manipulation in extension to the Pantelides [5] algorithm. Attacking this problem will start with a simple example that cannot be solved by the usual Pantelides algorithm. Then, one can find the modified equations for the example shown in Fig. 1.1, and derive from these equations underlying basic rules. Working with these basic rules, they can be embodied in an extended algorithm for arbitrarily complex circuits.

### **1.2 Basic Concepts**

This section describes briefly basic concepts that are important to understand the subsequent work. Model descriptions, equation systems, differential algebraic equation systems, and switch equations are the four parts that are explained in detail. The first part on model descriptions elaborates on the two most frequently used model descriptions, the differential algebraic equation system and the ordinary

Figure 1.1: Example circuit

differential equation system. Subsequently, general equation system concepts that are necessary to understand algebraic loops are introduced. Differential algebraic equation systems are the focus of the third part that includes the definition of the DAE index, the explanation of the higher index problem, and the description of the Pantelides algorithm. In the final part, switch equations are introduced and explained. Finally, the conditional index changes resulting from switch equations are introduced by means of an example.

#### **1.2.1** Model Descriptions

#### 1.2.1.1 Differential Algebraic Equation Systems (DAE)

In general, modeling of physical systems leads naturally to models described by sets of *differential algebraic equations*. A Differential Algebraic Equation system (DAE) is of the following general form:

$$0 = h(x, \frac{\partial x}{\partial t}, y, p, t) \qquad ; \qquad x(t_0) = x_0 \tag{1.1}$$

where x is the vector of unknown variables that truly appear in differentiated form, whereas y is the vector of purely algebraic unknown variables. p is a vector of parameters contained in the model description, and t denotes time. Note that the number of equations equals the sum of the unknown variables, i.e. dim(h) = dim(x) + dim(y).

If Equation (1.1) can be explicitly solved for y and y is independent of any derivative, we can use the more specialized form:

$$0 = f(x, \frac{\partial x}{\partial t}, p, t) \qquad ; \qquad x(t_0) = x_0 \tag{1.2}$$

$$y = g(x, p, t) \tag{1.3}$$

This form is characterized by a set of implicit purely differential equations and a set of explicit purely algebraic equations. Note that this form is contained in the previous general form, and

$$h = \begin{bmatrix} f(x, \frac{\partial x}{\partial t}, p, t) \\ y - g(x, p, t) \end{bmatrix}$$

(1.4)

### 1.2.1.2 Ordinary Differential Equation Systems (ODE)

Another frequently used model description is the state–space model, represented by a set of *ordinary differential equations*, and a set of algebraic output equations. A state–space model is described by an Ordinary Differential Equation System (ODE):

$$\dot{x} = f(x, p, t)$$

;  $x(t_0) = x_0$  (1.5)

supplemented by the set of algebraic output equations:

$$y = g(x, p, t) \tag{1.6}$$

where x is the vector of state variables, y is the vector of output variables, p is a vector of parameters contained in the model description, and t denotes time. Note that both parts, the ODE system and the algebraic output system, are contained in the state-space model. This frequently used model description is even more specific than the specialized DAE description. The state-space description assumes that the state variables are known, and calculates the derivatives using the set of assignments given by f. The knowledge of the state variables makes the solution of the algebraic output system trivial, as this results in a mere function evaluation. Thus, the output equation system is frequently neglected.

The number of equations in the ODE system equals the sum of unknown variables, however this time, the derivatives of the state variables and not the state variables themselves are considered to be unknown.

## 1.2.2 Equation System Concepts

### 1.2.2.1 Structure Incidence Matrix

The structure incidence matrix is used to describe the properties of an equation system. The following example equation system:

$$f_1(x_1, x_2) = 0 \tag{1.7}$$

$$f_2(x_2) = 0 (1.8)$$

$$f_3(x_1, x_2, x_3) = 0 \tag{1.9}$$

can be characterized by the structure incidence matrix:

$$S = \begin{cases} x_1 & x_2 & x_3 \\ f_1 \begin{pmatrix} 1 & 1 & 0 \\ 0 & 1 & 0 \\ f_3 \begin{pmatrix} 0 & 1 & 0 \\ 1 & 1 & 1 \end{pmatrix}$$

(1.10)

Thereby an element in the  $i^{th}$  row and  $k^{th}$  column is either one, if the  $k^{th}$  variable forms part of the  $i^{th}$  equation, or zero, if the  $k^{th}$  variable does not show up in the  $i^{th}$ equation.

### 1.2.2.2 Algebraic Loop

The structure of an equation system is preserved if the order of the equations or the order of the variables is changed. Multiplying the structure incidence matrix Swith a permutation matrix P from the left corresponds to rearranging the equation sequence, whereas multiplying the structure incidence matrix S with a permutation matrix Q from the right corresponds to rearranging the variable sequence.

$$\hat{S} = P \cdot S \cdot Q \tag{1.11}$$

The equivalent structure incidence matrix  $\hat{S}$  has the same properties as the original structure incidence matrix S. The permutation matrices, P and Q, are determined in such a way that they transform the matrix S into a lower block-triangular matrix  $\hat{S}$ . This lower block-triangular form represents the easiest way to solve the equation system. For the above example

$$P = \begin{pmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & 0 & 1 \end{pmatrix} \quad \text{and} \quad Q = \begin{pmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & 0 & 1 \end{pmatrix}$$

result in the lower triangular matrix

$$\hat{S} = \begin{pmatrix} 1 & 0 & 0 \\ 1 & 1 & 0 \\ 1 & 1 & 1 \end{pmatrix}$$

(1.12)

In this matrix  $\hat{S}$  the diagonal entries are blocks of size one. However, if the entries in the matrix  $\hat{S}$  require diagonal block sizes greater than one, then the equation system contains one or more *algebraic loops*. The number of algebraic loops is equivalent to the number of diagonal blocks with a dimension greater than one.

For example:

$$f_1(x_1, x_2, x_3) = 0 (1.13)$$

$$f_2(x_1, x_2, x_3) = 0 (1.14)$$

$$f_3(x_1, x_2, x_3) = 0 (1.15)$$

is a completely coupled algebraic system that can be characterized by the structure incidence matrix:

This structure incidence matrix is already in a lower block triangular form, and permutation matrices cannot change the form of the structure incidence matrix. In

| DAE index   | incidence matrix  | linear                | $\operatorname{nonlinear}$ |

|-------------|-------------------|-----------------------|----------------------------|

|             | $\mathbf{S}$      |                       |                            |

| 0           | lower triangular  | can be converted into | solvable by successive     |

|             |                   | ODE form              | Newton Iterations for      |

|             |                   |                       | single variables           |

| 1           | block lower       | contains algebraic    | solvable by successive     |

|             | ${ m triangular}$ | loops                 | Newton Iterations for      |

|             |                   |                       | several (indicated by      |

|             |                   |                       | diagonal block size)       |

|             |                   |                       | variables together         |

| 2 or higher | is singular       | contains one or more  | contains one or more       |

|             |                   | depending storage     | depending storage          |

|             |                   | elements              | elements                   |

Table 1.1: Index of a DAE System

this example, we have the extreme case of a single block that can be considered as a diagonal block of dimension three. Consequently, the equation system has one algebraic loop containing all three equations and all three variables.

## 1.2.3 Differential Algebraic Equation System Concepts

## 1.2.3.1 DAE Index

The index of a DAE system is a measure of the solvability of a DAE system description by certain DAE solvers, and describes the difficulties involved in solving the DAE system [11]. The index of a DAE system is described concisely in the Table 1.1.

In the linear case, an index 0 DAE system can be converted into ODE form, whereas

in the nonlinear case, successive Newton Iterations for one variable result in values for the derivatives that are then the input of an ODE solving integration algorithm. The index 1 DAE system is in the linear case nothing more than a matrix equation that can be solved in many ways, e.g. using Cramer's rule for the inversion of the matrix. A nonlinear index 1 DAE can be solved by successive Newton Iterations over several simultaneous variables. Thus, the main difference to the index 0 DAE system is the need for Newton Iterations over a vector of simultaneous variables, instead of successive Newton Iterations over a single variable. A DAE system with an index of two or higher is called a *higher index problem*, and is described by an example in the next section.

#### 1.2.3.2 Higher Index Problem

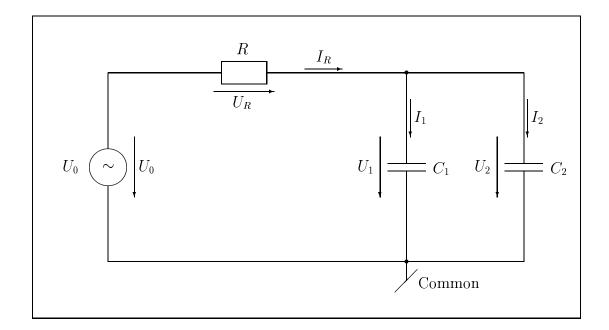

Fig. 1.2 represents a simple example of a higher index problem. The two capacitors in parallel are two dependent storage elements. The voltage across the two capacitors is always the same, and thus the amount of energy stored in the electric field is characterized by a single variable. In such a simple example, one would probably replace the two capacitors with one resulting capacitance, however in more complex circuits, detecting dependent storage elements is a difficult and error-prone task. Let us take a look at the DAE description to get a feeling for the peculiarities that occur:

$$U_0 - \hat{U}_0 \cdot \cos(\omega t) = f_1 = 0$$

Figure 1.2: Higher Index Problem

$U_R - R \cdot I_R = f_2 = 0$  $I_1 - C_1 \cdot \frac{\partial U_1}{\partial t} = f_3 = 0$  $I_2 - C_2 \cdot \frac{\partial U_2}{\partial t} = f_4 = 0$  $U_0 - U_R - U_1 = f_5 = 0$  $U_1 - U_2 = f_6 = 0$  $I_R - I_1 - I_2 = f_7 = 0$

Let us try to transform the set of equations to a set of explicit equations for an ODE solver. In this case  $U_1$  and  $U_2$  are assumed known, and the structure incidence matrix is thus:

$$U_{0} \quad U_{R} \quad I_{R} \quad I_{1} \quad I_{2} \quad \frac{\partial U_{1}}{\partial t} \quad \frac{\partial U_{2}}{\partial t}$$

$$f_{1} \begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 0 & 0 & 0 \\ f_{3} & 0 & 0 & 0 & 1 & 0 & 1 \\ 0 & 0 & 0 & 0 & 1 & 0 & 1 \\ f_{5} & 1 & 1 & 0 & 0 & 0 & 0 \\ f_{6} & 0 & 0 & 0 & 0 & 0 & 0 \\ f_{7} & 0 & 0 & 1 & 1 & 1 & 0 & 0 \end{pmatrix}$$

$$(1.17)$$

Equation  $f_6$  does not contain any unknowns, and thus the structure incidence matrix S contains a zero row. This clearly indicates a singular structure incidence matrix and points to the higher index problem. The structure incidence matrix indicates that we have seven equations for seven unknowns, yet equation  $f_6$  is completely useless. Let us take a closer look at equation  $f_6$ :

$$U_1 - U_2 = f_6 = 0 \tag{1.18}$$

$f_6$  is a function of time, and is equal to zero for all times, and therefore, also the derivative  $\frac{\partial f_6}{\partial t}$  must be equal to zero for all times.

$$\frac{\partial U_1}{\partial t} - \frac{\partial U_2}{\partial t} = \frac{\partial f_6}{\partial t} = \hat{f}_6 = 0 \tag{1.19}$$

If we substitute this modified equation  $\hat{f}_6$  for the previously used equation  $f_6$ , we obtain the structure incidence matrix:

The structure incidence matrix  $\hat{S}$  is non–singular, and the problem can now be converted into ODE form.

In ODE simulation, the outputs of integrators are chosen as "state variables". This notation is already used in the DAE description that should be converted into ODE form. Whenever state variables appear in an algebraic equation, the model contains dependent storage elements that result in a higher index problem. The *Pantelides Algorithm* is used to determine, which equations need to be differentiated in order to reduce the DAE index before the DAE system can be converted to an ODE description.

#### 1.2.3.3 The Pantelides Algorithm

The Pantelides Algorithm determines the equations that need to be differentiated in order to remove algebraic couplings between "state variables." The algorithm does the index reduction in steps. Each step reduces the index by one, and if after a step there are still further algebraic couplings between state variables, another step is necessary. However, the Pantelides algorithm does not work if the DAE description itself can change the index depending on a discrete variable. Such model descriptions are called *Conditional Index Models*, and this thesis is particularly concerned with Conditional Index Changes caused by electrical switch elements.

### **1.3** Switch Elements

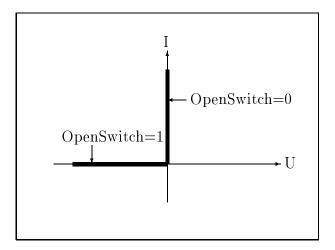

An electric switch element is a two-pin element, just like all of the traditional linear passive circuit elements. Yet whereas resistors, capacitors, inductors, voltage sources, and current sources are all modeled using a single equation, the switch element is usually described by two separate equations, one for each of the two possible switch positions. However it is possible to combine these two equations in a single conditional statement, and consequently, the switch element can be represented by the equation

$$0 = if OpenSwitch then I else U$$

(1.21)

OpenSwitch in this statement is a *boolean variable* with the two possible values *true* and *false*. These values correspond to the opened and closed position, respectively. For the purpose of an equation solver, this equation can be rewritten in a more useful form:

$$0 = OpenSwitch \cdot I + (1 - OpenSwitch) \cdot U \tag{1.22}$$

Here, OpenSwitch is a *discrete variable* with two possible values 0 and 1. The value 1 corresponds to the opened switch, and the value 0 represents the closed switch. Thus, an electric switch element can be characterized by a single equation, containing the voltage u and the current i, just like all other linear passive circuit elements. However, and contrary to the equations governing other circuit elements, the equation contains an additional discrete switch variable that describes the position of the switch.

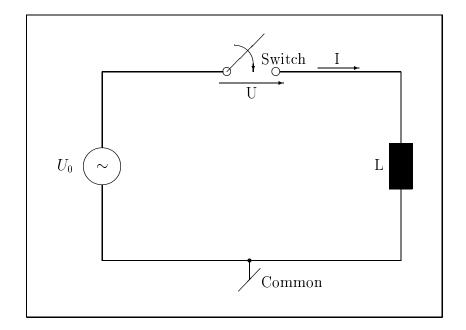

The equation is only of use if we can solve practical problems with it. Let us look at an introductory example, as shown in Fig.1.3. In this example circuit, the switch element is placed in series with an inductor. The current through the inductor is a natural state variable, thus the current I is known, and the switch equation must be solved for U.

$$U = \frac{OpenSwitch}{(OpenSwitch - 1)} \cdot I \tag{1.23}$$

Figure 1.3: Switch–Inductor example circuit

Unfortunately, equation (1.23) is only valid as long as the switch is closed. As soon as the switch opens, the expression in the denominator becomes zero, and the simulation ends with a division by zero. Thus, one may ask oneself how useful the switch equation (1.22) is. In this example, the result is understandable as the circuit behaves in a different manner in reality than in the model description. The current through an inductor cannot jump, and as a result, a light arc will be drawn. This light arc represents a growing resistance until the arc breaks with a resulting infinite resistance value. This example illustrates a property that any switch element used in a simulation model must adhere to. It can be concisely stated as follows: The causality of a switch element must not be dictated by the surrounding circuit, but must be merely a function of the independent discrete variable OpenSwitch.

The meaning of the causality principle will be further explained in the second chapter.

This characteristic property of an independent switch element leads to the conclusion that switch elements must always be contained in algebraic loops, and thus, the discrete switch variable can assume either value regardless of the switch environment. [2]

At this point it was not known, how this concept could be extended to more than one switch element. However, it was clear that at least one algebraic loop is needed, in which the switch equations are contained, to prevent the switch equations from being solved for either variable. Rather, the whole system of equations constituting the algebraic loop will be solved together.

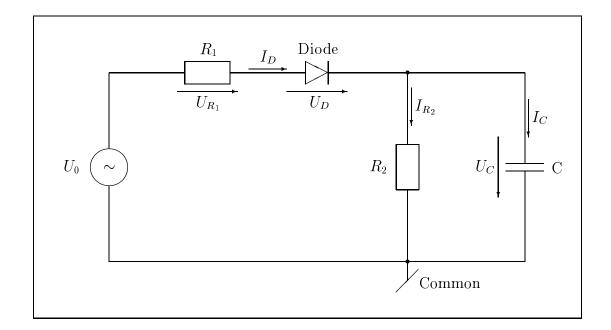

The next example circuit, shown in Fig.1.4, satisfies this requirement. This example contains a diode, a specific switch element. The relationship between a switch and a diode can be modeled in the object-oriented modeling language Dymola [6] as follows:

Figure 1.4: Half–wave rectifier circuit

```

model class TwoPin

cut WireA(Va/I), WireB(Vb/-I)

main cut Wires [WireA,WireB]

main path P <WireA-WireB>

local U

U = Va - Vb

```

$\mathbf{end}$

```

model class (TwoPin) Switch

terminal OpenSwitch

0 = OpenSwitch * I + (1 - OpenSwitch) * U

end

```

```

model class (Switch) Diode

```

```

new(OpenSwitch) = if ((not U>0) and (not I>0)) then 1 else 0

```

end

The first part of the code is the basic declaration of a TwoPin element, derived from this class is a new class Switch, which in turn is the superclass of another derived specific switch class Diode. In the same fashion, classes for voltage sources, current sources, capacitors, inductors, and resistors can be derived from the TwoPin class by inheritance. Similarly, classes for thyristors, samplers, and other specific switches can inherit the properties of the Switch class, which itself inherits properties from the TwoPin class.

This definition of an ideal diode is characterized by the diagram shown in Fig.1.5. The model for the circuit shown in Fig.1.4 contains the following equations:

$$-U_0 + U_C + U_D + U_{R_1} = 0 (1.24)$$

Figure 1.5: Ideal Diode Characteristics

$$I_D - I_C - I_{R_2} = 0 (1.25)$$

$$U_{R_1} - R_1 \cdot I_D = 0 \tag{1.26}$$

$$U_C - R_2 \cdot I_{R_2} = 0 \tag{1.27}$$

$$I_C - C \cdot \frac{\partial U_C}{\partial t} = 0 \tag{1.28}$$

$$OpenSwitch \cdot I_D + (1 - OpenSwitch) \cdot U_D = 0$$

(1.29)

accompanied by the equations:

$$New(OpenSwitch) - \text{If } not(U_D > 0) \text{ and } not(I_D > 0) \text{ then } 1 \text{ else } 0 = 0$$

(1.30)

$$U_0 = \hat{U}_0 \cdot \sin(\omega t) \quad (1.31)$$

1.24 - 1.29 describe a system of six equations for the six unknowns  $U_D$ ,  $\frac{\partial U_C}{\partial t}$ ,  $U_{R_1}$ ,  $I_D$ ,  $I_C$ , and  $I_{R_2}$  with the parameters  $R_1$ ,  $R_2$ , and C. The voltage  $U_C$  across the

capacitor is a state variable. Its value is known from a simulation step, whereas the derivative  $\frac{\partial U_C}{\partial t}$  is one of the unknowns. Equation 1.30 contains the information on how to determine the new value of the discrete switch variable *OpenSwitch* after a simulation step, whereas 1.31 determines how to calculate a new value for the input voltage using additional parameters  $\hat{U}_0$ , and  $\omega$ . The Differential Algebraic Equation (DAE) system of six unknowns can be rewritten in matrix form:

$$\begin{pmatrix}

1 & 0 & 1 & 0 & 0 & 0 \\

0 & 0 & 0 & 1 & -1 & -1 \\

0 & 0 & 1 & -R_1 & 0 & 0 \\

0 & 0 & 0 & 0 & R_2 & 0 \\

0 & -C & 0 & 0 & 0 & 1 \\

(1 - OS) & 0 & 0 & OS & 0 & 0

\end{pmatrix}

\cdot

\begin{pmatrix}

U_D \\

\frac{\partial U_C}{\partial t} \\

U_{R_1} \\

I_D \\

I_{R_2} \\

I_C

\end{pmatrix} =

\begin{pmatrix}

U_0 - U_C \\

0 \\

0 \\

U_C \\

0 \\

0

\end{pmatrix}$$

(1.32)

where OS has been introduced as an abbreviation for the hitherto used name OpenSwitch for the benefit of a more compact notation.

$$\det A_{1} = \begin{bmatrix} 1 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & -1 & -1 \\ 0 & 0 & 1 & -R_{1} & 0 & 0 \\ 0 & 0 & 0 & 0 & R_{2} & 0 \\ 0 & -C & 0 & 0 & 0 & 1 \\ (1 - OS) & 0 & 0 & OS & 0 & 0 \end{bmatrix}$$

$$= (1 - OS) \cdot \underbrace{CR_1R_2}_{k_1} - OS \cdot \underbrace{CR_2}_{k_2}$$

(1.33)

Equation 1.33 verifies that the DAE system is indeed non-singular for both OS = OpenSwitch = 0 and OS = OpenSwitch = 1, because the determinant assumes the values  $k_1$  and  $k_2$ , respectively, in the two cases. Thus, we have an algebraic loop that is always solvable, and the simulation of this sample circuit will work without any problems.

However, in this example we missed one important aspect: the *conditional index change*. A conditional index change is characterized by a change in the index of the DAE system. If one would describe the example circuit 1.4 by two separate models, one for each of the two possible switch positions, the indices of the two DAE systems would be 0 in both cases.

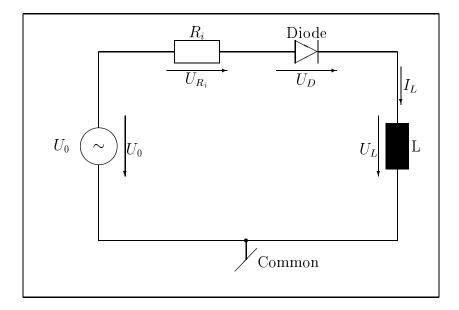

Let us look at a different example in which the aspect of the conditional index change comes to bear. Fig.1.6 contains a diode to assure the proper modeling of the circuit at switch instants. Contrary to Fig.1.3, the switch in this model opens only if the current passes through zero. Thus, the characteristic of the ideal diode prevents the light arc. However, just as in the earlier example, the current through the inductor is a natural state variable, and thus, the causality of the switch is predetermined by the inductor. In reality, if the switch opens, there is no longer any inductor present, because the inductor is no longer contained in any mesh. Yet, the model contains a first order differential equation for the inductor, even if the inductor no longer plays any part in determining the behavior of the circuit. Therefore, in this example, the index jumps from 0 to 2 when the discrete switch variable changes its value from 0 to 1.

For the model of the circuit shown in Fig.1.6, the necessary algebraic loop for the switch element can be achieved quite easily by modifying the switch equation to

$$0 = OpenSwitch \cdot \frac{\partial I}{\partial t} + (1 - OpenSwitch) \cdot U$$

(1.34)

This equation uses the knowledge that, if a variable is zero for all times, the higher derivatives of that variable must also be zero for all times. If all lower derivatives

Figure 1.6: Inductive load circuit

of the variable are properly initialized to zero, the modified equation expresses the same condition as the original switch equation. Another view of this modification is that the differentiation introduces auxiliary state variables in the switch element that equalize the DAE Index of the modeled system for all switch positions.

The model for the circuit shown in Fig.1.6 contains the following equations:

$$U_0 - U_{R_i} - U_D - U_L = 0 (1.35)$$

$$U_{R_i} - R_i \cdot I_L = 0 \tag{1.36}$$

$$OpenSwitch \cdot \frac{\partial i_L}{\partial t} + (1 - OpenSwitch) \cdot U_D = 0$$

(1.37)

$$U_L - L \cdot \frac{\partial i_L}{\partial t} = 0 \tag{1.38}$$

accompanied by the equations:

$$New(OpenSwitch) - \text{If } \operatorname{not}(U_D > 0) \text{ and } \operatorname{not}(I_L > 0) \text{ then } 1 \text{ else } 0 = 0 \quad (1.39)$$

$$U_0 = \hat{U_0} \cdot \sin(\omega t) \quad (1.40)$$

The identity  $i_{R_i} = i_D = I_L$  was used to substitute  $i_{R_i}$ , and  $i_D$ . The Differential Algebraic Equation (DAE) system of four unknowns can be rewritten in matrix form:

$$\underbrace{\begin{pmatrix} 1 & 1 & 1 & 0 \\ 1 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & (1 - OS) & 0 & OS \\ 0 & 0 & 1 & -L \end{pmatrix}}_{A_2} \cdot \begin{pmatrix} U_{R_i} \\ U_D \\ U_L \\ \frac{\partial i_L}{\partial t} \end{pmatrix} = \begin{pmatrix} U_0 \\ R_i \cdot i_L \\ 0 \\ 0 \end{pmatrix}$$

(1.41)

where OS is again the abbreviation for the previously used name OpenSwitch for the benefit of a more compact notation.

$$\det A_{2} = \begin{vmatrix} 1 & 1 & 1 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & (1 - OS) & 0 & OS \\ 0 & 0 & 1 & -L \end{vmatrix} = (1 - OS) \cdot \underbrace{-L}_{k_{3}} + OS \cdot \underbrace{(+1)}_{k_{4}}$$

(1.42)

Equation 1.42 verifies that the conditional index system with the modified switch equation is indeed non-singular for both OS = OpenSwitch = 0 and OS = OpenSwitch =

1, because the determinant assumes the values  $k_3$  and  $k_4$ , respectively, in the two cases. Thus the modification of the switch equation created an algebraic loop that is always solvable, and the simulation of this circuit will proceed correctly without any problems.

In this simple circuit, the necessary modification was easy to find, and in the dual case of a capacitor in parallel with a diode, the modification can be found just as easily. That is, the voltage term  $\mathbf{U}$  is replaced by its first-order derivative and the current term  $\mathbf{I}$  stays the same as in the original switch equation.

This leads to the basic task to be performed:

Replace the general switch equation (1.22) by the modified switch equation (1.43), and determine especially the constants  $n_1$  and  $n_2$  specifying the number of differentiations needed for each of the branches of the if statement. Add the necessary equations for the proper initialization.

$$0 = OpenSwitch \cdot \frac{\partial^{n_1}I}{\partial t^{n_1}} + (1 - OpenSwitch) \cdot \frac{\partial^{n_2}U}{\partial t^{n_2}}$$

(1.43)

The modified switch equation is accompanied by  $n_1 + n_2$  initial conditions to assure the same behavior as the original switch equation. In Dymola, the initialization process at switch time points is expressed in the following code that is only executed when the expression in the **when** statement *becomes* true.

```

when OpenSwitch then

init(I)

init(Id)

init(Id2)

...

init(Id(n1-1))

```

$\mathbf{endwhen}$

when (1 - OpenSwitch) then

init(U)

init(Ud)

init(Ud2)

...

init(Ud(n2-1))

#### endwhen

To find an algorithm to perform such modifications for each switch element in an arbitrarily complex circuit in a deterministic way was the task that should be tackled in this thesis.

Note that we want to use ideal switch elements. Our conditional index problem could be solved by non-ideal switch elements. In *non-ideal* switch elements, the switch is replaced by a small but non-vanishing resistance in the closed case and by a small yet non-zero conductance in the open case. Using such switch elements allows to simulate conditional index systems. However, the simulation with non-ideal switch elements has a significant disadvantage. Whenever the ideal switch equation would result in a zero denominator, the non-ideal switch equation will have a very small denominator, leading to artificial stiff system behavior. This behavior causes increasing simulation times and thus increased simulation cost.

# CHAPTER 2

# Graphical Tools and Representations Used Throughout This Thesis

In this chapter, the graphical methods that are being used in later chapters are described and explained by means of simple examples. The meanings of important concepts related to this thesis are briefly described. For further details, the reader is referred to the quoted references.

The chapter consists of two parts, bond graphs and dependence graphs. The first part introduces bond graphs and continues with the bond graph causality concept. The bond graph methodology offers an excellent tool for visualizing the problems associated with conditional index changes. The second part is concerned with dependence graphs and introduces several modifications that are useful in the subsequent work. The modified dependence graphs are used to find requirements for algebraic loops. The algebraic loops should contain the switch equations and thus prevent the problem of singular denominators.

## 2.1 Graphical Modeling Tools

# 2.1.1 Bond Graphs

# 2.1.1.1 Bond Graph Modeling

This is a short introduction to the technique of Bond Graph Modeling. For a complete understanding, the corresponding literature should be reviewed. A more detailed description of the technique can be found in [1].

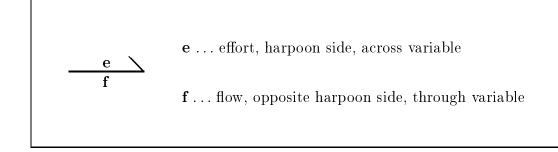

A bond, represented by a harpoon, is a graphical way of representing equations. Two variables are associated with each bond, an *across variable*, in bond graph terminology usually referred to as the *effort* **e**, and a *through variable*, called the *flow* **f**. A bond is shown in Fig.2.1.

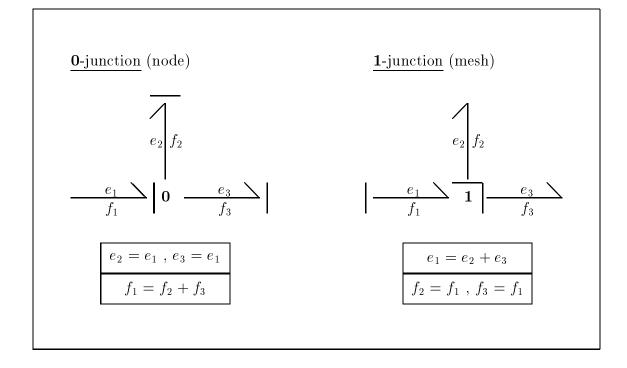

Figure 2.2: Types of Junctions

A bond graph, contrary to many other graphical representations, does not separate the two types of variables from each other. Hence a bond graph preserves the *topological structure* of the model [1]. A further advantage of bond graphs is their ability of being used for different application domains, such as electric circuits, translational kinetics, rotational kinetics, hydraulic systems, chemical kinetics, and thermodynamics [1]. Bonds connect either to model elements or to other bonds in a junction. There are two different junction types, shown in Fig.2.2. For linear circuit theory, the 0-junction represents a node, and the 1-junction represents a mesh. In a 0-junction, all effort variables are set equal whereas all flow variables add up to zero, corresponding to Kirchhoff's current law. In a 1-junction, all effort variables add up to zero whereas all flow variables are set equal, reflecting Kirchhoff's voltage law. At least three bonds are needed to form a true junction, since two-bond junctions can be eliminated by amalgamating the two bonds into one. This follows from the fact, that in the case of only two bonds, the junction equations result in two identities. Neighboring junctions of the same gender can be combined into a single junction. Hence a bond connects either two junctions of different gender or a junction with a model element.

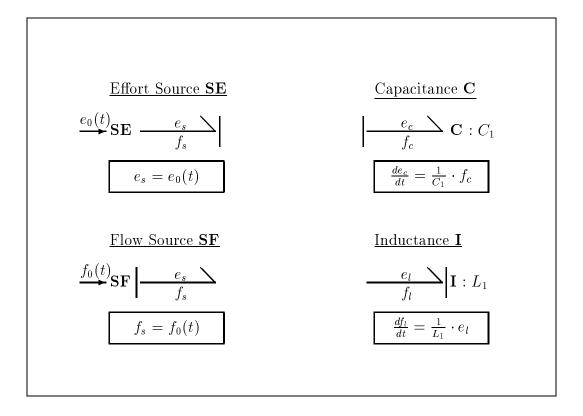

The two-pin elements of the previous chapter are, in bond graph terminology, called oneport elements. The bondgraphic oneport elements are shown in Fig.2.3.

Of course, in the case of electrical circuits, the effort variable corresponds to the voltage across the two-pin element whereas the flow variable maps into the current flowing through the two pins. The switch element is a general switch element that can be modified to become a *special switch*, e.g. an ideal diode, by specializing the functionality that defines the discrete terminal variable OS1.

Figure 2.3: Bond Elements for Circuit Theory

Figure 2.4: Bond Graph Inductive Load

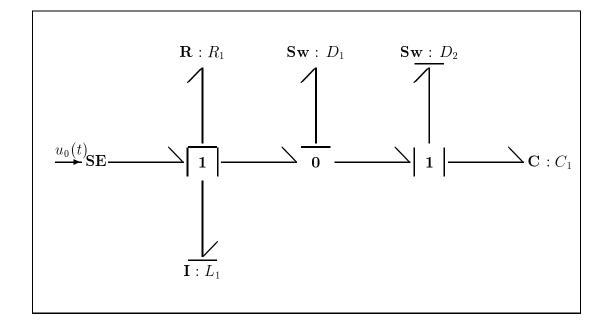

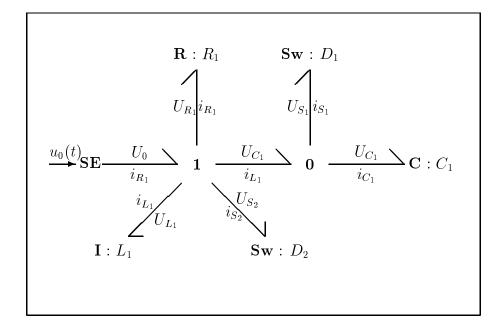

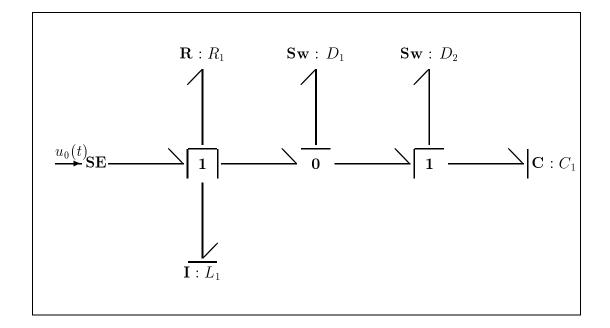

The bond graph representation for the last example of the introduction, 1.6, is shown in Fig.2.4.

## 2.1.1.2 Bond Graph Causality

The computational structure behind a bond graph can be easily represented using *causality strokes*. Each bond is involved in two equations, one to determine its effort variable **e**, the other to determine its flow variable **f**. The causality can be indicated by a short stroke perpendicular to the bond. The stroke is placed at one side of the

Figure 2.5: Resistor Causalities

bond. There it marks the side of the bond, at which the flow variable is determined [1].

For a resistor  $\mathbf{R}$ , both causalities are meaningful since the element equation  $e_r = R \cdot f_r$  can be solved for either the effort variable  $e_r$  or the flow variable  $f_r$ . In Fig.2.5(a), the flow variable is determined at the resistor element, and the resistor equation is solved for  $f_r$ . In contrast, in Fig.2.5(b), the effort variable is determined at the resistor, and the equation is solved for  $e_r$ . The second variable,  $e_r$  in Fig.2.5(a) and  $f_r$  in Fig.2.5(b), is determined at the node to which the element is connected.

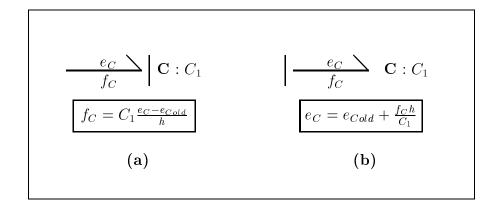

However for both types of source elements, the capacitor element, and the inductor element the causality is fixed. In the case of sources, the causality is physically determined through the source type. For the capacitor and inductor, the causality

Figure 2.6: Required Element Causalities

is given by a computational requirement. In these two elements, one of the variables is a state variable, and to determine the value of a state variable in a simulation, the derivative of that state variable needs to be calculated. The mandated causality strokes for these element types are shown in Fig.2.6.

Also junctions have requirements since only one flow variable can be determined at any 0-junction whereas only one effort variable can be determined at any 1junction. Thus at a 0-junction, only one causality stroke can be present, whereas at

Figure 2.7: Required Junction Causalities

a 1-junction, only one missing stroke is allowed. These requirements are shown in Fig.2.7.

The process of assigning causality strokes results in the conclusions shown in Table 2.1.

As already mentioned in the introduction, an algebraic loop is necessary for an independent switch element. It must be possible to open and close the switch independently from the circuit in which it is embedded. Therefore, a switch element

| causality requirements | system is called | causes and implications            |  |

|------------------------|------------------|------------------------------------|--|

| can be satisfied       | causal           | computational structure uniquely   |  |

|                        |                  | determined                         |  |

| cannot be satisfied    | non-causal       | if not satisfied at a source (e.g. |  |

|                        |                  | two parallel voltage sources with  |  |

|                        |                  | different voltages)                |  |

|                        | degenerate       | if not satisfied at an I or C      |  |

|                        |                  | element, structural singularity,   |  |

|                        |                  | higher index DAE                   |  |

| are insufficient       | having an alge-  | there is a free choice in the com- |  |

|                        | braic loop       | putational structure               |  |

Table 2.1: Conclusions Causality Strokes Assignment

cannot have a fixed requirement for its causality stroke. Its causality must be determined by the process of opening or closing the switch, as reflected in the value of the discrete variable *OpenSwitch*. Whenever a switch is forced to assume a fixed causality, this will invariably result in a crash of the simulation as soon as the *OpenSwitch* variable changes its value. This led to the conclusion that a switch element can only operate properly if contained in an algebraic loop.

Now we have another interpretation, from the point of view of the bond graph causality, of what goes wrong with the inductive load circuit shown in Fig.1.6. In this example circuit, the diode is used as a specialized switch element. To satisfy the causality requirement of a 1-junction, the causality of the switch element is predetermined, and therefore, the switch can only be simulated in the externally

Figure 2.8: Bond Graph with Causality

enforced position. The bond graph containing the causality strokes for the inductive load circuit is shown in Fig.2.8.

# 2.2 Graphical Methods to Represent Algebraic Structures

So far we have seen that we need an algebraic structure to include a properly working switch element. In this subsection, several possibilities for visualizing algebraic structures are described. The *modified dependence graphs* are extensively used throughout the later chapters.

## 2.2.1 Bipartite Graphs

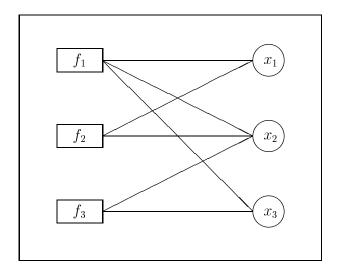

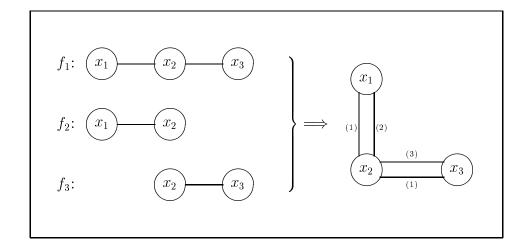

Bipartite Graphs [9] are a good way to visualize the dependences between a set of variables and a set of equations. First, it must be noted that only the dependence and not the functional relationship is shown in such a graph. It is thus a good tool for general equations, but does not include any specifications about the functions. The dependence among variables in a generic equation such as  $f(x_1, x_2, x_3) = 0$  can be visualized in a *bipartite graph*, and the equation can be regenerated from that graph. The dependence of variables in a specific equation such as  $sin(x_1) + log(x_2) = x_3$ can also be represented in a bipartite graph, but the equation can no longer be regenerated from that graph. Hence the graph is only useful for showing dependences among variables in equations, and not quantitatively specified functionalities, as e.g. in a signal flow graph.

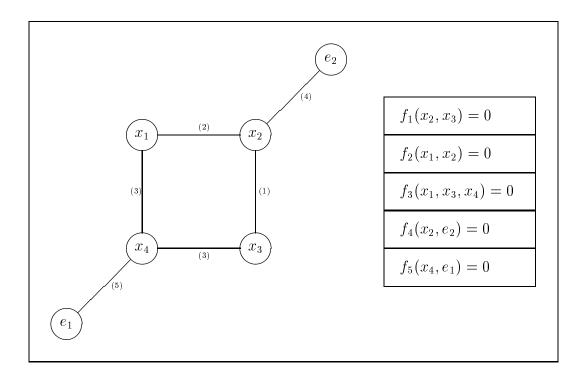

Let us look at an example:

$$f_1(x_1, x_2, x_3) = 0 (2.1)$$

$$f_2(x_1, x_2) = 0 (2.2)$$

$$f_3(x_2, x_3) = 0 \tag{2.3}$$

The system (2.1-2.3) can be visualized through a bipartite graph. On the left side, the set of equations is being listed as leaves, whereas on the right side, the union set

Figure 2.9: Bipartite Graph

of all variables is listed element by element as leaves. Branches connect the two sets of vertices to visualize the dependences among the variables in the equations. The bipartite graph is shown in Fig.2.9.

While this visualization is reversible, it is difficult to see the algebraic loop behind this bipartite graph. Indeed, the variable  $x_1$  can be determined from equation (2.1) or (2.2), but only with knowledge of  $x_2$  and  $x_3$ , or  $x_2$  respectively. The variable  $x_2$ itself can be determined from either of the three equations, but only with knowledge of  $x_1$  and  $x_3$ ,  $x_1$ , or  $x_3$  depending on the equation used. Finally,  $x_3$  can be calculated from either equation (2.1) or (2.3) with knowledge of  $x_1$  and  $x_2$ , or  $x_2$ . Thus, none of the variables can be calculated independently without knowing already at least one of the others, which clearly indicates an algebraic loop. The awkwardness of this

Figure 2.10: Dependence Graph

graph for more complex systems leads to the need for an alternative representation, as provided in the *dependence graphs*. These are described in the next section.

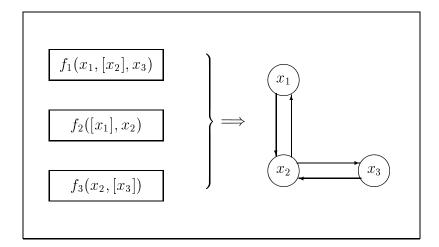

#### 2.2.2 Dependence Graphs

A dependence graph has only one set of elements as leaves, and is therefore less complex than a bipartite graph. However there is no unique way of determining a dependence graph from any set of equations. A computational order has to be determined that is shown in the dependence graph in the form of arrows. In Fig. 2.10, square brackets are used to denote the computational structure. Each equation is solved for the variable marked by square brackets. Hence each equation must contain exactly one set of square brackets, and each loop variable must be marked in exactly one equation. The computational structure indicated in the functions of Fig. 2.10 shows that  $x_2$  is evaluated from equation  $f_1$ ,  $x_1$  is determined using equation  $f_2$ , and  $x_3$  is calculated using equation  $f_3$ . The variables  $x_1$  and  $x_3$  are needed to evaluate  $x_2$  from equation  $f_1$ , and these *dependences* are indicated by two arrows pointing from the leaves representing the variables  $x_1$  and  $x_3$  to the leaf showing variable  $x_2$ . An arrow from  $x_2$  to  $x_1$  indicates that knowledge of  $x_2$  is necessary to determine  $x_1$  using equation  $f_2$ . In the same way, an arrow from  $x_2$  to  $x_3$  indicates that knowledge of  $x_2$  is needed to compute  $x_3$  through use of equation  $f_3$ . Algebraic structures are recognizable as loops formed by the arrows.

As there exists freedom in the assignment of the computational structure in an algebraically coupled equation system, the dependence graph is not unique, and even the resulting algebraic structures are not invariant to the selection of the computational order. However, once the computational order has been chosen, the resulting algebraic loops can be seen easily from the dependence graph.

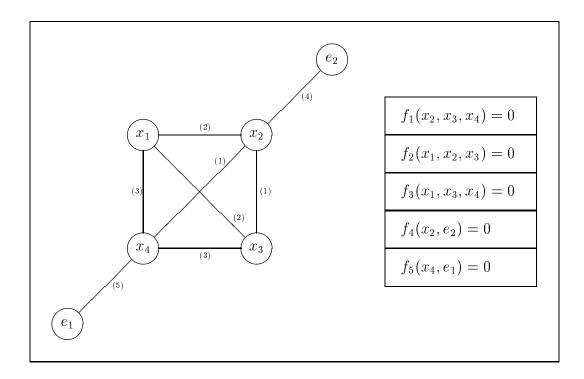

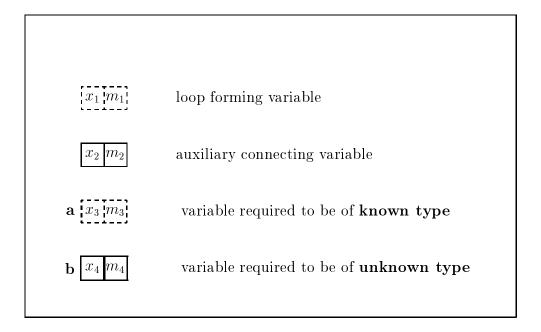

## 2.2.3 Modified Dependence Graphs

For the purpose of this thesis, the need to predetermine the computational structure of an algebraically coupled equation system is not optimal. A slight modification makes it possible to abstract the dependence graph a little further. It is

Figure 2.11: Modified Dependence Graph

always possible to eliminate the arrows, making the connections between the variables bi-directional, if the equation number is added to each connection. The so modified dependence graph contains less information than the original one, because the chosen computational structure can no longer be reconstructed from it. However, the modified dependence graph is also more general, because it is possible to draw modified dependence graphs that do not correspond to any possible computational structure, i.e., there exists even more freedom in drawing the modified dependence graph. Yet, the modified dependence graph is better suited for the task at hand.

Fig.2.11 shows one possible version of a modified dependence graph for the same example. On the left side, the equations are depicted together with the variables that they contain. The right side provides the same information in a more compact form. There is no need to draw a connection between variables  $x_1$  and  $x_3$ , because these two variables are already connected indirectly through variable  $x_2$  by means of two connections carrying the same equation number.

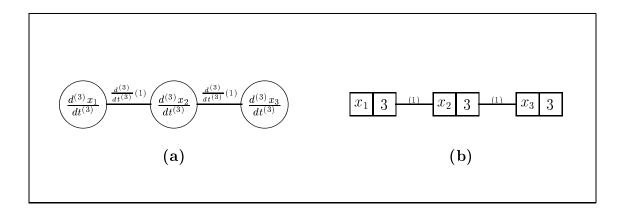

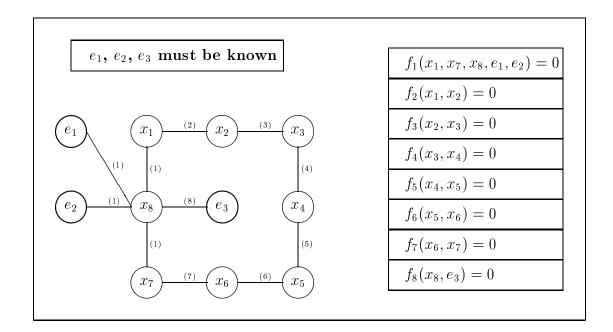

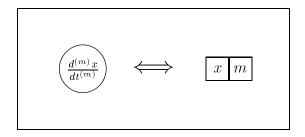

## 2.2.4 Modified Dependence Graphs for Time Derivatives

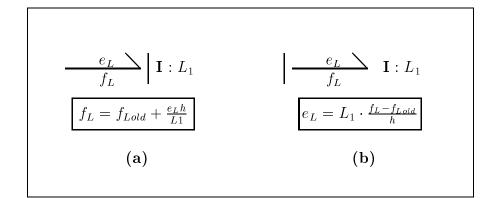

However, we still need one more abstraction level. Since we are dealing with DAE systems and the Pantelides algorithm, we encounter many equations in differentiated form. It may even happen that the same equation needs to be differentiated several times. As an example, we may consider that it was necessary to differentiate equation  $f_1$  three times. It would be possible to represent the differentiated equation  $f_1$  as shown in Fig.2.12(a) using the previously introduced notation. However, this would lead to overloaded figures that are hard to decipher. Therefore, an alternative representation was chosen as shown in Fig.2.12(b). This for derivatives once more modified dependence graph concentrates the information contained in the graph, and thus simplifies it.

This final notation may seem quite cryptic and abstract at first, but it increases the readability of the graphs used later. It is therefore the preferred representation chosen in subsequent chapters of this thesis.

Figure 2.12: For Derivatives Modified Dependence Graph

# CHAPTER 3

# First Unsuccessful Attempts at Solving the Problem

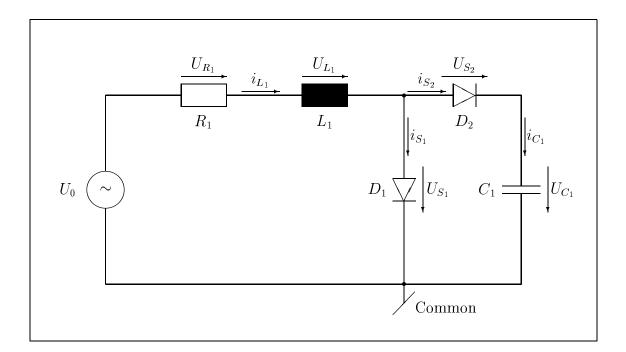

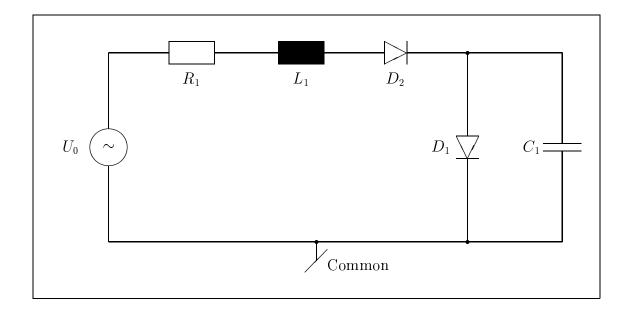

#### 3.1 The Example Circuit

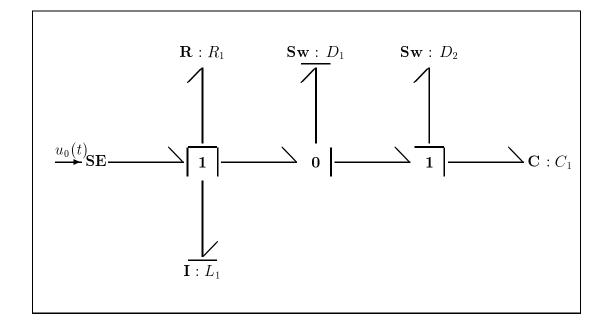

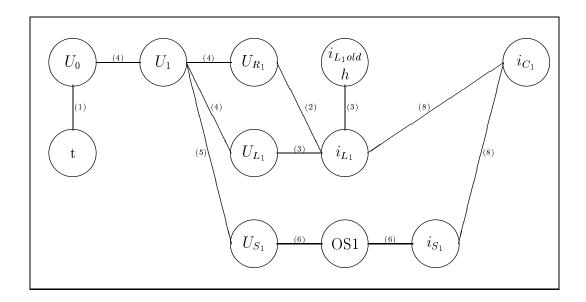

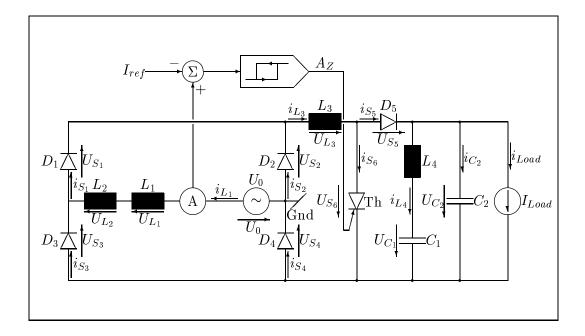

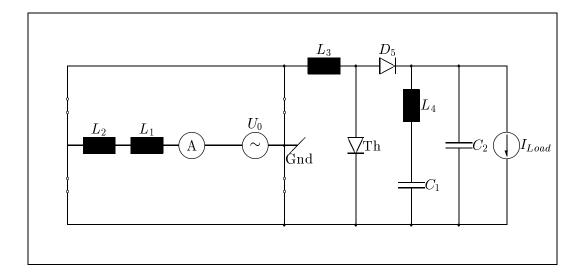

The example circuit was introduced in the introduction and is shown once more in Fig. 3.1 with the variable names used in the sequel. The circuit, which consists of two diodes, one inductor, one capacitor, and one resistor, contains a structure that makes the modifications of the switch equations difficult. While the modifications necessary to deal with an inductor in series with a diode or a capacitor in parallel with a diode were found quite easily, it is not at all trivial to find the modifications necessary to deal with this sample circuit. Somehow the diode  $D_2$  causes problems that defy attempts at finding a successful modification for the switch equation. If the diode was to the left of the node, as shown in Fig. 3.2, the known modifications would work. In the configuration of Fig. 3.2, the switch equation for diode  $D_1$  is modified to Equ. 3.1 whereas the switch equation for diode  $D_2$  is modified to Equ. 3.2. These two modifications create the necessary algebraic loops as desired. In both switches, the diode characteristic is needed to assure proper modeling. The second switch should only be opened if the current is 0, whereas the first switch should only be closed if the voltage is 0.

$$0 = OS1 \cdot I + (1 - OS1) \cdot \frac{\partial U}{\partial t}$$

(3.1)

$$0 = OS2 \cdot \frac{\partial I}{\partial t} + (1 - OS2) \cdot U \tag{3.2}$$

Figure 3.1: Detailed example circuit

However, in the case of the example circuit shown in Fig. 3.1, the required modifications don't follow such a simple pattern. Let us take different views of the model structure to gain a better understanding of the peculiarities of this example.

Figure 3.2: Example 2

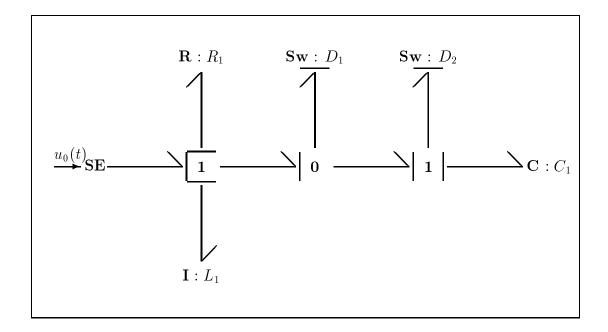

## 3.1.1 Bond Graph Causalities for the Example Circuit

There are two possibilities for assigning causality strokes to the bond graph for this example circuit. The two possibilities are shown in Fig. 3.3 and Fig. 3.4. The presence of more than one possibility for assigning the causality strokes leads to the conclusion that there must exist an algebraic loop. Yet, if we feed the model to a simulator, the simulation won't work. The explanation is simple. The algebraic loop contains *both* switches. Once the position of one switch is specified, the second switch position is dictated by the first one. Another aspect is that we have only two possibilities of assigning causality strokes, yet we have four possible switch positions.

Figure 3.3: Bond Graph Causality (a) for Example 1

In the physical circuit, this can be described as follows.

Let us consider two separate models that represent either switch  $D_1$  closed, represented in the model by a short circuit, or switch  $D_1$  opened, represented in the model by removing the switch element. In the first case, the second switch  $D_2$  must be opened, as otherwise, the voltage across the parallel capacitor would be forced to zero at once irrespective of its former value. In the second case, the second switch  $D_2$  must be closed, as otherwise, the current through the inductor would be forced to zero at once irrespective of its former value.

Figure 3.4: Bond Graph Causality (b) for Example 1

# 3.1.2 DAE Indices for the Example Circuit

Table 3.1 describes the four different combinations of possible switch positions and their associated DAE indices. The *equation order* in all four cases is two, because the system of equations contains two first order derivatives representing the two storage

| case | OS1 | OS2 | Order(Equ) | Order(Phy) | DAE index |  |  |

|------|-----|-----|------------|------------|-----------|--|--|

| 1    | 0   | 0   | 2          | 1          | 2         |  |  |

| 2    | 0   | 1   | 2          | 1          | 2         |  |  |

| 3    | 1   | 0   | 2          | 2          | 0         |  |  |

| 4    | 1   | 1   | 2          | 0          | 2         |  |  |

Table 3.1: DAE Indices for Example Circuit

elements, the inductor and the capacitor. The *physical order* describes how many storage elements are currently in use, depending on the switch positions. Only in case 3, when switch 1 is open and switch 2 is closed, is the physical order also two. In case 1 the two closed switches short out the capacitor, and thus the capacitor is taken out of the circuit. In case 2, where switch 1 is closed and switch 2 is opened, the capacitor is not properly connected. In case 4, both switches are open, no current flows at all, and the physical order of the system is thus zero. These differences between the equation order and the physical order results in a higher index problem. In the third case, no algebraic loop is present, and the index is zero.

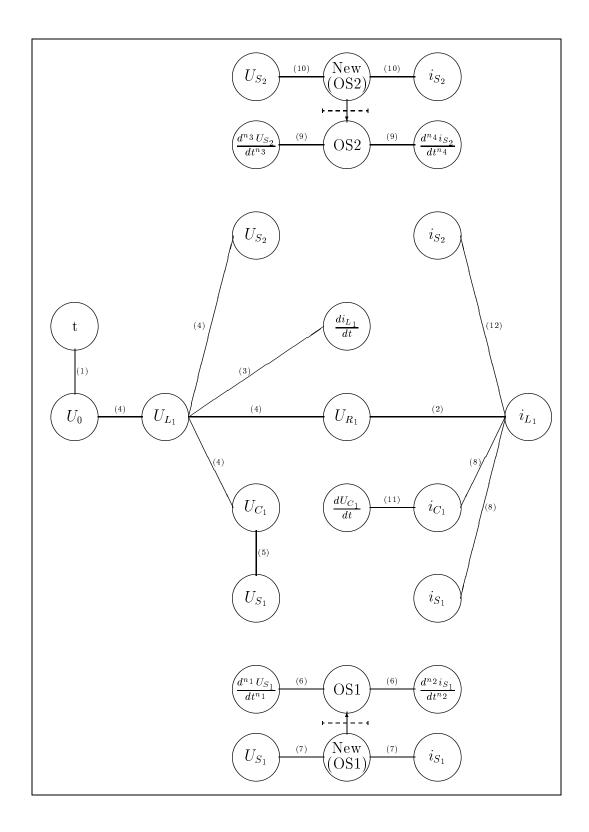

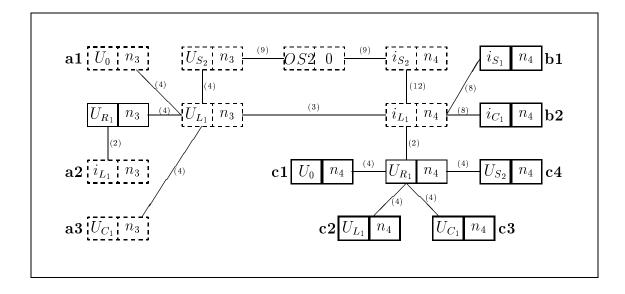

#### 3.2 The Task to be Accomplished

The example circuit contains two diodes, and thus the model has two switch equations. The task that needs to be addressed is the following. Determine the four integer parameters  $n_1$ ,  $n_2$ ,  $n_3$ , and  $n_4$  in the switch equations, (3.3) and (3.4).

$$0 = OS1 \cdot \frac{\partial^{n_2} I}{\partial t^{n_2}} + (1 - OS1) \cdot \frac{\partial^{n_1} U}{\partial t^{n_1}}$$

(3.3)

$$0 = OS2 \cdot \frac{\partial^{n_4} I}{\partial t^{n_4}} + (1 - OS2) \cdot \frac{\partial^{n_3} U}{\partial t^{n_3}}$$

(3.4)

such that the two modified switch equations show up in two separate, independent algebraic loops. Unfortunately for the example circuit at hand, these parameters cannot be determined in an easy way. So far, no rules have been derived that would allow us to determine the smallest possible values for the four unknown parameters.

#### 3.3 An Inductive Approach

Since the example model description contains only two switch equations and the DAE index changes in the range from zero to two depending on the four possible switch positions, the first approach was an inductive trial and error method. In each step, values were chosen for the four parameters  $n_1$  to  $n_4$ , and the equations were modified accordingly. Then the corresponding determinant of the resulting equation system was determined using Dymola. It was subsequently inspected for singularities. From the knowledge of the singular cases for the given parameter values, a new set of hopefully better suited parameter values was chosen, and the process was repeated. Unfortunately, no progress was made in this manner. Each chosen parameter set resulted in a singularity in at least one of the four cases.

#### 3.4 The Permutation Approach

As the solution could not be found through trial and error, a more structured approach was called for. The process of selecting the parameter vector was made more systematic. First, all permutations up to order one, which result in  $n_1$ ,  $n_2$ ,  $n_3$ ,  $n_4 \in \{0, 1\}$ , i.e.,  $2^4 = 16$  possibilities, were examined. Thereafter all permutations up to order two, resulting in  $n_1$ ,  $n_2$ ,  $n_3$ ,  $n_4 \in \{0, 1, 2\}$ , i.e.,  $3^4 = 81$  possibilities, were investigated. Of course, these 81 possibilities include only 65 new possibilities as well as the 16 previously investigated possibilities. Unfortunately, this approach did not improve the result at all. The simulation would still only work in a maximum of three out of the four cases. However, through examining the dependence graphs associated with these possibilities, an important first result was achieved. If the two switches showed up in a single algebraic loop, the description always contained a singularity in two cases. If only one switch equation was contained in an algebraic loop, there was only a singularity in one case. This led to the following extension of the requirements for the switch equation:

Choosing the position of a switch must not determine variables that are part of the algebraic system in which another switch equation is contained.

This concludes that a system of equations containing n switches needs at least n independent algebraic loops, each containing a single switch equation. These loops can only be interconnected in such a manner that the connecting leaves cannot be determined prior to the calculation of the loop variables using the matrix solver.

This concept is physically intuitive, as replacing a switch in a model with either an open or a short circuit, should not influence the remaining circuit at all. Replacing a switch corresponds to fixing the value of one discrete switch variable, which should not determine any other switch variables. The switch variables are expected to be independent of each other.

#### 3.5 The Direct Approach

After all the trials of the permutation approach, including some really promising ones, had failed, a search was initiated to find a method to examine what was going wrong in all the previous attempts at modifying the switch equations. In this search for the right tool to examine the modification problem, the dependence graphs appeared to be the most useful tool. Several dependence graphs were examined in full detail. This was quite cumbersome, since it involved several sets of the equations. These sets included the equations from zeroth up to the highest differential order included in a modification of the switch equation. For example in the case of  $n_1 = 1$ ,  $n_2 = 2$ ,  $n_3 = 4$ , and  $n_4 = 3$ , which was thought to be close to the solution. Five sets of equations were involved including the zeroth, first, second, third, and fourth order derivatives, and thus, already  $5 \cdot 9 + 2 = 47$  equations. This case was thought to be promising, because it should create one loop containing the diode  $D_1$  and the inductor  $L_1$ , and a second loop containing the diode  $D_2$  together with the capacitor  $C_1$ . However, neither this nor any other parameter sets created the necessary algebraic loops to guarantee the independence of the discrete switch variables. Yet, examining this case in full detail resulted in a starting point for formulating necessary conditions for the four unknowns  $n_1$ ,  $n_2$ ,  $n_3$ , and  $n_4$ . The two expected loops were not created because of two facts:

- Variables of one proposed loop, or lower order derivatives of variables contained in the proposed loop, had connections to variables forming the second proposed loop. Thus, solving the first algebraic loop resulted in the knowledge of elements of the second loop through the connecting equations, thereby destroying the second algebraic loop.

- Loops were not even created, because a used equation contained a surplus undetermined variable that was not part of the algebraic loop. Hence, the algebraic system was not completely determined.

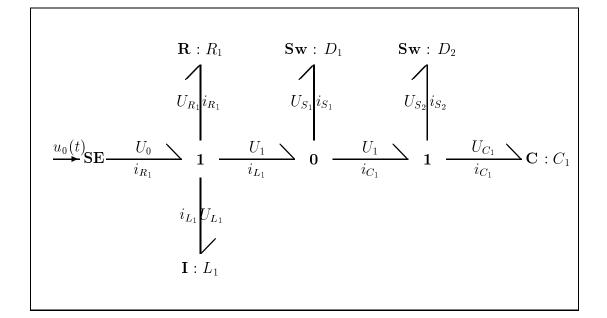

The conditions were developed to prevent exactly these two ways of destroying the algebraic loops for each switch element using the modified dependence graph. The necessary dependence graphs were constructed using the bond graph notation. As a reminder, the detailed bond graph for the example circuit is shown in Fig. 3.5.

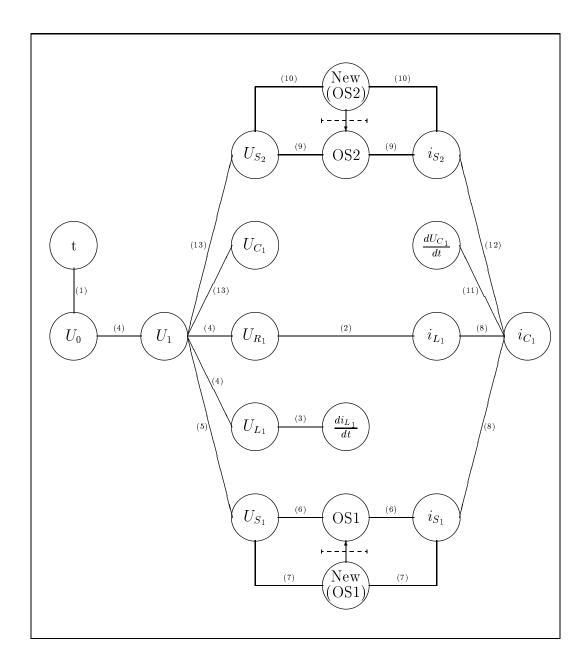

From this bond graph, we can easily determine the following set of equations, where the same variables as in Fig. 3.1 show up. The only additional variable is the

Figure 3.5: Detailed Bond Graph for Example 1

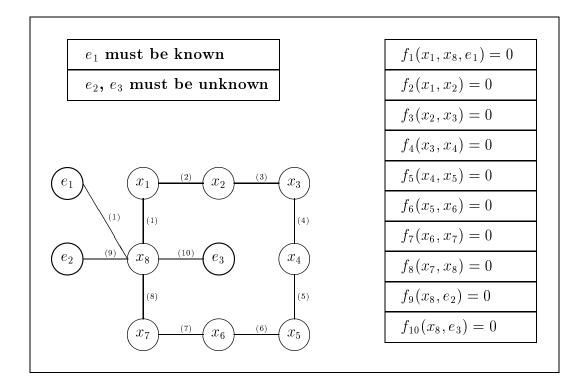

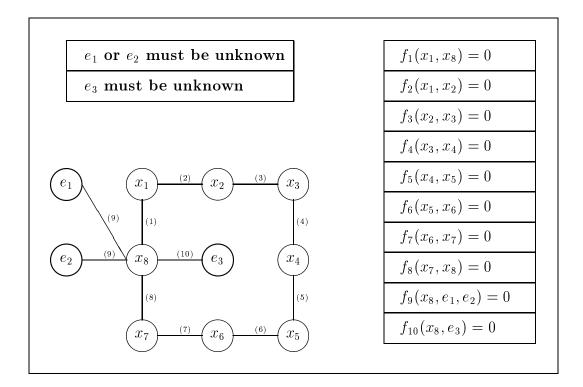

potential  $U_1$  of the node connecting the two diodes and the inductor. The identity  $i_{R_1} = i_{L_1}$  is already used to replace  $i_{R_1}$  in the set of equations. The identities in equations  $f_5$  and  $f_{12}$  were kept in that form, because they contain variables also contained in the switch equations. OS1 and OS2 in equations  $f_6$  and  $f_9$  are the abbreviated discrete switch variables that determine the positions of the switches. These positions are determined through equations  $f_7$  and  $f_{10}$  using the result of an earlier integration step or an initial condition. The operator, New(.), expresses the difference in time instants, and the complete equations  $f_7$  and  $f_{10}$  are representing the diode characteristic. This equation system is shown in the modified dependence

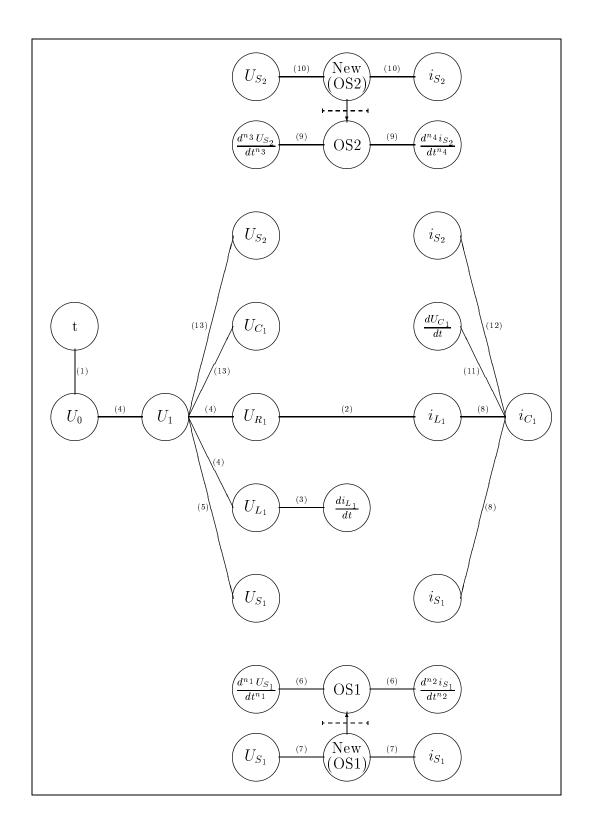

graph notation in Fig. 3.6

$$\begin{split} U_0 - u_0(t) &= f_1 = 0 \\ U_{R_1} - R_1 \cdot i_{L_1} &= f_2 = 0 \\ -U_{L_1} + L_1 \cdot \frac{\partial i_{L_1}}{\partial t} &= f_3 = 0 \\ U_0 - U_{R_1} - U_1 - U_{L_1} &= f_4 = 0 \\ U_1 - U_{S_1} &= f_5 = 0 \\ OS1 \cdot \frac{\partial^{n_2} i_{S_1}}{\partial t^{n_2}} + (1 - OS1) \cdot \frac{\partial^{n_1} U_{S_1}}{\partial t^{n_1}} &= f_6 = 0 \\ \text{if } [\operatorname{not}(U_{S_1} > 0) \text{ and } \operatorname{not}(i_{S_1} > 0)] \text{ then } 1 \text{ else } 0 - New(OS1) = f_7 = 0 \\ i_{L_1} - i_{S_1} - i_{C_1} &= f_8 = 0 \\ OS2 \cdot \frac{\partial^{n_4} i_{S_2}}{\partial t^{n_4}} + (1 - OS2) \cdot \frac{\partial^{n_3} U_{S_2}}{\partial t^{n_3}} &= f_9 = 0 \\ \text{if } [\operatorname{not}(U_{S_2} > 0) \text{ and } \operatorname{not}(i_{S_2} > 0)] \text{ then } 1 \text{ else } 0 - New(OS2) = f_{10} = 0 \\ -i_{C_1} + C_1 \cdot \frac{\partial U_{C_1}}{\partial t} &= f_{11} = 0 \\ i_{C_1} - i_{S_2} &= f_{12} = 0 \\ U_1 - U_{S_2} - U_{C_1} &= f_{13} = 0 \end{split}$$

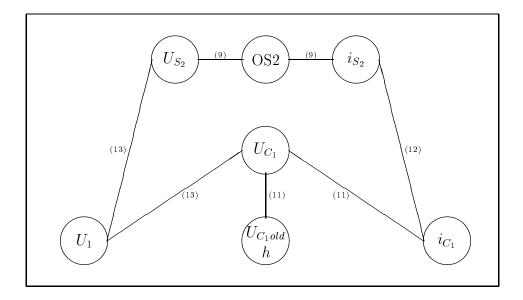

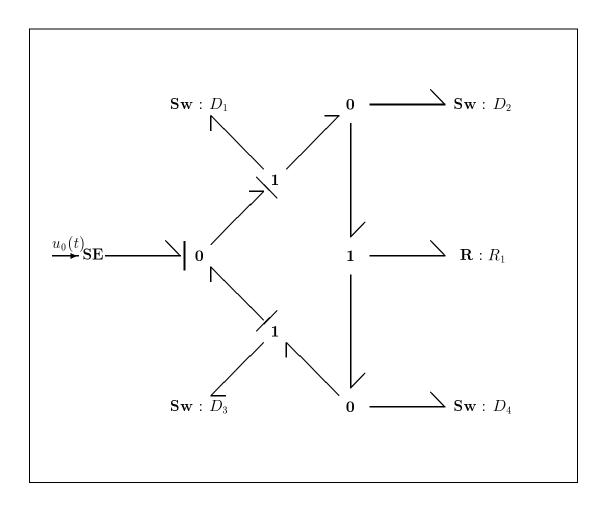

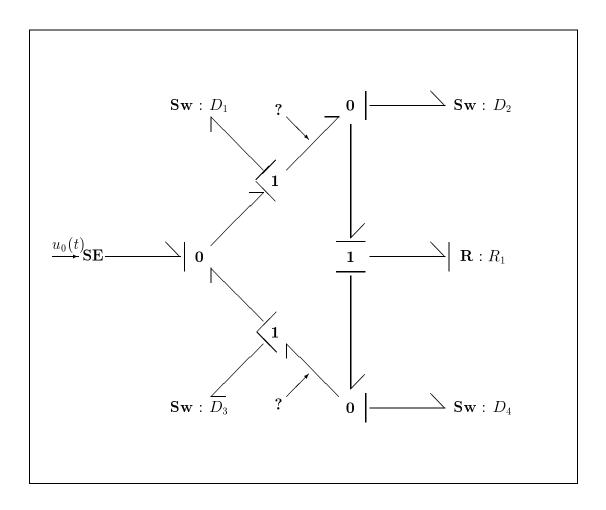

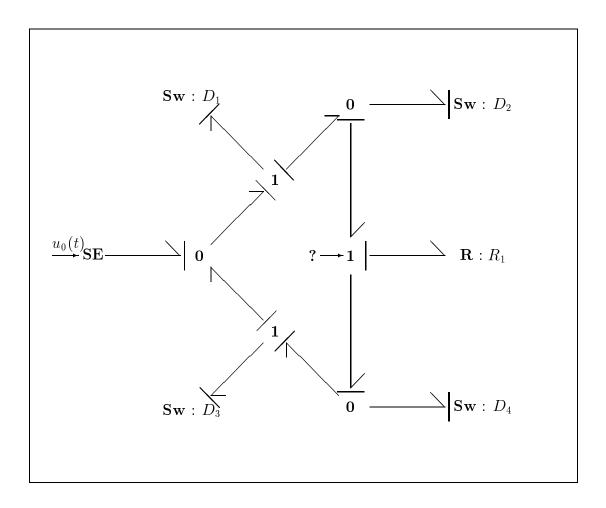

Fig. 3.6 is composed of three parts, a switch part at the bottom, a switch part at the top, and a general equations part in the middle section. Both the bottom and top parts consist of a switch equation and an equation to express the diode characteristic. The dashed line crossing the arrow represents the extraordinary character

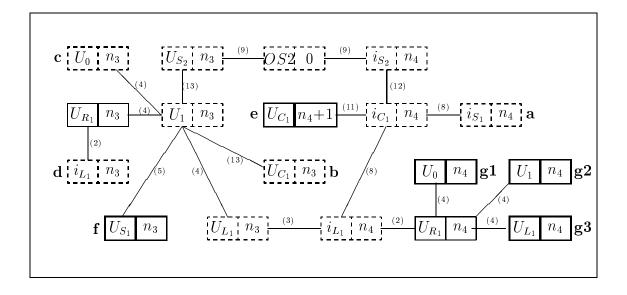

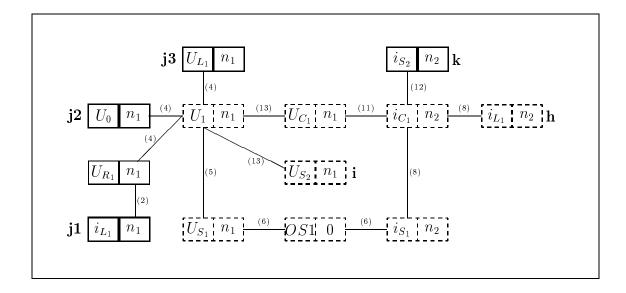

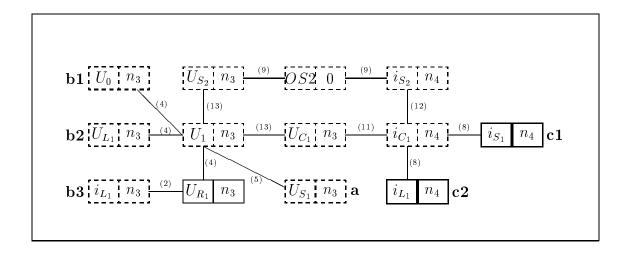

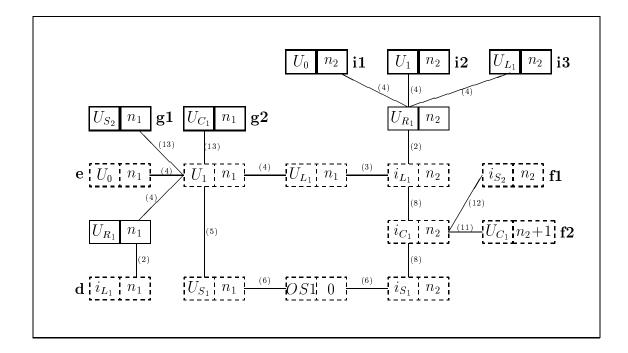

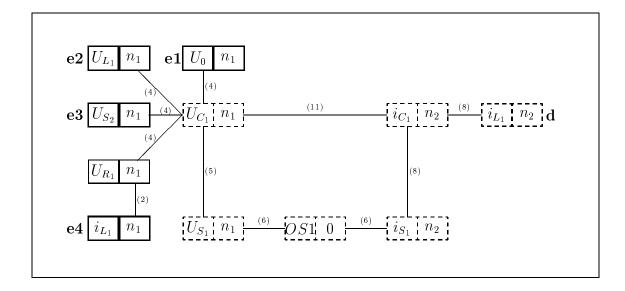

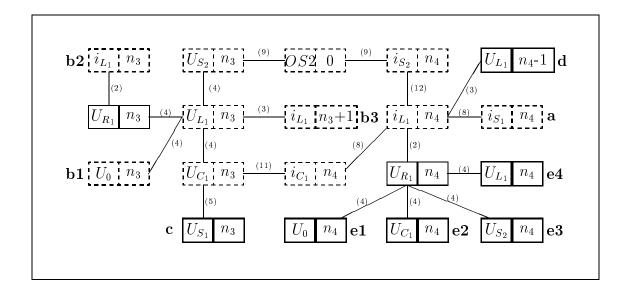

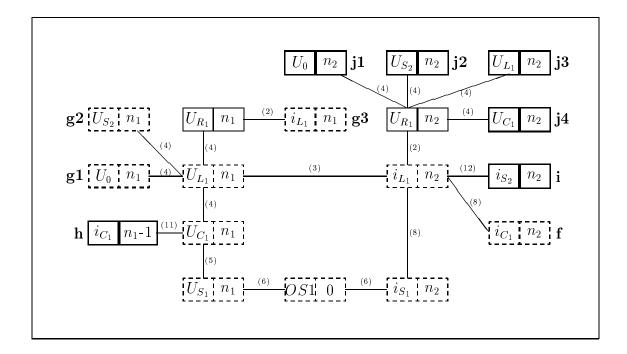

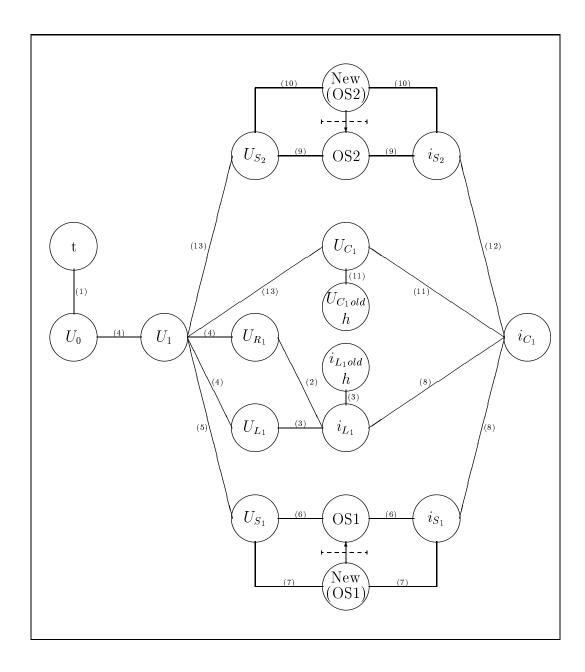

Figure 3.6: Dependence Graph for Example 1