## Efficient Cache Coherence Support for Near-Data Accelerators

Amirali Boroumand, Saugata Ghose, Minesh Patel, Hasan Hassan, Brandon Lucia, Rachata Ausavarungnirun, Kevin Hsieh, Nastaran Hajinazar, Krishna Malladi, Hongzhong Zheng, Onur Mutlu

For Connected Components application, only **5.1%** of the CPU accesses **collide** with NDA accesses

CPU threads rarely update the same data that an NDA is actively working on

1<sup>st</sup> key observation: CPU threads often concurrently access the same region of data that NDA kernels are accessing which leads to significant data sharing

(2) NDA applications generate NDA a large amount of off-chip data movement

It is impractical to use traditional coherence protocols

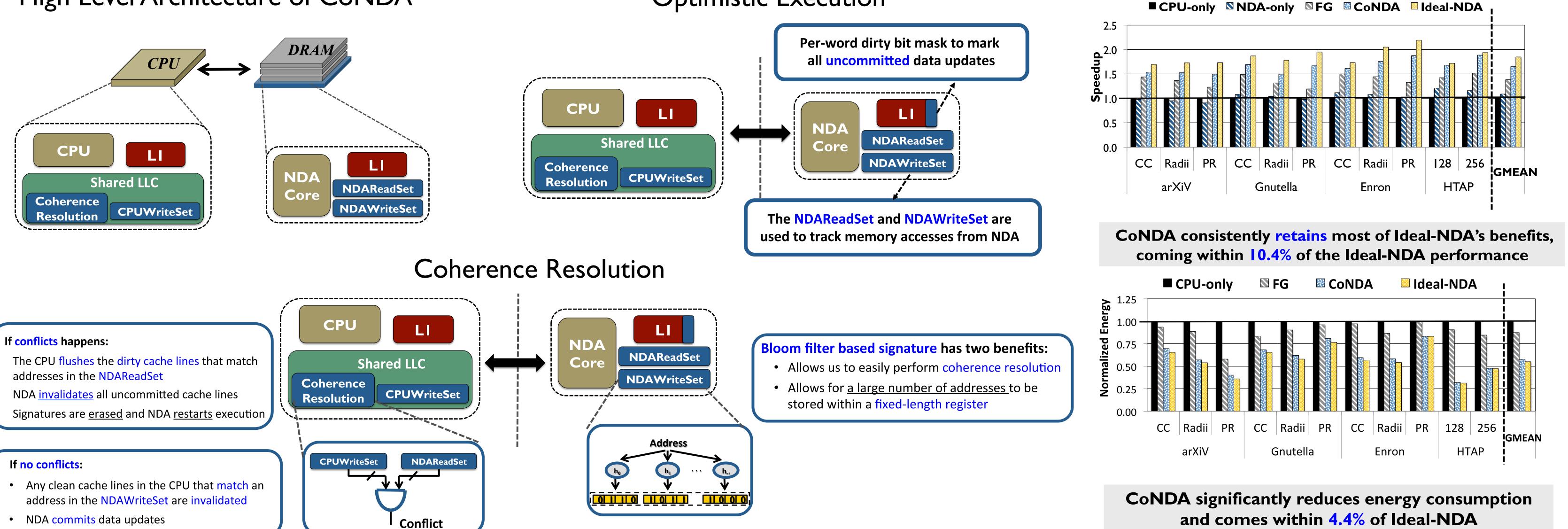

## CoNDA

Analytics

$\langle \langle \rangle \rangle$

NDA

Data Sharing

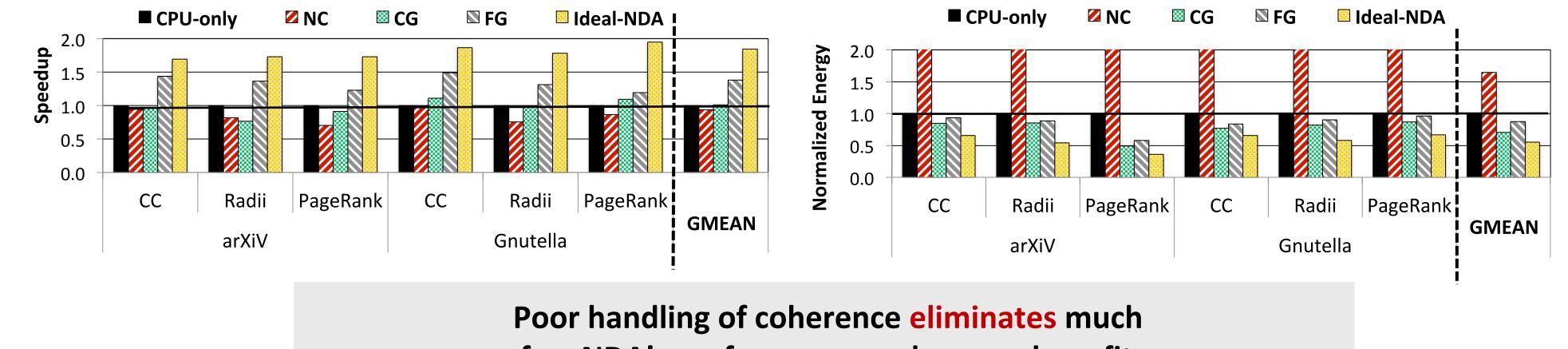

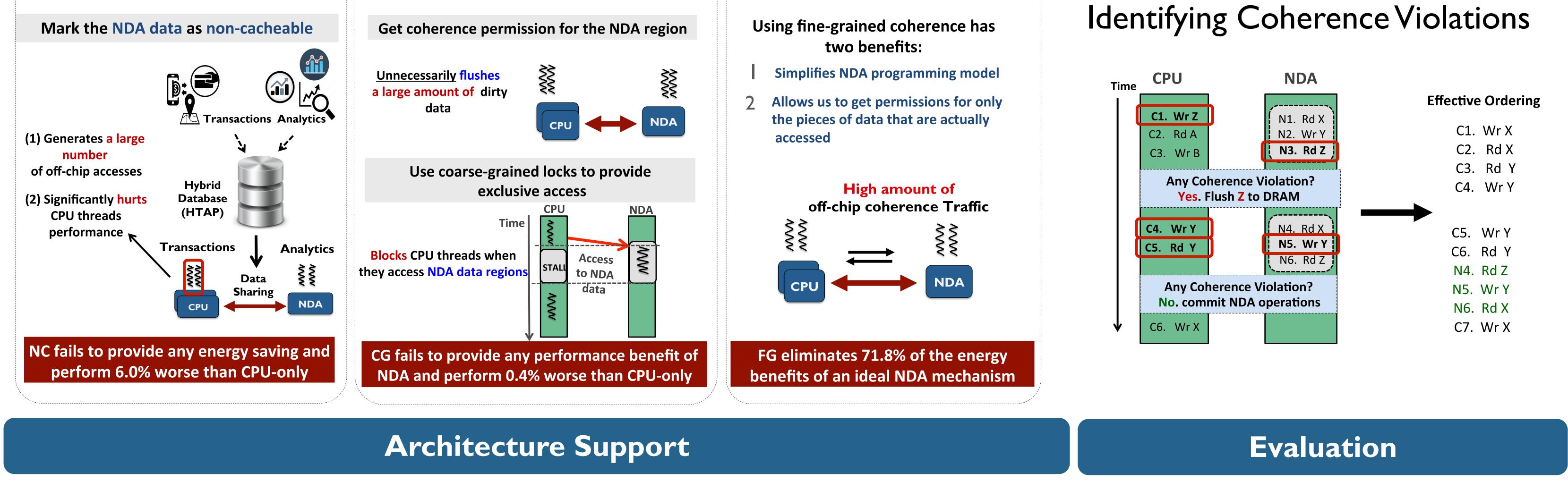

## **Analysis of Existing Coherence Mechanisms**

of an NDA's performance and energy benefits

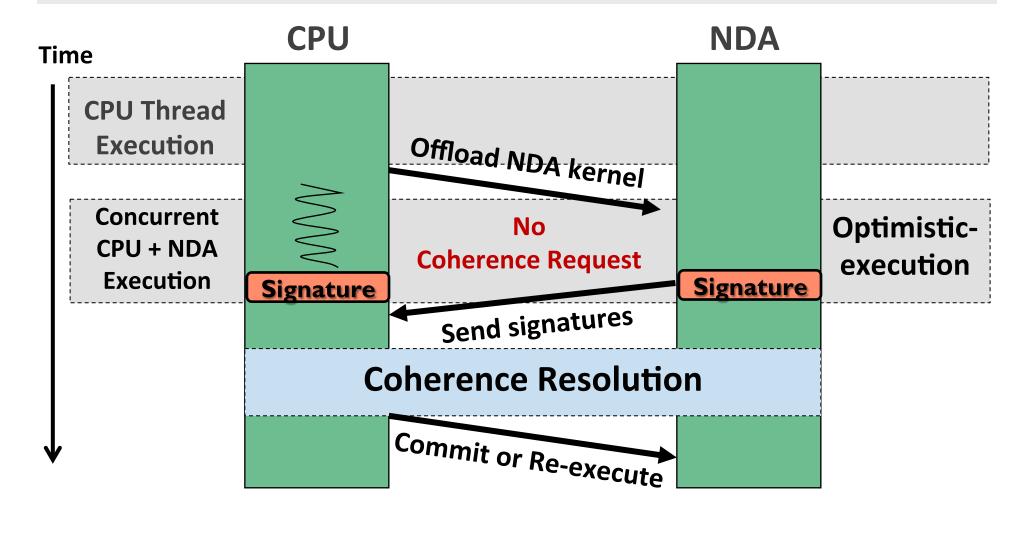

We propose CoNDA, a mechanism that uses optimistic NDA execution to avoid unnecessary coherence traffic

**Non-Cacheable Approach Coarse-Grained Coherence**

**Fine-Grained Coherence**

Transactions

$\langle \langle \rangle \rangle$

CPU

High Level Architecture of CoNDA

DRAM

**Optimistic Execution**

Per-word dirty bit mask to mark all uncommitted data updates