### Analysis and Modeling of Collaborative Execution Strategies for Heterogeneous CPU-FPGA Architectures

Sitao Huang<sup>1</sup>, Li-Wen Chang<sup>2</sup>, Izzat El Hajj<sup>3</sup>, <u>Simon Garcia De Gonzalo</u><sup>1</sup>, Juan Gómez-Luna<sup>4</sup>, Sai Rahul Chalamalasetti<sup>5</sup>, Mohamed El Hadedy<sup>6</sup>, Dejan Milojicic<sup>5</sup>, Onur Mutlu<sup>4</sup>, Deming Chen<sup>1</sup>, Wen-mei Hwu<sup>1</sup>

<sup>1</sup>University of Illinois at Urbana-Champaign, USA

<sup>2</sup>Microsoft, USA

<sup>3</sup>American University of Beirut, Lebanon

<sup>4</sup>ETH Zürich, Switzerland

<sup>5</sup>Hewlett Packard Labs, USA

<sup>6</sup>California State Polytechnic University, Pomona, USA

**ILLINOIS** Electrical & Computer Engineering COLLEGE OF ENGINEERING

# Outline

- Introduction to Collaborative Computing

- Analytical Models of Collaborative Computing

- Evaluation

- Evaluation platform

- Data partitioning vs. task partitioning

- Impact of kernel replication

- Key Insights

- Chai Benchmarks for CPU-FPGA Systems

### **Collaborative Computing**

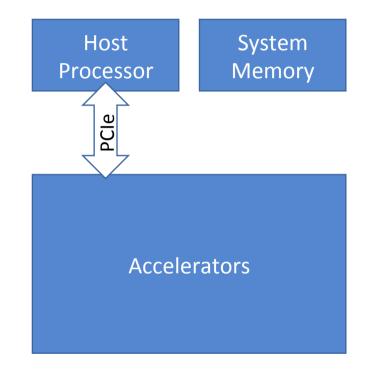

• Traditionally, accelerators (GPUs, FPGAs, etc.) have been used as *offload* engines

Host processor *offloads* computation tasks to accelerators

### **Collaborative Computing**

- Traditionally, accelerators (GPUs, FPGAs, etc.) have been used as offload engines

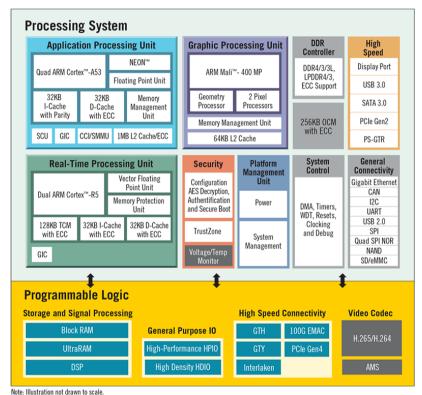

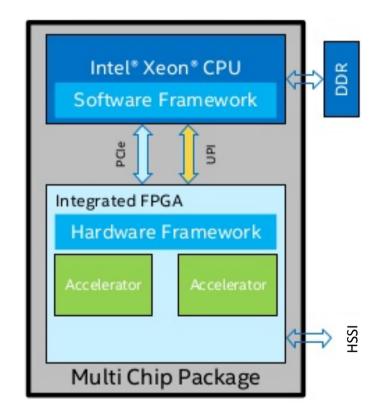

- Heterogeneous architectures moving towards tighter integration

- Unified memory

- System-wide atomics

Xilinx Zynq UltraScale+ MPSoC

# **Collaborative Computing**

- Traditionally, accelerators (GPUs, FPGAs, etc.) have been used as offload engines

- Heterogeneous architectures moving towards tighter integration

- Unified memory

- System-wide atomics

- Tighter integration allows finegrained collaboration

**Key challenge**: identify the best CPU-FPGA collaboration strategy

Intel Xeon + FPGA Integrated Platform (MCP)

## **Integrated Heterogeneous Systems**

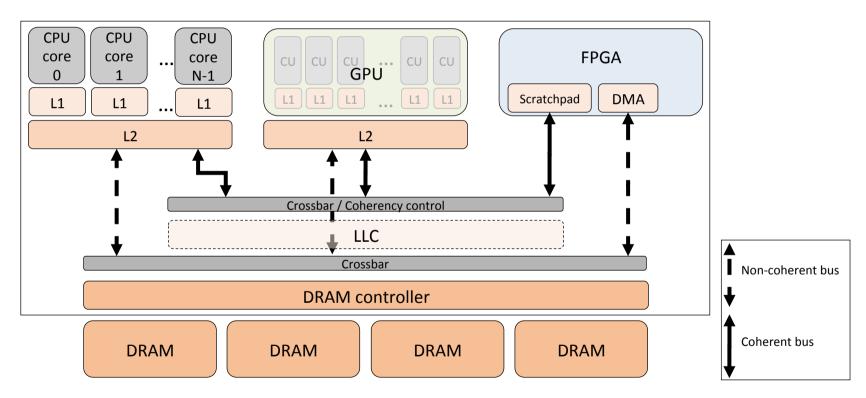

Our vision of an integrated heterogeneous system:

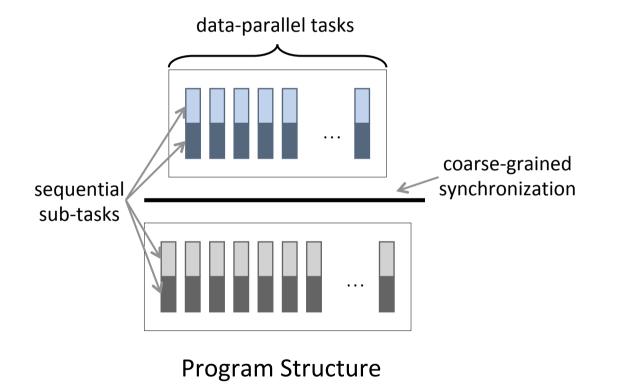

# **Collaborative Patterns**

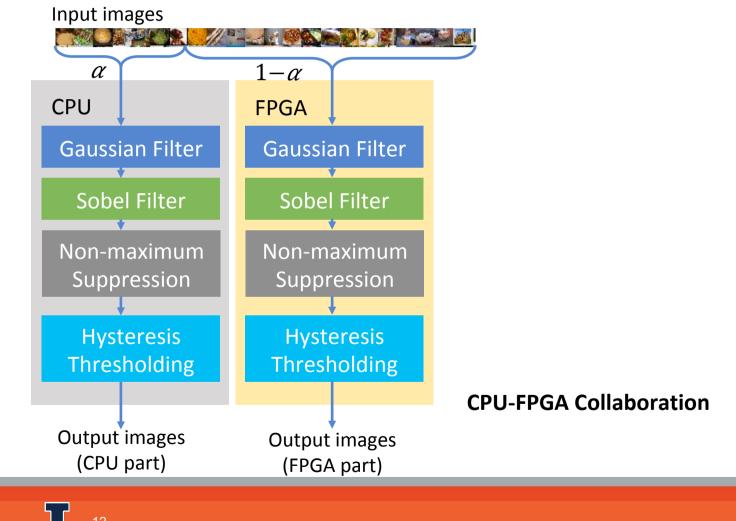

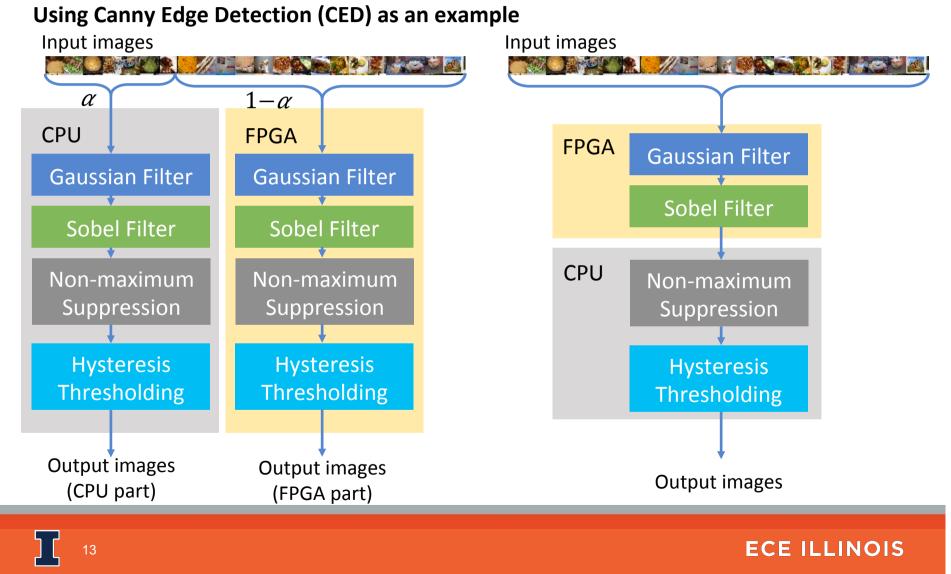

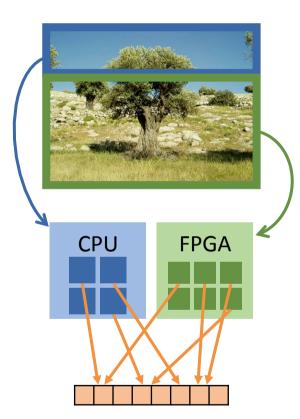

#### Data Partitioning

## **Collaborative Patterns**

# **Collaborative Patterns**

# **Data Partitioning**

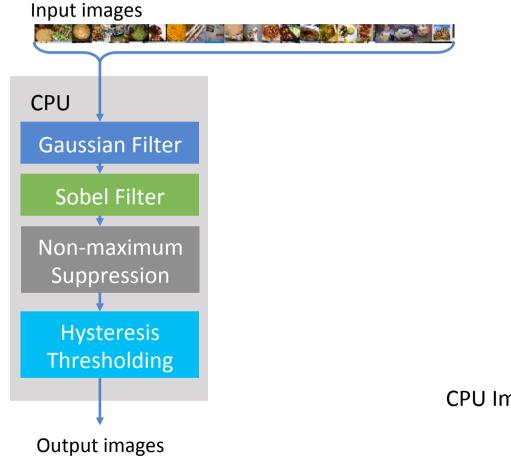

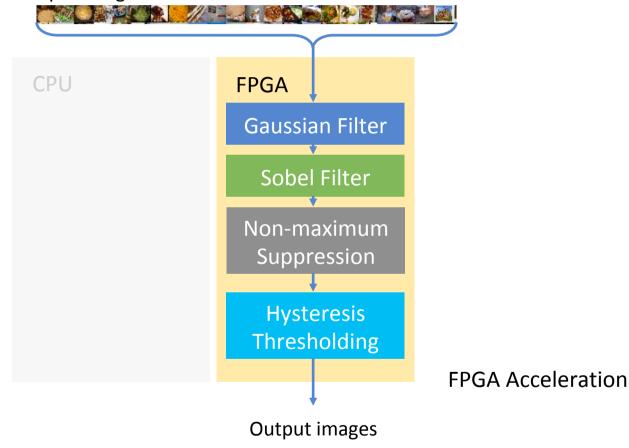

#### Using Canny Edge Detection (CED) as an example

CPU Implementation

# **Data Partitioning**

#### Using Canny Edge Detection (CED) as an example

#### Input images

# **Data Partitioning**

#### Using Canny Edge Detection (CED) as an example

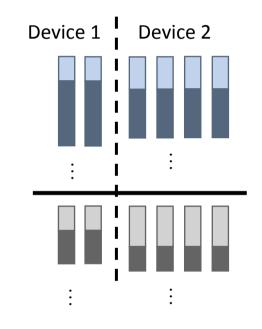

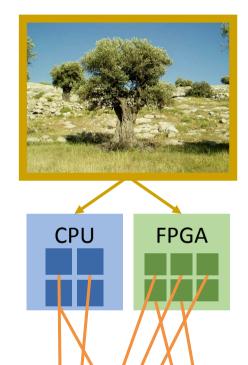

# Data Partitioning vs. Task Partitioning

### Another Data Partitioning Example: Image Histogram

Input pixels distributed across devices

Output bins distributed across devices

- *N*: Number of data parallel tasks in the application

- $t \downarrow i$ , C: Execution time of sub-task i by a CPU worker

- $t \downarrow i, F$ : Execution time of sub-task i by an FPGA worker

- *w\lambda C* : Number of available CPU workers

- $w \downarrow F$ : Number of available FPGA workers

- $\beta$ : Distribution and aggregation overhead factor

- *α*: Fraction of data parallel tasks assigned to CPU

- N: Number of data parallel tasks in the application

- $t\downarrow i$ , C: Execution time of sub-task i by a CPU worker

- $t\downarrow i, F$ : Execution time of sub-task i by an FPGA worker

- $W \downarrow C$ : Number of available CPU workers

Data partitioninger of available FPGA workare execution time

• B: Distribution and aggregation overhead factor The total execution time is

time Total FPGA execution time n) (sequential execution)

Data partitioning

**FPGA**

CPU

•  $\alpha_{\text{Fraction of data parallel tasks assigned to GPU$  $<math>t \downarrow data, total = \beta \downarrow data \cdot \max(\alpha N \sum i \uparrow = t \downarrow i, C / w \downarrow C ,$  $(1 - \alpha) N \sum i \uparrow = t \downarrow i, F / w \downarrow F )$

- N: Number of data parallel tasks in the application

- $t\downarrow i$ , C: Execution time of sub-task i by a CPU worker

- $t\downarrow i, F$ : Execution time of sub-task i by an FPGA worker

- $W \downarrow C$ : Number of available CPU workers

### Data partitioninger of available FPGA workers

17

- $\beta$ : Distribution and aggregation overhead factor The total execution time is

- $\alpha$ : Fraction of data parallel tasks assigned to CPU  $t \downarrow data, total = \beta \downarrow data - \max(\alpha N \sum i 1 = m \downarrow i, C / w \downarrow C , (1 - \alpha) N \sum i 1 = t \downarrow i, F / w \downarrow F )$

Fixing all the variables except  ${\mathcal A}$ , the optimal  ${\mathcal A}$  (global minimum point) is

$$\alpha \widehat{1} * = \sum i \widehat{1} = t \downarrow i \psi F K \phi i \psi F F \phi M F F \phi M F$$

- N: Number of data parallel tasks in the application

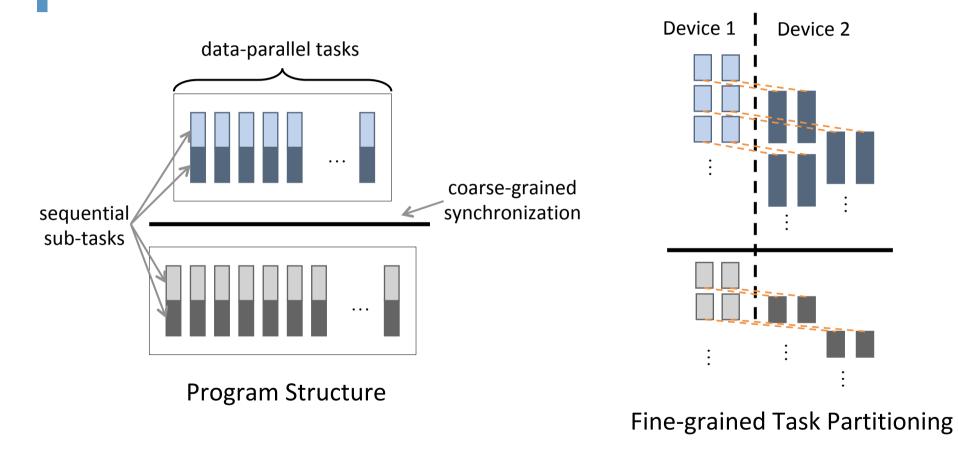

- $t\downarrow i$ , C: Execution time of sub-task i by a CPU worker

- $t\downarrow i$ , F: Execution time of sub-task  $\dot{l}$  by an FPGA worker

- $w \downarrow C$ : Number of available CPU workers

- $W \downarrow F$ : Number of available FPGA workers

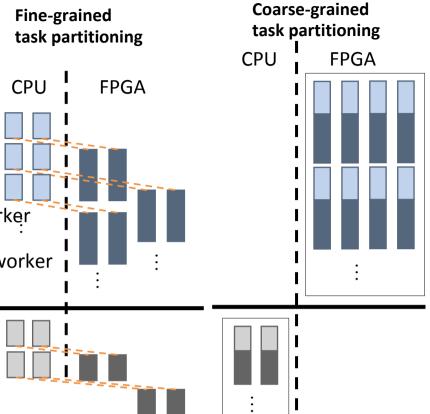

Fing grained task no titien overhead factor The total execution time is

**ECE ILLINOIS**

$t\downarrow task, total = \beta \downarrow task N \cdot max(\sum i \in S \downarrow C \uparrow = t \downarrow i, C / w \downarrow C),$  $\sum_{i \in S \downarrow F} \uparrow = f_{i} F_{task}$

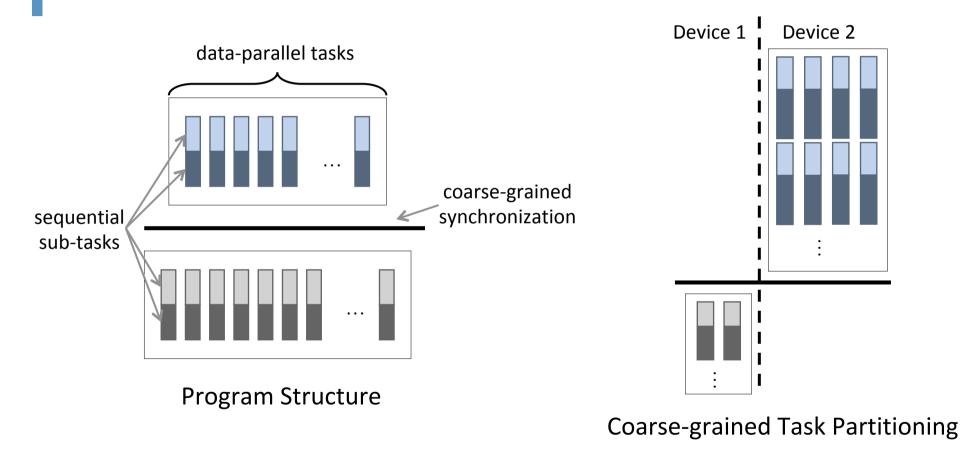

#### **Coarse-grained task partitioning**

The total execution time is

$S \downarrow F \uparrow = t \downarrow i, F / w \downarrow F$ )

# **Chai Benchmark Suite**

Chai: Collaborative Heterogeneous Applications for Integrated-architectures

• Chai benchmark suite:

### chai-benchmarks.github.io

- 14 benchmarks covers data partitioning, fine-grain task partitioning, and coarse-grain task partitioning patterns

- OpenCL, C++ AMP, and CUDA versions

- Unified memory and system-wide atomic versions and traditional discrete architecture versions

### **Evaluated Chai Benchmarks**

| Benchmark | Description                   | Strategy          |

|-----------|-------------------------------|-------------------|

| CED-D     | Canny Edge Detection          | Data Partitioning |

| CED-T     | Canny Edge Detection          | Task Partitioning |

| RSC-D     | Random Sample Consensus       | Data Partitioning |

| RSC-T     | Random Sample Consensus       | Task Partitioning |

| BS        | Bézier Surface                | Data Partitioning |

| HSTO      | Image Histogram               | Data Partitioning |

| SSSP      | Single-Source Shortest Path   | Task Partitioning |

| TQ        | Task Queue System (Synthetic) | Task Partitioning |

| ТQН       | Task Queue System (Histogram) | Task Partitioning |

OpenCL-D (OpenCL discrete architecture) versions of these benchmarks are used.

### **Evaluation Platforms**

|                        | Platform A            | Platform B            |

|------------------------|-----------------------|-----------------------|

| FPGA Board             | Terasic DE5-Net       | Nallatech 510T        |

| FPGA Chip              | Intel Stratix V GX    | Intel Arria 10 GX     |

| <b>On-Board Memory</b> | 4 GB (DDR3)           | 8 GB (DDR4)           |

| Host CPU               | Intel Xeon E3-1240 v3 | Intel Xeon E5-2650 v3 |

| Host Memory            | 8 GB (DDR3)           | 96 GB (DDR4)          |

| Interface              | PCle gen3.0 x8        | PCIe gen3.0 x8        |

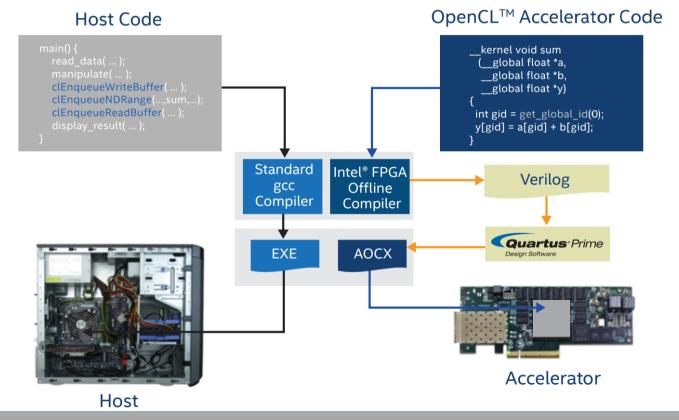

## **Intel OpenCL SDK for FPGA**

• Intel OpenCL SDK for FPGA is used to compile and synthesize host executable and FPGA design

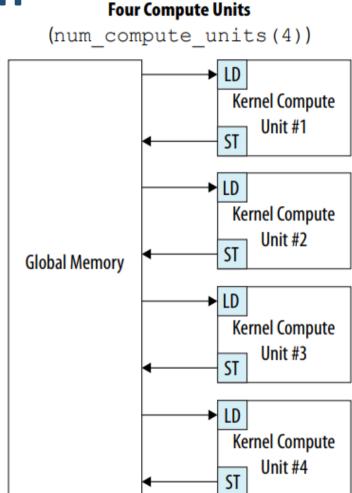

# **Compute Unit Replication**

- OpenCL kernels are synthesized to compute units on FPGA

- The compute units on FPGA can be replicated by adding num\_compute\_units attribute in the OpenCL kernel code

- num\_compute\_units attribute modifies the number of compute units to which work-groups can be scheduled, which also modifies the number of times a kernel accesses global memory

- We evaluate the impact of compute unit replication

Intel<sup>®</sup> FPGA SDK for OpenCL<sup>™</sup> Best Practices Guide

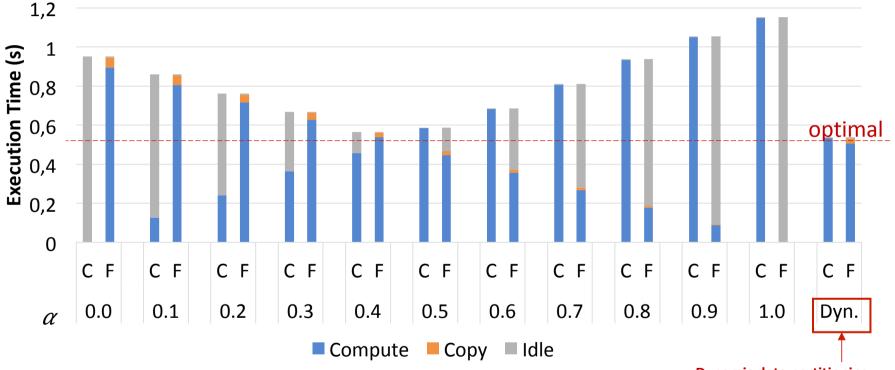

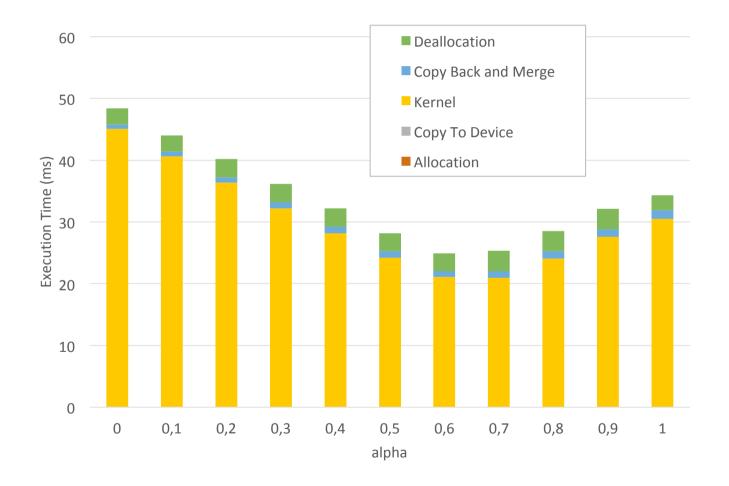

# **Evaluation: Canny Edge Detection** (Data Partitioning)

- C: CPU; F: FPGA

- $\alpha$ : Fraction of data parallel tasks assigned to CPU

**Dynamic data partitioning:** assigning batch of data parallel tasks to idle devices, achieving dynamic workload balance

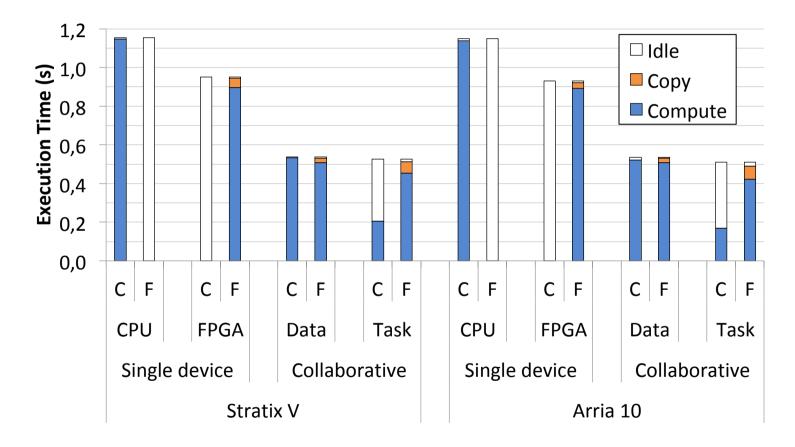

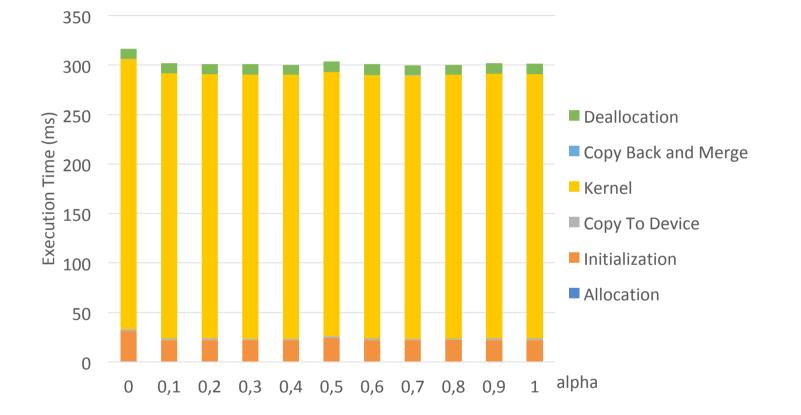

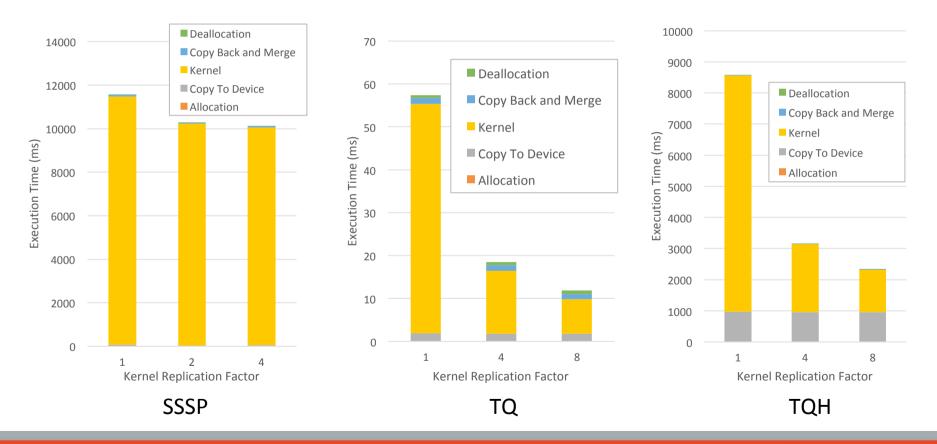

### **Evaluation: Canny Edge Detection** (Data Partitioning and Task Partitioning)

### **Evaluation: Random Sample Consensus** (Data Partitioning and Task Partitioning)

### **Bézier Surface (BS, Data Partitioning)**

### Histogram (HSTO, Output Data Partitioning)

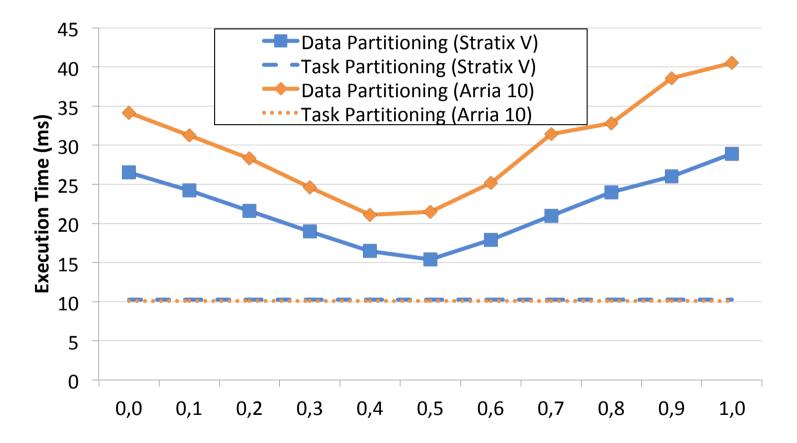

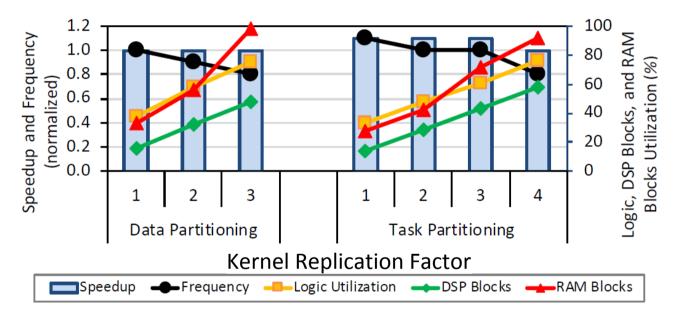

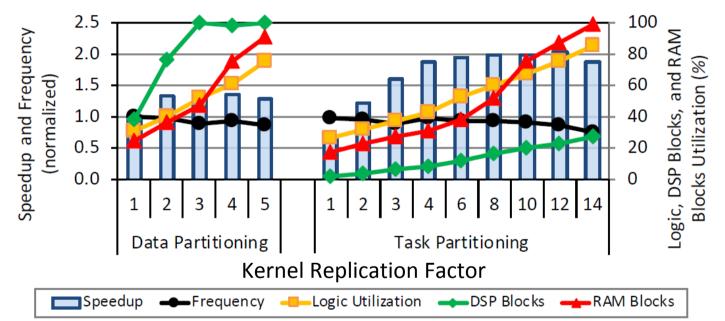

### **Kernel Replication – Data Partitioning**

We evaluated the performance under different kernel replication factors.

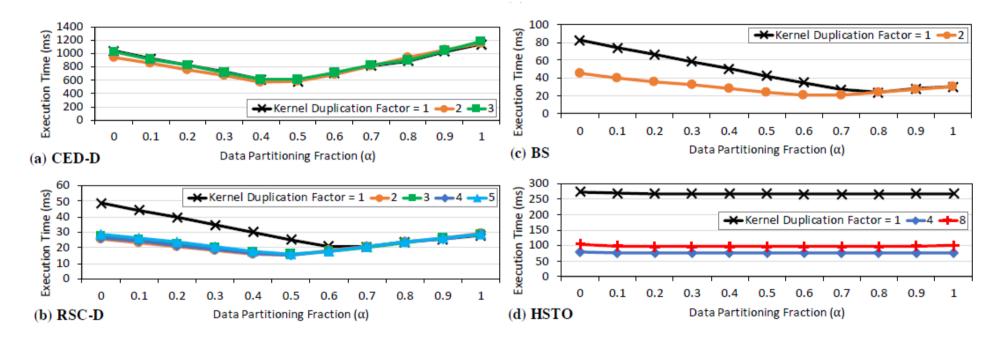

### **Kernel Replication – Task Partitioning**

We evaluated the performance under different kernel replication factors.

# **Impact of Replication**

#### **Canny Edge Detection**

- Replication factor for this application has little impact on performance

- Further profiling reveals the reason of performance saturation is the saturation of the memory bandwidth

ECE ILLINOIS

Task partitioning can afford a larger replication factor

## **Impact of Replication**

#### Random Sample Consensus

- Replication improves performance of this application

- Bounding resource: DSP blocks

- Task partitioning releases the pressure on DSP block and thus can afford a larger replication factor

# **Key Insights**

- Collaborative execution is beneficial

- Data partitioning requires careful choice of partitions to provide the highest performance

- Task partitioning generally enables more kernel replication on the FPGA than data partitioning

- Data partitioning inflicts less burden on programmers and has less communication overhead than task partitioning

- OpenCL stack provides a convenient programming model while there is still room for better programmability and higher performance

# **Chai Project**

- Papers:

- Analysis and Modeling of Collaborative Execution Strategies for Heterogeneous CPU-FPGA Architectures. *ICPE'19.* (this work)

- Collaborative Computing for Heterogeneous Integrated Systems. ICPE'17 Vision Track.

- Chai: Collaborative Heterogeneous Applications for Integratedarchitectures. *ISPASS'17*.

- Chai Benchmark Suite:

- <u>Website</u>: chai-benchmarks.github.io

- <u>Code</u>: github.com/chai-benchmarks/chai

- <u>Online Forum</u>: groups.google.com/d/forum/chai-dev

### Analysis and Modeling of Collaborative Execution Strategies for Heterogeneous CPU-FPGA Architectures

Sitao Huang<sup>1</sup>, Li-Wen Chang<sup>2</sup>, Izzat El Hajj<sup>3</sup>, <u>Simon Garcia De Gonzalo</u><sup>1</sup>, Juan Gómez-Luna<sup>4</sup>, Sai Rahul Chalamalasetti<sup>5</sup>, Mohamed El Hadedy<sup>6</sup>, Dejan Milojicic<sup>5</sup>, Onur Mutlu<sup>4</sup>, Deming Chen<sup>1</sup>, Wen-mei Hwu<sup>1</sup>

<sup>1</sup>University of Illinois at Urbana-Champaign, USA

<sup>2</sup>Microsoft, USA

<sup>3</sup>American University of Beirut, Lebanon

<sup>4</sup>ETH Zürich, Switzerland

<sup>5</sup>Hewlett Packard Labs, USA

<sup>6</sup>California State Polytechnic University, Pomona, USA

**ILLINOIS** Electrical & Computer Engineering COLLEGE OF ENGINEERING