# Pythia

### A Customizable Hardware Prefetching Framework Using Online Reinforcement Learning

<u>Rahul Bera</u>, Konstantinos Kanellopoulos, Anant V. Nori, Taha Shahroodi, Sreenivas Subramoney, Onur Mutlu

https://github.com/CMU-SAFARI/Pythia

## **Executive Summary**

- Background: Prefetchers predict addresses of future memory requests by associating memory access patterns with program context (called feature)

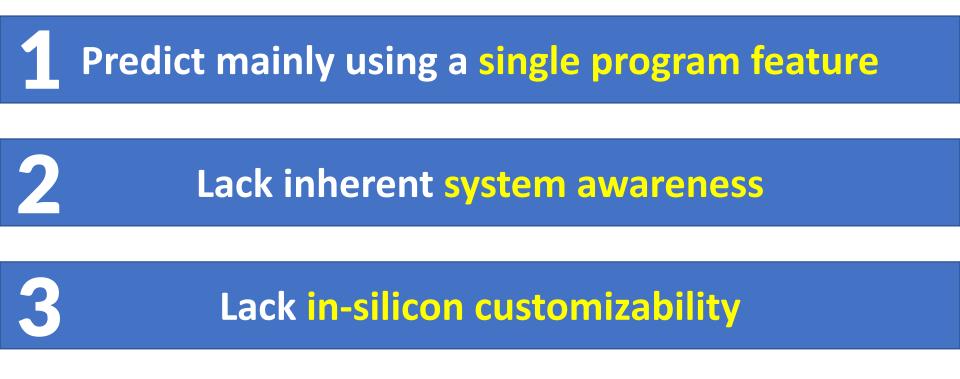

- **Problem**: Three key shortcomings of prior prefetchers:

- Predict mainly using a single program feature

- Lack inherent system awareness (e.g., memory bandwidth usage)

- Lack in-silicon customizability

- Goal: Design a prefetching framework that:

- Learns from multiple features and inherent system-level feedback

- Can be customized in silicon to use different features and/or prefetching objectives

- Contribution: Pythia, which formulates prefetching as reinforcement learning problem

- Takes adaptive prefetch decisions using multiple features and system-level feedback

- Can be customized in silicon for target workloads via simple configuration registers

- Proposes a realistic and practical implementation of RL algorithm in hardware

- Key Results:

SAFARI

- Evaluated using a wide range of workloads from SPEC CPU, PARSEC, Ligra, Cloudsuite

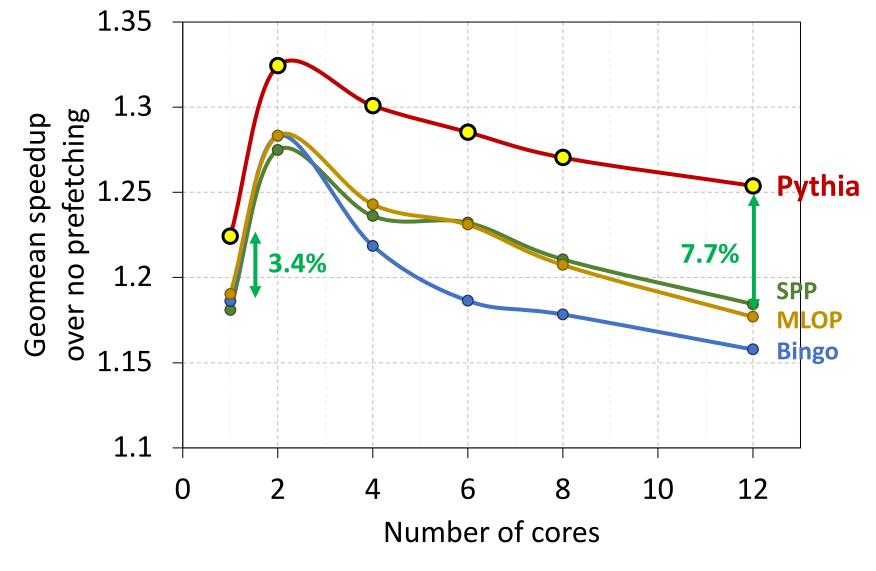

- Outperforms best prefetcher (in 1-core config.) by **3.4%**, **7.7%** and **17%** in 1/4/bw-constrained cores

- Up to 7.8% more performance over basic Pythia across Ligra workloads via simple customization

#### https://github.com/CMU-SAFARI/Pythia

# **Talk Outline**

### **Key Shortcomings of Prior Prefetchers**

### Formulating Prefetching as Reinforcement Learning

**Pythia: Overview**

**Evaluation of Pythia and Key Results**

Conclusion

# **Prefetching Basics**

- Predicts addresses of long-latency memory requests and fetches data before the program demands it

- Associates access patterns from past memory requests with program context information

### **Program Feature** → Access Pattern

### • Example program features

- Program counter (PC)

- Page number

- Page offset

- Cacheline delta

- ...

- Or a combination of these attributes

## **Key Shortcomings in Prior Prefetchers**

We observe three key shortcomings that significantly limit performance benefits of prior prefetchers

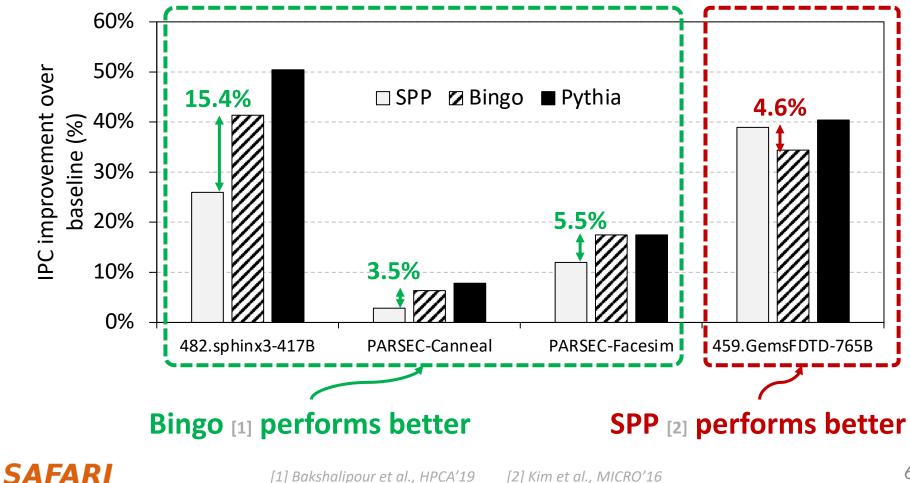

## (1) Single-Feature Prefetch Prediction

Provides good performance gains mainly on workloads where the feature-to-pattern correlation exists

## (1) Single-Feature Prefetch Prediction

Provides good performance gains mainly on workloads where the feature-to-pattern correlation exists

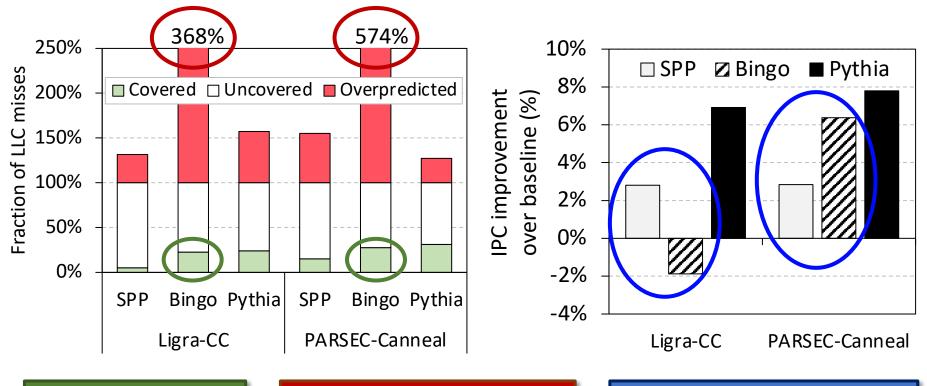

# (2) Lack of Inherent System Awareness

- Little understanding of **undesirable effects** (e.g., memory bandwidth usage, cache pollution, ...)

- Performance loss in **resource-constrained** configurations

Similar coverage

Lower overpredictions

Yet, lower performance

# (2) Lack of Inherent System Awareness

- Little understanding of **undesirable effects** (e.g., memory bandwidth usage, cache pollution, ...)

- Performance loss in **resource-constrained** configurations

# (3) Lack of In-silicon Customizability

• Feature **statically** selected at design time

SAFA

- **Rigid hardware** designed specifically to exploit that feature

- No way to change program feature and/or change prefetcher's objective in silicon

- Cannot adapt to a wide range of workload demands

## **Our Goal**

### A prefetching framework that can:

1.Learn to prefetch using multiple features and inherent system-level feedback information

2.Be **easily customized in silicon** to use different features and/or change prefetcher's objectives

## **Our Proposal**

# Pythia

# Formulates prefetching as a reinforcement learning problem

Pythia is named after the oracle of Delphi, who is known for her accurate prophecies https://en.wikipedia.org/wiki/Pythia

# **Talk Outline**

**Key Shortcomings of Prior Prefetchers**

### Formulating Prefetching as Reinforcement Learning

**Pythia: Overview**

### **Evaluation of Pythia and Key Results**

Conclusion

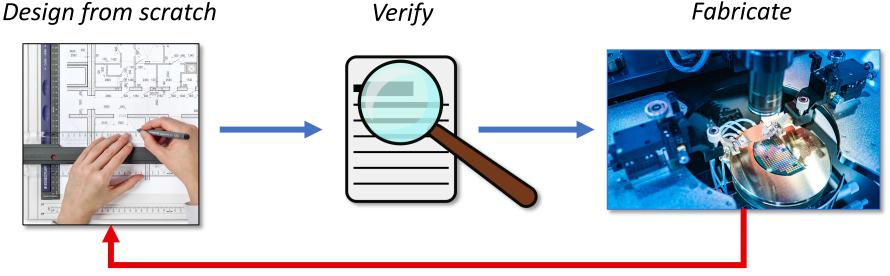

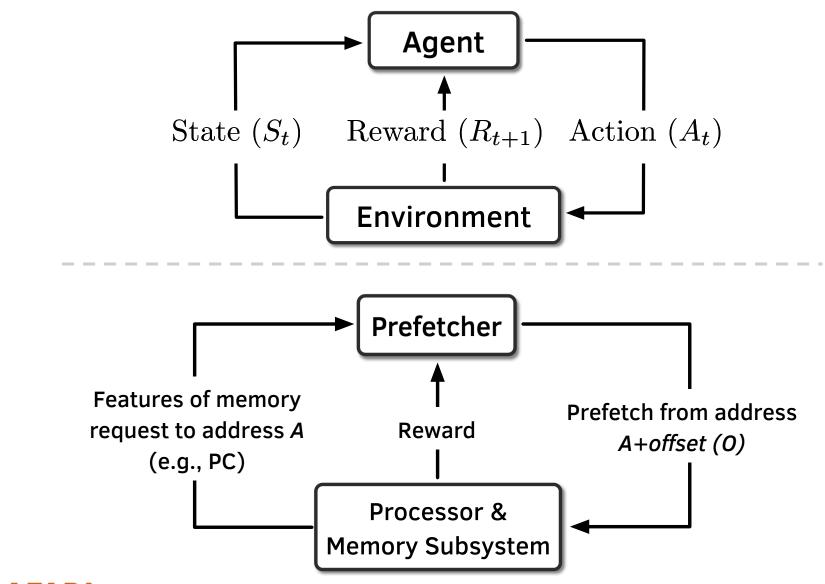

# **Basics of Reinforcement Learning (RL)**

Algorithmic approach to learn to take an action in a given situation to maximize a numerical reward

Environment

- Agent stores Q-values for every state-action pair

- **Expected return** for taking an action in a state

- Given a state, selects action that provides highest Q-value SAFARI

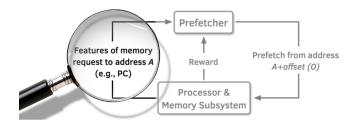

## **Formulating Prefetching as RL**

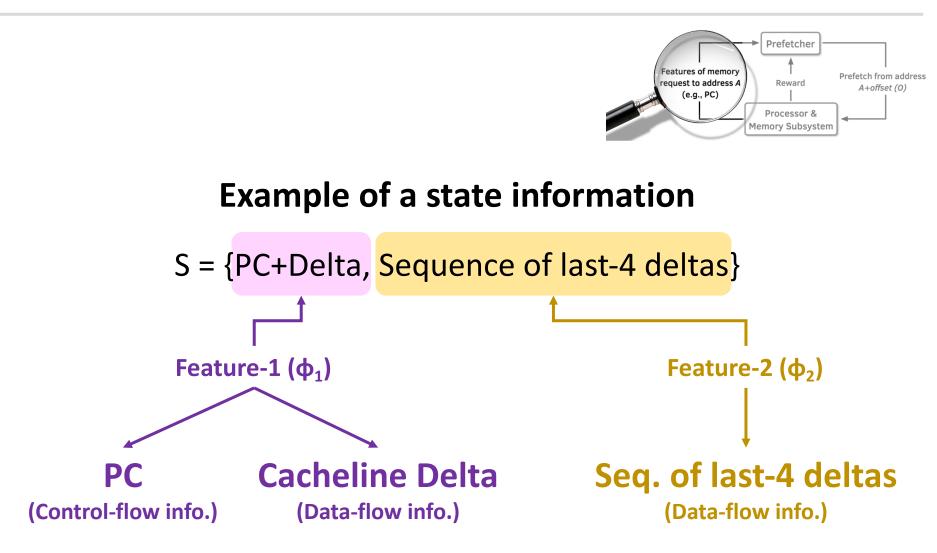

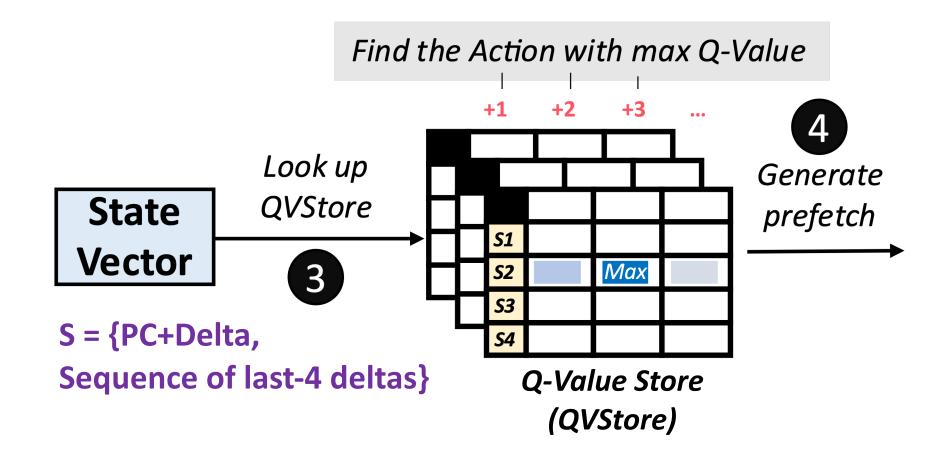

# What is State?

k-dimensional vector of features

$S \equiv \{\phi_S^1, \phi_S^2, \dots, \phi_S^k\}$

• Feature = control-flow + data-flow

### Control-flow examples

- PC

- Branch PC

- Last-3 PCs, ...

### Data-flow examples

- Cacheline address

- Physical page number

- Delta between two cacheline addresses

- Last 4 deltas, ...

### What is State?

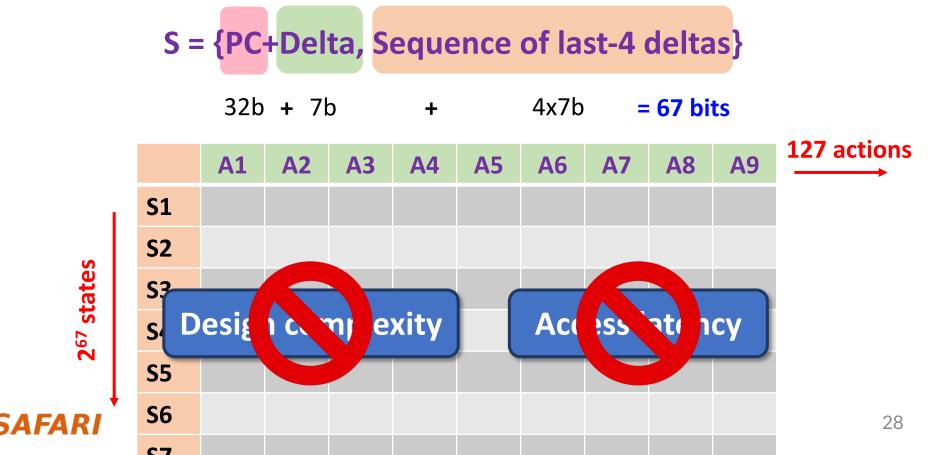

# What is Action?

Given a demand access to address A the action is to select prefetch offset "O"

- Action-space: 127 actions in the range [-63, +63]

- For a machine with 4KB page and 64B cacheline

- Upper and lower limits ensure prefetches do not cross physical page boundary

- A zero offset means no prefetch is generated

- We further **prune** action-space by design-space exploration

### SAFARI

Prefetcher

Reward

Prefetch from addres

A+offset (0)

Features of memory

request to address A

(e.g., PC)

# What is Reward?

- Defines the **objective** of Pythia

- Encapsulates two metrics:

- (e.g., PC) Processor & Memory Surosystem

Features of memory

request to address A

Reward

- Prefetch usefulness (e.g., accurate, late, out-of-page, ...)

- System-level feedback (e.g., mem. b/w usage, cache pollution, energy, ...)

- We demonstrate Pythia with memory bandwidth usage as the system-level feedback in the paper

Prefetch from address

A+offset (0)

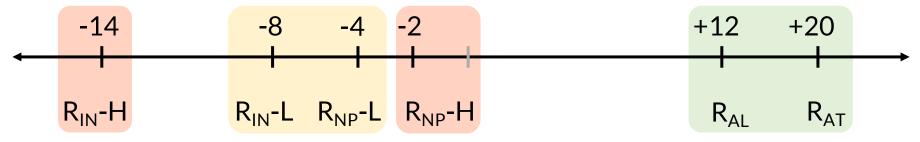

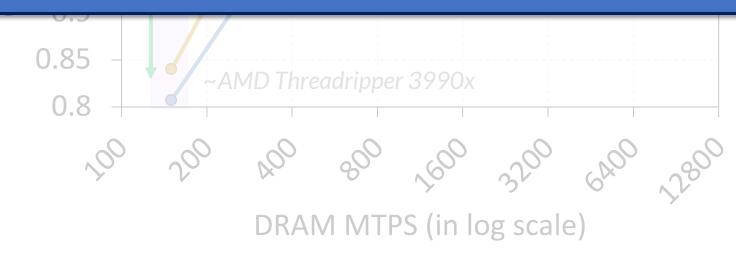

# What is Reward?

### Seven distinct reward levels

- Accurate and timely (R<sub>AT</sub>)

- Accurate but late (R<sub>AL</sub>)

- Loss of coverage (R<sub>CL</sub>)

- Inaccurate

- With low memory b/w usage (R<sub>IN</sub>-L)

- With high memory b/w usage (R<sub>IN</sub>-H)

- No-prefetch

- With low memory b/w usage (R<sub>NP</sub>-L)

- With high memory b/w usage(R<sub>NP</sub>-H)

- Values are set at design time via automatic designspace exploration

- Can be customized further in silicon for higher performance SAFARI

### **Steering Pythia's Objective via Reward Values**

- Example reward configuration for

- Generating accurate prefetches

- Making bandwidth-aware prefetch decisions

AT = Accurate & timely; AL = Accurate & late; NP = No-prefetching; IN = Inaccurate; H = High mem. b/w; L = Low mem. b/w

Highly prefers to generate accurate prefetches

Prefers not to prefetch if memory bandwidth usage is low

Strongly prefers not to prefetch if memory bandwidth usage is high

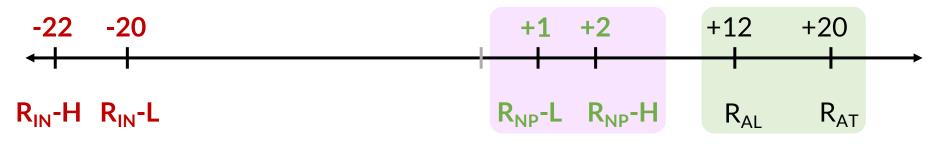

### **Steering Pythia's Objective via Reward Values**

Customizing reward values to make Pythia conservative towards prefetching

AT = Accurate & timely; AL = Accurate & late; NP = No-prefetching; IN = Inaccurate; H = High mem. b/w; L = Low mem. b/w

Highly prefers to generate accurate prefetches

### **Otherwise prefers not to prefetch**

### **Steering Pythia's Objective via Reward Values**

Customizing reward values to make Dythic concernative towards p Strict Pythia configuration

# **Talk Outline**

**Key Shortcomings of Prior Prefetchers**

### Formulating Prefetching as Reinforcement Learning

**Pythia: Overview**

### **Evaluation of Pythia and Key Results**

### Conclusion

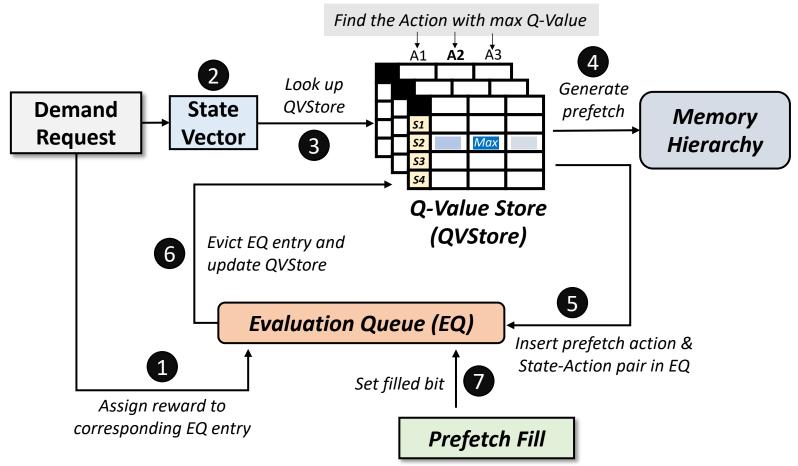

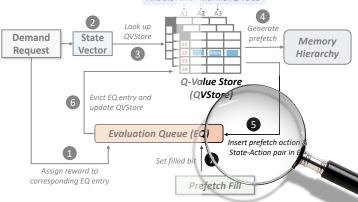

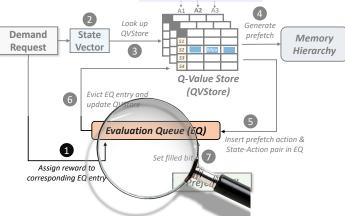

# **Pythia Overview**

- **Q-Value Store**: Records Q-values for *all* state-action pairs

- Evaluation Queue: A FIFO queue of recently-taken actions

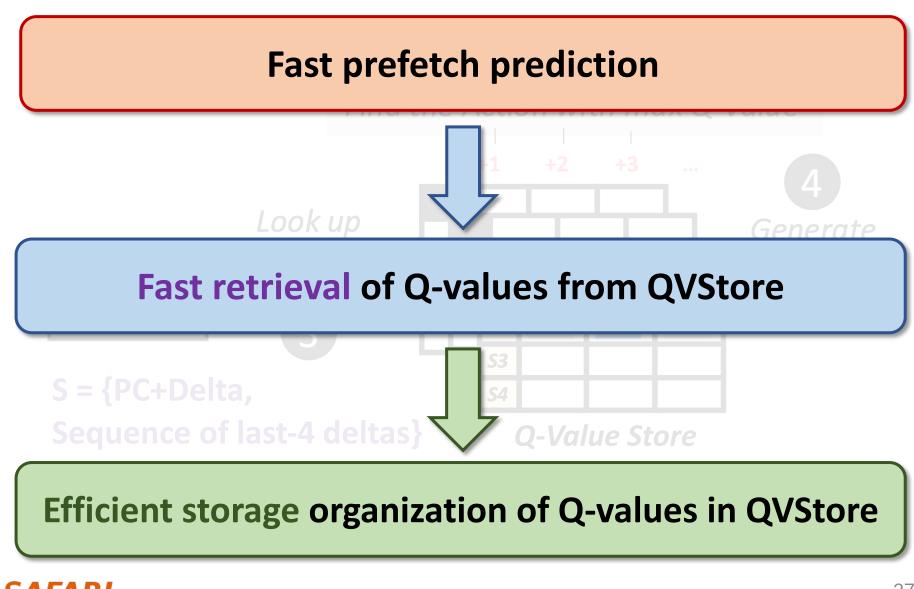

## **Architecting QVStore**

# **Architecting QVStore**

- A monolithic two-dimensional table?

- Indexed by state and action values

- State-space increases exponentially with #bits

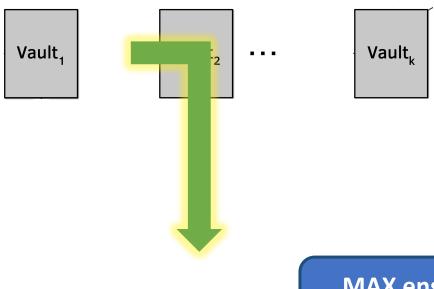

- We partition QVStore into k vaults [k = number of features in state]

- Each vault corresponds to one feature and stores the Qvalues of feature-action pairs

### To retrieve Q(S,A) for each action

- Query each vault in parallel with feature and action

- Retrieve feature-action

Q-value from each vault

- Compute MAX of all feature-action Q-values

MAX ensures the Q(S,A) is driven by the constituent feature that has highest Q( $\phi$ ,A)

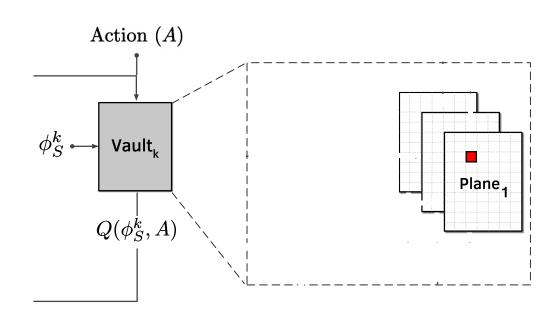

- We further partition each vault into multiple planes

- Each plane stores a partial Q-value of a feature-action pair

### To retrieve Q(φ,A) for each action

- Query each plane in parallel with hashed feature and action

- Retrieve partial featureaction Q-value from each plane

- Compute SUM of all parital feature-action Q-values

We further partition each vault into multiple planes

Each plane stores a partial Q-value of a feature-action pair

**1. Enables sharing of partial Q-values between similar feature values, shortens prefetcher training time**

parallel with hashed feature and action

2. Reduces chances of sharing partial Q-values across widely different feature values

feature-action Q-values

# **More in the Paper**

- Pipelined search operation for QVStore

- Reward assignment and **QVStore update**

- Automatic design-space exploration

- Feature types

- Action

- Reward and Hyperparameter values

# **More in the Paper**

• Pipelined search operation for QVStore

#### Reward assignment and OVStore undate

### Pythia: A Customizable Hardware Prefetching Framework Using Online Reinforcement Learning

Rahul Bera<sup>1</sup> Konstantinos Kanellopoulos<sup>1</sup> Anant V. Nori<sup>2</sup> Taha Shahroodi<sup>3,1</sup> Sreenivas Subramoney<sup>2</sup> Onur Mutlu<sup>1</sup> <sup>1</sup>ETH Zürich <sup>2</sup>Processor Architecture Research Labs, Intel Labs <sup>3</sup>TU Delft

- Reward a <a href="https://arxiv.org/pdf/2109.12021.pdf">https://arxiv.org/pdf/2109.12021.pdf</a>

# **Talk Outline**

**Key Shortcomings of Prior Prefetchers**

### Formulating Prefetching as Reinforcement Learning

**Pythia: Overview**

**Evaluation of Pythia and Key Results**

Conclusion

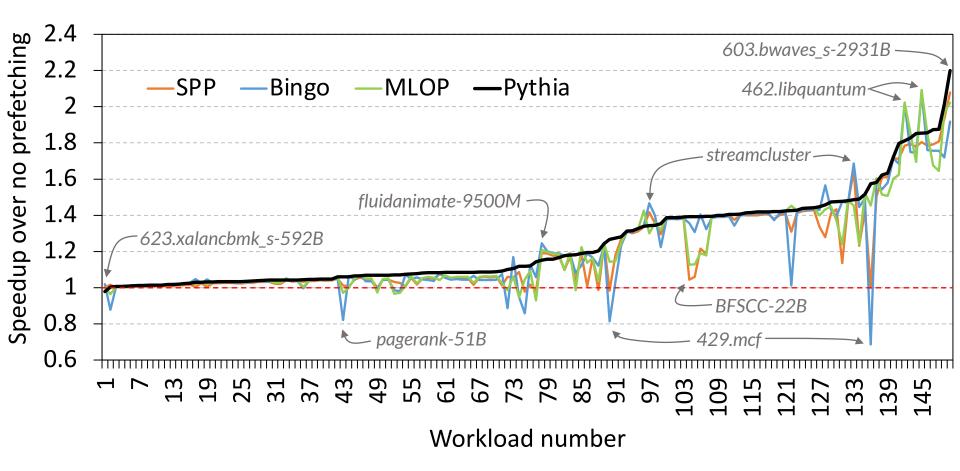

# **Simulation Methodology**

- Champsim [3] trace-driven simulator

- **150** single-core memory-intensive workload traces

- SPEC CPU2006 and CPU2017

- PARSEC 2.1

- Ligra

- Cloudsuite

- Homogeneous and heterogeneous multi-core mixes

### • Five state-of-the-art prefetchers

- SPP [Kim+, MICRO'16]

- Bingo [Bakhshalipour+, HPCA'19]

- MLOP [Shakerinava+, 3<sup>rd</sup> Prefetching Championship, 2019]

- SPP+DSPatch [Bera+, MICRO'19]

- SPP+PPF [Bhatia+, ISCA'20]

# **Basic Pythia Configuration**

• Derived from automatic design-space exploration

### • State: 2 features

- PC+Delta

- Sequence of last-4 deltas

### • Actions: 16 prefetch offsets

- Ranging between -6 to +32. Including 0.

### • Rewards:

- $R_{AT} = +20$ ;  $R_{AL} = +12$ ;  $R_{NP}$ -H=-2;  $R_{NP}$ -L=-4;

- $R_{IN}$ -H=-14;  $R_{IN}$ -L=-8;  $R_{CL}$ =-12

### **Performance with Varying Core Count**

### **Performance with Varying Core Count**

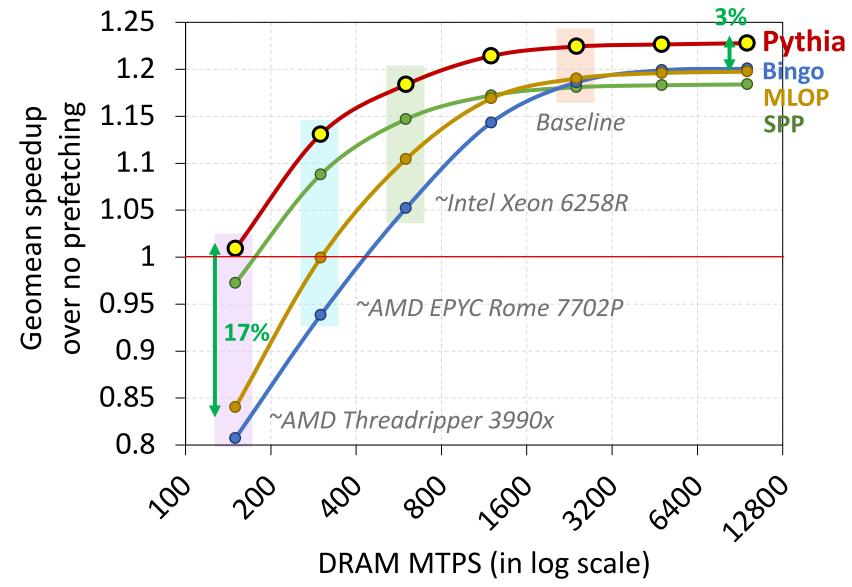

### **Performance with Varying DRAM Bandwidth**

### **Performance with Varying DRAM Bandwidth**

### Pythia outperforms prior best prefetchers for a wide range of DRAM bandwidth configurations

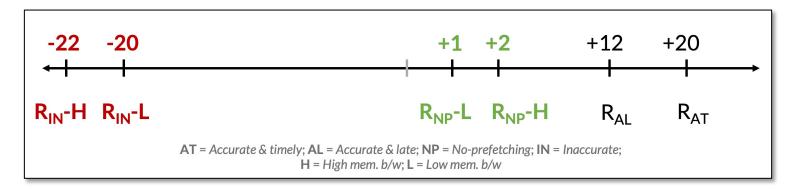

### **Performance Improvement via Customization**

- Reward value customization

- Strict Pythia configuration

- Increasing the rewards for no prefetching

- Decreasing the rewards for inaccurate prefetching

- Strict Pythia is more conservative in generating prefetch requests than the basic Pythia

- Evaluate on all Ligra graph processing workloads

### **Performance Improvement via Customization**

### **Performance Improvement via Customization**

# Pythia can extract even higher performance via customization without changing hardware

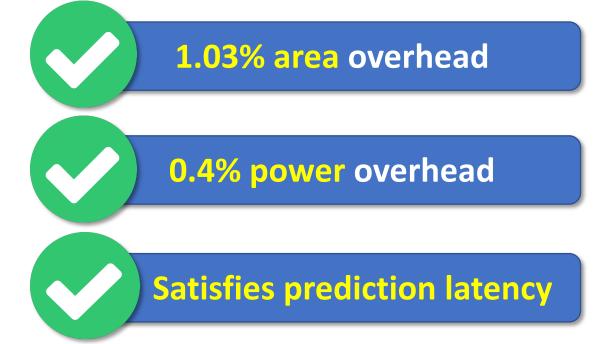

# **Pythia's Overhead**

#### • 25.5 KB of total metadata storage per core

- Only simple tables

- We also model functionally-accurate Pythia with full complexity in Chisel [4] HDL

of a desktop-class 4-core Skylake processor (Xeon D2132IT, 60W)

# More in the Paper

- Performance comparison with **unseen traces**

- Pythia provides equally high performance benefits

- Comparison against multi-level prefetchers

- Pythia outperforms prior best multi-level prefetchers

- Understanding Pythia's learning with a case study

- We reason towards the correctness of Pythia's decision

- Performance sensitivity towards different features and hyperparameter values

- Detailed single-core and four-core performance

# **More in the Paper**

Performance comparison with unseen traces

Pythia provides equally high performance benefits

#### Comparison against multi-level prefetchers

#### Pythia: A Customizable Hardware Prefetching Framework Using Online Reinforcement Learning

Rahul Bera<sup>1</sup> Konstantinos Kanellopoulos<sup>1</sup> Anant V. Nori<sup>2</sup> Taha Shahroodi<sup>3,1</sup> Sreenivas Subramoney<sup>2</sup> Onur Mutlu<sup>1</sup> <sup>1</sup>ETH Zürich <sup>2</sup>Processor Architecture Research Labs, Intel Labs <sup>3</sup>TU Delft

Performance sensitivity towards unterent features and hyperparameter values

Detailed single-core and four-core performance

## **Pythia is Open Source**

### https://github.com/CMU-SAFARI/Pythia

- MICRO'21 artifact evaluated

- Champsim source code + Chisel modeling code

- All traces used for evaluation

| CMU-SAFARI / Pythia Public           |                                                               | <ul> <li>Unwat</li> </ul> | ich → 3 🔂 🔂 Star 9                                                     | ণ্ট Fork 2                     |

|--------------------------------------|---------------------------------------------------------------|---------------------------|------------------------------------------------------------------------|--------------------------------|

| <> Code                              | s 🕞 Actions III Projects 🗔 Wiki 🔃 Security 🗠                  | Insights 🔯 Set            | tings                                                                  |                                |

| 😚 master 👻 🕻 1 branch 🛇 5 tags       | Go to file Add fi                                             | le - Code -               | About                                                                  | ţô                             |

| rahulbera Github pages documentation | ✓ d1efc65 7 hours ago                                         | 3 40 commits              | A customizable hardv<br>framework using onlin<br>learning as described | ne reinforcement               |

| branch                               | Initial commit for MICRO'21 artifact evaluation               | 2 months ago              | 2021 paper by Bera a                                                   |                                |

| config                               | Initial commit for MICRO'21 artifact evaluation               | 2 months ago              | Kanellopoulos et al.                                                   |                                |

| docs                                 | Github pages documentation                                    | 7 hours ago               |                                                                        | 12021.pdf                      |

| experiments                          | Added chart visualization in Excel template                   | 2 months ago              | machine-learning                                                       |                                |

| inc inc                              | Updated README                                                | 8 days ago                | reinforcement-learning                                                 |                                |

| prefetcher                           | Initial commit for MICRO'21 artifact evaluation               | 2 months ago              | computer-architecture<br>microarchitecture ca                          | prefetcher<br>ache-replacement |

| replacement                          | Initial commit for MICRO'21 artifact evaluation               | 2 months ago              | branch-predictor cha                                                   | ampsim-simulator               |

| scripts                              | Added md5 checksum for all artifact traces to verify download | 2 months ago              | champsim-tracer                                                        |                                |

| src                                  | Initial commit for MICRO'21 artifact evaluation               | 2 months ago              | 🛱 Readme                                                               |                                |

| tracer                               | Initial commit for MICRO'21 artifact evaluation               | 2 months ago              | か View license                                                         |                                |

| gitignore                            | Initial commit for MICRO'21 artifact evaluation               | 2 months ago              | Ç∄ Cite this repository                                                | Ŧ                              |

| CITATION.cff                         | Added citation file                                           | 8 days ago                |                                                                        |                                |

|                                      | Updated LICENSE                                               | 2 months ago              | Releases 5                                                             |                                |

|                                      | Initial commit for MICRO'21 artifact evaluation               | 2 months ago              | V1.3 Latest                                                            |                                |

|                                      |                                                               |                           | 21 days ago                                                            |                                |

### **Talk Outline**

**Key Shortcomings of Prior Prefetchers**

### Formulating Prefetching as Reinforcement Learning

**Pythia: Overview**

#### **Evaluation of Pythia and Key Results**

#### Conclusion

### **Executive Summary**

- Background: Prefetchers predict addresses of future memory requests by associating memory access patterns with program context (called feature)

- **Problem**: Three key shortcomings of prior prefetchers:

- Predict mainly using a single program feature

- Lack inherent system awareness (e.g., memory bandwidth usage)

- Lack in-silicon customizability

- Goal: Design a prefetching framework that:

- Learns from multiple features and inherent system-level feedback

- Can be customized in silicon to use different features and/or prefetching objectives

- Contribution: Pythia, which formulates prefetching as reinforcement learning problem

- Takes adaptive prefetch decisions using multiple features and system-level feedback

- Can be customized in silicon for target workloads via simple configuration registers

- Proposes a realistic and practical implementation of RL algorithm in hardware

- Key Results:

SAFARI

- Evaluated using a wide range of workloads from SPEC CPU, PARSEC, Ligra, Cloudsuite

- Outperforms best prefetcher (in 1-core config.) by **3.4%**, **7.7%** and **17%** in 1/4/bw-constrained cores

- Up to 7.8% more performance over basic Pythia across Ligra workloads via simple customization

#### https://github.com/CMU-SAFARI/Pythia

# Pythia

### A Customizable Hardware Prefetching Framework Using Online Reinforcement Learning

<u>Rahul Bera</u>, Konstantinos Kanellopoulos, Anant V. Nori, Taha Shahroodi, Sreenivas Subramoney, Onur Mutlu

https://github.com/CMU-SAFARI/Pythia

# BACKUP

# **Reward Assignment to EQ Entry**

- Every action gets inserted into EQ

- Reward is assigned to each EQ entry **before or during** the eviction

- **During EQ insertion**: for actions

- Not to prefetch

- Out-of-page prefetch

# **Reward Assignment to EQ Entry**

- Every action gets inserted into EQ

- Reward is assigned to each EQ entry **before or during** the eviction

- **During EQ insertion**: for actions

- Not to prefetch

- Out-of-page prefetch

- During EQ residency:

In case address of a demand matches with address in EQ (signifies accurate prefetch)

# **Reward Assignment to EQ Entry**

- Every action gets inserted into EQ

- Reward is assigned to each EQ entry **before or during** the eviction

- During EQ insertion: for actions

- Not to prefetch

- Out-of-page prefetch

- During EQ residency:

- In case address of a demand matches with address in EQ (signifies accurate prefetch)

- During EQ eviction:

- In case no reward is assigned till eviction (signifies inaccurate prefetch)

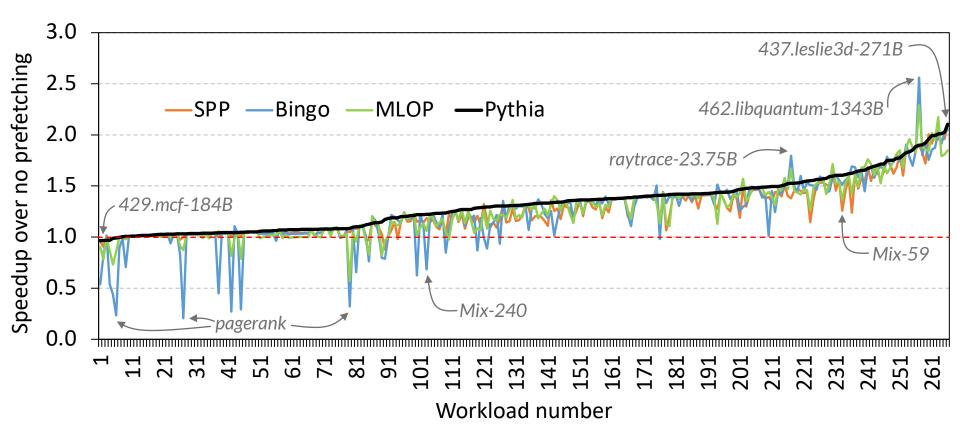

### **Performance S-curve: Single-core**

### **Performance S-curve: Four-core**