# RowHammer: A Retrospective

Onur Mutlu $^{\S \ddagger}$  Jeremie S. Kim $^{\ddagger \S}$   $^{\S}$ ETH Zürich  $^{\ddagger}$ Carnegie Mellon University

Abstract—This retrospective paper describes the RowHammer problem in Dynamic Random Access Memory (DRAM), which was initially introduced by Kim et al. at the ISCA 2014 conference [133]. RowHammer is a prime (and perhaps the first) example of how a circuit-level failure mechanism can cause a practical and widespread system security vulnerability. It is the phenomenon that repeatedly accessing a row in a modern DRAM chip causes bit flips in physically-adjacent rows at consistently predictable bit locations. RowHammer is caused by a hardware failure mechanism called DRAM disturbance errors, which is a manifestation of circuit-level cell-to-cell interference in a scaled memory technology.

Researchers from Google Project Zero demonstrated in 2015 that this hardware failure mechanism can be effectively exploited by user-level programs to gain kernel privileges on real systems. Many other follow-up works demonstrated other practical attacks exploiting RowHammer. In this article, we comprehensively survey the scientific literature on RowHammer-based attacks as well as mitigation techniques to prevent RowHammer. We also discuss what other related vulnerabilities may be lurking in DRAM and other types of memories, e.g., NAND flash memory or Phase Change Memory, that can potentially threaten the foundations of secure systems, as the memory technologies scale to higher densities. We conclude by describing and advocating a principled approach to memory reliability and security research that can enable us to better anticipate and prevent such vulnerabilities.

Index Terms—DRAM, Security, Vulnerability, Technology Scaling, Reliability, Errors, Memory Systems.

#### I. INTRODUCTION AND OUTLINE

Memory is a key component of all modern computing systems, often determining the overall performance, energy efficiency, and reliability characteristics of the entire system. The push for increasing the density of modern memory technologies via technology scaling, which has resulted in higher capacity (i.e., density) memory and storage at lower cost, has enabled large leaps in the performance of modern computers [175]. This positive trend is clearly visible in especially the dominant main memory and solid-state storage technologies of today, i.e., DRAM [57, 58, 125, 146, 151] and NAND flash memory [42, 45, 52], respectively. Unfortunately, the same push has also greatly decreased the reliability of modern memory technologies, due to the increasingly smaller memory cell size and increasingly smaller amount of charge that is maintainable in the cell, which makes the memory cell much more vulnerable to various failure mechanisms and noise and interference sources, both in DRAM [113, 115-118, 133, 161, 176, 196, 203] and NAND flash nemory [42– 48, 50–53, 164, 166–168, 176].

As memory scales down to smaller technology nodes, new failure mechanisms emerge that threaten its correct operation. If such failure mechanisms are not anticipated and corrected, they can not only degrade system reliability and availability but also, perhaps even more importantly, open up new security vulnerabilities: a malicious attacker can exploit the exposed failure mechanism to take over the entire system. As such, new failure mechanisms in memory can become practical and significant threats to system security.

In this article, we provide a retrospective of one such example failure mechanism in DRAM, which was initially introduced by Kim et al. at the ISCA 2014 conference [133]. We provide a description of the RowHammer problem and its implications by summarizing our ISCA 2014 paper [133], describe solutions proposed by our original work [133], comprehensively examine the many works that build on our original work in various ways, e.g., by developing new security attacks, proposing solutions, and analyzing RowHammer. What comes next in this section provides a roadmap of the entire article.

In our ISCA 2014 paper [133], we introduce the RowHammer problem in DRAM, which is a prime (and perhaps the first) example of how a circuit-level failure mechanism can cause a practical and widespread system security vulnerability. RowHammer, as it is now popularly referred to, is the phenomenon that repeatedly accessing a row in a modern DRAM chip causes bit flips in physically-adjacent rows at consistently predictable bit locations. It is caused by a hardware failure mechanism called DRAM disturbance errors, which is a manifestation of circuit-level cell-to-cell interference in a scaled memory technology. We describe the RowHammer problem and its root causes in Section II.

Inspired by our ISCA 2014 paper's fundamental findings, researchers from Google Project Zero demonstrated in 2015 that this hardware failure mechanism can be effectively exploited by user-level programs to gain kernel privileges on real systems [215, 216]. Tens of other works since then demonstrated other practical attacks exploiting RowHammer, e.g., [12, 31–33, 37, 54, 66, 73, 76, 89, 90, 108, 158, 198, 199, 201, 207, 235, 236, 241, 251, 260]. These include remote takeover of a server vulnerable to RowHammer, takeover of a victim virtual machine by another virtual machine running on the same system, takeover of a mobile device by a malicious user-level application that requires no permissions, takeover of a mobile system quickly by triggering RowHammer using a mobile GPU, and takeover of a remote system by triggering RowHammer on it through the Remote Direct Memory Access (RDMA) protocol [6]. We describe the works that build on RowHammer to develop new security attacks in Section III-A.

Our ISCA 2014 paper rigorously and experimentally analyzes the RowHammer problem and examines seven different solutions, multiple of which are already employed in practice to prevent the security vulnerabilities (e.g., increasing the

memory refresh rate). We propose a low-cost solution, Probabilistic Adjacent Row Activation, which provides a strong and configurable reliability and security guarantee; a solution whose variants are being adopted by DRAM manufacturers and memory controller designers [5]. We describe this solution and the six other solutions of our original paper in Section II-E. Many other works build on our original paper to propose and evaluate other solutions to RowHammer, and we discuss them comprehensively in Section III-B.

Our ISCA 2014 paper leads to a new mindset that has enabled a renewed interest in hardware security research: general-purpose hardware is fallible, in a very widespread manner, and this causes real security problems. We believe the RowHammer problem will become worse over time since DRAM cells are getting closer to each other with technology scaling. Other similar vulnerabilities may also be lurking in DRAM and other types of memories, e.g., NAND flash memory or Phase Change Memory, that can potentially threaten the foundations of secure systems, as the memory technologies scale to higher densities. Our ISCA 2014 paper advocates a principled system-memory co-design approach to memory reliability and security research that can enable us to better anticipate and prevent such vulnerabilities. We describe promising ongoing and future research directions related to RowHammer (Section IV), including the examination of other potential vulnerabilities in memory (in Section IV-A) and the use of a principled approach to make memory more reliable and more secure (in Section IV-B).

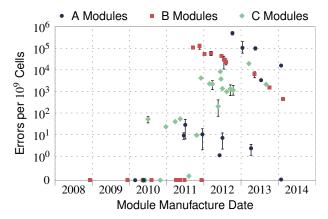

## II. THE ROWHAMMER PROBLEM: A SUMMARY

Memory isolation is a key property of a reliable and secure computing system. An access to one memory address should not have unintended side effects on data stored in other addresses. However, as process technology scales down to smaller dimensions, memory chips become more vulnerable to disturbance, a phenomenon in which different memory cells interfere with each others' operation. We have shown, in our ISCA 2014 paper [133], the existence of disturbance errors in commodity DRAM chips that are sold and used in the field. Repeatedly reading from the same address in DRAM could corrupt data in nearby addresses. Specifically, when a DRAM row is opened (i.e., activated) and closed (i.e., precharged) repeatedly (i.e., hammered), enough times within a DRAM refresh interval, one or more bits in physicallyadjacent DRAM rows can be flipped to the wrong value. This DRAM failure mode is now popularly called RowHammer [1, 2, 23, 37, 90, 131, 141, 207, 215, 216, 241, 246]. Using an FPGA-based experimental DRAM testing infrastructure, which we originally developed for testing retention time issues in DRAM [161],1 we tested 129 DRAM modules manufactured by three major manufacturers (A, B, C) in seven recent years (2008–2014) and found that 110 of them exhibited RowHammer errors, the earliest of which dates back to 2010. This is illustrated in Figure 1, which shows the error rates we found in all 129 modules we tested where modules are categorized based on manufacturing date.<sup>2</sup> In particular, *all* DRAM modules from 2012–2013 were vulnerable to RowHammer, indicating that RowHammer is a recent phenomenon affecting more advanced process technology generations (as also demonstrated repeatedly by various works that come after our ISCA 2014 paper [12, 17, 66, 141, 198, 241]).

Fig. 1: RowHammer error rate vs. manufacturing dates of 129 DRAM modules we tested (reproduced from [133]).

#### A. RowHammer Mechanisms

In general, disturbance errors occur whenever there is a strong enough interaction between two circuit components (e.g., capacitors, transistors, wires) that should be isolated from each other. Depending on which component interacts with which other component and also how they interact, many different modes of disturbance are possible.

Among them, our ISCA 2014 paper identifies one particular disturbance mode that affects commodity DRAM chips from all three major manufacturers. When a wordline's voltage is toggled repeatedly, some cells in nearby rows leak charge at a much faster rate than others. Such vulnerable cells, if disturbed enough times, cannot retain enough charge for even 64ms, the time interval at which they are refreshed. Ultimately, this leads to the cells losing data and experiencing disturbance errors.

Without analyzing existing DRAM chips at the device-level, which is an option not available for us, we cannot make definitive claims about how a wordline interacts with nearby cells to increase their leakiness. Our ISCA 2014 paper hypothesizes, based on past studies and findings, that there may be three ways of interaction. At least two major DRAM manufacturers have confirmed all three of these hypotheses as potential causes of disturbance errors. First, changing the voltage of a wordline could inject noise into an adjacent wordline through *electromagnetic coupling* [60, 173, 208]. This

<sup>&</sup>lt;sup>1</sup>This infrastructure is currently released to the public, and is described in detail in our HPCA 2017 paper [98]. The infrastructure has enabled many studies [57, 58, 79, 98, 115–117, 133, 147, 148, 151, 161, 203] into the failure and performance characteristics of modern DRAM, which were previously not well understood.

<sup>&</sup>lt;sup>2</sup>Test details and experimental setup, along with a listing of all modules and their characteristics, are reported in our original RowHammer paper [133].

partially enables the adjacent row of access-transistors for a short amount of time and facilitates the leakage of charge from vulnerable cells. Thus, if a row is hammered enough times to disturb such vulnerable cells before they get refreshed, charge in such cells get drained to a point that the original cell values are not recoverable any more. Second, bridges are a wellknown class of DRAM faults in which conductive channels are formed between unrelated wires and/or capacitors [19, 20]. One study on embedded DRAM (eDRAM) found that toggling a wordline could accelerate the flow of charge between two bridged cells [104]. Third, it has been reported that toggling a wordline for hundreds of hours can permanently damage it by hot-carrier injection [64]. If some of the hot-carriers are injected into the neighboring rows, this could modify the amount of charge in their cells or alter the characteristics of their access-transistors to increase their leakiness.

Several recent works have tried to examine and model RowHammer at the circuit level; we survey these works in Section III-C.

## B. User-Level RowHammer

Our ISCA 2014 paper also demonstrates that a very simple user-level program [3, 133] can reliably and consistently induce RowHammer errors in three commodity AMD and Intel systems using vulnerable DRAM modules. We released the source code of this program [3], which Google Project Zero later enhanced [4]. Using our user-level RowHammer test program, we showed that RowHammer errors violate two invariants that memory should provide: (i) a read access should not modify data at any address and (ii) a write access should modify data only at the address that it is supposed to write to. As long as a row is repeatedly opened, both read and write accesses can induce RowHammer errors, all of which occur in rows other than the one that is being accessed. Since different DRAM rows are mapped (via mechanisms in the system software and the memory controller) to different software pages, our user-level program could reliably corrupt specific bits in pages belonging to other programs. As a result, RowHammer errors can be exploited by a malicious program to breach memory protection and compromise the system. In fact, we hypothesized, in our ISCA 2014 paper, that our user-level program, with some engineering effort, could be developed into a disturbance attack that injects errors into other programs, crashes the system, or hijacks control of the system. We left such research for the future since our primary objective in our ISCA 2014 paper was to understand and prevent RowHammer errors [133].

## C. Characteristics of RowHammer

Our ISCA 2014 paper [133] provides a detailed experimental analysis of various characteristics of RowHammer, including its prevalence across DRAM chips, access pattern dependence, data pattern dependence, temperature dependence, address correlation between victim and aggressor memory rows, number of bits in a victim row that flip due to RowHammer in an adjacent row, number of rows that get

affected due to RowHammer in an adjacent row, relationship of RowHammer-vulnerable cells with leaky cells that need higher refresh rates, repeatability of RowHammer errors, the fact that a memory row is vulnerable to RowHammer on both adjacent wordlines, and real system demonstration of RowHammer. We omit these analyses here in this retrospective and focus on security vulnerabilities and prevention of RowHammer. We refer the reader to [133] for a rigorous treatment of the characteristics of the RowHammer phenomenon.

One of the key takeaways from our characterization is that RowHammer-induced errors are predictably repeatable. In other words, if a cell's value gets corrupted via RowHammer, the same cell's value is very likely to get corrupted again via RowHammer. This repeatability enables the construction of repeatable security attacks in a controlled manner, which we briefly discuss next and cover in detail in Section III-A.

#### D. RowHammer as a Security Threat

RowHammer exposes a security threat since it leads to a breach of memory isolation, where accesses to one row (e.g., a user-level memory page) modifies the data stored in another memory row (e.g., a privileged operating system page). As indicated above, malicious software can be written to take advantage of these disturbance errors. We call these disturbance attacks [133], or RowHammer attacks. Such attacks can be used to corrupt system memory, crash a system, or take over the entire system. Confirming the predictions of our ISCA paper [133], researchers from Google Project Zero developed a user-level attack that exploits RowHammer to gain kernel privileges and thus take over an entire system [215, 216]. More recently, researchers showed that RowHammer can be exploited in various ways to take over various classes of systems. As such, the RowHammer problem has widespread and profound real implications on system security, threatening the foundations of memory isolation on top of which modern system security principles are built. We survey the works that exploit RowHammer to build many different security attacks in Section III-A.

## E. RowHammer Solutions

Our ISCA 2014 paper discusses and analyzes seven different countermeasures to the RowHammer problem. Each solution makes a different trade-off between feasibility, cost, performance, power, and reliability. Among them, we believe our seventh and last solution, called PARA, to be the most efficient with the lowest overhead.

The first six solutions are: 1) manufacturing better DRAM chips that are not vulnerable, 2) using (strong) error correcting codes (ECC) to correct RowHammer-induced errors, 3) increasing the refresh rate for all of memory, 4) statically remapping/retiring RowHammer-prone cells via a one-time post-manufacturing analysis, 5) dynamically remapping/retiring RowHammer-prone cells during system operation, 6) accurately identifying hammered rows during runtime and refresh-

ing their neighbors.<sup>3</sup> We will not go into significant detail in this summary and retrospective, but none of these first six solutions are very desirable as they come at significant power, performance or cost overheads, as we describe in our original work [133]. We will revisit some of these solutions in Section III-B of this article, when we survey related work that builds on RowHammer.

Our ISCA 2014 paper's main proposal to prevent RowHammer is a low-overhead mechanism called PARA (probabilistic adjacent row activation). The key idea of PARA is simple: every time a row is opened and closed, one or more of its adjacent rows are also opened (i.e., refreshed) with some low probability p (by the memory controller or the DRAM chip). If one particular row happens to be opened and closed repeatedly, then it is statistically certain that the row's adjacent rows will eventually be opened as well, as we show in our original work, assuming p is chosen intelligently and carefully. The main advantages of PARA are that 1) it is stateless in the sense that it does not require expensive hardware datastructures to count the number of times that rows have been opened or to store the addresses of the aggressor/victim rows, 2) its performance and power consumption overheads are very low due to the infrequent activation of only adjacent rows of a closed row. Our ISCA 2014 paper provides a memory-controller-based implementation of PARA, evaluates its reliability guarantee against adversarial access patterns, and empirically examines its performance overhead. We show that by setting the probability of refresh of adjacent rows p to a reasonable yet very low value (e.g., 0.001 or 0.005), PARA provides a strong guarantee against RowHammer and leads to a very small performance overhead of less than 0.75%. More detailed discussion of the implementation and evaluation of PARA can be found in our original work. We will revisit PARA in Section III-B of this article.

#### III. SURVEY OF WORKS THAT BUILD ON ROWHAMMER

RowHammer has spurred a significant amount of research since its publication in 2014. In this section, we provide a categorical survey of the array of works that build off of our original paper that introduces the concept of RowHammer and *disturbance attacks* [133]. We describe seven different types of works: (1) security attacks that exploit the RowHammer vulnerability, (2) defense and mitigation mechanisms against the RowHammer phenomenon and the security attacks, (3) circuit-level studies that aim to understand and model the RowHammer phenomenon, (4) other works that exploit RowHammer for various purposes, (5) works that build platforms to study RowHammer, (6) pop culture references to RowHammer, and (7) works that show that the RowHammer phenomenon continues to exist in future generation DRAM chips younger than the ones we examined in our original ISCA 2014 paper.

While we describe the works, we also point out the potential for future research in each topic area.

#### A. Exploits using RowHammer

Inspired by our ISCA 2014 paper's fundamental findings, researchers from Google Project Zero demonstrated in 2015 that RowHammer can be effectively exploited by user-level programs to gain kernel privileges on real systems [215, 216]. Google Project Zero presented two exploits using RowHammer. The first exploit runs as a Native Client (NaCl) program and escalates privilege to escape from the x86-64 sandbox environment. Since NaCl statically validates code before running it, Google Project Zero simply shows that an attacker can modify safe instructions to become unsafe. The second exploit, which is even more powerful, runs as a normal x86-64 process on Linux and escalates privilege to gain access to all of physical memory and thus take over the entire system. The attacker hammers a page table entry (PTE) such that it changes the PTE to point to a page table owned by the attacking process. This gives the attacking process full readwrite access to its own page table and hence to all of physical memory, which enables the attacking process to take over the entire system.

Tens of other works since then demonstrated other attacks exploiting RowHammer and we explain several of them in some detail here. One involves the takeover of a victim virtual machine (VM) by another attacker VM running on the same system [207]. In [207], the attacker VM writes a memory page that it knows exists in the victim VM at a RowHammer-vulnerable memory location. If memory deduplication merges the victim VM's and attacker VM's duplicate pages to the attacker VM page's location, the attacker can then induce RowHammer failures in the deduplicated page's data, which is shared by both the attacker and the victim. Since RowHammer attacks modify memory without writes, the deduplication engine does not detect the modification to memory, and the victim VM continues to use the corrupted page. The authors show two attacks using this method. The first attack compromises OpenSSH [10] by modifying the public keys in a victim VM such that the attacker can easily generate a private key that matches the modified public key. It is easier to generate a private key when a public key becomes easily factorable. The second attack compromises the Linux package installation tool, apt-get [8] using two steps. First, the attacker flips a bit in the apt-get domain name of the victim, such that the victim's apt-get requests are redirected to a malicious repository. Second, the attacker flips a bit in the page containing the Ubuntu Archive Signing Keys, which are used to check the validity of packages before installation. Thus, this work exploits the RowHammer vulnerability to break both OpenSSH public key authentication and install malicious software via widely-used installation tools.

The Drammer work [241] demonstrates an attack that exploits RowHammer on a mobile device using a malicious user-level application that requires no permissions. This is the first demonstration of RowHammer attacks on ARM-

<sup>&</sup>lt;sup>3</sup>Several early patent applications propose to maintain an array of counters ("detection logic") in either the memory controller [25, 27, 88] or in the DRAM chips themselves [26, 28, 87]. If the counters are tagged with the addresses of only the most recently activated rows, the number of required counters can be significantly reduced [88].

based systems. The work takes advantage of the deterministic memory allocation patterns in the Android Linux Operating System. By exploiting these deterministic memory allocation patterns, the authors present a methodology for forcing a victim process to allocate its page table entry in a RowHammervulnerable region of memory. To do this, the attacker process must essentially allocate all possible memory regions for a page table allocation and then release the page table allocation that contains the RowHammer-vulnerable DRAM cells at bit offsets that enable exploitation. Because of the use of Buddy Allocation [135] (an allocation scheme that forces allocations to the smallest available contiguous region of memory) in Linux platforms, the attacker does not need to allocate all of memory and risk crashing the system. The researchers found 18 out of 27 phone models to be vulnerable to RowHammer and have since released a mobile application that tests memory for RowHammer-vulnerable cells and aggregates statistics on how widespread the RowHammer phenomenon is on mobile devices. This work shows that existing mobile systems are widely vulnerable to RowHammer attacks.

[90] demonstrates a remote takeover of a server vulnerable to RowHammer via JavaScript code execution. Since JavaScript is present and enabled by default in every modern browser, this work demonstrates the proof-of-concept that the RowHammer attack can be launched by a website to gain root privileges on a system that visits the website.

Other works that have demonstrated attacks exploiting RowHammer include takeover of a mobile system by triggering RowHammer using the WebGL interface on a mobile GPU [76, 89], takeover of a remote system by triggering RowHammer through the Remote Direct Memory Access (RDMA) protocol [158, 235], and various other attacks [12, 31–33, 37, 54, 66, 73, 89, 108, 198, 199, 201, 236, 251, 260]. Thus, RowHammer has widespread and profound real implications on system security, as it breaks memory isolation on top of which modern system security principles are built.

Our work has inspired many researchers to exploit RowHammer to devise new attacks. As mentioned earlier, tens of papers were written in top security venues that demonstrate various practical attacks exploiting RowHammer (e.g., [12, 31–33, 37, 54, 66, 73, 76, 89, 90, 108, 158, 198, 199, 201, 207, 215, 216, 235, 236, 241, 251, 260]). These attacks started with Google Project Zero's first work in 2015 [215, 216] and they continue to this date, with the latest ones that we know of being published in late 2018 [31, 33, 54, 158, 199, 235, 236, 260] and mid 2019 [66]. We believe there is a lot more to come in this direction: as systems security researchers understand more about RowHammer, and as the RowHammer phenomenon continues to fundamentally affect memory chips due to technology scaling problems [176], researchers and practitioners will develop different types of attacks to exploit RowHammer in various contexts and in many more creative ways. Various recent reports suggest that new-generation DDR4 DRAM and other DRAM chips are vulnerable to RowHammer [12, 17, 66, 141, 198], as we examine further in Section III-G, so the fundamental security

research on RowHammer is likely to continue into the future.

#### B. Defenses against RowHammer

Our work also inspired many solution and mitigation techniques for RowHammer from both researchers and industry practitioners. Apple publicly mentioned, in their critical security release for RowHammer, that they increased the memory refresh rates due to the "original research by Yoongu Kim et al. (2014)" [21]. The industry-standard *Memtest86* program, which is used to test deployed memory chips for errors, was updated, including a RowHammer test, acknowledging our ISCA 2014 paper [194]. Many academic works developed solutions to RowHammer, working from our original research (e.g., [23, 38, 40, 81, 106, 120, 152, 190, 222, 226, 242]). Additionally, many patents for solutions to RowHammer have been filed [25-28, 30, 88]. We believe such solutions will continue to be generated in both academia and industry, extending RowHammer's impact into the very long term. We cover some of these solutions in this section.

Given that RowHammer is such a critical vulnerability, it is important to find both *immediate* and *long-term* solutions to the RowHammer problem (as well as related problems that might cause similar vulnerabilities). The goal of the immediate solutions is to ensure that existing systems are patched such that the vulnerable DRAM devices that are already in the field cannot be exploited. The goal of the long-term solutions is to ensure that future DRAM devices do not suffer from the RowHammer problem when they are released into the field.

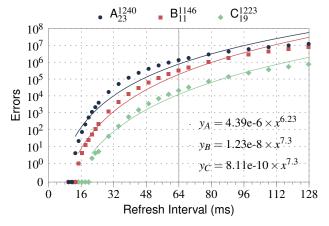

Given that immediate solutions require mechanisms that already exist in systems operating in the field, they are fundamentally more limited. A popular immediate solution, described and analyzed by our ISCA 2014 paper [133], is to increase the refresh rate of memory such that the probability of inducing a RowHammer error before DRAM cells get refreshed is reduced. Several major system manufacturers (including Apple, HP, Cisco, Lenovo, and IBM) have adopted this solution and released security patches that increased DRAM refresh rates (e.g., [21, 75, 100, 154]) in the memory controllers. While this solution might be practical and effective in reducing the vulnerability, it has the significant drawbacks of increasing energy/power consumption, reducing system performance, and degrading quality of service experienced by user programs. Our paper shows that the refresh rate needs to be increased by 7.8X its nominal value today, if we want to eliminate all RowHammer-induced errors we saw in our tests of 129 DRAM modules! Figure 2 demonstrates this study: if we examine the most RowHammer-vulnerable module that we test from each manufacturer A, B, C, we find that completely eliminating the RowHammer-induced errors requires us to reduce the refresh interval from the nominal 64ms to 8.2ms, leading to a 7.8X increase in the refresh rate. Since DRAM refresh is already a significant burden [59, 113, 115, 160, 196, 203] on energy consumption, performance, and quality of service, increasing it by any significant amount would only exacerbate the problem. Yet, increased refresh rate is likely the most practical immediate solution to RowHammer that does not require any significant change to the system.

Fig. 2: Number of RowHammer-induced errors observed on the most RowHammer-vulnerable module of each DRAM manufacturer A, B, C, as the refresh interval is varied from 8ms to 128ms (reproduced from [133]).

Other immediate solutions modify the software [38, 106, 107, 137, 190, 215, 242, 250]. For example, ANVIL proposes software-based detection of RowHammer attacks by monitoring via hardware performance counters and selective explicit refreshing of victim rows that are found to be under attack [23]. One short-term approach to mitigating RowHammer attacks is intelligently allocating and physically isolating pages such that RowHammer cannot affect important pages [38, 137, 242]. [38] extends the physical memory allocator of the Operating System to allocate memory in such a way that isolates memory pages of different system entities. [242] prevents DMA-based attacks by isolating DMA buffers with additional buffer rows (i.e., guard rows) that do not store data. This ensures that any DMA-based attack can only induce RowHammer bit flips in the guard rows without affecting rows containing important data. Another approach for mitigating RowHammer statically analyzes code to identify code segments that are probably RowHammer attacks and prevents them prior to execution [106]. ZebRAM [137] reserves odd rows as "safe" rows and even rows as "unsafe" rows such that hammering a safe row should never result in a RowHammer failure in another safe row. The unsafe rows are used as swap space and a portion of safe rows are used as a cache for data in the unsafe-row swap space. Whenever data in unsafe rows is migrated to safe rows, ZebRAM performs software integrity checks and error correction. Unfortunately, such software-based solutions usually 1) require modifications to system software, 2) might be intrusive to system operation, and/or 3) might cause significant performance or memory space overheads (yet they are still promising to research).

As briefly discussed in Section II-E, our ISCA 2014 paper [133] discusses and analyzes seven short-term and long-term countermeasures to the RowHammer problem. The first six solutions are: 1) making better DRAM chips that are not

vulnerable, 2) using (strong) error correcting codes (ECC) to correct RowHammer-induced errors, 3) increasing the refresh rate for all of memory, 4) statically remapping/retiring RowHammer-prone cells via a one-time post-manufacturing analysis, 5) dynamically remapping/retiring RowHammerprone cells during system operation, 6) accurately identifying hammered rows during runtime and refreshing their neighbors. Our work shows that the first six solutions are not very desirable as they come at significant power, performance or cost overheads. We already discussed the overheads of increasing the refresh rates across the board. Similarly, the use of simple SECDED (single-error correcting double-error detecting) error correcting codes (ECC), as employed in many server and datacenter systems, is *not* enough to prevent all RowHammer errors, as some cache blocks experience two or more bit flips, which are not correctable by SECDED ECC, as we have shown in our ISCA 2014 paper [133]. Table I demonstrates this by showing how many 64-bit words in the full address-space (0-2GB) of the most RowHammervulnerable DRAM modules of the three major DRAM manufacturers contain 1, 2, 3, or 4 victim cells. While most words have just a single victim, there are also some words with multiple victims. Thus, stronger ECC is very likely required to correct RowHammer errors, which comes at the cost of additional energy, performance, cost, and DRAM capacity overheads.<sup>4</sup> Alternatively, the sixth solution described above, i.e., accurately identifying a row as a hammered row requires keeping track of access counters for a large number of rows in the memory controller [120], potentially leading to very large hardware area and power consumption, and performance, overheads.

| Module                             | Number of 64-bit words with X errors |             |                |     |

|------------------------------------|--------------------------------------|-------------|----------------|-----|

|                                    | X = 1                                | X = 2       | X = 3          | X=4 |

| A <sub>23</sub><br>B <sub>11</sub> | 9,709,721                            | 181856      | 2248           | 18  |

| $C_{19}$                           | $2,632,280 \\ 141,821$               | 13638<br>42 | <b>47</b><br>0 | 0   |

TABLE I: Uncorrectable multi-bit RowHammer errors (in bold) observed on the most RowHammer-vulnerable module of each DRAM manufacturer A, B, C (reproduced from [133])

There are many other works that propose long-term solutions [28, 30, 40, 68, 81, 82, 88, 111, 128, 134, 152, 213, 222, 226, 243, 245], building on our original work. [226] uses a probabilistic mechanism similar to PARA in the original RowHammer paper in addition to a small stack for maintaining access history information to determine whether adjacent rows need to be refreshed to avoid bit flips. [152, 222, 243, 245] are counter-based defenses that rely on maintaining access counts

<sup>&</sup>lt;sup>4</sup>Note that protecting *all* memory rows with strong ECC is likely a wasteful solution for RowHammer because RowHammer-induced bit-flips are accesspattern dependent; they are not randomly-occurring bit-flips. Since only a small number of rows can be hammered at a given time, paying the capacity, cost, and energy overheads of extra redundancy required for strong ECC for *all* memory rows, solely to protect them against RowHammer, is likely not an efficient solution to the RowHammer problem.

to DRAM rows and refreshing adjacent rows when the access count of a row exceeds a pre-determined threshold. These works focus on reducing the overhead of counting accesses to DRAM addresses to enable a viable implementation of the sixth soution we described above.

We believe the long-term solution to RowHammer can actually be very simple and low cost: when the memory controller closes a row (after it was activated), it, with a very low probability, refreshes the adjacent rows. The probability value is a parameter determined by the system designer or provided programmatically, if needed, to trade off between performance overhead and vulnerability protection guarantees. We show that this probabilistic solution, called *PARA* (*Probabilistic Adjacent Row Activation*), is extremely effective: it eliminates the RowHammer vulnerability, providing much higher reliability guarantees than modern hard disks today, while requiring no storage cost and having negligible performance and energy overheads [133].

PARA is not immediately implementable in an existing system because it requires changes to either the memory controllers or the DRAM chips, depending on where it is implemented. If PARA is implemented in the memory controller, the memory controller needs to obtain information on which rows are adjacent to each other in a DRAM bank. This information is currently unknown to the memory controller as DRAM manufacturers can internally remap rows to other locations [116, 117, 133, 151, 161] for various reasons, including for tolerating various types of faults. However, this information can be simply provided by the DRAM chip to the memory controller using the serial presence detect (SPD) readonly memory present in modern DRAM modules, as described in our ISCA 2014 paper [133]. It appears that some very recent Intel memory controllers implement a limited variant of PARA, whose adjacent-row activation probability can be chosen by the user via modifications in the BIOS [5]. If PARA is implemented in the DRAM chip, then the hardware interface to the DRAM chip should be such that it allows DRAM-internal refresh operations that are not initiated by an external memory controller. This could be achieved with the addition of a new DRAM command, like the targeted refresh command proposed in a patent by Intel [29]. In 3Dstacked memory technologies [130, 150], e.g., HBM (High Bandwidth Memory) [109, 150] or HMC (Hybrid Memory Cube) [7], which combine logic and memory in a tightly integrated fashion, the logic layer can be easily modified to implement PARA.<sup>5</sup> Alternatively, if the memory interface is

asynchronous with the processor, a simple controller that is tightly coupled with the memory chip can freely and easily implement PARA internally to the memory chip.

All these implementations of the promising PARA solution are examples of much better cooperation between memory controller and the DRAM chips. Regardless of the exact implementation, we believe RowHammer, and other upcoming reliability vulnerabilities like RowHammer, can be much more easily found, mitigated, and prevented with better cooperation between and co-design of system and memory, i.e., system-memory co-design [175]. System-memory co-design is explored by recent works for mitigating various DRAMbased security and DRAM scaling issues, including retention failures and performance problems (e.g., [56, 57, 59, 97, 113-117, 125–127, 129, 133, 146, 147, 149, 151, 160, 161, 165, 175, 183, 203, 205, 217-219, 231-233, 237, 238, 252]). Taking the system-memory co-design approach further, providing more intelligence and configurability/programmability/patchability in the memory controller can greatly ease the tolerance to errors like RowHammer: when a new failure mechanism in memory is discovered, the memory controller can be configured/programmed/patched to execute specialized functions to profile and correct for such mechanisms. We believe this direction is very promising, and several works have explored online profiling mechanisms for fixing retention errors [115– 118, 196, 203], reducing latency [151], and reducing energy consumption [58]. These works provide examples of how an intelligent memory controller can alleviate the retention failures, and thus the DRAM refresh problem [160, 161], as well as the DRAM latency problem [146, 147].

## C. Circuit-level Studies of RowHammer

A very recent work [254] presents evidence via 3D CAD simulations with single charge traps, that the RowHammer effect is governed by the charge pumping process. The RowHammer effect is exacerbated when charge is captured around an aggressor wordline and carriers migrate to victim wordlines. The authors also find that feature size scaling aggravates the RowHammer effect, which could make it more difficult to mitigate in future DRAM generations.

[257] provides a study of the effects of irradiating DRAM on the RowHammer phenomenon, with two major findings. First, the study finds that irradiating DRAM with gamma rays increases the number of DRAM rows that are vulnerable to RowHammer. Second, the authors correlate the cells that are vulnerable to RowHammer with those that have low data retention times and they find almost no correlation, corroborating the results of our ISCA 2014 paper.

[157] also irradiates DRAM with gamma rays, which results in cells with lower data retention times and cells with a higher susceptibility to RowHammer failures. The authors then perform *temperature annealing* (i.e., a method for baking DRAM at a high temperature to "repair" retention-weak cells) on the DRAM devices and find that cells that experience a higher susceptibility to RowHammer after irradiation maintain the

<sup>&</sup>lt;sup>5</sup>Alternatively, for a solution like PARA to be implemented in the DRAM chip, without modifying the hardware interface to the DRAM chip, one can exploit the timing slack in the DRAM timing parameters that already exist under various conditions. For example, the timing slack in the specified precharge timing parameter or the refresh latency parameter can be exploited by the DRAM chip itself to internally issue refresh operations to targeted rows with some probability. Even though such timing slack exists in DRAM chips, as shown by many recent experimental studies [57, 69, 125, 147, 151], we do not believe this is a robust solution since 1) the timing slack may not exist under all operating conditions or for all chips, 2) many studies would like to reduce the timing slack as much as possible to improve DRAM performance and energy [57, 69, 125, 147, 151].

higher susceptibility to RowHammer even after temperature annealing.

[210] presents evidence that hydrogen (H2) annealing of cell-transistors during the dry etch process shows a reduction in interface trap density. Since the RowHammer failure is mainly caused by the traps in the interface (according to the authors' hypotheses), the authors show that this technique can help to improve DRAM reliability against crosstalk and thus alleviate RowHammer attacks.

[192] and [193] experimentally test DDR3 devices for RowHammer susceptibility, show statistical distributions of RowHammer failures across many devices, and present evidence that the root cause of the RowHammer phenomenon is charge recombination of the victim cell with electrons from the current channels between neighboring cells and their corresponding bitlines.

#### D. Other Works Exploiting RowHammer

There are other papers that build upon RowHammer but do not necessarily show a RowHammer attack or defense. One work shows that the RowHammer phenomenon can be used as a security primitive. [212] shows that RowHammer can be used as an effective Physical Unclonable Function (PUF), a function that generates unique identifiers (i.e., fingerprints) of a device based on the unique properties of the device due to manufacturing variation. The authors experimentally show that by reserving a region of memory and inducing RowHammer failures in each of the rows of the region, they can generate bit flips in the region whose locations are unique to the device and can be used to identify the device. A more recent work [258] presents an attack on the RowHammer-based PUF [212] by effectively showing that hammering on rows surrounding the region reserved by the RowHammer-based PUF causes the rows at the edges of the reserved DRAM region to have an increased number of bit flips. This results in a modification of the resulting fingerprint, which then results in an unidentifiable device.

## E. Platforms for Studying RowHammer

Many prior works present ways to make studying RowHammer easier. [74] describes their Raspberry Pi Operating System for exploring memory concepts simply due to a direct linear mapping between virtual addresses to physical addresses. This mitigates the difficulty of determining which DRAM rows are physically adjacent. SoftMC [98, 225] is an FPGAbased memory controller implementation that enables testing custom DRAM timing parameter values with direct access to DRAM physical addresses. Drammer [70, 71] is an opensource Android application that tests mobile devices for vulnerability to the RowHammer exploit and gathers data from users to determine how widespread the RowHammer vulnerability is across many generations of mobile devices. MemTest86 [194] is software that tests DRAM for many types of reliability issues. As described above, after our original ISCA 2014 paper, MemTest86 developers added RowHammer testing to their suite, which enables users to test their system for the RowHammer vulnerability. [31, 107, 190] provide methods for reverse engineering DRAM address mapping such that attackers can determine the two rows that surround a victim row and hammer the victim row more effectively for causing RowHammer failures. [244] provides an algorithm for determining the eviction set of cache lines in linear time such that an attacker can maximize accesses to DRAM even when caching is unavoidable. [17] repurposes a DDR protocol analyzer with a DIMM interposer to count the activations to each row within a 64 ms interval to detect whether RowHammer occurs in any application.

## F. Media References to RowHammer

Our ISCA 2014 work also turned RowHammer into a popular phenomenon (e.g., [1, 2, 16, 39, 65, 83–85, 94, 105, 119, 139, 141, 187–189, 194, 211, 216, 239, 240, 246]), which, in turn, has helped make hardware security even more "mainstream" in popular media and the broader security community. It showed that hardware reliability problems can be very serious security threats that have to be defended against. A well-read article from the Wired magazine, all about RowHammer, is entitled "Forget Software - Now Hackers are Exploiting Physics!" [86], indicating the shift of mindset towards very low-level hardware security vulnerabilities in the popular mainstream security community. Many other popular articles in press have been written about RowHammer, many of which pointing to our ISCA 2014 work [133] as the first demonstration and scientific analysis of the RowHammer problem. Showing that hardware reliability problems can be serious security threats and pulling them to the popular discussion space, and thus influencing the mainstream discourse, creates a very long term impact for the RowHammer problem and thus our original ISCA 2014 paper.

# G. Persistence of RowHammer Failures in Modern DRAM

Unfortunately, despite the many proposals in industry and academia to fix the RowHammer issue, RowHammer failures still seem to be observable in state-of-the-art DRAM devices in a variety of generations and standards (e.g., DDR4 [12, 17, 141, 198], ECC DRAM [66], LPDDR3 and LPDDR2 DRAM [241]). This persisting phenomenon suggests that the security vulnerabilities might continue in the current generation of DRAM chips as well. As such, it is critical to continue to investigate solutions to the RowHammer vulnerability.

#### H. RowHammer in a Broader Context

Springing off from the stir created by RowHammer, we take a step back and argue that there is little that is surprising about the fact that we are seeing disturbance errors in the heavily-scaled DRAM chips of today. Disturbance errors are a general class of reliability problems that is present in not only DRAM, but also other memory and storage technologies. All scaled memory technologies, including SRAM [62, 93, 121], flash [42, 45, 46, 50–53, 67, 167, 168, 171, 214], and hard disk drives [110, 234, 249], exhibit such disturbance problems. In

fact, two of our works experimentally examine read disturb errors in flash memory: 1) our original work in DATE 2012 [42] that provides a rigorous experimental study of error patterns in modern MLC NAND flash memory chips demonstrates the importance of read disturb error patterns, 2) our recent work at DSN 2015 [51] experimentally characterizes the read disturb errors in flash memory, shows that the problem is widespread in recent flash memory chips, and develops mechanisms to correct such errors in the flash memory controller. Even though the mechanisms that cause the bit flips are different in different technologies, the high-level root cause of the problem, cell-tocell interference, due to the fact that the memory cells are too close to each other, is a fundamental issue that appears and will likely continue to appear in any technology that scales down to small enough technology nodes [53, 254]. Thus, we should expect such problems to continue as we scale any memory technology, including emerging ones, to higher densities.

What sets DRAM disturbance errors apart from other technologies' disturbance errors is that 1) DRAM is exposed to the user-level programs and manipulated directly by a program's load and store instructions (which we do not anticipate to change any time soon, since direct data manipulation in main memory is a fundamental component of programming languages and systems), and 2) in modern DRAM, as opposed to other technologies, strong error correction mechanisms are not commonly employed (either in the memory controller or the memory chip). The success of DRAM scaling until recently has not relied on a memory controller that corrects errors (other than performing periodic refresh and more recently employing very simple single-error correcting codes [9, 113, 185, 186, 191, 195]). Instead, DRAM chips were implicitly assumed to be error-free and did not require the help of the controller to operate correctly. Thus, such errors were perhaps not as easily anticipated and corrected within the context of DRAM. In contrast, the success of other technologies, e.g., flash memory and hard disks, has heavily relied on the existence of an intelligent controller that plays a key role in correcting errors and making up for reliability problems of the memory chips themselves [52]. This has not only enabled the correct operation of assumed-faulty memory chips but also enabled a mindset where the controllers are codesigned with the chips themselves, covering up the memory technology's deficiencies and hence perhaps enabling better anticipation of errors with technology scaling. This approach is very prominent in modern SSDs (solid state drives), for example, where the flash memory controller employs a wide variety of error mitigation and correction mechanisms [42-48, 50–53, 166], including not only sophisticated strong ECC mechanisms but also targeted voltage optimization, retention mitigation and disturbance mitigation techniques. We believe changing the mindset in modern DRAM to a similar mindset of assumed-faulty memory chip and an intelligent memory controller that makes it operate correctly can not only enable better anticipation and correction of future issues like RowHammer but also better scaling of DRAM into future technology nodes [175].

#### IV. ONGOING AND FUTURE WORK

We believe there is a lot more research to come that will build on RowHammer, from at least three perspectives: 1) the security attack perspective, 2) the defense/mitigation perspective, 3) a broader understanding, modeling, and prevention perspective.

As systems security researchers understand more about RowHammer, and as the RowHammer phenomenon continues to fundamentally affect memory chips due to technology scaling problems [176], researchers and practitioners will develop different types of attacks to exploit RowHammer in various contexts and in many more creative ways. RowHammer is a critical problem that manifests in the difficulties in DRAM scaling and is expected to only become worse in the future [177, 182, 183]. As we discussed, some recent reports suggest that new-generation DRAM chips are vulnerable to RowHammer (e.g., DDR4 [12, 17, 141, 198], ECC [66, 133], LPDDR3 and LPDDR2 [241]). This indicates that effectively mitigating the RowHammer problem with low overhead is difficult and becomes more difficult as process technology scales further. Even with the wide array of works that build on top of RowHammer, we believe that these papers have yet to scratch the surface of this field of reliability and security, especially as manufacturing technology scaling continues in all technologies. It is critical to deeply understand the underlying factors of the RowHammer problem (and more generally the crosstalk problem) such that we can effectively prevent these issues across all technologies with minimal overhead. As DRAM cells become even smaller and less reliable, it is likely for them to become even more vulnerable to complicated and different modes of failure that are sensitized only under specific access-patterns and/or data-patterns. As a scalable solution for the future, our ISCA 2014 paper argues for adopting a system-level approach [175] to DRAM reliability and security, in which the DRAM chips, the memory controller, and perhaps the operating system collaborate together to diagnose/treat emerging DRAM failure modes.

We believe that more and more researchers will focus on providing security in all aspects of computing so that such hardware faults that are exposed to the software (and thus the public) are minimized. RowHammer enabled a shift of mindset among mainstream security researchers: generalpurpose hardware is fallible (in a very widespread manner) and its problems are actually exploitable. This shift of mindset enabled many systems security researchers to examine hardware in more depth and understand its inner workings and vulnerabilities better. We believe it is no coincidence that two of the groups that concurrently discovered the heavilypublicized Meltdown [159] and Spectre [136] vulnerabilities (Google Project Zero and TU Graz InfoSec) have heavily worked on RowHammer attacks before. We believe this shift in mindset, enabled in good part by the existence and prevalence of RowHammer, will continue to be very be important for discovering and solving other potential vulnerabilities that may rise as a result of both technology scaling and hardware design.

#### A. Other Potential Vulnerabilities

We believe that, as memory technologies scale to higher densities, other problems may start appearing (or may already be going unnoticed) that can potentially threaten the foundations of secure systems. There have been recent largescale field studies of memory errors showing that both DRAM and NAND flash memory technologies are becoming less reliable [42, 50, 52, 53, 167, 168, 171, 172, 175, 176, 183, 196, 214, 227-229]. As detailed experimental analyses of real DRAM and NAND flash chips show, both technologies are becoming much more vulnerable to cell-to-cell interference effects [42, 45–48, 51–53, 133, 166, 175, 176, 178, 183], data retention is becoming significantly more difficult in both technologies [42-44, 46, 50, 52, 53, 59, 113, 115-117, 160, 161, 164, 167–169, 175, 178, 183, 203], and error variation within and across chip, and across operating conditions, is increasingly prominent [42, 46, 55, 57, 125– 127, 147, 151, 161]. Emerging memory technologies [170, 175], such as Phase-Change Memory [142–144, 202, 204, 206, 247, 255, 256, 261], STT-MRAM [61, 138], and RRAM/ReRAM/memristors [248] are likely to exhibit similar and perhaps even more exacerbated reliability issues. We believe, if not carefully accounted for and corrected, these reliability problems may surface as security problems as well, as in the case of RowHammer, especially if the technology is employed as part of the main memory system that is directly exposed to user-level programs.

We briefly examine two example potential vulnerabilities. We believe future work examining these vulnerabilities, among others, are promising for both fixing the vulnerabilities and enabling the effective scaling of memory technology.

1) Data Retention Failures: Data retention is a fundamental reliability problem, and hence a potential vulnerability, in especially charge-based memories like DRAM and flash memory. This is because charge leaks out of the charge storage unit (e.g., the DRAM capacitor or the NAND flash floating gate) over time. As such memories become denser, three major trends make data retention more difficult [50, 113, 160, 161]. First, the number of memory cells increases, leading to the need for more refresh operations to maintain data correctly. Second, the charge storage unit (e.g., the DRAM capacitor) becomes smaller and/or morphs in structure, leading to potentially lower retention times. Third, the voltage margins that separate one data value from another become smaller (e.g., the same voltage window gets divided into more "states" in NAND flash memory, to store more bits per cell), and, as a result, the same amount of charge loss is more likely to cause a bit error in a smaller technology node than in a larger one.

#### **DRAM Data Retention Issues**

Data retention issues in DRAM are a fundamental scaling limiter of the DRAM technology [113, 161, 175]. We have shown, in recent works based on rigorous experimental analyses of modern DRAM chips [115, 117, 118, 161, 196, 203], that determining the minimum retention time of a DRAM cell is getting significantly more difficult. Thus, determining the

correct rate at which to refresh DRAM cells has become more difficult, as also indicated by industry [113]. This is due to two major phenomena, both of which get worse (i.e., become more prominent) with technology scaling. First, Data Pattern Dependence (DPD): the retention time of a DRAM cell is heavily dependent on the data pattern stored in itself and in the neighboring cells [161]. Second, Variable Retention Time (VRT): the retention time of some DRAM cells can change drastically over time, due to a memoryless random process that results in very fast charge loss via a phenomenon called trap-assisted gate-induced drain leakage [161, 209, 253]. These phenomena greatly complicate the accurate determination of minimum data retention time of DRAM cells. In fact, VRT, as far as we know, is very difficult to test for because there seems to be no way of determining that a cell exhibits VRT until that cell is observed to exhibit VRT and the time scale of a cell exhibiting VRT does not seem to be bounded, given the current experimental data [115, 161, 196, 203]. As a result, some retention errors can easily slip into the field because of the difficulty of the retention time testing. Therefore, data retention in DRAM is a vulnerability that can greatly affect both reliability and security of current and future DRAM generations. We encourage future work to investigate this area further, from both reliability and security, as well as performance and energy efficiency perspectives. Various works in this area provide insights about the retention time properties of modern DRAM devices based on experimental data [98, 115, 117, 118, 161, 196, 203], develop infrastructures to obtain valuable experimental data [98], and provide potential solutions to the DRAM retention time problem [59, 115– 118, 160, 161, 196, 203], all of which the future works can build on.

Note that data retention failures in DRAM are likely to be investigated heavily to ensure good performance and energy efficiency. And, in fact they already are being investigated for this purpose (see, for example, [59, 115–118, 160, 196, 203]). We believe it is important for such investigations to ensure no new vulnerabilities (e.g., side channels) open up due to the solutions developed.

# NAND Flash Data Retention Issues

Experimental analysis of modern flash memory devices show that the dominant source of errors in flash memory are data retention errors [42, 52]. As a flash cell wears out, its charge retention capability degrades [42, 50, 52, 53, 167, 168, 171, 214] and the cell becomes leakier. As a result, to maintain the original data stored in the cell, the cell needs to be refreshed [43, 44]. The frequency of refresh increases as wearout of the cell increases. We have shown that performing refresh in an adaptive manner greatly improves the lifetime of modern MLC (multi-level cell) NAND flash memory while causing little energy and performance overheads [43, 44]. Most high-end SSDs today employ such adaptive refresh mechanisms.

As flash memory scales to smaller manufacturing technology nodes and even more bits per cell, data retention becomes a bigger problem. As such, it is critical to understand the issues with data retention in flash memory. Our recent work provides detailed experimental analysis of data retention behavior of planar and 3D MLC NAND flash memory [50, 52, 53, 167, 168]. We show, among other things, that there is a wide variation in the leakiness of different flash cells: some cells leak very fast, some cells leak very slowly. This variation leads to new opportunities for correctly recovering data from a flash device that has experienced an uncorrectable error: by identifying which cells are fast-leaking and which cells are slow-leaking, one can probabilistically estimate the original values of the cells before the uncorrectable error occurred. This mechanism, called Retention Failure Recovery, leads to significant reductions in bit error rate in modern MLC NAND flash memory [50, 52, 53] and is thus very promising. Unfortunately, it also points to a potential security and privacy vulnerability: by analyzing data and cell properties of a failed device, one can potentially recover the original data. We believe such vulnerabilities can become more common in the future and therefore they need to be anticipated, investigated, and understood.

2) Other Vulnerabilities in NAND Flash Memory: We believe other sources of error (e.g., cell-to-cell interference) and cell-to-cell variation in flash memory can also lead various vulnerabilities. For example, another type of variation (that is similar to the variation in cell leakiness that we described above) exists in the vulnerability of flash memory cells to read disturbance [51]: some cells are much more prone to read disturb effects than others. This wide variation among cells enables one to probabilistically estimate the original values of cells in flash memory after an uncorrectable error has occurred. Similarly, one can probabilistically correct the values of cells in a page by knowing the values of cells in the neighboring page [47]. These mechanisms [47, 51] are devised to improve flash memory reliability and lifetime, but the same phenomena that make them effective in doing so can also lead to potential vulnerabilities, which we believe are worthy of investigation to ensure security and privacy of data in flash memories.

As an example, we have recently shown [48] that it is theoretically possible to exploit vulnerabilities in flash memory programming operations on existing solid-state drives (SSDs) to cause (malicious) data corruption. This particular vulnerability is caused by the two-step programming method employed in dense flash memory devices, e.g., MLC NAND flash memory. An MLC device partitions the threshold voltage range of a flash cell into four distributions. In order to reduce the number of errors introduced during programming of a cell, flash manufacturers adopt a two-step programming method, where the least significant bit of the cell is partially programmed first to some intermediate threshold voltage, and the most significant bit is programmed later to bring the cell up to its full threshold voltage. We find that two-step programming exposes new vulnerabilities, as both cell-tocell program interference and read disturbance can disrupt the intermediate value stored within a multi-level cell before the second programming step completes. We show that it is possible to exploit these vulnerabilities on existing solid-state drives (SSDs) to alter the partially-programmed data, causing (malicious) data corruption. We experimentally characterize the extent of these vulnerabilities using contemporary 1X-nm (i.e., 15-19nm) flash chips [48]. Building on our experimental observations, we propose several new mechanisms for MLC NAND flash that eliminate or mitigate disruptions to intermediate values, removing or reducing the extent of the vulnerabilities, mitigating potential exploits, and increasing flash lifetime by 16% [48]. We believe investigation of such vulnerabilities in flash memory will lead to more robust flash memory devices in terms of both reliability and security, as well as performance. In fact, a recent work from IBM builds on our work [48] to devise a security attack at the file system level [140].

#### B. Prevention

Various reliability problems experienced by scaled memory technologies, if not carefully anticipated, accounted for, and corrected, may surface as security problems as well, as in the case of RowHammer. We believe it is critical to develop principled methods to understand, anticipate, and prevent such vulnerabilities. In particular, principled methods are required for three major steps in the design process.

First, it is critical to understand the potential failure mechanisms and anticipate them beforehand. To this end, developing solid methodologies for failure modeling and prediction is critical. To develop such methodologies, it is essential to have real experimental data from past and present devices. Data available both at the small scale (i.e., data obtained via controlled testing of individual devices, as in, e.g., [42–53, 57, 115, 125–127, 147, 161, 166–168, 195, 196]) as well as at the large scale (i.e., data obtained during in-the-field operation of the devices, under likely-uncontrolled conditions, as in, e.g., [171, 172]) can enable accurate models for failures, which could aid many purposes, including the development of better reliability mechanisms and prediction of problems before they occur.

Second, it is critical to develop principled architectural methods that can avoid, tolerate, or prevent such failure mechanisms that can lead to vulnerabilities. For this, we advocate co-architecting of the system and the memory together, as we described earlier. Designing intelligent, flexible, configurable, programmable, patch-able memory controllers that can understand and correct existing and potential failure mechanisms can greatly alleviate the impact of failure mechanisms on reliability, security, performance, and energy efficiency. A system-memory co-design approach can also enable new opportunities, like performing effective processing near or in the memory device (e.g., [13–15, 18, 22, 24, 34–36, 56, 63, 72, 77, 78, 80, 91, 92, 95, 96, 99, 101–103, 112, 122–124, 153, 155, 156, 162, 163, 174, 180, 181, 184, 197, 200, 217– 221, 223, 224, 230, 259, 262]). In addition to designing the memory device together with the controller, we believe it is important to investigate mechanisms for good partitioning of duties across the various levels of transformation in computing, including system software, compilers, and application software.

Third, it is critical to develop principled methods for electronic design, automation and testing, which are in harmony with the failure modeling/prediction and system reliability methods, which we mentioned in the above two paragraphs. Design, automation and testing methods need to provide high and predictable coverage of failures and work in conjunction with architectural and across-stack mechanisms. For example, enabling effective and low-cost *online profiling of DRAM* [115–117, 151, 161, 196, 203] in a principled manner requires cooperation of failure modeling mechanisms, architectural methods, and design, automation and testing methods.

## V. CONCLUSION

We provided a retrospective on the RowHammer problem and our original ISCA 2014 paper [133] that introduced the problem, and a survey of many flourishing works that have built on RowHammer. It is clear that the reliability of memory technologies we greatly depend on is reducing, as these technologies continue to scale to ever smaller technology nodes in pursuit of higher densities. These reliability problems, if not anticipated and corrected, can also open up serious security vulnerabilities, which can be very difficult to defend against, if they are discovered in the field. RowHammer is an example, likely the first one, of a hardware failure mechanism that causes a practical and widespread system security vulnerability. As such, its implications on system security research are tremendous and exciting. We hope the summary, retrospective, and commentary we provide in this paper on the RowHammer phenomenon are useful for understanding the RowHammer problem, its context, mitigation mechanisms, and the large body of work that has built on it in the past five years.

We believe that the need to prevent such reliability and security vulnerabilities at heavily-scaled memory technologies opens up new avenues for principled approaches to 1) understanding, modeling, and prediction of failures and vulnerabilities, and 2) architectural as well as design, automation and testing methods for ensuring reliable and secure operation. We believe the future is very bright for research in reliable and secure memory systems, and many discoveries abound in the exciting yet complex intersection of reliability and security issues in such systems.

## ACKNOWLEDGMENTS

This paper is based on two previous papers we have written on RowHammer, one that first scientifically introduced and analyzed the phenomenon in ISCA 2014 [133] and the other that provided an analysis and future outlook on RowHammer [176]. The presented work is a result of the research done together with many students and collaborators over the course of the past eight years. In particular, three PhD theses have shaped the understanding that led to this work. These are Yoongu Kim's thesis entitled "Architectural Techniques to Enhance DRAM Scaling" [132], Yu Cai's thesis entitled "NAND Flash Memory: Characterization, Analysis, Modeling

and Mechanisms" [49] and his continued follow-on work after his thesis, summarized in [52, 53], and Donghyuk Lee's thesis entitled "Reducing DRAM Latency at Low Cost by Exploiting Heterogeneity" [145]. We also acknowledge various funding agencies (NSF, SRC, ISTC, CyLab) and industrial partners (AliBaba, AMD, Google, Facebook, HP Labs, Huawei, IBM, Intel, Microsoft, Nvidia, Oracle, Qualcomm, Rambus, Samsung, Seagate, VMware) who have supported the presented and other related work in our group generously over the years.

The first version of the talk associated with this paper was delivered at a CMU CyLab Partners Conference in September 2015. Other versions of the talk were delivered as part of an Invited Session at DAC 2016, with a collaborative accompanying paper entitled "Who Is the Major Threat to Tomorrow's Security? You, the Hardware Designer" [41], at DATE 2017 [176], and at the Top Picks in Hardware and Embedded Security workshop, co-located with ICCAD 2018 [11], where RowHammer was selected as a Top Pick among hardware and embedded security papers published between 2012-2017. The most recent version of the associated talk was delivered at COSADE 2019 [179].

#### REFERENCES

- [1] "RowHammer Discussion Group," https://groups.google.com/forum/\#!forum/rowhammer-discuss.

- [2] "RowHammer on Twitter," https://twitter.com/search?q=rowhammer

- [3] "Rowhammer: Source Code for Testing the Row Hammer Error Mechanism in DRAM Devices." https://github.com/CMU-SAFARI/rowhammer.

- [4] "Test DRAM for Bit Flips Caused by the RowHammer Problem," https://github.com/google/rowhammer-test.

- [5] "Tweet about RowHammer Mitigation on x210," https://twitter.com/isislovecruft/ status/1021939922754723841.

- [6] "RDMA Consortium," http://www.rdmaconsortium.org, 2009.

- [7] Hybrid Memory Consortium, 2012, http://www.hybridmemorycube.org.

- [8] "apt-get Linux man page," https://linux.die.net/man/8/apt-get, 2017.

- [9] "ECC Brings Reliability and Power Efficiency to Mobile Devices," Micron Technology inc., Tech. Rep., 2017.

- [10] "OpenSSH," https://www.openssh.com/, 2017.

- [11] "Top Picks in Hardware and Embedded Security Workshop Collocated with ICCAD 2018," https://wp.nyu.edu/toppicksinhardwaresecurity/, 2017.

- [12] M. T. Aga et al., "When Good Protections go Bad: Exploiting anti-DoS Measures to Accelerate Rowhammer Attacks," in HOST, 2017.

- [13] S. Aga *et al.*, "Compute caches," in *HPCA*, 2017.

- [14] J. Ahn et al., "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing," in ISCA, 2015.

- [15] J. Ahn et al., "PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture," in ISCA, 2015.

- [16] B. Aichinger, "The Known Failure Mechanism in DDR3 Memory referred to as Row Hammer," http://ddrdetective.com/files/6414/1036/5710/The\_Known\_Failure\_Mechanism\_in\_DDR3\_memory\_referred\_to\_as\_Row\_Hammer.pdf, September 2014.

- [17] B. Aichinger, "DDR Memory Errors Caused by Row Hammer," in HPEC, 2015.

- [18] B. Akin et al., "Data Reorganization in Memory using 3D-stacked DRAM," in ISCA, 2015.

- [19] Z. Al-Ars et al., "DRAM-Specific Space of Memory Tests," in ITC, 2006.

- [20] Z. Al-Ars, "DRAM Fault Analaysis and Test Generation," Ph.D. dissertation, TU Delft, 2005.

- [21] Apple Inc., "About the security content of Mac EFI Security Update 2015-001," https://support.apple.com/en-us/HT204934, June 2015.

- [22] H. Asghari-Moghaddam et al., "Chameleon: Versatile and Practical Near-DRAM Acceleration Architecture for Large Memory Systems," in MICRO, 2016.

- [23] Z. B. Aweke et al., "Anvil: Software-based protection against next-generation rowhammer attacks," in ASPLOS, 2016.

- [24] O. O. Babarinsa and S. Idreos, "JAFAR: Near-data Processing for Databases," in SIGMOD, 2015.

- [25] K. Bains *et al.*, "Row Hammer Refresh Command," US Patent App. 14/068,677, Feb. 27 2014.

[26] K. Bains *et al.*, "Method, Apparatus and System for Providing a Memory Refresh."

- US Patent App. 13/625,741, Mar. 27 2014. [27] K. Bains *et al.*, "Row Hammer Refresh Command," US Patent App. 13/539,415,

- [27] K. Bains et al., "Row Hammer Refresh Command," US Patent App. 13/539,415 Jan. 2 2014.

- [28] K. Bains and J. Halbert, "Distributed Row Hammer Tracking," US Patent App. 13/631,781, Apr. 3 2014.

- [29] K. Bains et al., "Row hammer refresh command," U.S. Patent Number 9117544 B2 2015

- [30] K. S. Bains and J. B. Halbert, "Row Hammer Monitoring Based on Stored Row Hammer Threshold Value," uS Patent 9,032,141. May 12 2015.

- [31] A. Barenghi et al., "Software-only Reverse Engineering of Physical DRAM Mappings for Rowhammer Attacks," in IVSW, 2018.

- [32] S. Bhattacharya and D. Mukhopadhyay, "Curious Case of RowHammer: Flipping Secret Exponent Bits using Timing Analysis," in CHES, 2016.

- [33] S. Bhattacharya and D. Mukhopadhyay, "Advanced Fault Attacks in Software: Exploiting the Rowhammer Bug," in Fault Tolerant Architectures for Cryptography and Hardware Security, 2018.

- A. Boroumand et al., "LazyPIM: An Efficient Cache Coherence Mechanism for

- Processing-in-Memory," *IEEE CAL*, 2016.

[35] A. Boroumand *et al.*, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks," in ASPLOS, 2018.

- [36] A. Boroumand et al., "CoNDA: Enabling Efficient Near-Data Accelerator Communication by Optimizing Data Movement," ISCA, 2019.

- [37] E. Bosman et al., "Dedup Est Machina: Memory Deduplication as an Advanced Exploitation Vector," S&P, 2016.

- [38] F. Brasser et al., "Can't Touch This: Practical and Generic Software-only Defenses Against RowHammer Attacks," USENIX Sec., 2017.

- [39] S. Brown, "Rowhammer: The Evolution of a New Generation of Attacks," https: //cyware.com/news/rowhammer-the-evolution-of-a-new-generation-of-attacks-7baa0a3c, December 2018.

- L. Bu et al., "SRASA: a Generalized Theoretical Framework for Security and Reliability Analysis in Computing Systems," Journal of Hardware and Systems Security, 2018.

- [41] W. Burleson et al., "Who Is the Major Threat to Tomorrow's Security? You, the Hardware Designer," DAC, 2016.

- [42] Y. Cai et al., "Error Patterns in MLC NAND Flash Memory: Measurement, Characterization, and Analysis," in DATE, 2012.

- [43] Y. Cai et al., "Flash Correct-and-Refresh: Retention-Aware Error Management for Increased Flash Memory Lifetime," in ICCD, 2012.

- [44] Y. Cai et al., "Error Analysis and Retention-Aware Error Management for NAND

- Flash Memory," *IIJ*, 2013. [45] Y. Cai *et al.*, "Program Interference in MLC NAND Flash Memory: Characterization, Modeling, and Mitigation," in ICCD, 2013.

- [46] Y. Cai et al., "Threshold Voltage Distribution in MLC NAND Flash Memory: Characterization, Analysis and Modeling," in DATE, 2013.

- Y. Cai et al., "Neighbor-Cell Assisted Error Correction for MLC NAND Flash Memories," in SIGMETRICS, 2014.

- [48] Y. Cai et al., "Vulnerabilities in MLC NAND Flash Memory Programming: Experimental Analysis, Exploits, and Mitigation Techniques," in HPCA, 2017.

- [49] Y. Cai, "NAND flash memory: Characterization, Analysis, Modeling and Mechanisms," Ph.D. dissertation, Carnegie Mellon University, 2012.

- [50] Y. Cai et al., "Data Retention in MLC NAND Flash Memory: Characterization, Optimization and Recovery," in HPCA, 2015.

- Y. Cai et al., "Read Disturb Errors in MLC NAND Flash Memory: Characterization, Mitigation, and Recovery," in DSN, 2015.

- [52] Y. Cai et al., "Error Characterization, Mitigation, and Recovery in Flash-memorybased Solid-state Drives," Proceedings of the IEEE, 2017.

- Y. Cai et al., "Errors in Flash-Memory-Based Solid-State Drives: Analysis, [53] Mitigation, and Recovery," arXiv preprint arXiv:1711.11427, 2017.

- [54] S. Carre et al., "OpenSSL Bellcore's Protection Helps Fault Attack," in DSD, 2018.

- K. Chandrasekar et al., "Exploiting Expendable Process-margins in DRAMs for [55] Run-time Performance Optimization," in DATE, 2014.