### SynCron Efficient Synchronization Support for Near-Data-Processing Architectures

#### **Christina Giannoula**

Nandita Vijaykumar, Nikela Papadopoulou, Vasileios Karakostas Ivan Fernandez, Juan Gómez Luna, Lois Orosa Nectarios Koziris, Georgios Goumas, Onur Mutlu

## SAFARI

**ETH** zürich

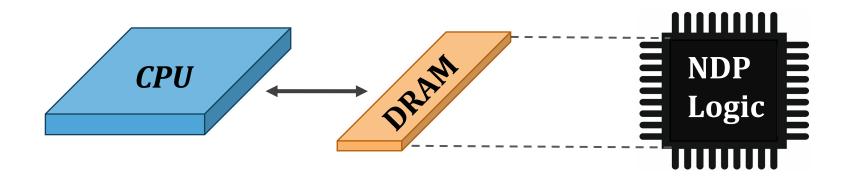

### Near-Data-Processing (NDP) Systems

Neural Networks

**Graph Analytics**

#### **Recommendation Systems**

**Bioinformatics**

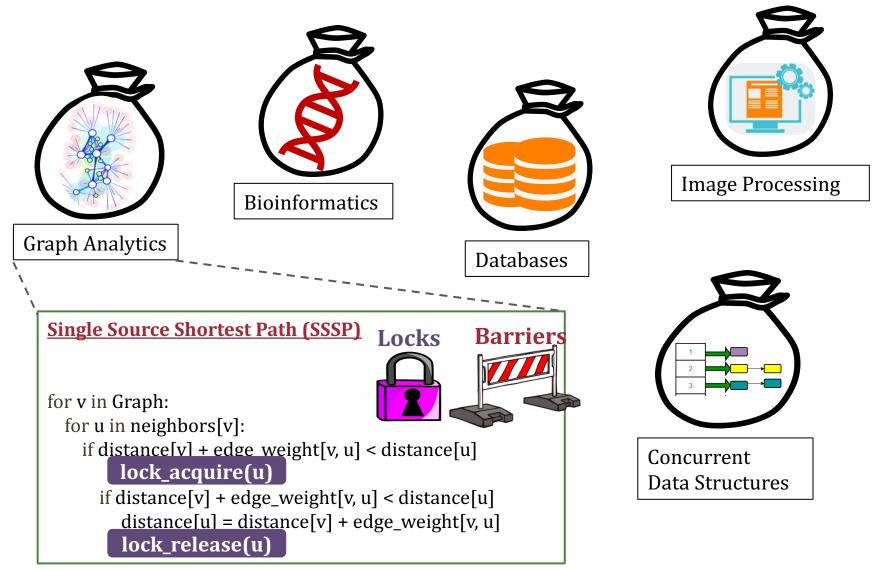

### Synchronization is Necessary

### **Challenge: Efficient Synchronization**

## The first end-to-end synchronization solution for NDP architectures

### SynCron's Benefits:

- 1. High System Performance

- 2. Low Hardware Cost

- 3. Programming Ease

- 4. General Synchronization Support

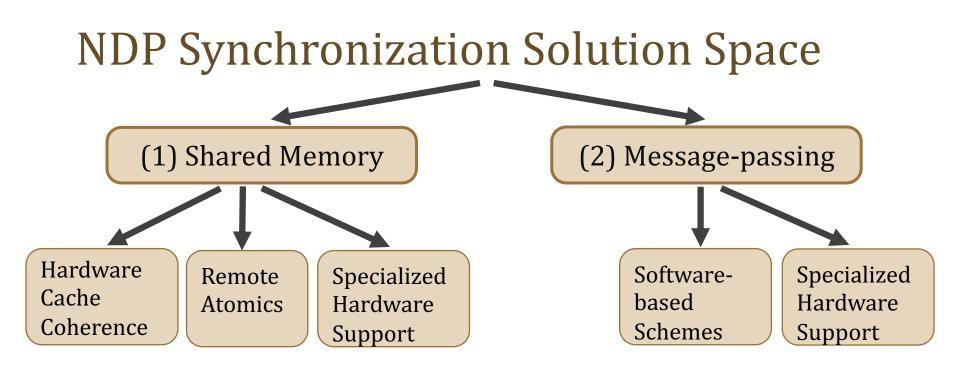

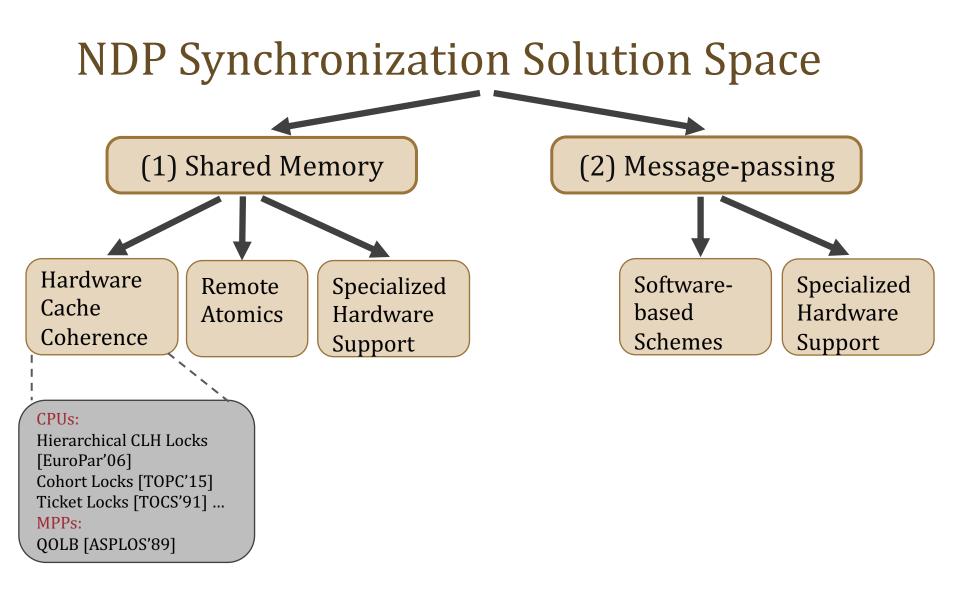

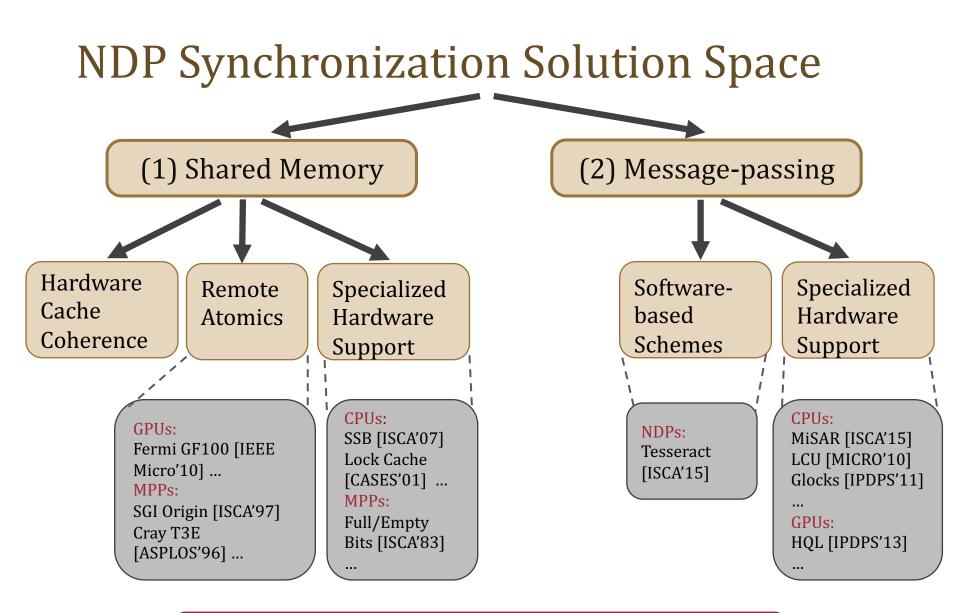

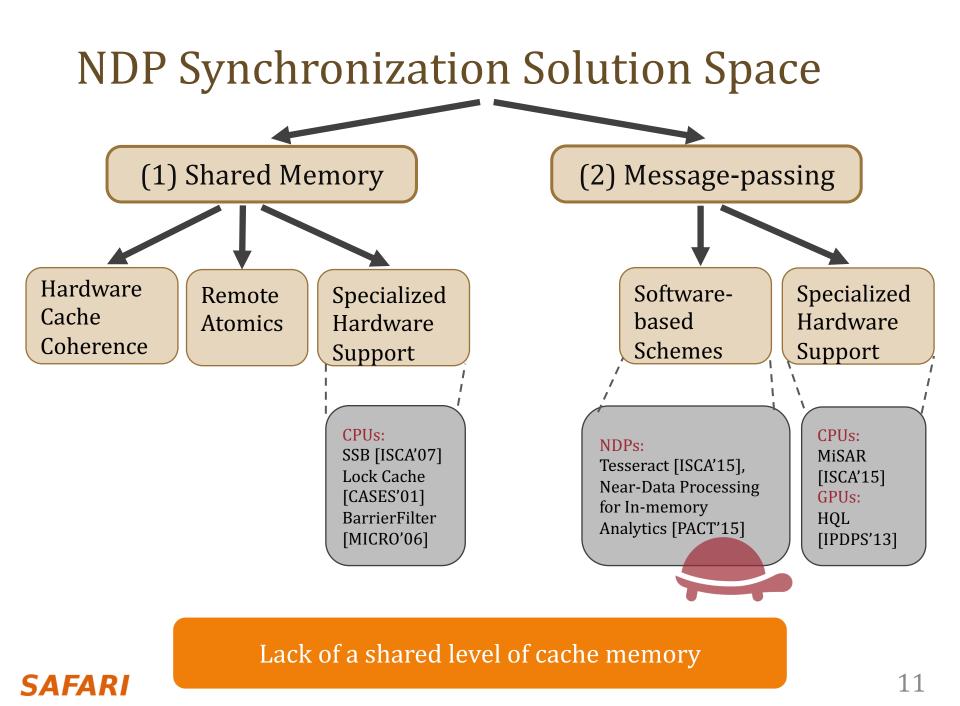

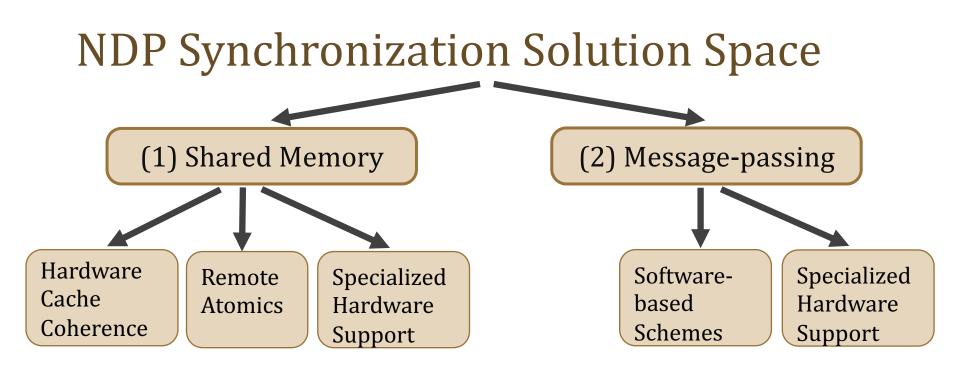

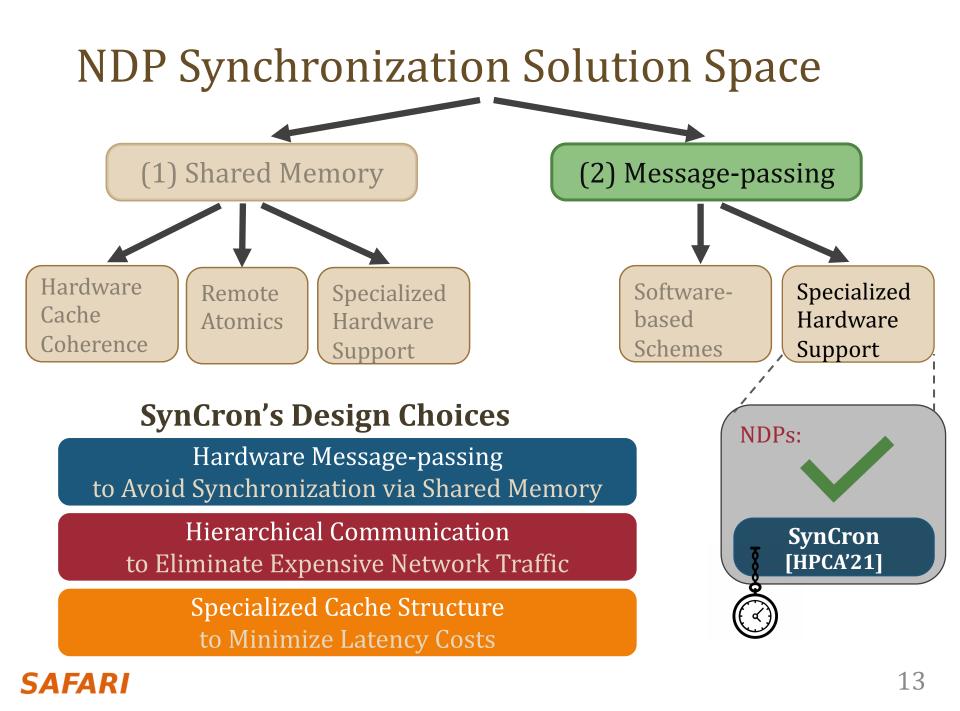

### NDP Synchronization Solution Space

### Our Mechanism: SynCron

Evaluation

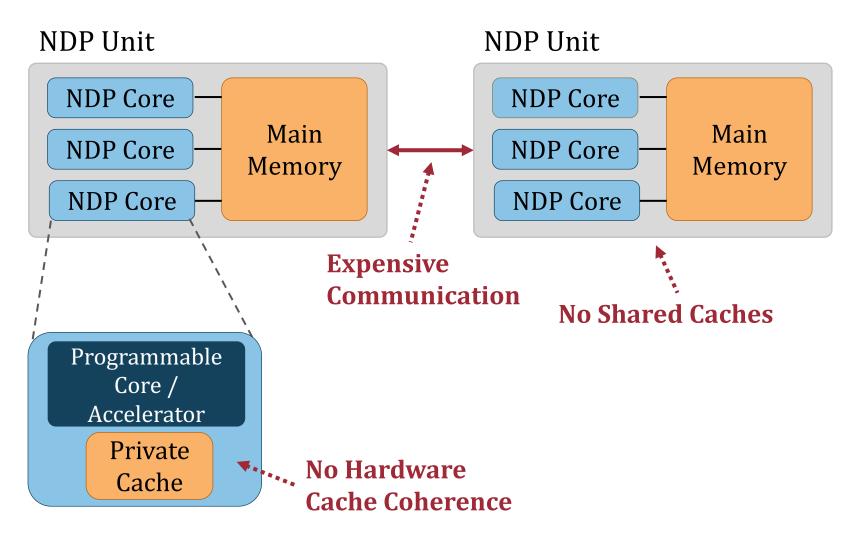

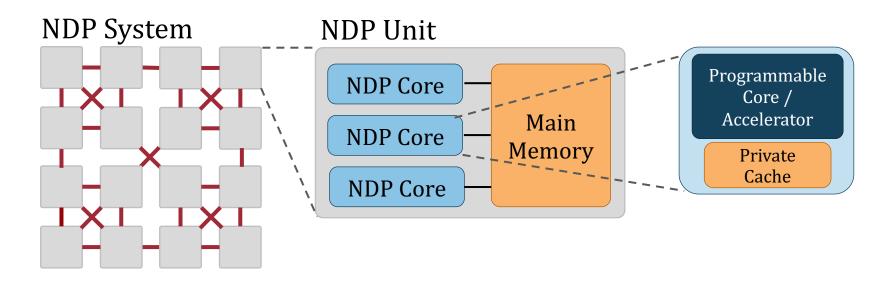

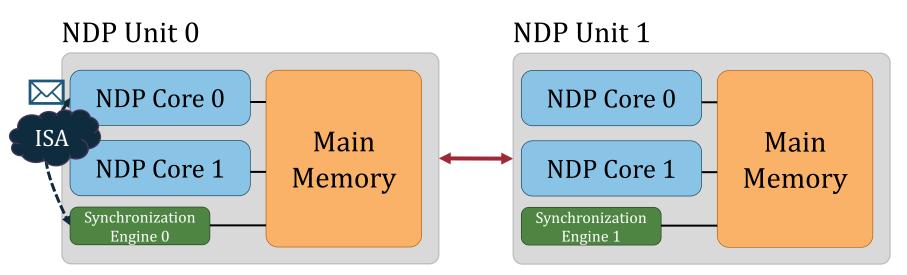

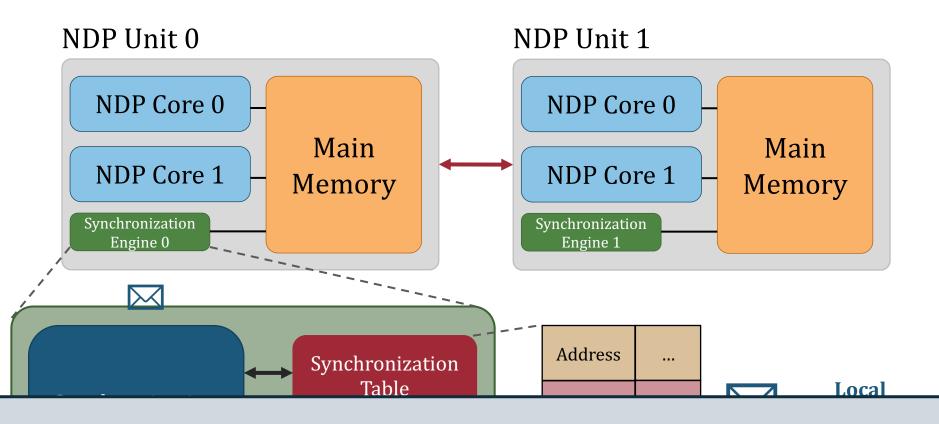

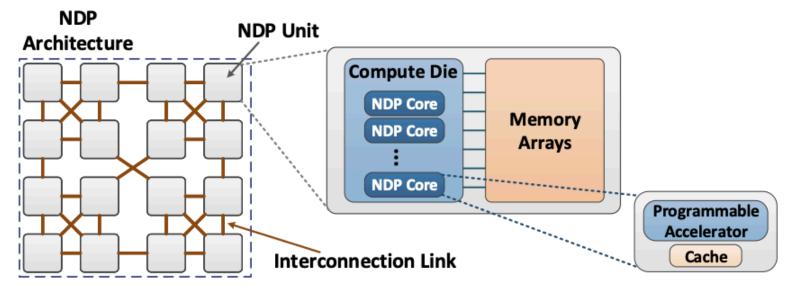

### **Baseline NDP Architecture**

Synchronization challenges in NDP systems:

(1) Lack of hardware cache coherence support

(2) Expensive communication across NDP units

(3) Lack of a shared level of cache memory

Lack of hardware cache coherence support

Expensive communication across NDP units

### Prior schemes are not suitable or efficient for NDP systems

### NDP Synchronization Solution Space

Our Mechanism: SynCron

**Evaluation**

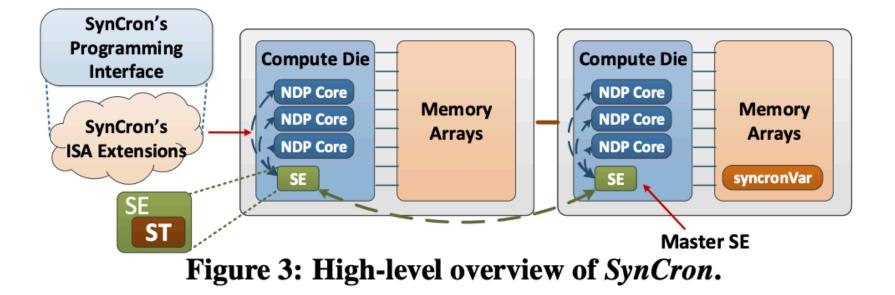

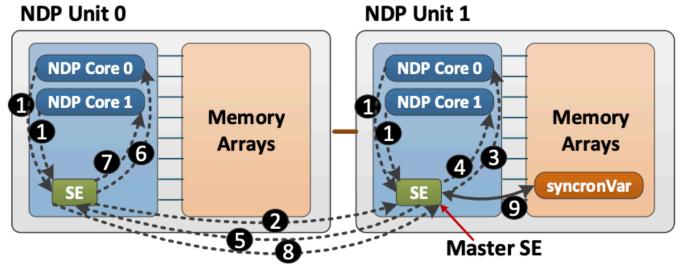

SynCron: Overview

SynCron consists of **four key techniques**:

- 1. Hardware support for synchronization acceleration

- 2. **Direct buffering** of synchronization variables

- 3. Hierarchical message-passing communication

- 4. Integrated hardware-only **overflow management**

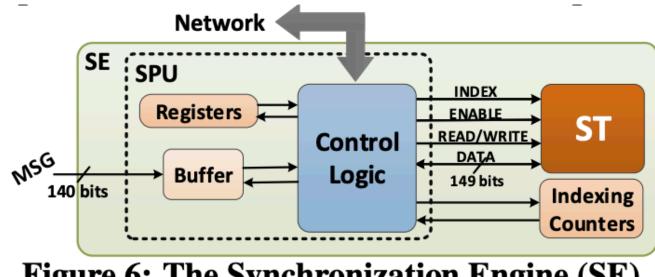

## 1. Hardware Synchronization Support

- ✓ No Complex Cache Coherence Protocols

- ✓ No Expensive Atomic Operations

- ✓ Low Hardware Cost

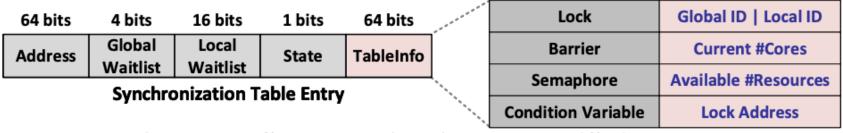

### 2. Direct Buffering of Variables

### 2. Direct Buffering of Variables

✓ No Costly Memory Accesses✓ Low Latency

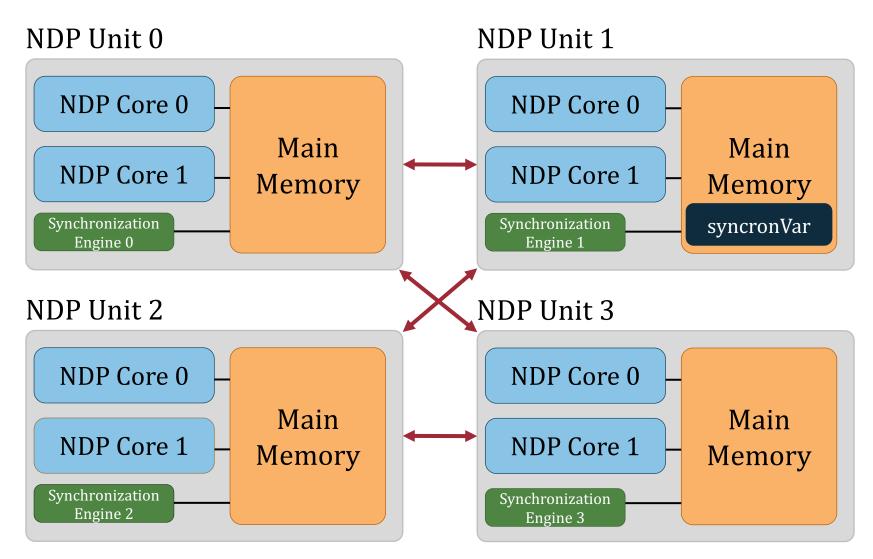

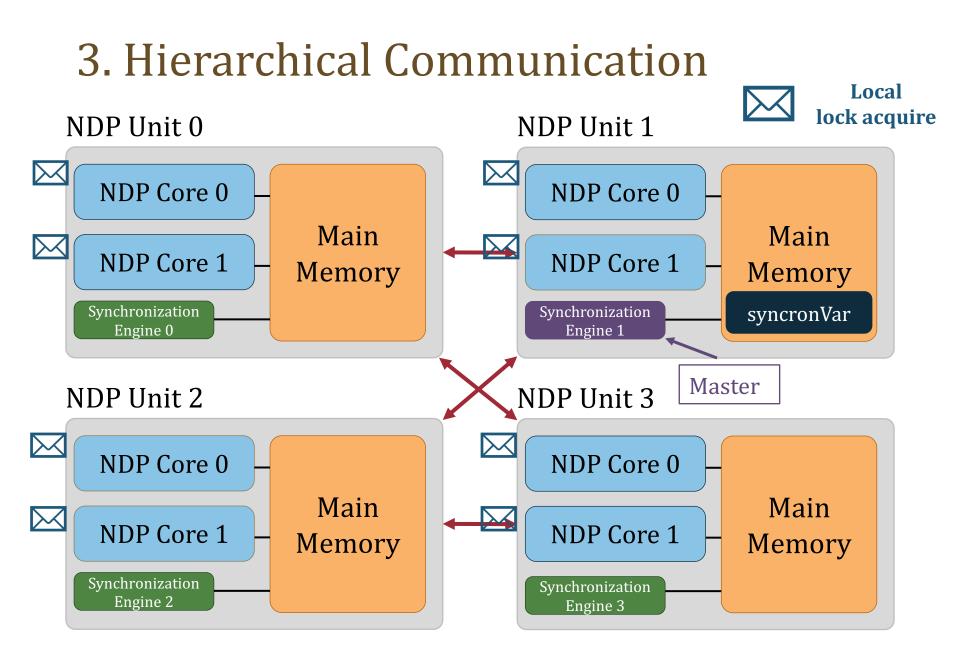

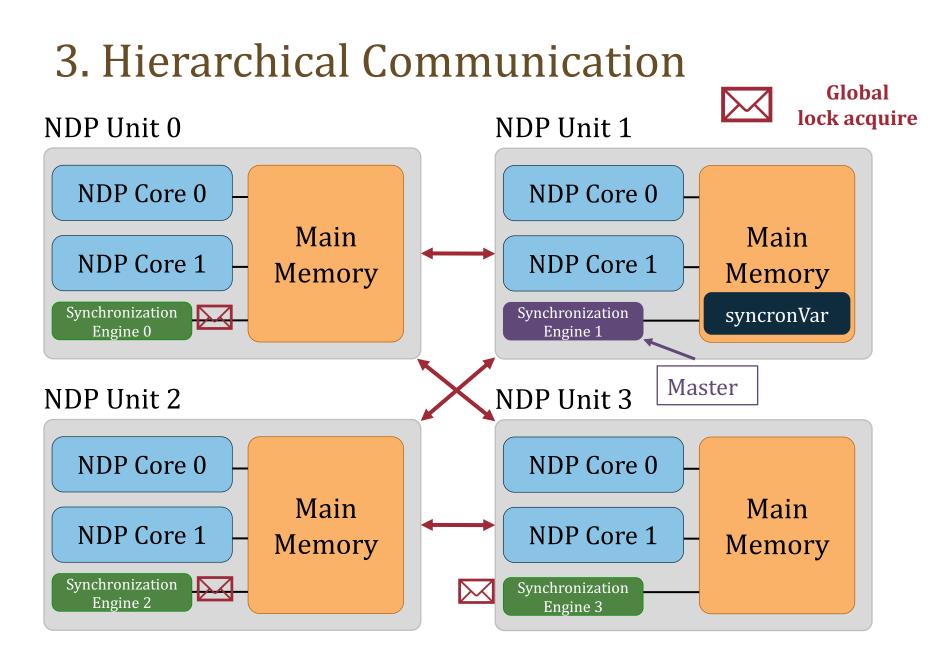

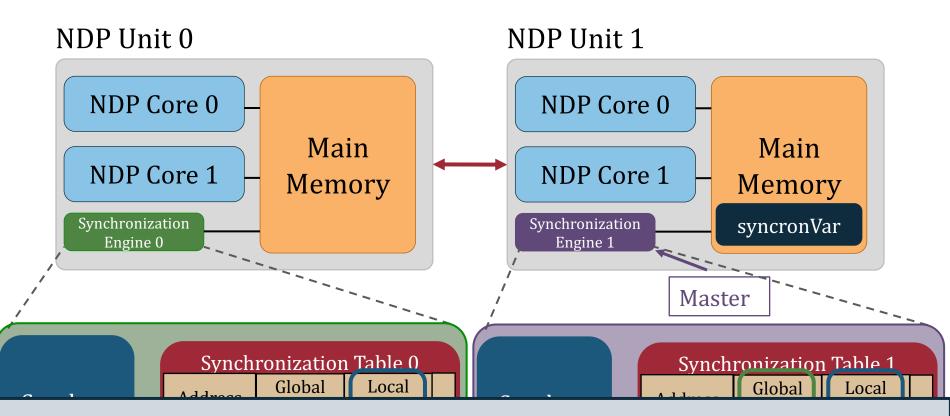

### 3. Hierarchical Communication

### 3. Hierarchical Communication

### ✓ Minimize Expensive Traffic

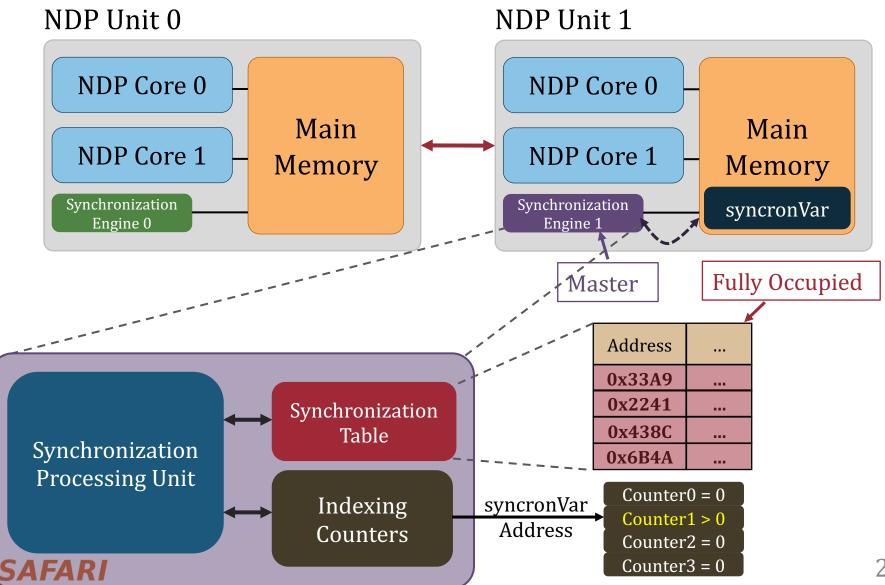

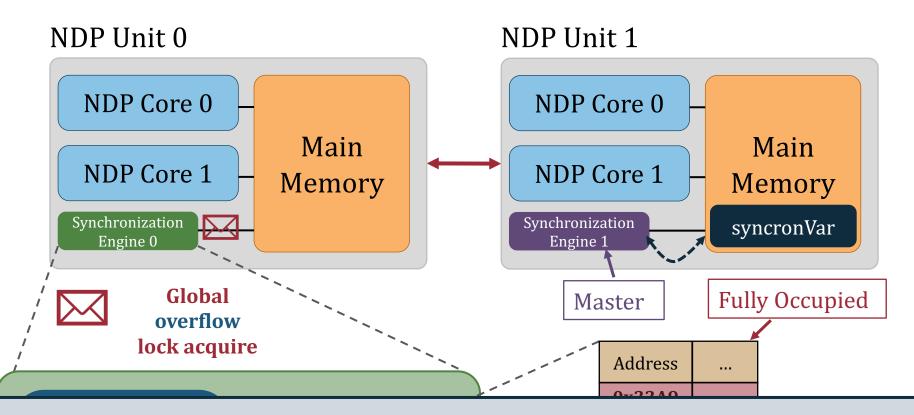

### 4. Integrated Overflow Management

### 4. Integrated Overflow Management

# ✓ Low Performance Degradation✓ High Programming Ease

Counters

### SynCron's Supported Primitives

#### Lock primitive

- lock\_acquire()

- lock\_release ()

#### **Barrier** primitive

- barrier\_wait\_within\_NDP\_unit()

- barrier\_wait\_across\_NDP\_units()

#### Semaphore primitive

- sem\_wait()

- sem\_post()

### **Condition variable** primitive

- cond\_wait()

- cond\_signal()

- cond\_broadcast()

All NDP cores compete for the same lock variable

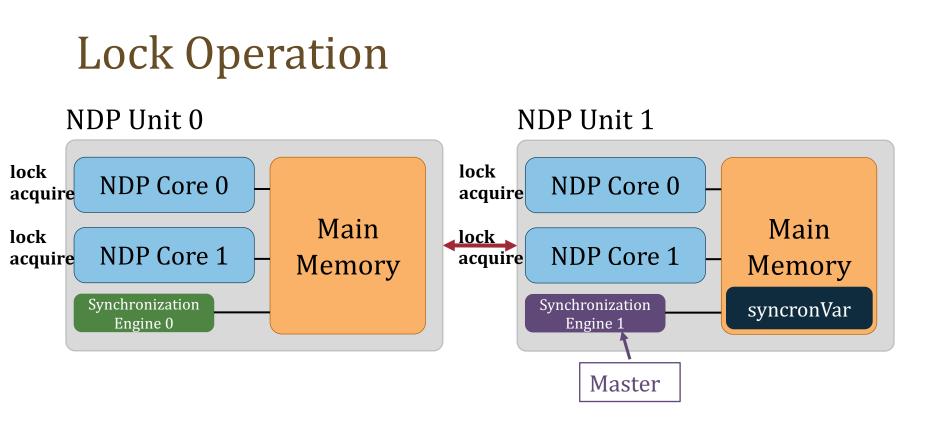

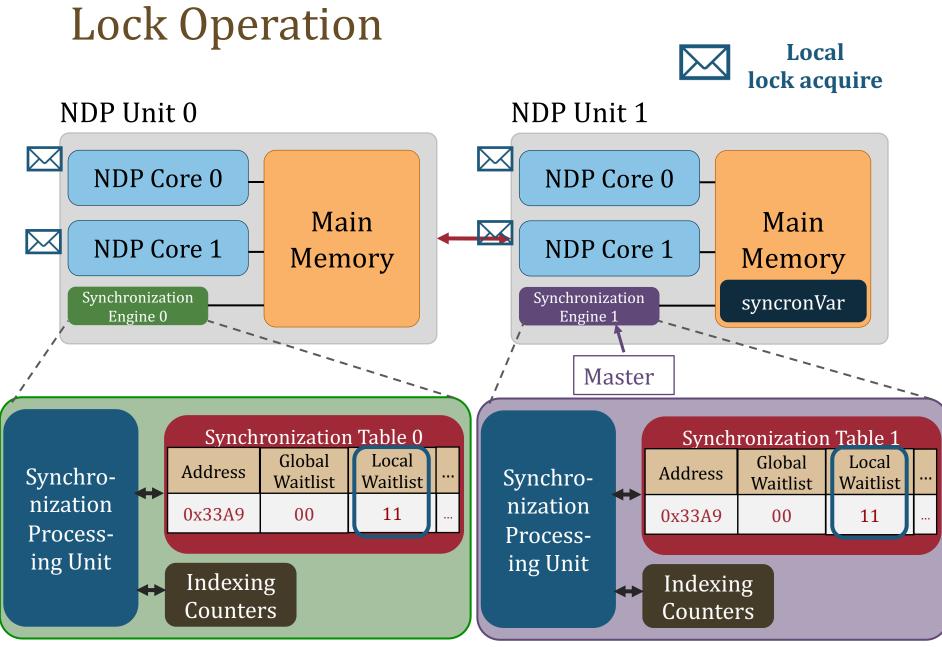

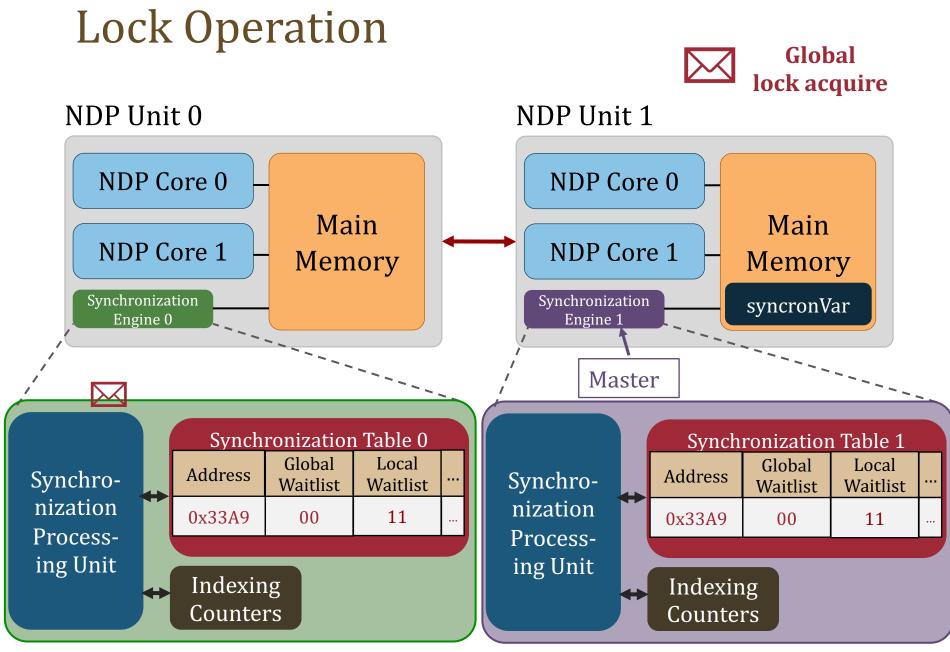

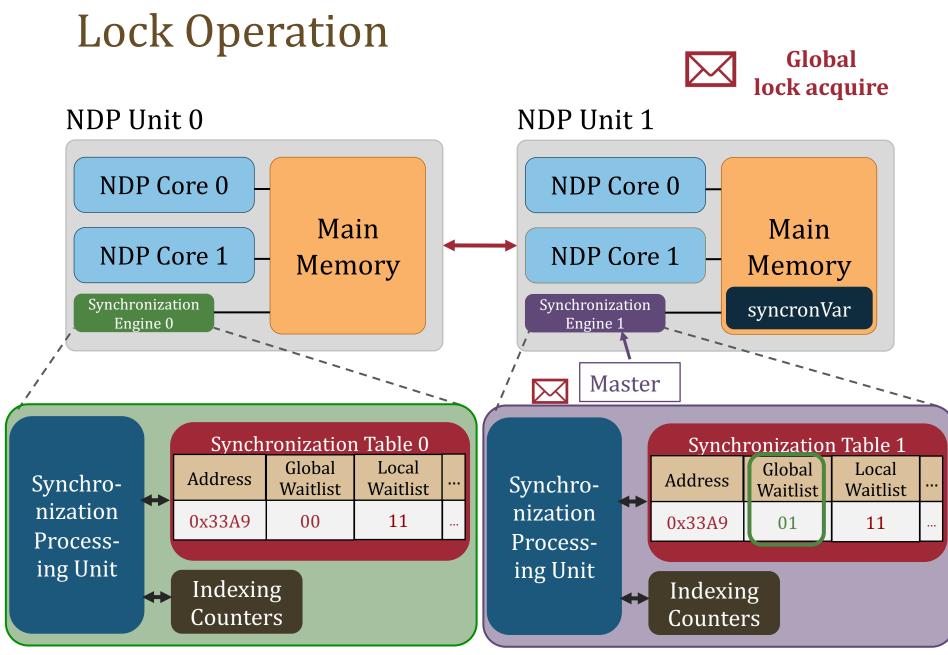

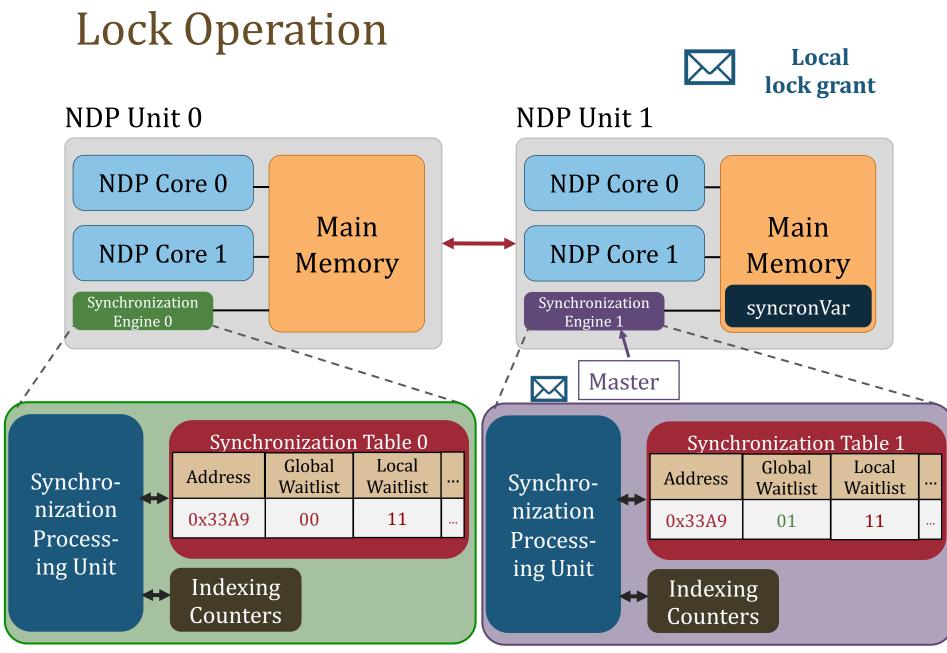

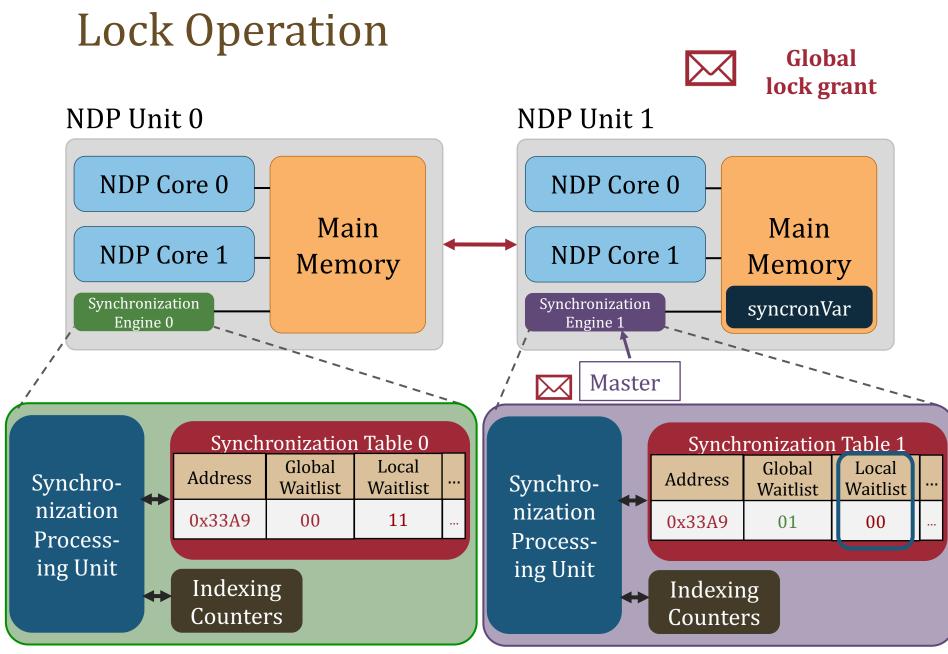

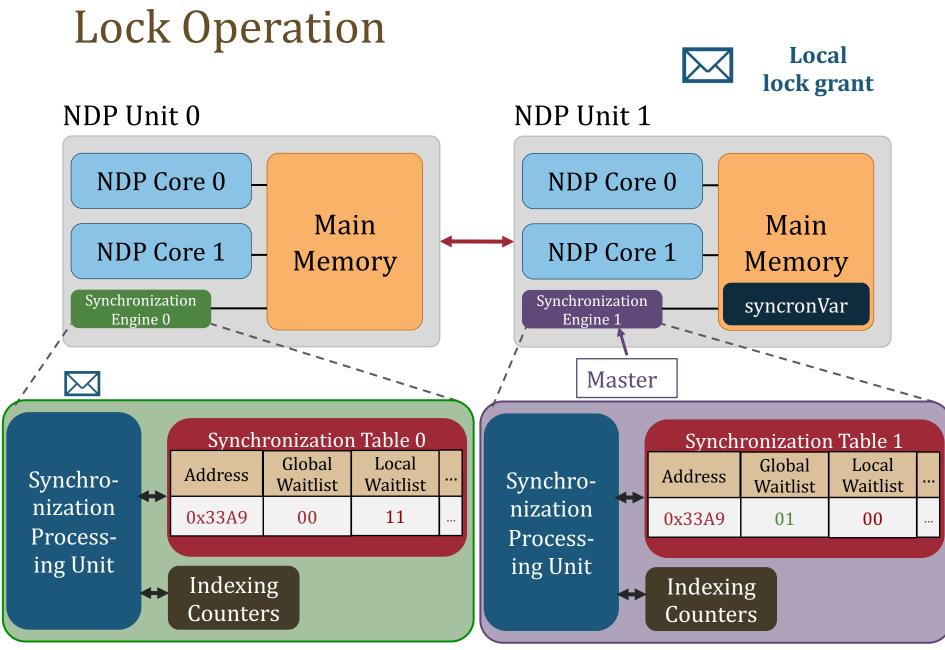

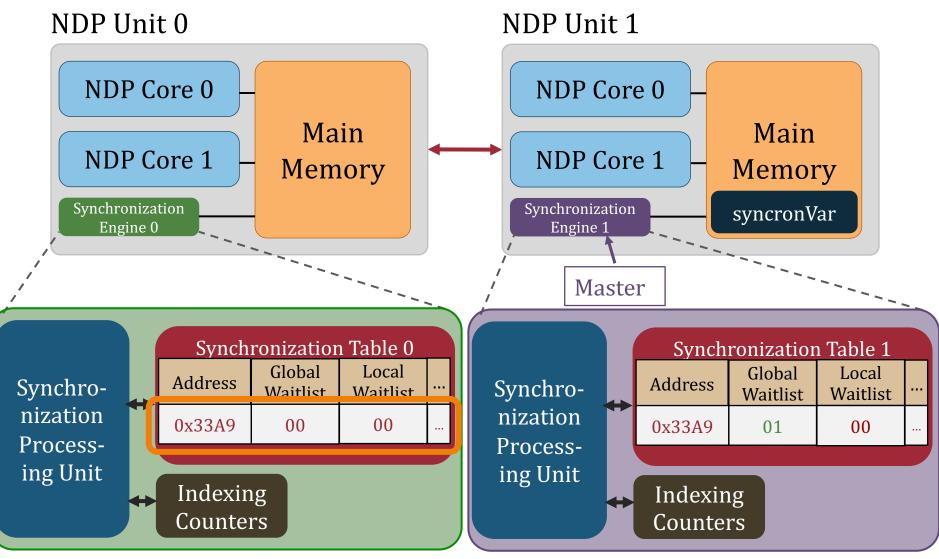

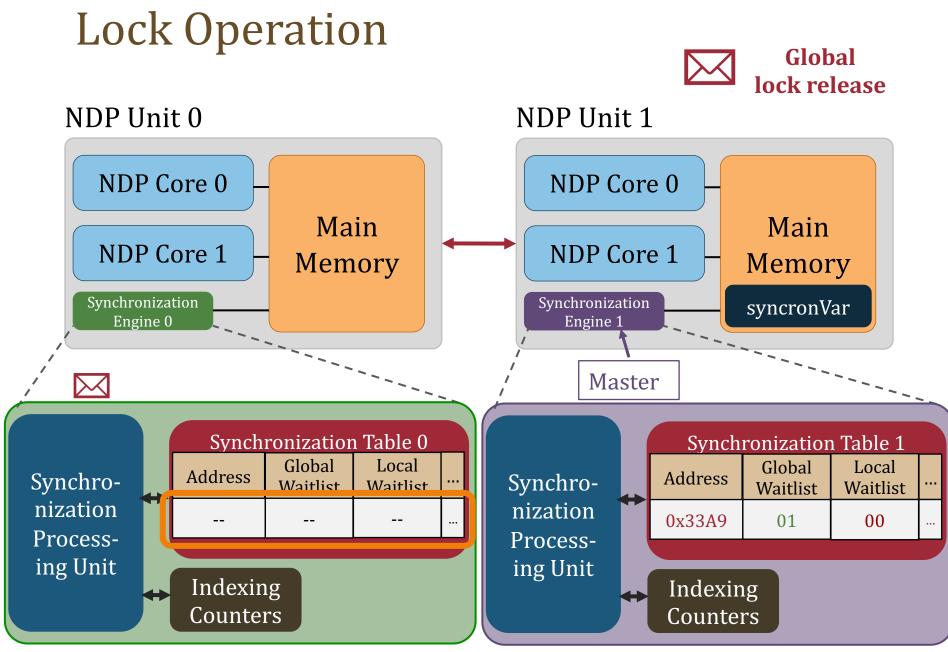

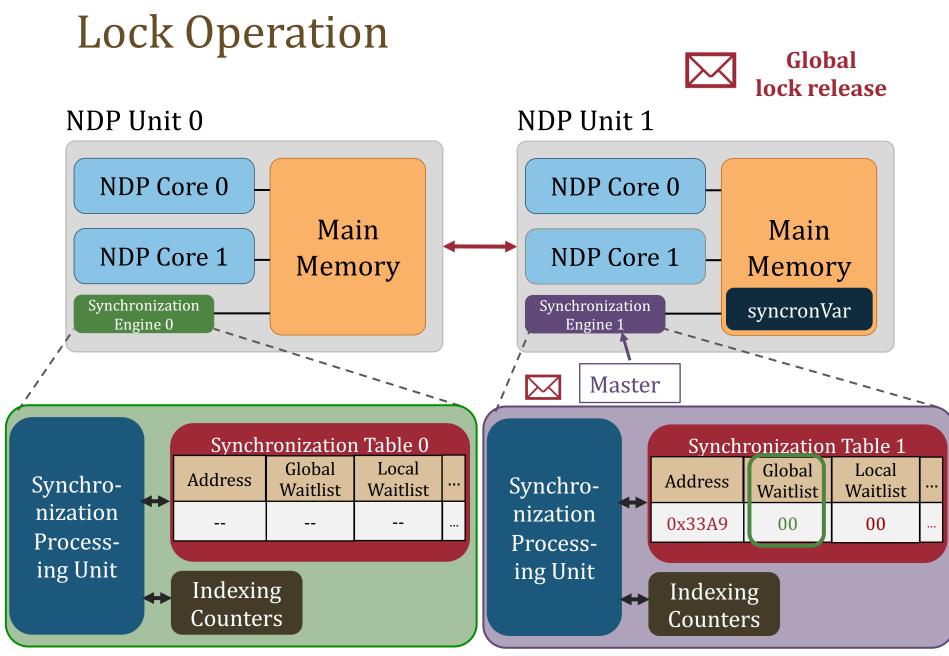

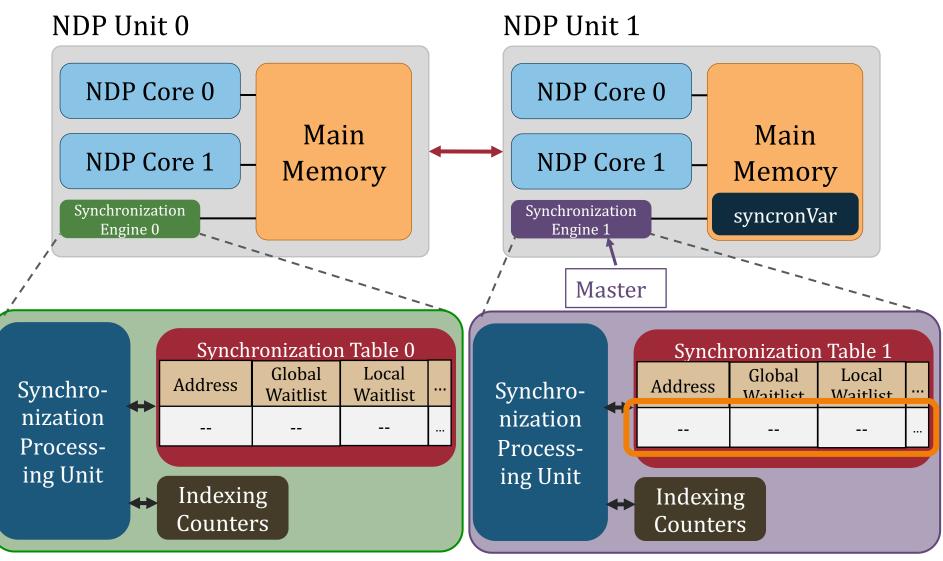

### Lock Operation

#### 35

### Lock Operation

#### More details in the paper

#### NDP Synchronization Solution Space

#### Our Mechanism: SynCron

**Evaluation**

# **Evaluation Methodology**

- Simulators:

- Zsim [Sanchez+, ISCA'13]

- Ramulator [Kim+, CAL'15]

- System Configuration:

- 4x NDP units of 16 in-order cores

- 16KB L1 Data + Instr. Cache

- 4GB HBM memory

- SynCron's Default Parameters:

- Synchronization Processing Unit @1GHz

- 12-cycle worst-case latency for a message to be served [Aladdin]

- 64 entries in Synchronization Table, 1-cycle latency [CACTI]

- 256 entries in indexing counters 2-cycle latency [CACTI]

- Workloads:

- 9x Pointer-chasing Data Structures from ASCYLIB [David+, ASPLOS'15]

- 6x Graph Applications from Crono [Ahmad+, IISWC'15]

- Time Series Analysis from Matrix Profile [Yeh+, ICDM'16]

# **Comparison Points for SynCron**

#### 1. SynCron

#### 2. <u>Central</u> [Ahn+, ISCA'15]:

- Synchronization Server: One NDP core of the NDP system

- Centralized hardware message-passing communication

- **3.** <u>Hier</u> [Gao+, PACT'15 / Tang+, ASPLOS'19]:

- Synchronization Servers: One NDP core per NDP unit

- Hierarchical hardware message-passing communication

- 4. <u>Ideal</u>

- Zero overhead for synchronization

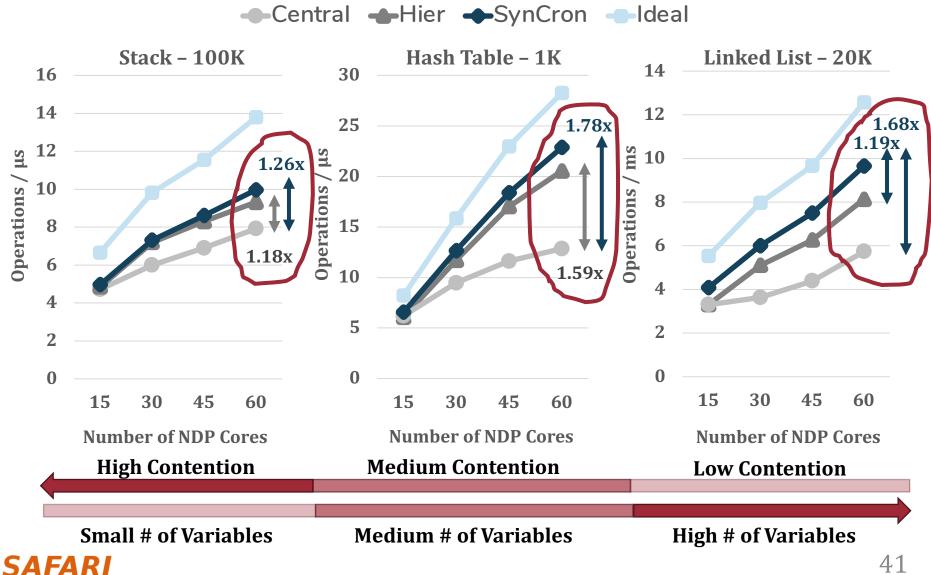

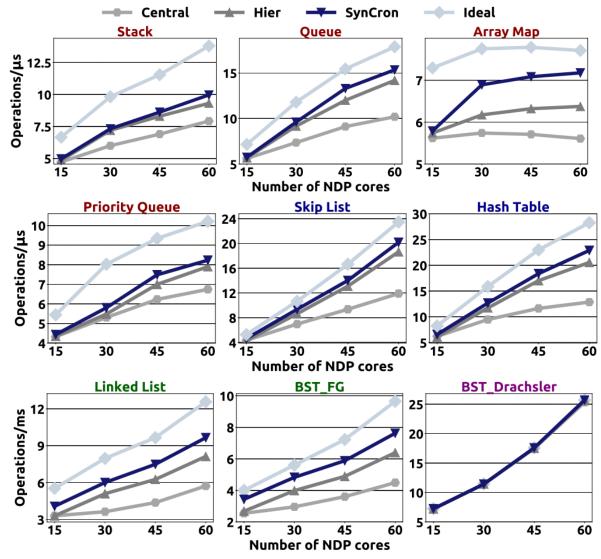

## Throughput of Pointer Chasing

## **Throughput of Pointer Chasing**

#### SynCron achieves the highest throughput under all scenarios

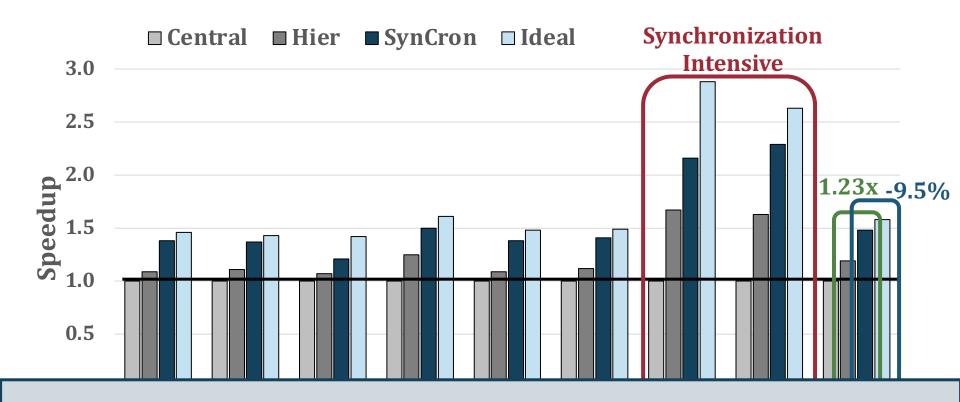

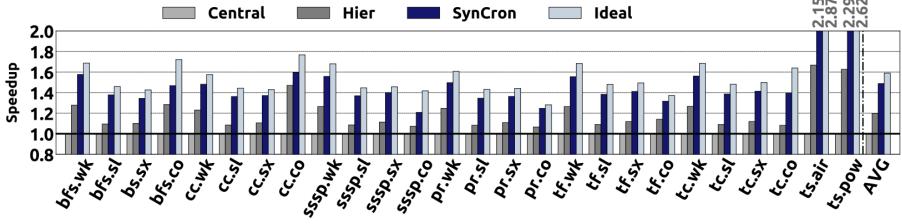

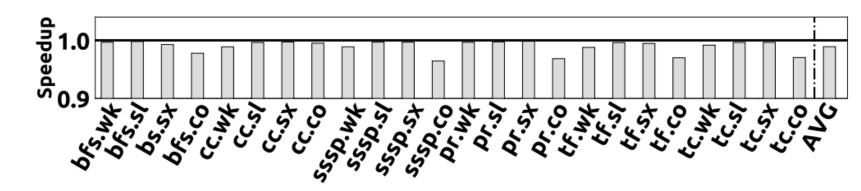

# Speedup in Real Applications

SynCron performs best across all real applications

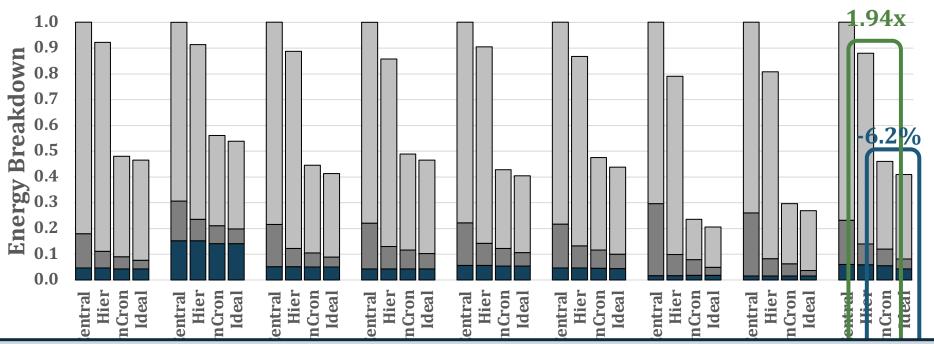

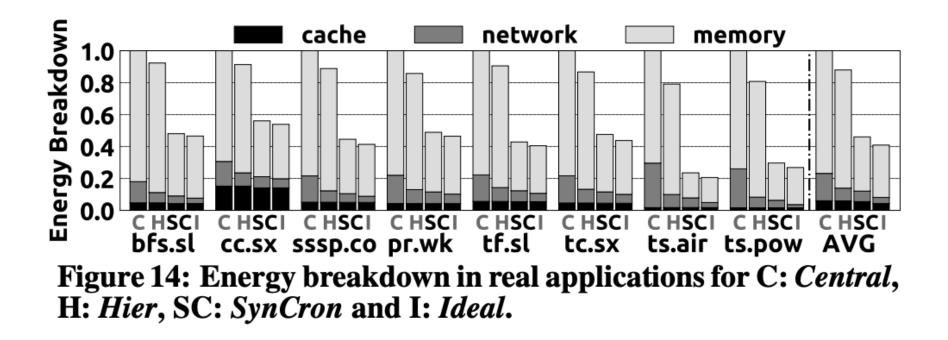

## System Energy in Real Applications

SynCron reduces system energy significantly

## Area and Power Overheads

|           |       | Synchronization Engine | ARM Cortex A7  |

|-----------|-------|------------------------|----------------|

| Technolog | JY    | 40nm                   | 28nm           |

| Area      | 9.78% | Total: 0.0461mm2       | Total: 0.45mm2 |

| Power     | 2.70% | 2.7mW                  | 100mW          |

#### SynCron has low area and power overheads

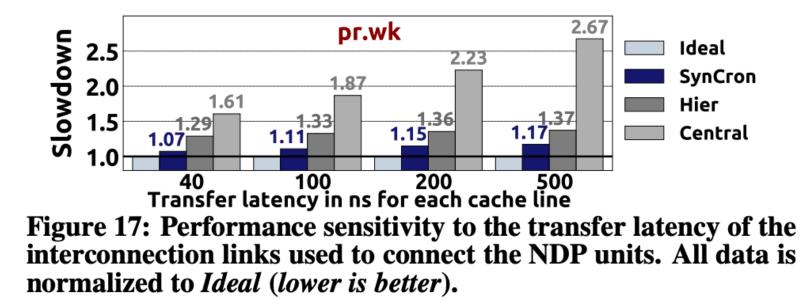

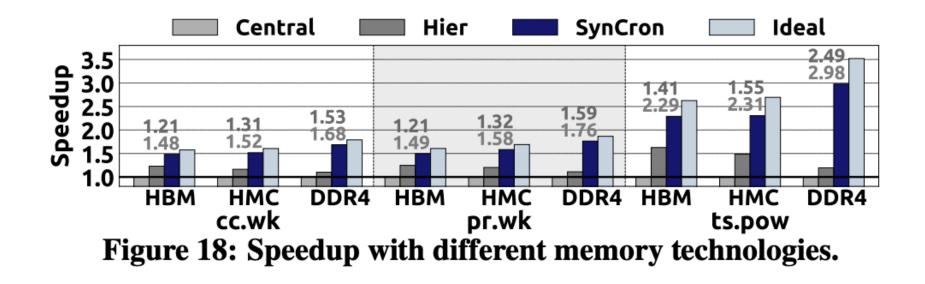

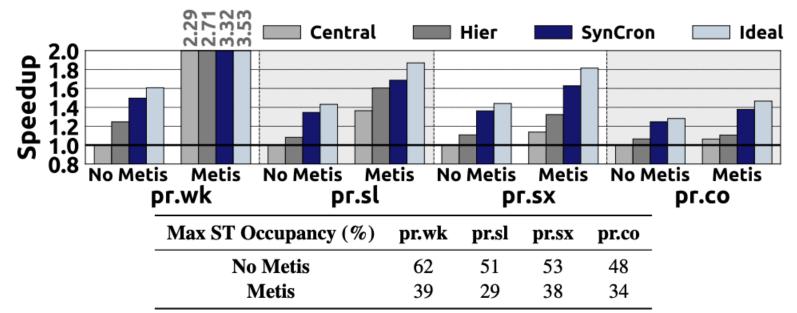

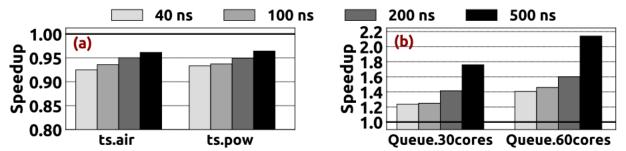

## Sensitivity Studies

- Different memory technologies (HBM, HMC, DDR4)

- Various data placement techniques

- Various transfer latencies on links across NDP units

- Overflow management cost

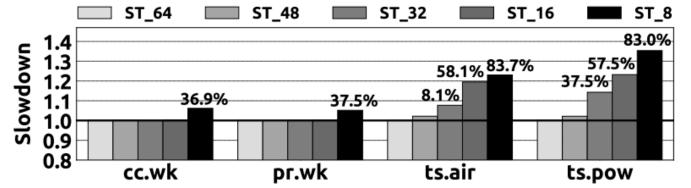

- Various sizes for the Synchronization Table

# SynCron is effective for a wide variety of configurations

## Summary & Conclusion

- Synchronization is a **major system challenge** for NDP systems

- **Prior** schemes are **not suitable** or **efficient** for NDP systems

- **SynCron** is the **first end-to-end** synchronization solution for NDP architectures

- Syncron consists of **four** key techniques:

- i. Hardware support for synchronization acceleration

- ii. **Direct buffering** of synchronization variables

- iii. Hierarchical message-passing communication

- iv. Integrated hardware-only **overflow management**

- SynCron's benefits: **90.5%** and **93.8%** of performance and energy of an **Ideal** zero-overhead scheme

- SynCron is **highly-efficient**, **low-cost**, **easy-to-use**, and **general** to support many synchronization primitives

# SynCron Efficient Synchronization Support for Near-Data-Processing Architectures

#### Christina Giannoula christina.giann@gmail.com

Nandita Vijaykumar, Nikela Papadopoulou, Vasileios Karakostas Ivan Fernandez, Juan Gómez Luna, Lois Orosa Nectarios Koziris, Georgios Goumas, Onur Mutlu

SAFARI ETHzürich

UNIVERSIDAD DE MÁI AGA

### **Backup Slides**

## **Baseline NDP Architecture**

Figure 1: High-level organization of an NDP architecture.

## Low Scalability of Coherence-based Synchronization in Real System

| Million Operations             | 1 thread      | 14 threads single-socket | 2 threads   | 2 threads        |

|--------------------------------|---------------|--------------------------|-------------|------------------|

| per Second                     | single-socket |                          | same-socket | different-socket |

| TTAS lock [122]                | 8.92          | 2.28                     | 9.91        | 4.32             |

| Hierarchical Ticket lock [103] | 8.06          | 2.91                     | 9.01        | 6.79             |

Table 1: Throughput of two coherence-based lock algorithms on an Intel Xeon Gold server using the libslock library [30].

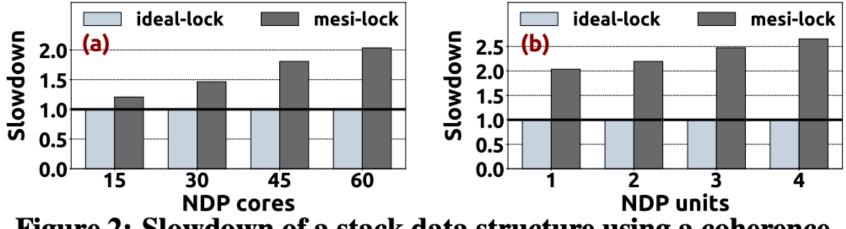

## Low Scalability of Coherence-based Synchronization in NDP Simulated System

Figure 2: Slowdown of a stack data structure using a coherencebased lock over using an *ideal* zero-cost lock, when varying (a) the NDP cores within a single NDP unit and (b) the number of NDP units while keeping core count constant at 60.

## SynCron's Overview

## Lock Operation using SynCron

Figure 4: An example execution scenario for a lock requested by *all* NDP cores.

## SynCron's API

#### SynCron Programming Interface

syncronVar \*create\_syncvar (); void destroy\_syncvar (syncronVar \*svar); void lock\_acquire (syncronVar \*lock); void lock\_release (syncronVar \*lock); void barrier\_wait\_within\_unit (syncronVar \*bar, int initialCores); void barrier\_wait\_across\_units (syncronVar \*bar, int initialCores); void sem\_wait (syncronVar \*sem, int initialResources); void sem\_post (syncronVar \*sem); void cond\_wait (syncronVar \*cond, syncronVar \*lock); void cond\_signal (syncronVar \*cond); void cond\_broadcast (syncronVar \*cond);

Table 2: SynCron's Programming Interface (i.e., API).

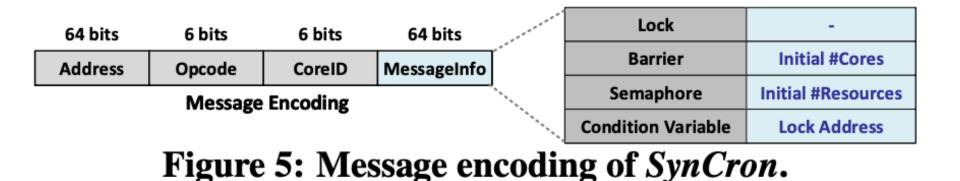

## Message Encoding of SynCron

### Message Opcodes for All Primitives

| Primitives             | SynCron Message Opcodes                                                                                                                                                                                                                      |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Locks                  | lock_acquire_global, lock_acquire_local, lock_release_global<br>lock_release_local, lock_grant_global, lock_grant_local<br>lock_acquire_overflow, lock_release_overflow, lock_grant_overflow                                                 |

| Barriers               | barrier_wait_global, barrier_wait_local_within_unit<br>barrier_wait_local_across_units, barrier_depart_global, barrier_depart_local<br>barrier_wait_overflow, barrier_departure_overflow                                                     |

| Semaphores             | sem_wait_global, sem_wait_local, sem_grant_global<br>sem_grant_local, sem_post_global, sem_post_local<br>sem_wait_overflow, sem_grant_overflow, sem_post_overflow                                                                            |

| Condition<br>Variables | cond_wait_global, cond_wait_local, cond_signal_global<br>cond_signal_local, cond_broad_global, cond_broad_local<br>cond_grant_global, cond_grant_local, cond_wait_overflow<br>cond_signal_overflow, cond_broad_overflow, cond_grant_overflow |

| Other                  | decrease_indexing_counter                                                                                                                                                                                                                    |

#### Table 3: Message opcodes of SynCron.

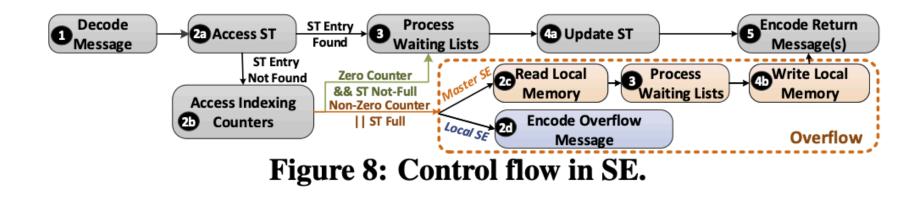

### The Synchronization Engine

**Figure 6: The Synchronization Engine (SE).**

## Synchronization Table Entry

Figure 7: Synchronization Table (ST) entry.

## Control Flow of Message in Synchronization Engine

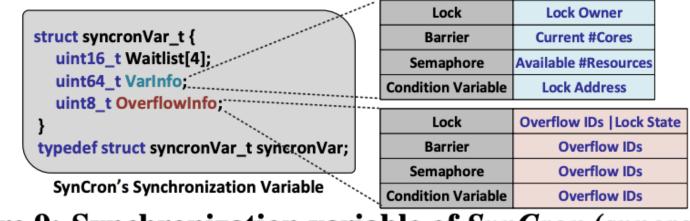

## Synchronization Variable of SynCron

Figure 9: Synchronization variable of SynCron (syncronVar).

#### Qualitative Comparison with Closely Related Works

|                      | SSB [157]  | LCU [146]  | MiSAR [97] | SynCron     |

|----------------------|------------|------------|------------|-------------|

| Supported Primitives | 1          | 1          | 3          | 4           |

| ISA Extensions       | 2          | 2          | 7          | 2           |

| Spin-Wait Approach   | yes        | yes        | no         | no          |

| Direct Notification  | no         | yes        | yes        | yes         |

| Target System        | uniform    | uniform    | uniform    | non-uniform |

| Overflow             | partially  | partially  | handled by | fully       |

| Management           | integrated | integrated | programmer | integrated  |

Table 4: Comparison of SynCron with prior mechanisms.

## Simulated System

| NDP Cores                                 | 16 in-order cores @2.5 GHz per NDP unit                                                                                                                                                     |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L1 Data + Inst. Cache                     | private, 16KB, 2-way, 4-cycle; 64 B line; 23/47 pJ per hit/miss [109]                                                                                                                       |

| NDP Unit<br>Local Network                 | buffered crossbar network with packet flow control; 1-cycle arbiter;<br>1-cycle per hop [6]; 0.4 pJ/bit per hop [149];<br>M/D/1 model [18] for queueing latency;                            |

| DRAM HBM                                  | 4 stacks; 4GB HBM 1.0 [92, 93]; 500MHz with 8 channels;<br>nRCDR/nRCDW/nRAS/nWR 7/6/17/8 ns [47, 85]; 7 pJ/bit [151]                                                                        |

| DRAM HMC                                  | 4 stacks; 4GB HMC 2.1; 1250MHz; 32 vaults per stack; nRCD/nRAS/nWR 17/34/19 ns [47, 85]                                                                                                     |

| DRAM DDR4                                 | 4 DIMMs; 4GB each DIMM DDR4 2400MHz;<br>nRCD/nRAS/nWR 16/39/18 ns [47, 85]                                                                                                                  |

| Interconnection Links<br>Across NDP Units | 12.8GB/s per direction; 40 ns per cache line;<br>20-cycle; 4 pJ/bit                                                                                                                         |

| Synchronization<br>Engine                 | SPU @1GHz clock frequency [129]; 8× 64-bit registers;<br>buffer: 280B; ST: 1192B, 64 entries, 1-cycle [109];<br>indexing counters: 2304B, 256 entries (8 LSB of the address), 2-cycle [109] |

|                                           |                                                                                                                                                                                             |

#### Table 5: Configuration of our simulated system.

### **Evaluated Workloads**

| Data Structure                                        | Configuration        |  |

|-------------------------------------------------------|----------------------|--|

| Stack [31]                                            | 100K - 100% push     |  |

| Queue [31, 104]                                       | 100K - 100% pop      |  |

| Array Map [31,56]                                     | 10 - 100% lookup     |  |

| Priority Queue [11, 31, 118]                          | 20K - 100% deleteMin |  |

| Skip List [31, 118]                                   | 5K - 100% deletion   |  |

| Hash Table [31,63]                                    | 1K - 100% lookup     |  |

| Linked List [31,63]                                   | 20K - 100% lookup    |  |

| Binary Search Tree Fine-Grained (BST_FG) [130]        | 20K - 100% lookup    |  |

| Binary Search Tree Drachsler (BST_Drachsler) [31, 37] | 10K - 100% deletion  |  |

| Real Application                        | Locks        | Barriers     | <b>Real Application</b> | Input Data Set                    |

|-----------------------------------------|--------------|--------------|-------------------------|-----------------------------------|

| Breadth First Search (bfs) [7]          | $\checkmark$ | $\checkmark$ |                         | wikipedia                         |

| Connected Components (cc) [7]           | $\checkmark$ | $\checkmark$ |                         | -20051105 ( <b>wk</b> )           |

| Single Source Shortest Paths (sssp) [7] | $\checkmark$ | $\checkmark$ | bfs, cc, sssp,          | soc-LiveJournal1 (sl)             |

| Pagerank (pr) [7]                       | $\checkmark$ | $\checkmark$ | pr, tf, tc              | sx-stackoverflow (sx)             |

| Teenage Followers (tf) [65]             | $\checkmark$ | -            |                         | com-Orkut (co)                    |

| Triangle Counting (tc) [7]              | $\checkmark$ | $\checkmark$ |                         | air quality ( <b>air</b> )        |

| Time Series Analysis (ts) [152]         | $\checkmark$ | $\checkmark$ | ts                      | energy consumption ( <b>pow</b> ) |

Table 6: Summary of all workloads used in our evaluation.

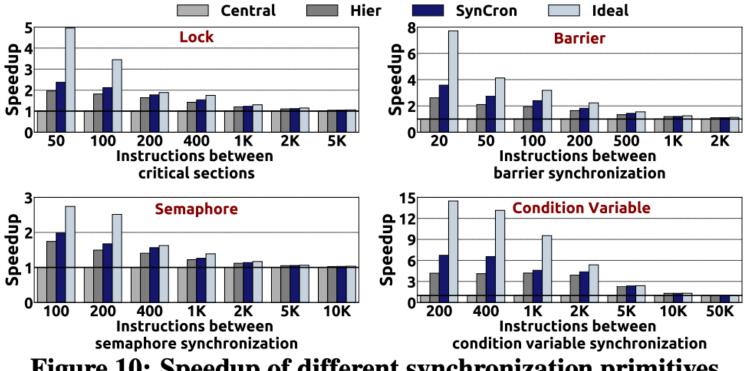

## Speedup in Simple Microbenchmarks

**Figure 10: Speedup of different synchronization primitives.**

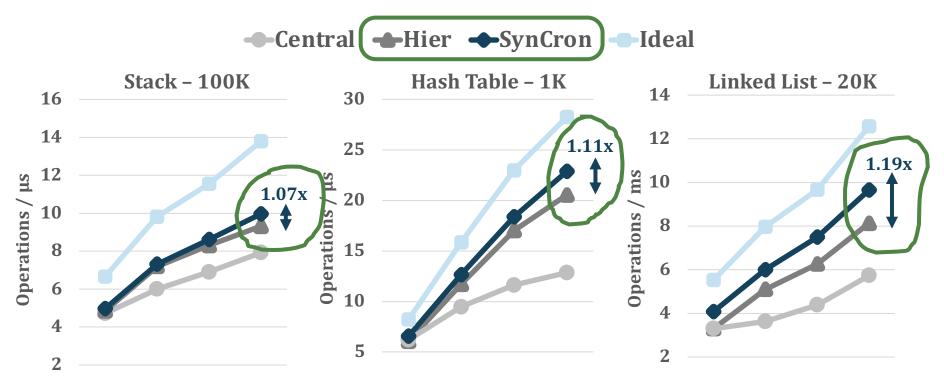

## **Throughput of Pointer Chasing**

SAFARI

Figure 11: Throughput of pointer chasing using data structures.

## Speedup in Real Applications

Figure 12: Speedup in real applications normalized to Central.

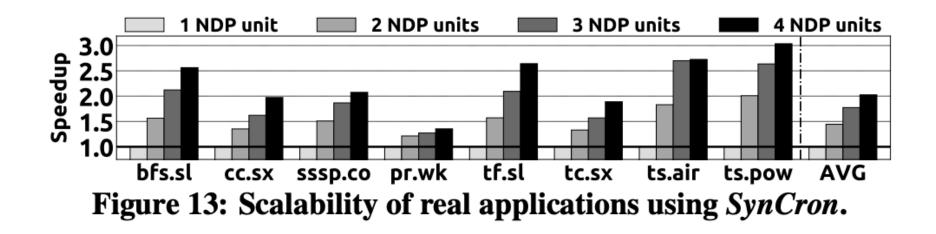

# Scalability in Real Applications using SynCron

## System Energy in Real Applications

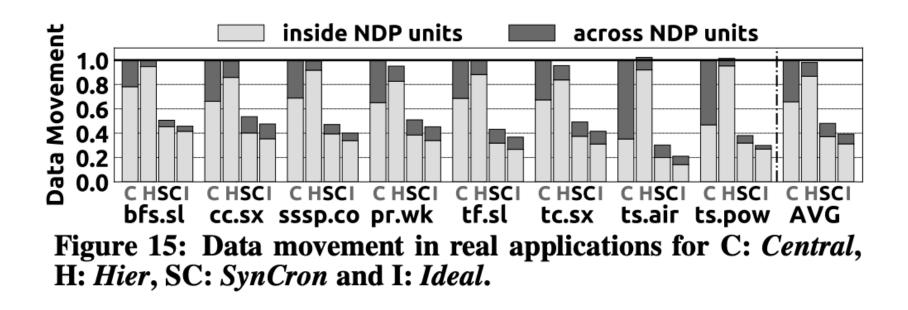

## Data Movement in Real Applications

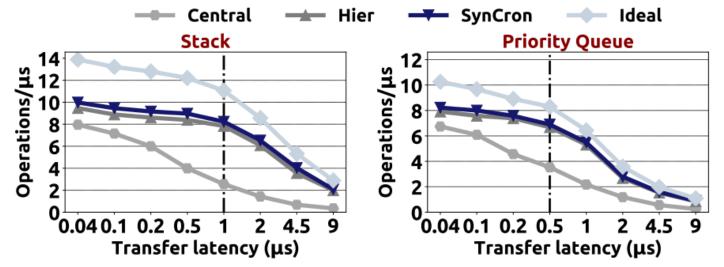

### Various Transfer Latencies on Links Across NDP Units – High Contention

Figure 16: Performance sensitivity to the transfer latency of the interconnection links used to connect the NDP units.

#### Various Transfer Latencies on Links Across NDP Units – Low Contention

## Speedup using Different Memory Technologies

## Speedup in Real Applications using two Different Data Placement Techniques

Figure 19: Performance sensitivity to a better graph partitioning and maximum ST occupancy of *SynCron*.

Speedup of Syncron over its Flat Variant in a Low-contention and Synchronization Non-intensive Scenario

Figure 20: Speedup of *SynCron* normalized to *flat* with 40 ns link latency between NDP units, under a low-contention and synchronization non-intensive scenario.

Speedup of Syncron over its Flat Variant in a Low-contention and Synchronization Intensive Scenario and in a High-contention Scenario

Figure 21: Speedup of *SynCron* normalized to *flat*, as we vary the transfer latency of the interconnection links used to connect NDP units, under (a) a low-contention and synchronizationintensive scenario using 4 NDP units, and (b) a high-contention scenario using 2 and 4 NDP units.

# Synchronization Table Occupancy in Real Applications

| ST Occupancy | Max (%) | Avg (%) | ST Occupancy   | Max (%) | Avg (%) |

|--------------|---------|---------|----------------|---------|---------|

| bfs.wk       | 51      | 1.33    | pr.sl          | 51      | 2.27    |

| bfs.sl       | 59      | 1.49    | pr.sx          | 53      | 2.46    |

| bfs.sx       | 51      | 3.24    | pr.co          | 48      | 4.72    |

| bfs.co       | 55      | 6.09    | <b>.</b> tf.wk | 62      | 1.44    |

| cc.wk        | 63      | 1.27    | tf.sl          | 53      | 2.21    |

| cc.sl        | 61      | 2.16    | tf.sx          | 50      | 2.99    |

| cc.sx        | 48      | 2.43    | tf.co          | 48      | 4.61    |

| cc.co        | 46      | 4.53    | tc.wk          | 62      | 1.26    |

| sssp.wk      | 62      | 1.18    | tc.sl          | 48      | 2.08    |

| sssp.sl      | 54      | 2.08    | tc.sx          | 50      | 2.77    |

| sssp.sx      | 50      | 2.20    | tc.co          | 51      | 4.52    |

| sssp.co      | 48      | 5.23    | ts.air         | 84      | 44.20   |

| pr.wk        | 62      | 4.27    | ts.pow         | 89      | 43.51   |

Table 7: ST occupancy in real applications.

Slowdown in Real Applications when Varying the Synchronization Table Size

Figure 22: Slowdown with varying ST size (normalized to 64entry ST). Numbers on top of bars show the percentage of overflowed requests.

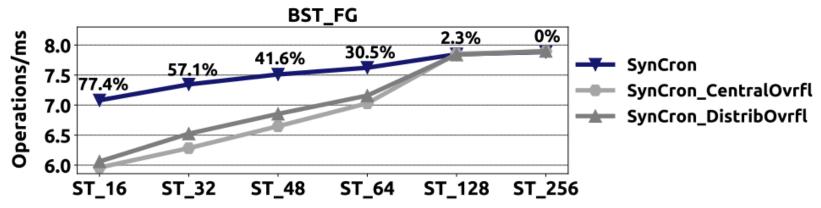

#### Overflow Management Cost of Different Overflow Schemes

Figure 23: Throughput achieved by BST\_FG using different overflow schemes and varying the ST size. The reported numbers show to the percentage of overflowed requests.

# Area and Power Overheads of the Synchronization Engine

|            | SE (Synchronization Engine)                                                                        | ARM Cortex A7 [14]                |

|------------|----------------------------------------------------------------------------------------------------|-----------------------------------|

| Technology | 40nm                                                                                               | 28nm                              |

| Area       | SPU: 0.0141mm <sup>2</sup> , ST: 0.0112mm <sup>2</sup><br>Indexing Counters: 0.0208mm <sup>2</sup> | 32KB L1 Cache                     |

|            | <b>Total:</b> 0.0461mm <sup>2</sup>                                                                | <b>Total:</b> 0.45mm <sup>2</sup> |

| Power      | 2.7 mW                                                                                             | 100mW                             |

Table 8: Comparison of SE with a simple general-purpose inorder core, ARM Cortex A7.