Program Interference in MLC NAND Flash Memory: Characterization, Modeling, and Mitigation

Yu Cai<sup>1</sup> Onur Mutlu<sup>1</sup> Erich F. Haratsch<sup>2</sup> Ken Mai<sup>1</sup>

<sup>1</sup> Carnegie Mellon University <sup>2</sup> LSI Corporation

**SAFARI**

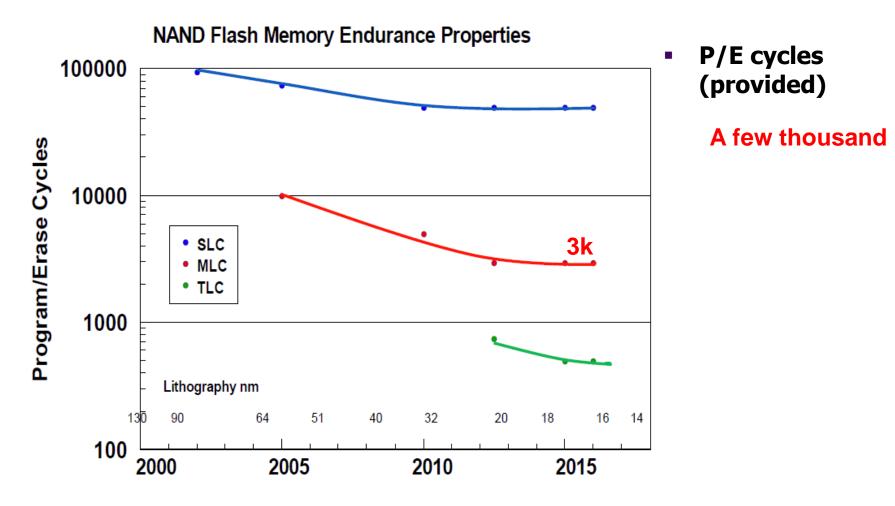

E. Grochowski et al., "Future technology challenges for NAND flash and HDD products", Flash Memory Summit 2012

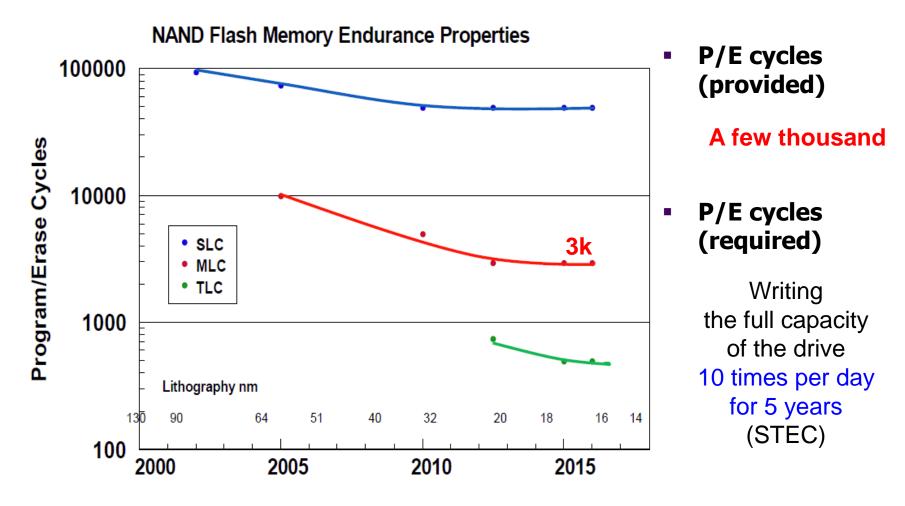

E. Grochowski et al., "Future technology challenges for NAND flash and HDD products", Flash Memory Summit 2012

3

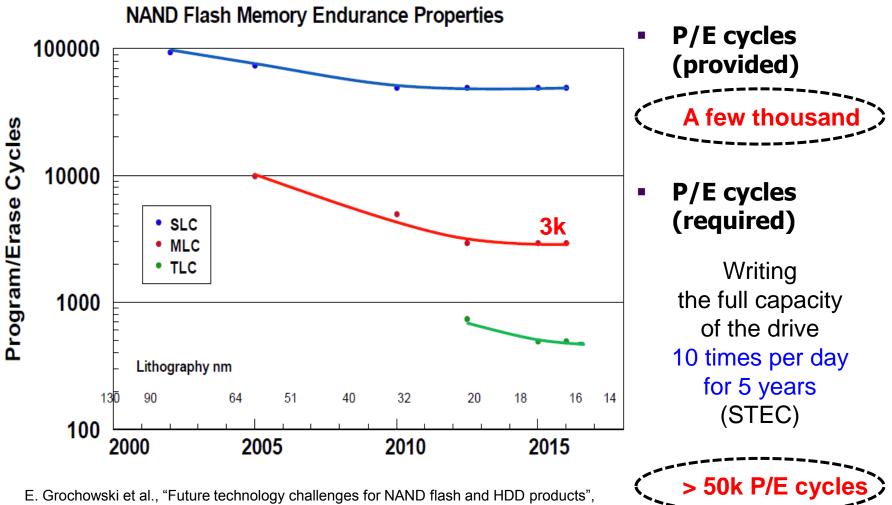

> 50k P/E cycles

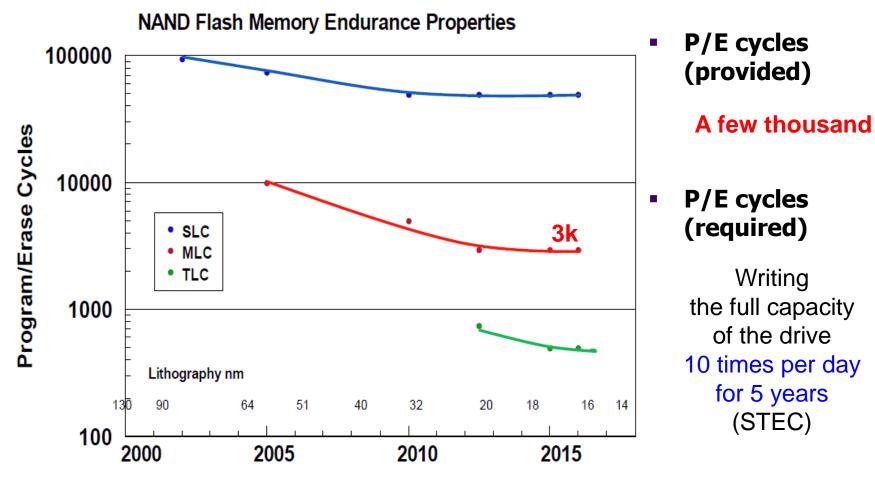

E. Grochowski et al., "Future technology challenges for NAND flash and HDD products", Flash Memory Summit 2012

**Carnegie Mellon**

4

Flash Memory Summit 2012

5

**Carnegie Mellon**

6

Our Goals:

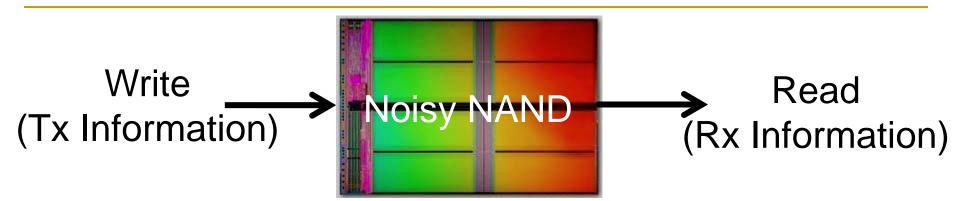

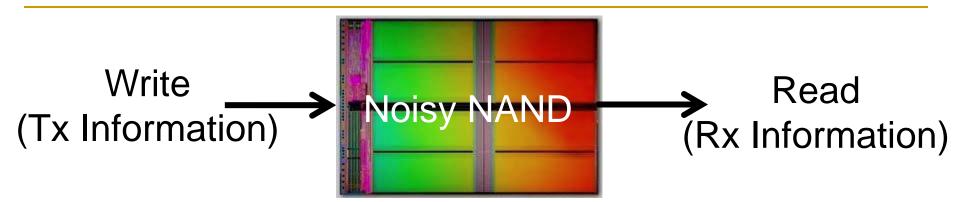

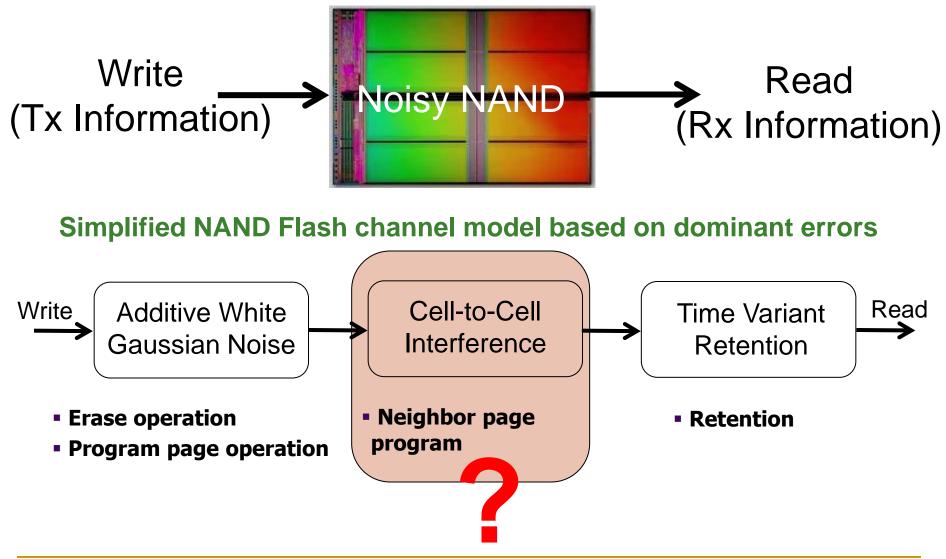

Our Goals: Model NAND Flash as a digital communication channel

Our Goals: Model NAND Flash as a digital communication channel Design efficient reliability mechanisms based on the model

9

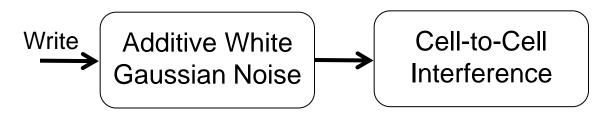

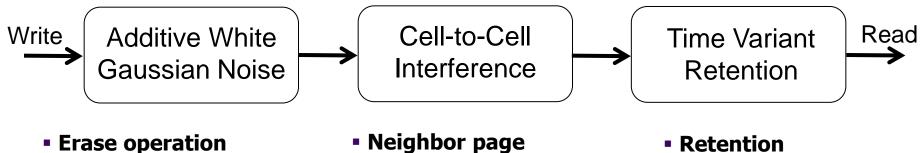

- Erase operation

- Program page operation

- Erase operation

- Program page operation

- Neighbor page program

- Program page operation

- program

Carnegie Mellon<sup>16</sup>

Carnegie Mellon<sup>17</sup>

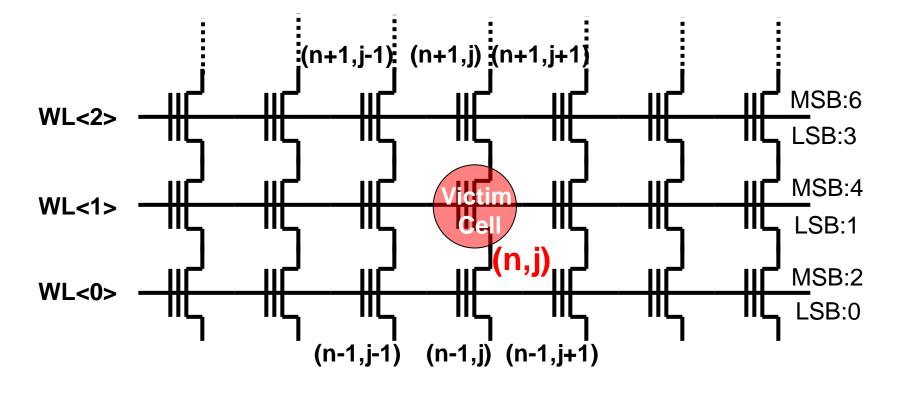

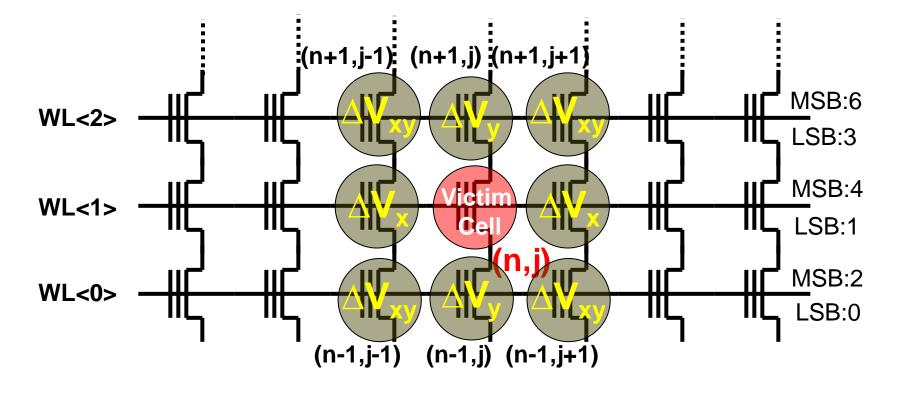

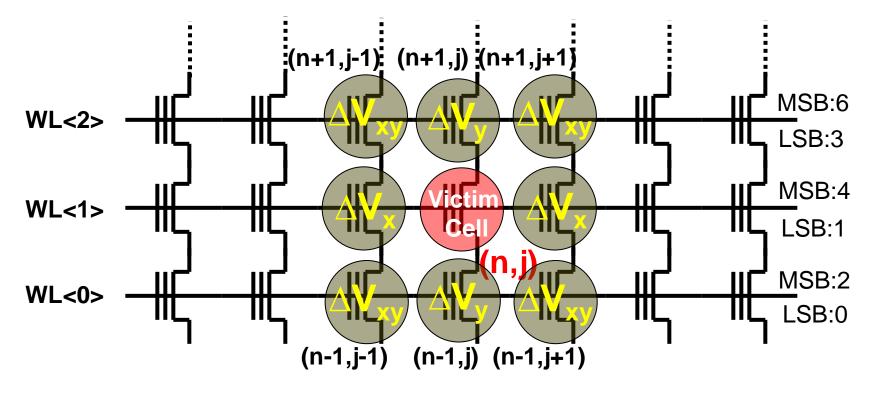

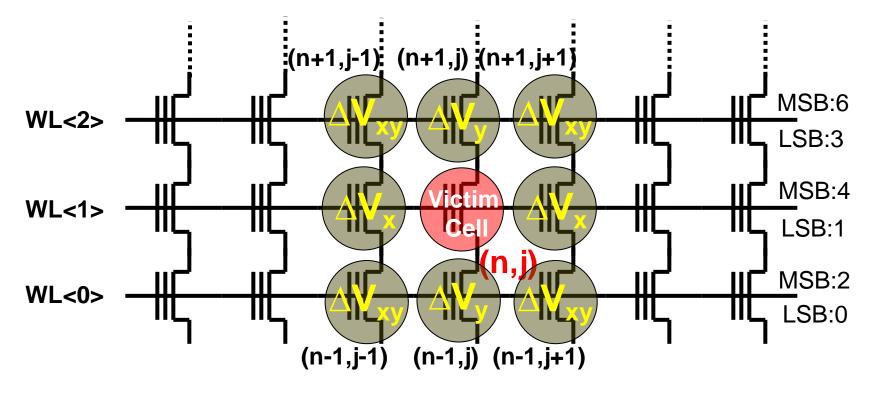

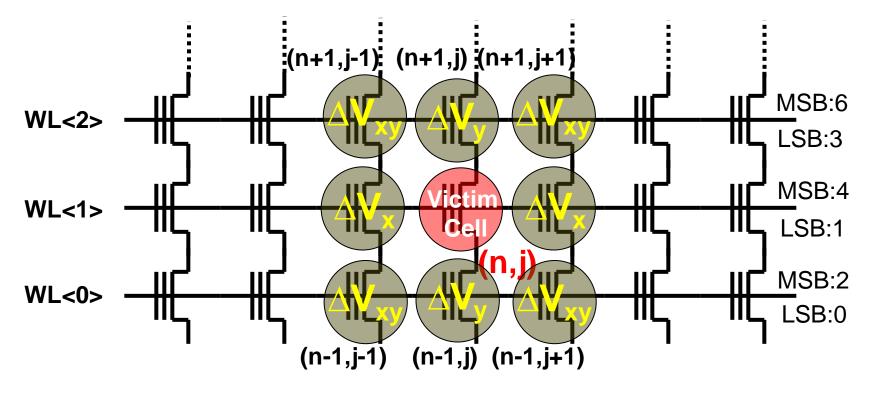

What affects cell-to-cell program interference in Flash chips?

What affects cell-to-cell program interference in Flash chips? How to accurately model cell-to-cell program interference?

What affects cell-to-cell program interference in Flash chips? How to accurately model cell-to-cell program interference? How to improve flash reliability using the model?

Methodology: Extensive experimentation with real 2Y-nm MLC NAND Flash chips

- Methodology: Extensive experimentation with real 2Y-nm MLC NAND Flash chips

- Amount of program interference is dependent on

- Methodology: Extensive experimentation with real 2Y-nm MLC NAND Flash chips

- Amount of program interference is dependent on

Location of cells (programmed and victim)

- Methodology: Extensive experimentation with real 2Y-nm MLC NAND Flash chips

- Amount of program interference is dependent on

- Location of cells (programmed and victim)

- Data values of cells (programmed and victim)

- Methodology: Extensive experimentation with real 2Y-nm MLC NAND Flash chips

- Amount of program interference is dependent on

- Location of cells (programmed and victim)

- Data values of cells (programmed and victim)

- Programming order of pages

- Methodology: Extensive experimentation with real 2Y-nm MLC NAND Flash chips

- Amount of program interference is dependent on

- Location of cells (programmed and victim)

- Data values of cells (programmed and victim)

- Programming order of pages

- Our new model can predict the amount of program interference with 96.8% prediction accuracy

- Methodology: Extensive experimentation with real 2Y-nm MLC NAND Flash chips

- Amount of program interference is dependent on

- Location of cells (programmed and victim)

- Data values of cells (programmed and victim)

- Programming order of pages

- Our new model can predict the amount of program interference with 96.8% prediction accuracy

- Our new read reference voltage prediction technique can improve flash lifetime by 30%

Program Interference in MLC NAND Flash Memory: Characterization, Modeling, and Mitigation

# Today 1:40pm CSA-2: Memory Systems Session

Yu Cai<sup>1</sup> Onur Mutlu<sup>1</sup> Erich F. Haratsch<sup>2</sup> Ken Mai<sup>1</sup>

<sup>1</sup> Carnegie Mellon University

<sup>2</sup> LSI Corporation