## Data Retention in MLC NAND Flash Memory: Characterization, Optimization, and Recovery

Yu Cai, <u>Yixin Luo</u>, Erich F. Haratsch\*, Ken Mai, Onur Mutlu

Carnegie Mellon University, \*LSI Corporation

### You Probably Know

•Many use cases:

+ High performance, low energy consumption

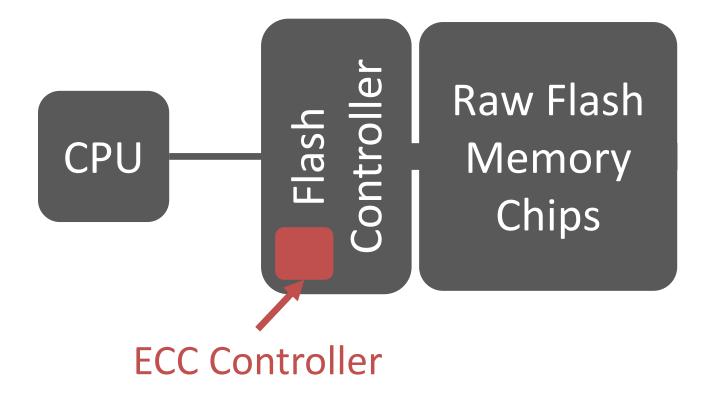

## NAND Flash Memory Challenges

Requires erase before program (write)

High raw bit error rate

## Limited Flash Memory Lifetime Goal: Extend flash memory lifetime Raw bit error rate (RBER) at low cost Nen P/E Cycle Lifetime ectable RBER 3000

Program/Erase (P/E) Cycles (or Writes Per Cell) 4

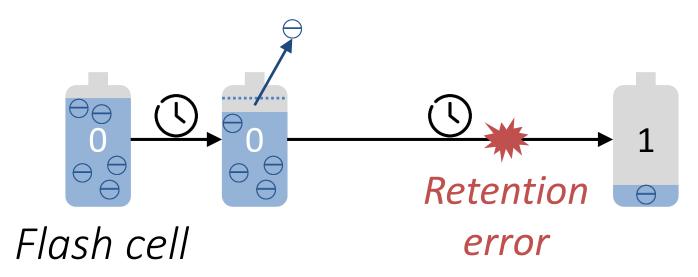

### **Retention Loss**

#### Charge leakage over time

### One dominant source of flash memory errors [DATE '12, ICCD '12]

Before I show you how we extend flash lifetime ...

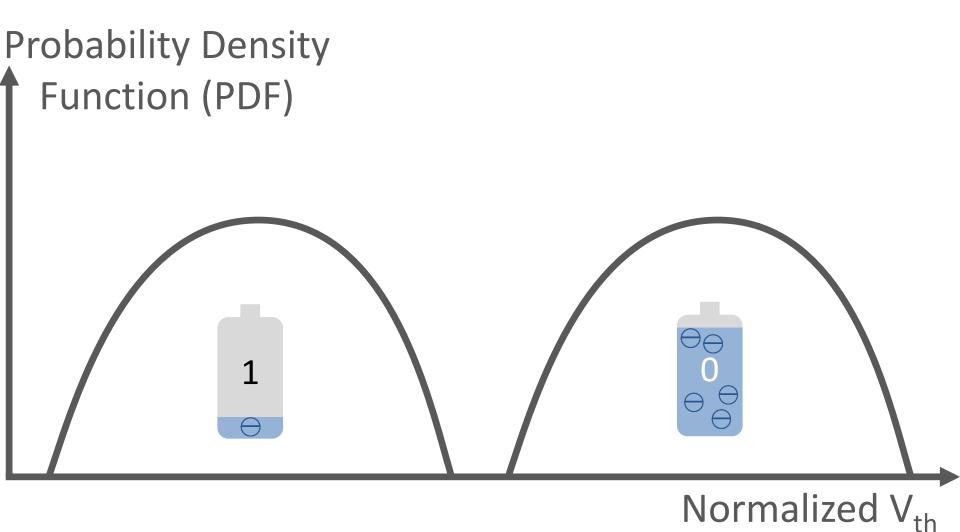

# NAND Flash 101

# Threshold Voltage (V<sub>th</sub>) $\Theta \Theta \Theta \Theta \Theta$ $\ominus$ Flash cell Flash cell 1 Normalized V<sub>th</sub>

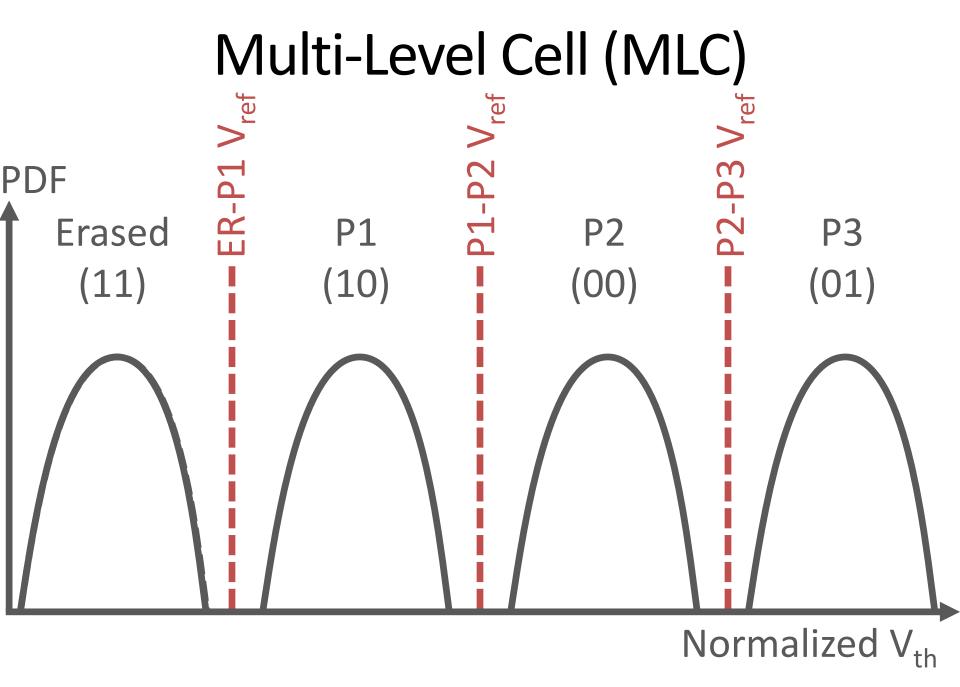

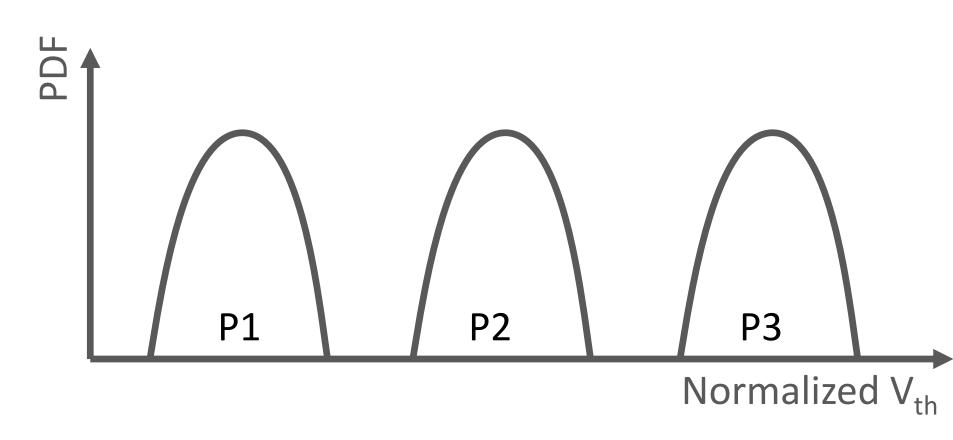

## Threshold Voltage (V<sub>th</sub>) Distribution

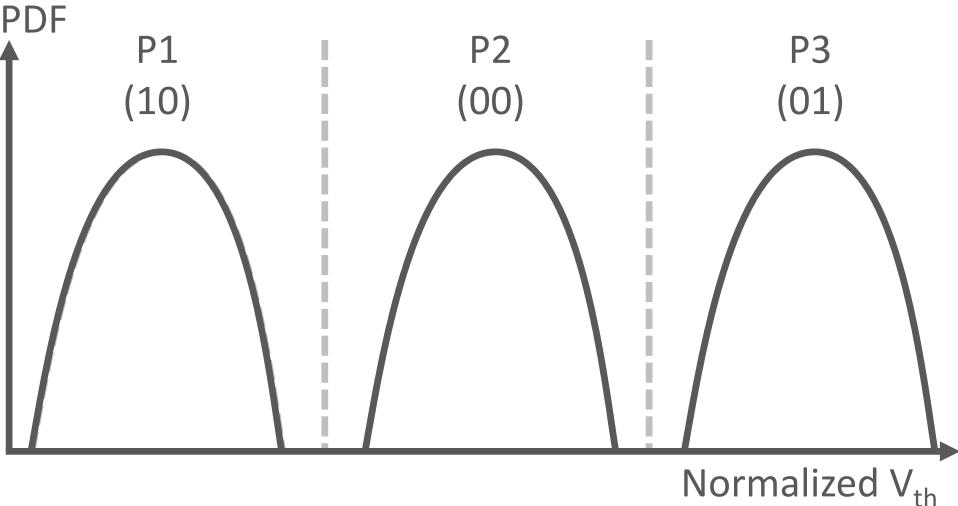

# **Threshold Voltage Reduces Over Time**

After some retention loss:

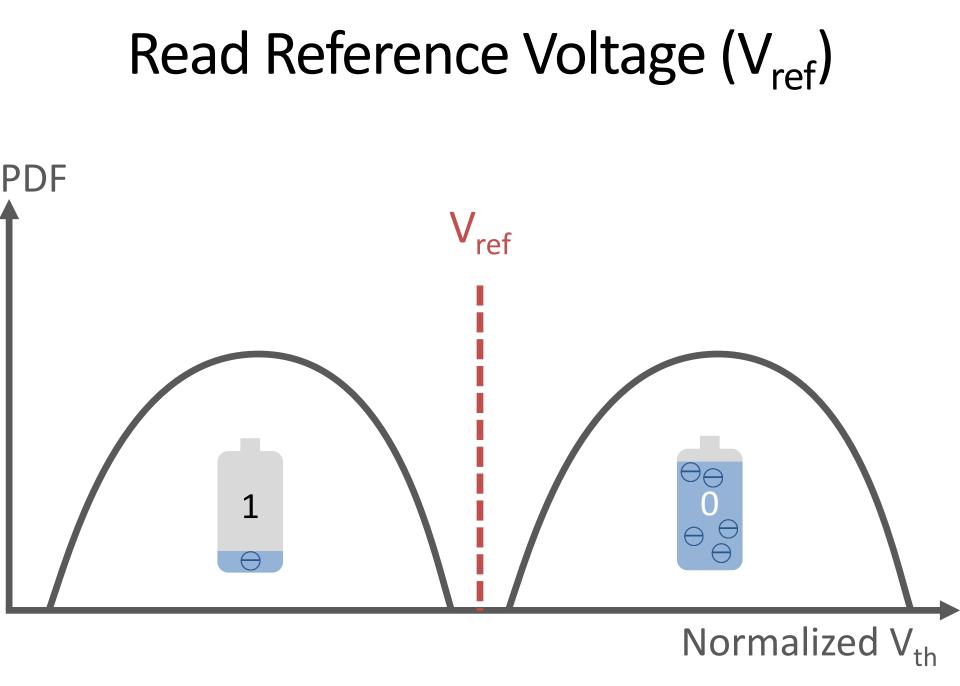

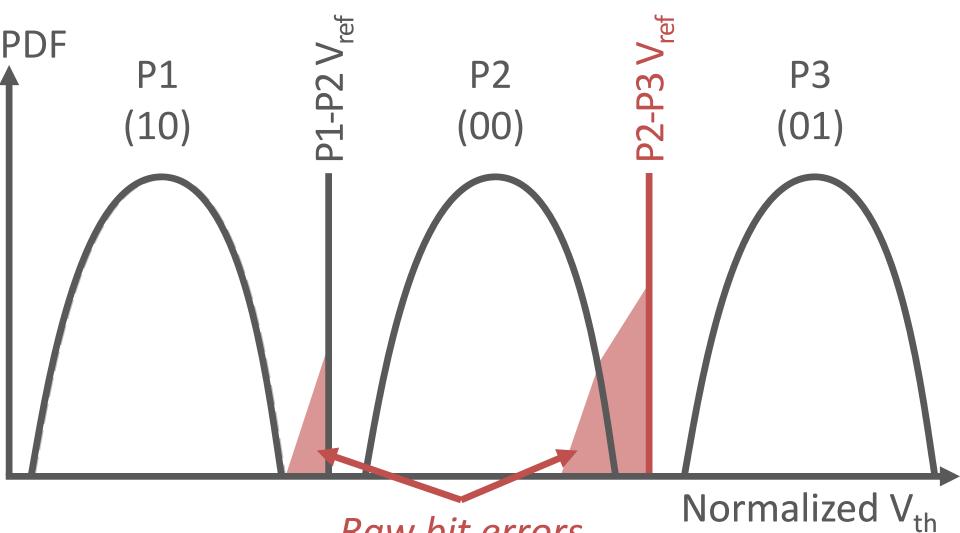

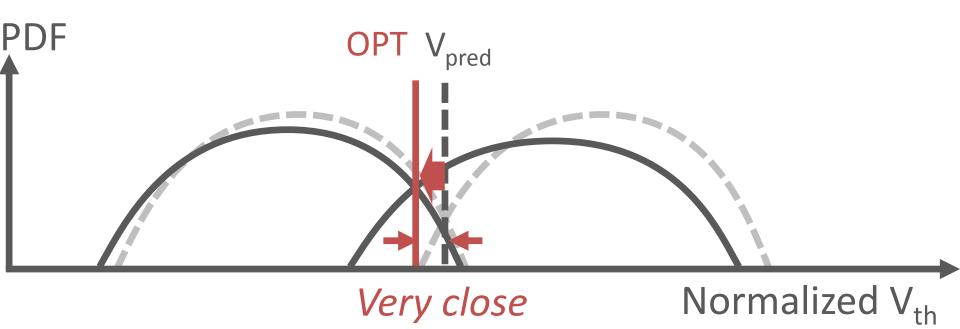

### **Fixed Read Reference Voltage Becomes Suboptimal**

After some retention loss:

Raw bit errors

### <u>Goal 1:</u> Design a low-cost mechanism that dynamically finds the optimal read reference voltage

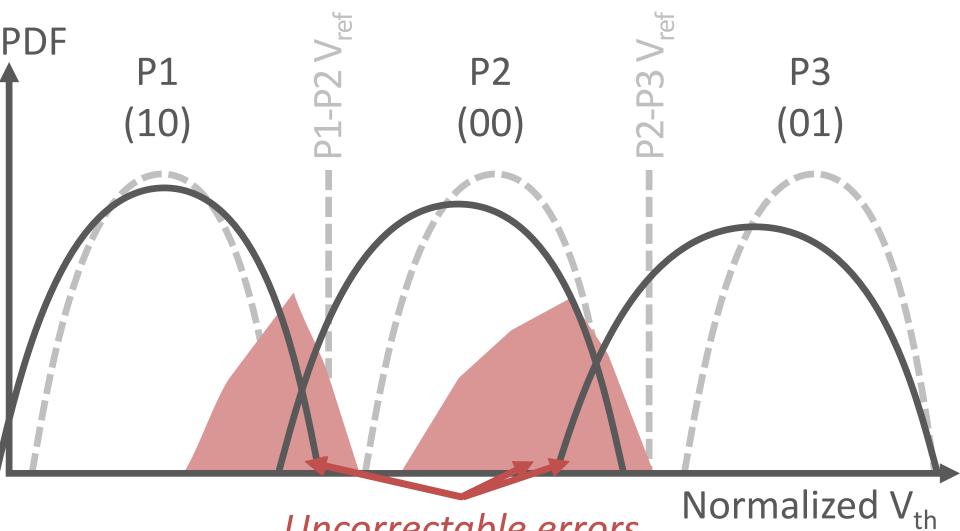

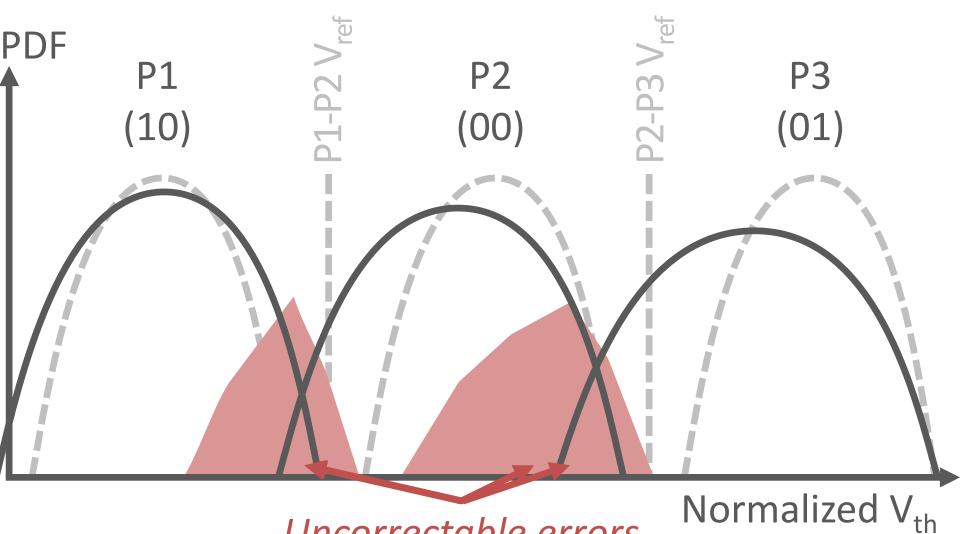

### **Retention Failure**

#### After **significant** retention loss:

Uncorrectable errors

### <u>Goal 1:</u> Design a low-cost mechanism that dynamically finds the optimal read reference voltage

<u>Goal 2:</u> Design an offline mechanism to recover data after detecting uncorrectable errors

### To understand the effects of retention loss: - Characterize retention loss using real chips

### To understand the effects of retention loss: - Characterize retention loss using real chips

<u>Goal 1:</u> Design a low-cost mechanism that dynamically finds the optimal read reference voltage

<u>Goal 2:</u> Design an offline mechanism to recover data after detecting uncorrectable errors

### **Characterization Methodology**

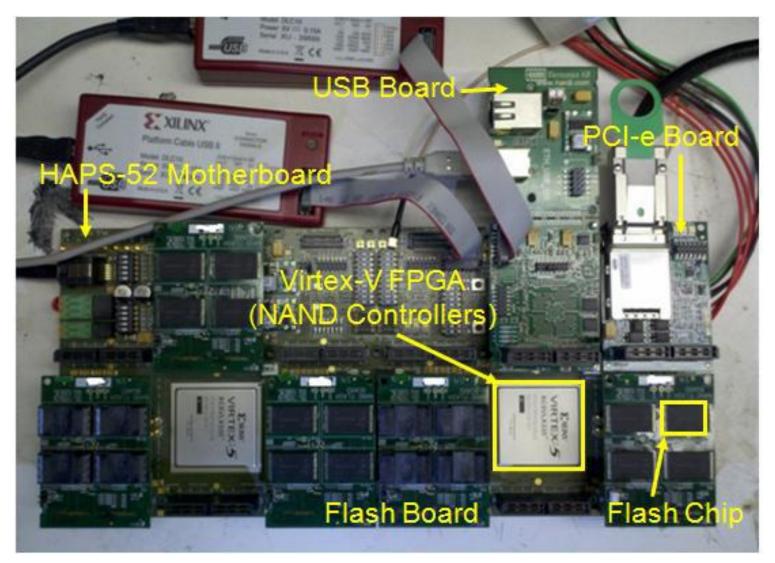

FPGA-based flash memory testing platform [Cai+,FCCM '11]

## **Characterization Methodology**

- •FPGA-based flash memory testing platform

- •Real 20- to 24-nm MLC NAND flash chips

- •0- to 40-day worth of retention loss

- •*Room temperature (20<sup>o</sup>C)*

- •*O to 50k P/E Cycles*

### Characterize the effects of retention loss

### 1. Threshold Voltage Distribution

### 2. Optimal Read Reference Voltage

### 3. RBER and P/E Cycle Lifetime

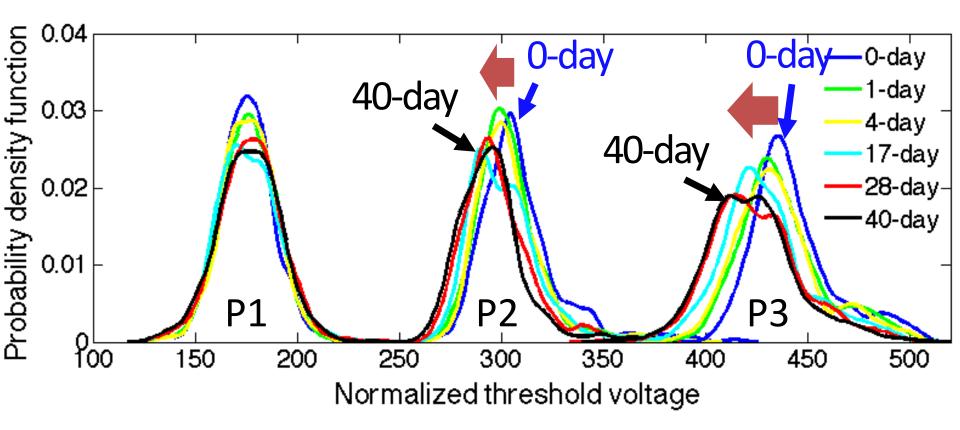

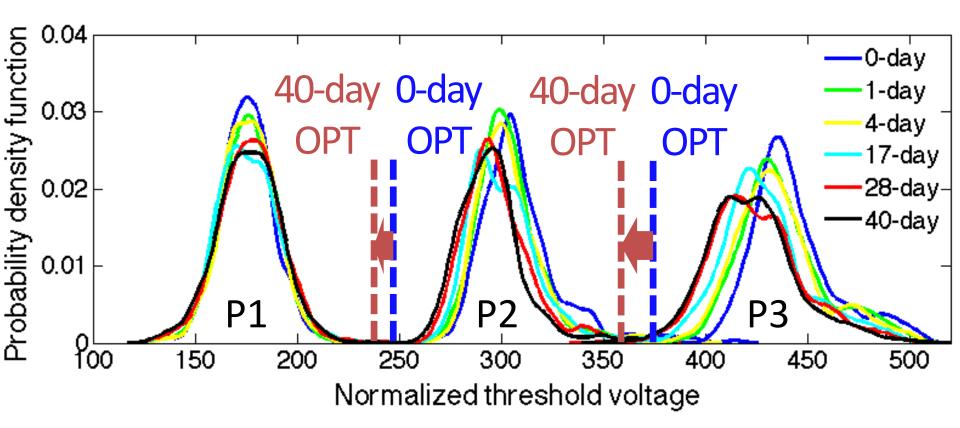

## 1. Threshold Voltage (V<sub>th</sub>) Distribution

## 1. Threshold Voltage (V<sub>th</sub>) Distribution

Finding: Cell's threshold voltage decreases over time

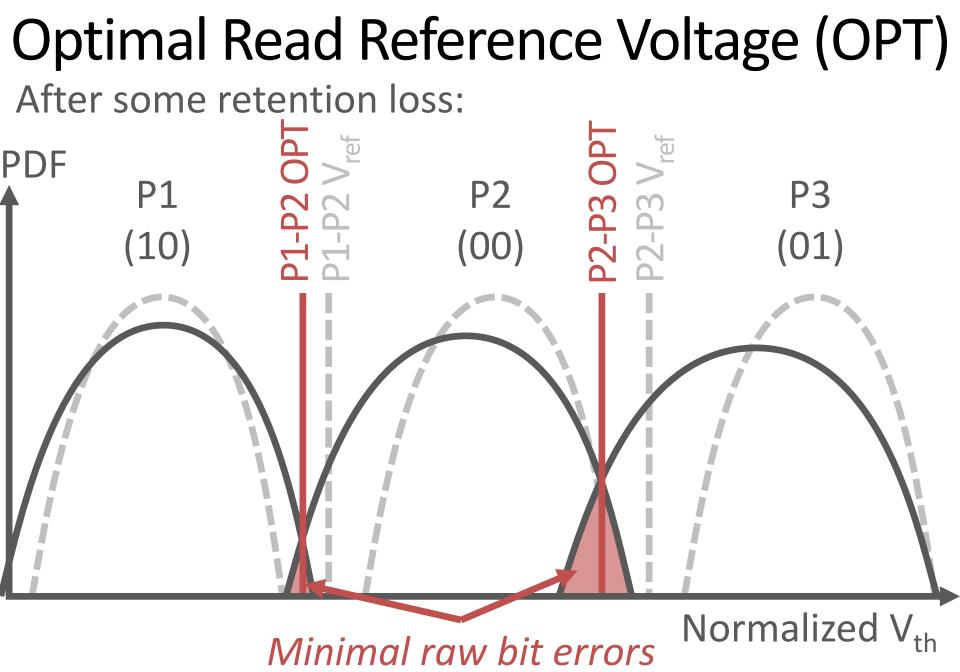

### 2. Optimal Read Reference Voltage (OPT)

#### Finding: OPT decreases over time

### 3. RBER and P/E Cycle Lifetime

P/E Cycles

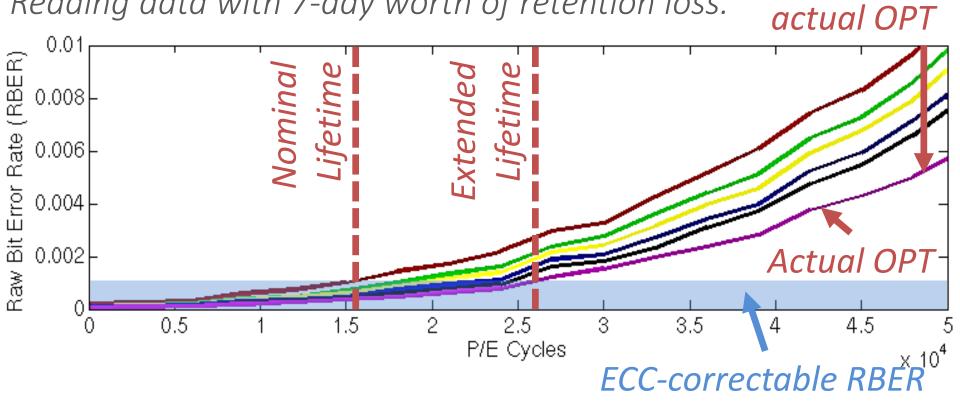

## 3. RBER and P/E Cycle Lifetime

Reading data with 7-day worth of retention loss.

Finding: Using actual OPT achieves the longest lifetime

#### SAFARI

V<sub>ref</sub> closer to

### **Characterization Summary**

- Due to *retention loss*

- Cell's threshold voltage (V<sub>th</sub>) decreases over time

- Optimal read reference voltage (OPT) decreases over time

*Using the actual OPT for reading* - Achieves the longest lifetime To understand the effects of retention loss: - Characterize retention loss using real chips

<u>Goal 1:</u> Design a low-cost mechanism that dynamically finds the optimal read reference voltage

<u>Goal 2:</u> Design an offline mechanism to recover data after detecting uncorrectable errors

## Naïve Solution: Sweeping V<sub>ref</sub>

<u>Key idea:</u> Read the data multiple times with different read reference voltages until the raw bit errors are correctable by ECC

✓ Finds the optimal read reference voltage

★Requires many read-retries → higher read latency

### **Comparison of Flash Read Techniques**

| Flash Read<br>Techniques     | <i>Lifetime<br/>(P/E Cycle)</i> | Performance<br>(Read Latency) |

|------------------------------|---------------------------------|-------------------------------|

| Fixed V <sub>ref</sub>       | ×                               |                               |

| Sweeping<br>V <sub>ref</sub> |                                 | ×                             |

| Our Goal                     |                                 |                               |

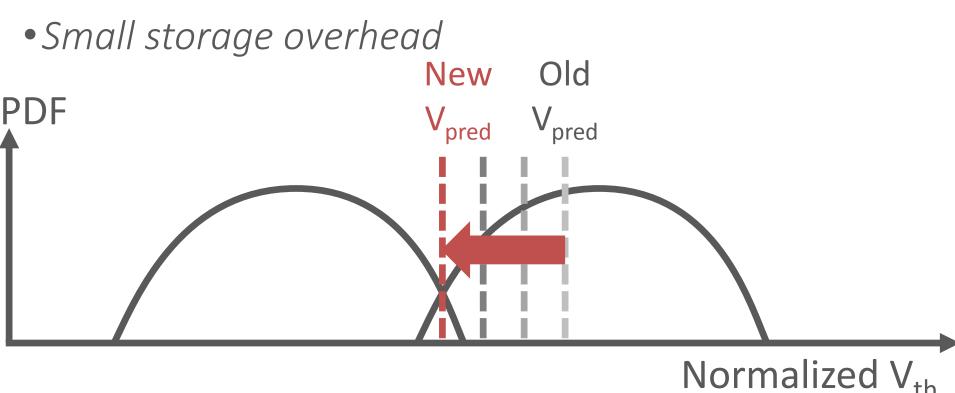

### Observations

1. The optimal read reference voltage gradually decreases over time

<u>Key idea:</u> Record the old OPT as a prediction ( $V_{pred}$ ) of the actual OPT

<u>Benefit:</u> Close to actual OPT -> Fewer read retries

2. The amount of retention loss is similar across pages within a flash block

<u>Key idea:</u> Record only one V<sub>pred</sub> for each block

<u>Benefit:</u> Small storage overhead (768KB out of 512GB)

## Retention Optimized Reading (ROR)

Components:

1. Online pre-optimization algorithm

- Periodically records a  $V_{pred}$  for each block

2. Improved read-retry technique

- Utilizes the recorded  $V_{\mbox{\scriptsize pred}}$  to minimize read-retry count

## 1. Online Pre-Optimization Algorithm

- Triggered periodically (e.g., per day)

- Find and record an OPT as per-block V<sub>pred</sub>

- Performed in background

33

## 2. Improved Read-Retry Technique

- Performed as normal read

- $\bullet V_{pred}$  already close to actual OPT

- Decrease  $V_{ref}$  if  $V_{pred}$  fails, and retry

### **Retention Optimized Reading: Summary**

| Flash Read<br>Techniques     | <i>Lifetime<br/>(P/E Cycle)</i> | Performance<br>(Read Latency)                                       |

|------------------------------|---------------------------------|---------------------------------------------------------------------|

| Fixed V <sub>ref</sub>       |                                 |                                                                     |

| Sweeping<br>V <sub>ref</sub> | 64%个                            |                                                                     |

| ROR                          | 64%个                            | <ul> <li>✓ Nom. Life: 2.4% ↓</li> <li>Ext. Life: 70.4% ↓</li> </ul> |

To understand the effects of retention loss: - Characterize retention loss using real chips

<u>Goal 1:</u> Design a low-cost mechanism that dynamically finds the optimal read reference voltage

<u>Goal 2:</u> Design an offline mechanism to recover data after detecting uncorrectable errors

# **Retention Failure**

After **significant** retention loss:

Uncorrectable errors

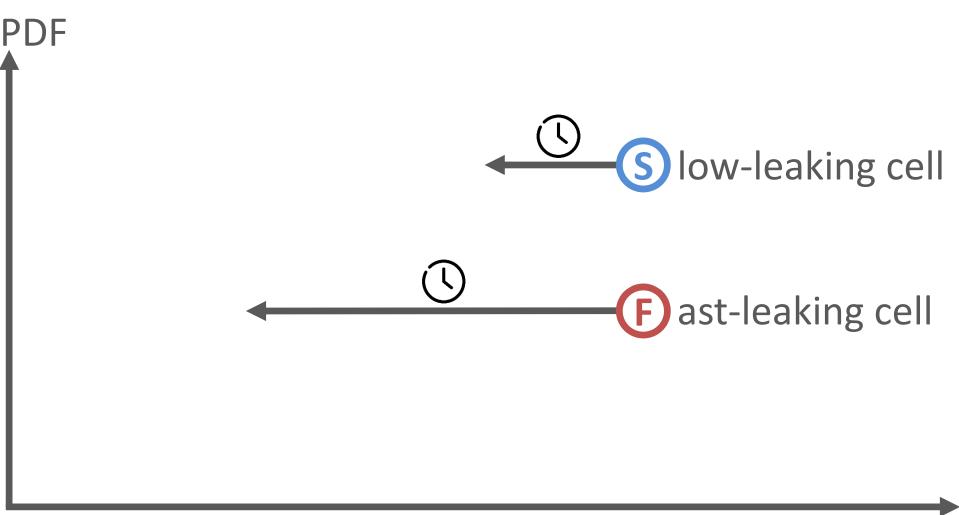

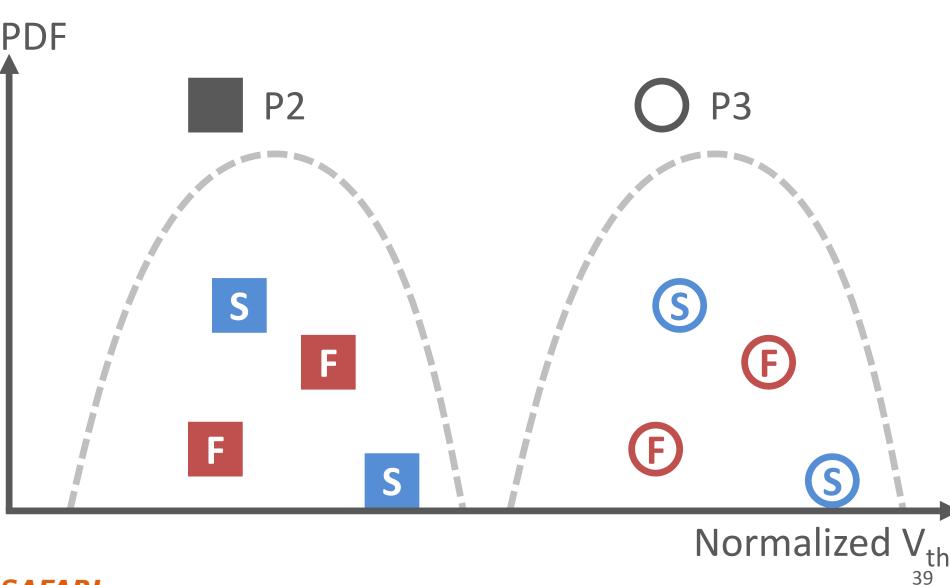

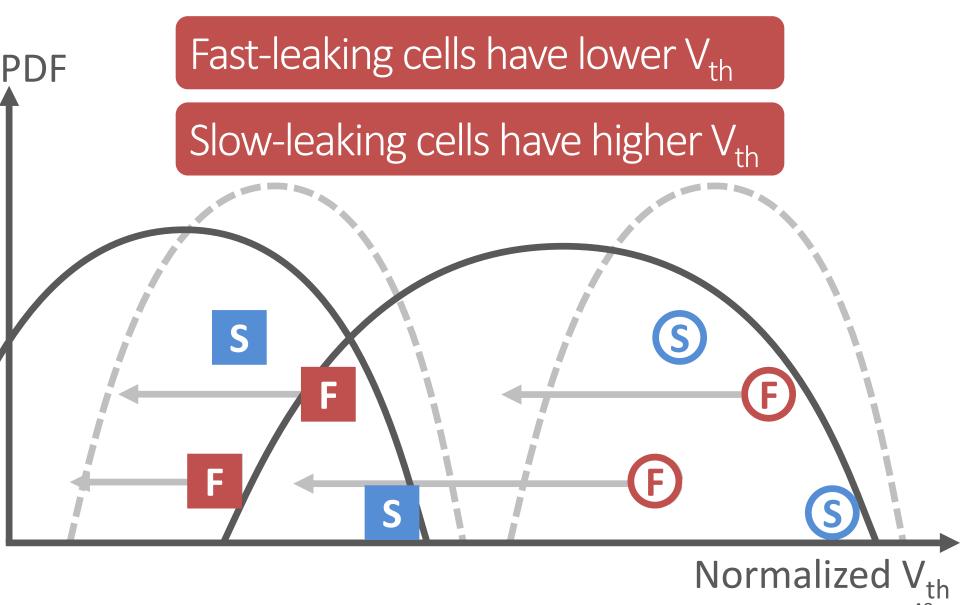

# Leakage Speed Variation

# Initially, Right After Programming

# After Some Retention Loss

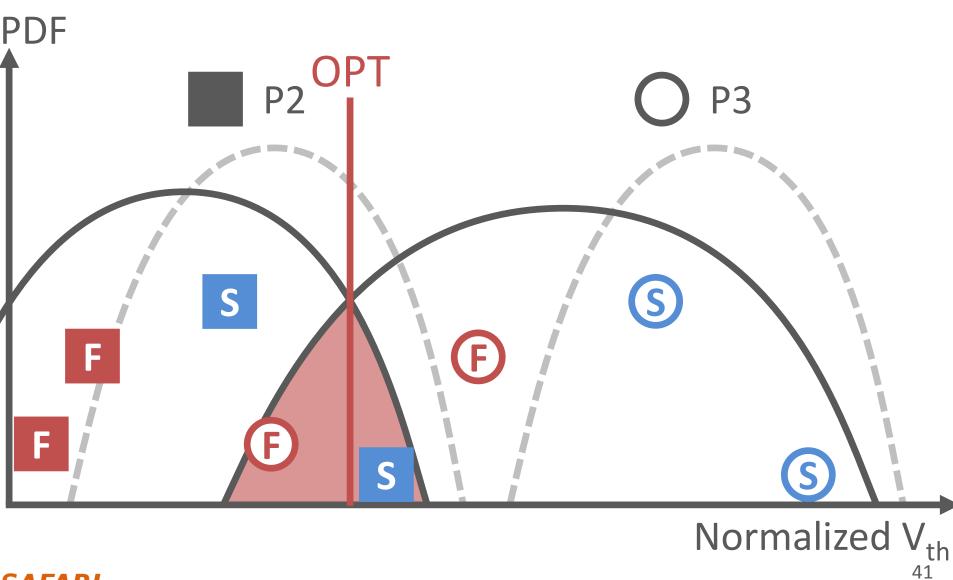

## **Eventually: Retention Failure**

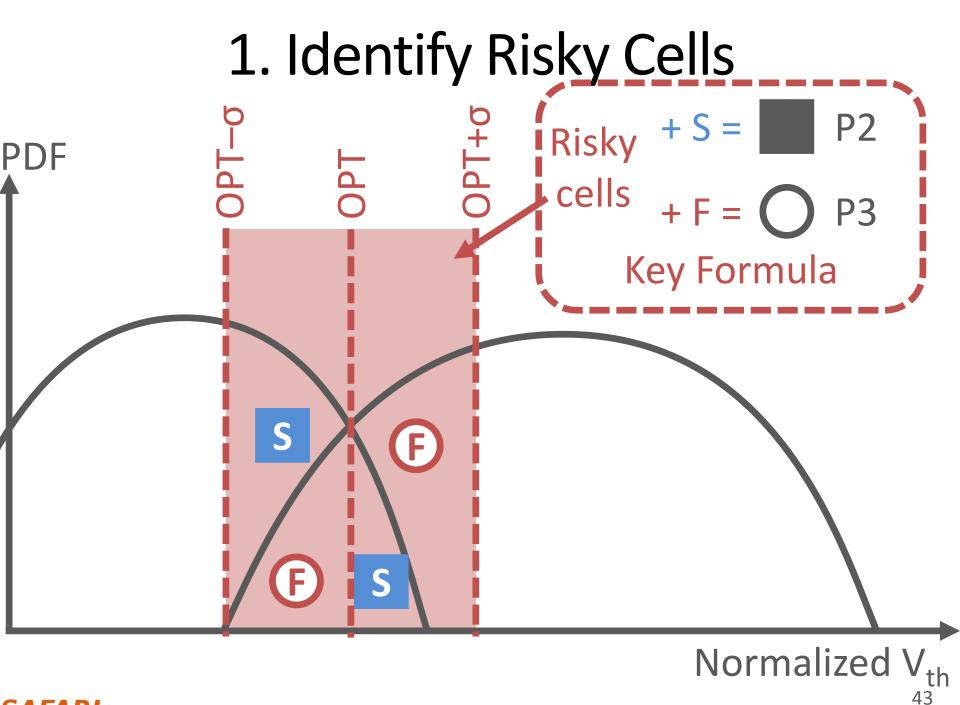

# Retention Failure Recovery (RFR)

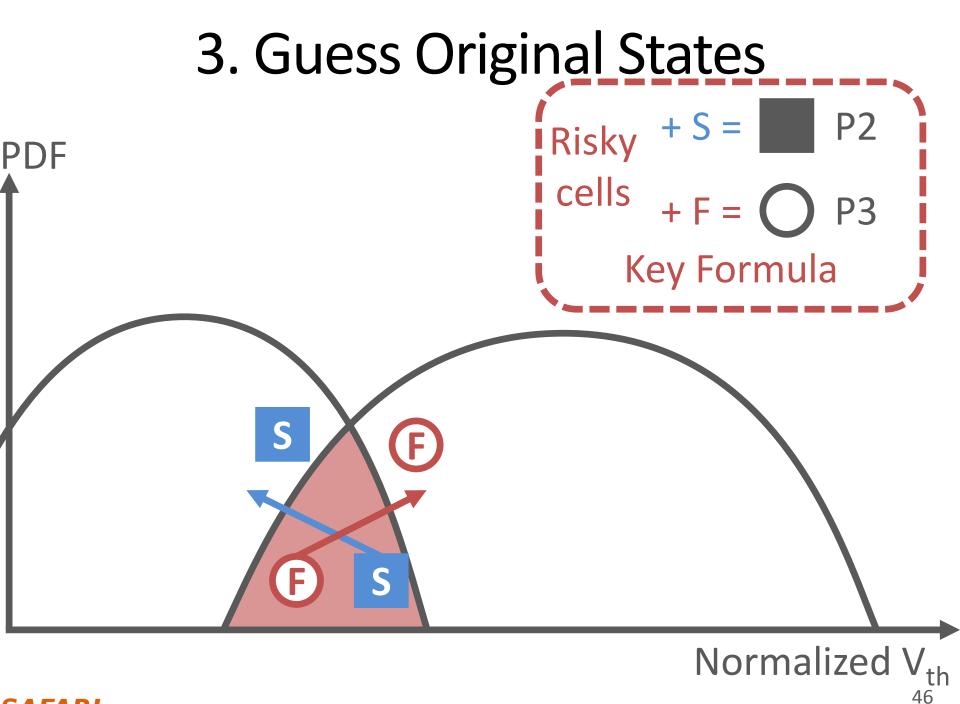

<u>Key idea:</u> Guess original state of the cell from its leakage speed property

Three steps

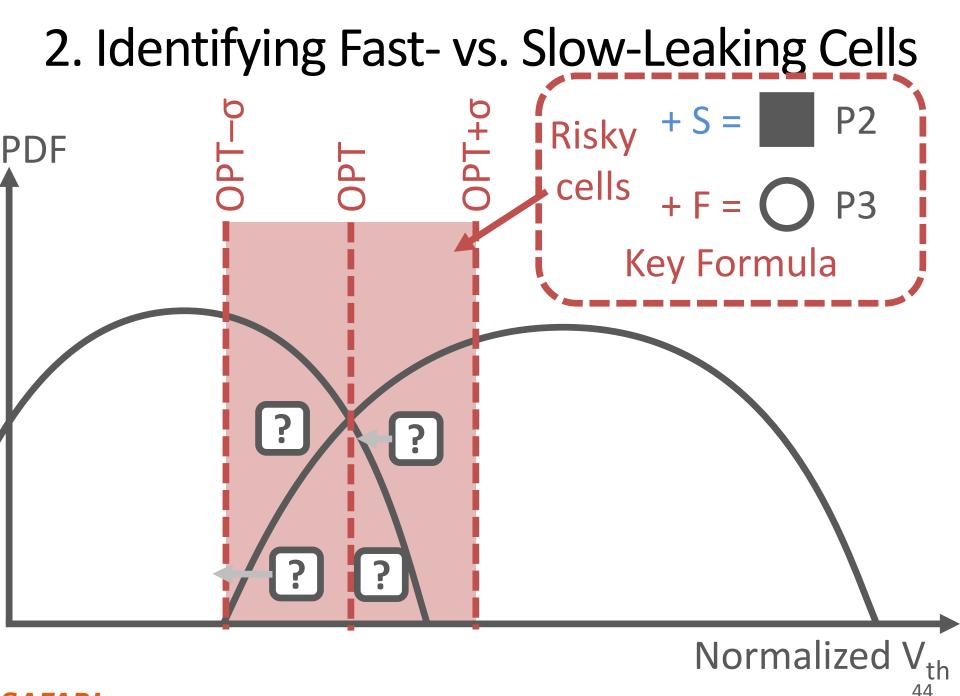

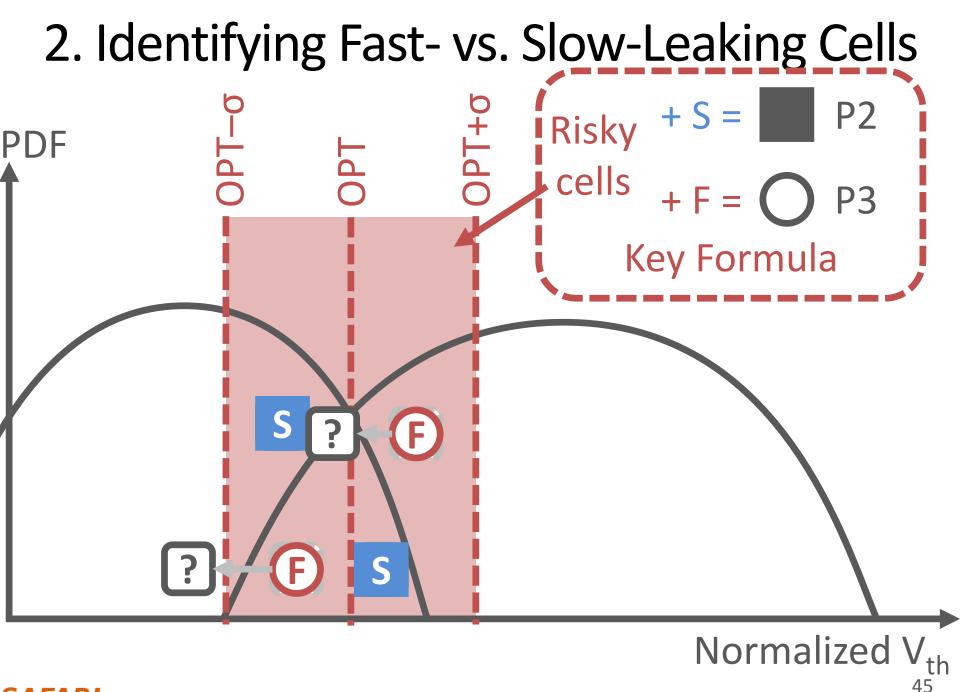

- 1. Identify risky cells

- 2. Identify fast-/slow-leaking cells

- 3. Guess original states

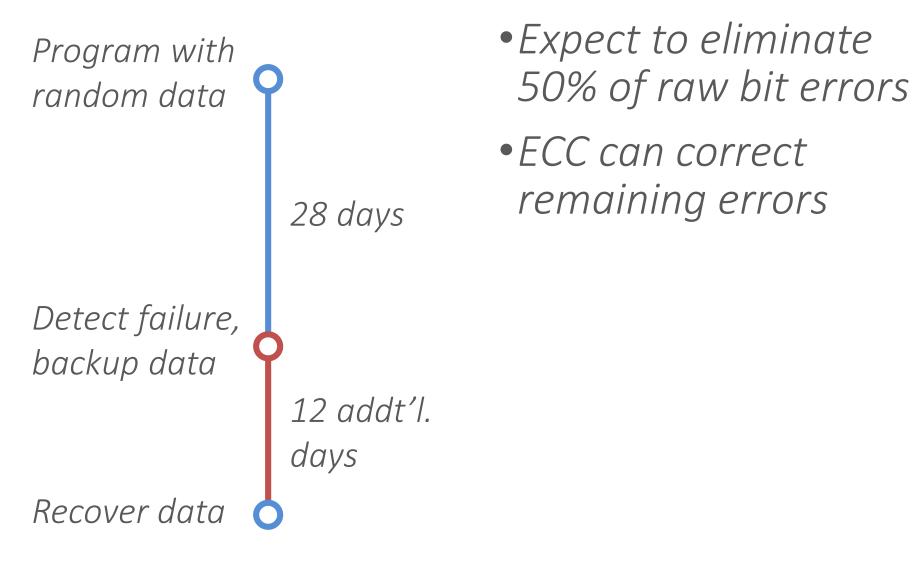

# **RFR Evaluation**

To understand the effects of retention loss: - Characterize retention loss using real chips

<u>Goal 1:</u> Design a low-cost mechanism that dynamically finds the optimal read reference voltage

<u>Goal 2:</u> Design an offline mechanism to recover data after detecting uncorrectable errors

# Conclusion

**Problem:** Retention loss reduces flash lifetime

**Overall Goal:** Extend flash lifetime at low cost

<u>Flash Characterization:</u> Developed an understanding of the effects of retention loss in real chips

<u>Retention Optimized Reading:</u> A low-cost mechanism that dynamically finds the optimal read reference voltage

- 64% lifetime  $\uparrow$ , 70.4% read latency  $\downarrow$

<u>Retention Failure Recovery:</u> An offline mechanism that recovers data after detecting uncorrectable errors

- Raw bit error rate 50%  $\downarrow$ , reduces data loss

# Data Retention in MLC NAND Flash Memory: Characterization, Optimization, and Recovery

Yu Cai, <u>Yixin Luo</u>, Erich F. Haratsch\*, Ken Mai, Onur Mutlu

Carnegie Mellon University, \*LSI Corporation

# **Backup Slides**

# **RFR** Motivation

Data loss can happen in many ways

- 1. High P/E cycle

- 2. High temperature  $\rightarrow$  accelerates retention loss

- 3. High retention age (lost power for a long time)

# What if there are other errors?

<u>Key:</u> RFR does not have to correct all errors

Example:

- ECC can correct 40 errors in a page

- •Corrupted page has 20 retention errors, 25 other errors (45 total errors)

- •After RFR: 10 retention errors, 30 other errors (40 total errors  $\rightarrow$  ECC correctable)