## Warp Scheduler Controls GPU Thread-Level Parallelism

## Warp Scheduler Controls GPU Thread-Level Parallelism

|                         | Improved GPU | Improved CPU |

|-------------------------|--------------|--------------|

|                         | performance  | performance  |

| CPU-centric<br>Strategy | ×            |              |

|                         |              |              |

|                         |              |              |

## Warp Scheduler Controls GPU Thread-Level Parallelism

|                     | Improved GPU | Improved CPU |

|---------------------|--------------|--------------|

|                     | performance  | performance  |

| <b>CPU</b> -centric | <b>✓</b>     | -<br>/       |

| Strategy            |              |              |

| CPU-GPU             |              |              |

| Balanced            |              |              |

| Strategy            |              |              |

## Warp Scheduler Controls GPU Thread-Level Parallelism

|                     | Improved GPU | Improved CPU |

|---------------------|--------------|--------------|

|                     | performance  | performance  |

| <b>CPU</b> -centric | <b>~</b>     | -<br>        |

| Strategy            |              |              |

| CPU-GPU             |              |              |

| Balanced            |              |              |

| Strategy            |              |              |

Control the trade-off

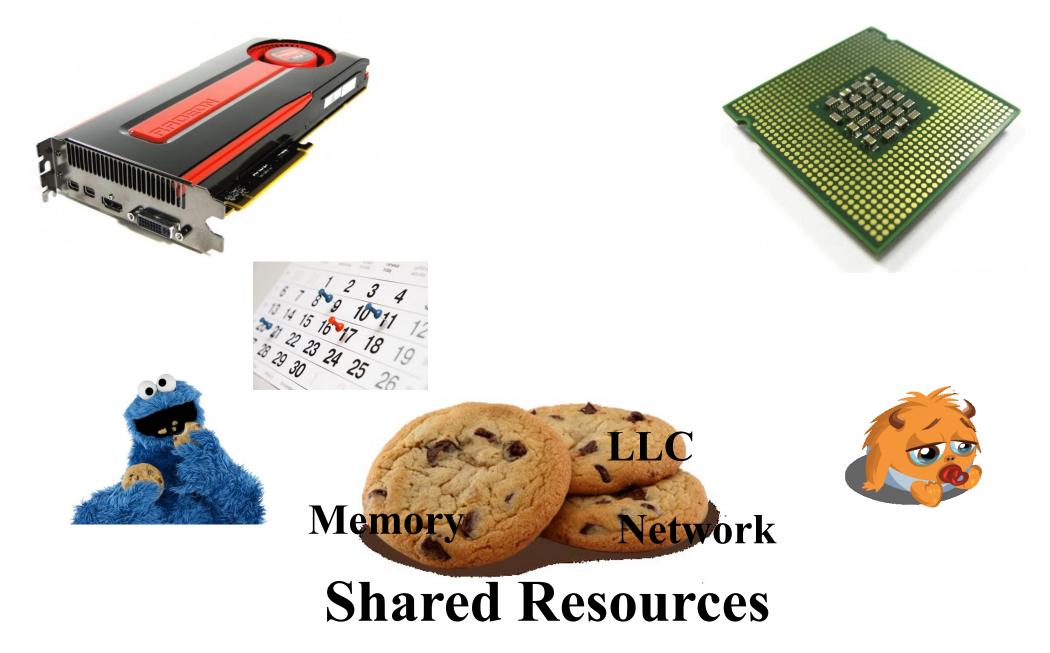

#### **CPU-centric Strategy**

Memory Congestion

#### **CPU-centric Strategy**

Memory Congestion

**CPU Performance**

IF Memory Congestion

#### **CPU-centric Strategy**

Memory Congestion

**CPU Performance**

IF Memory Congestion

GPU TLP

Results Summary:

+24% CPU & -11% GPU

#### **CPU-centric Strategy**

**CPU-GPU Balanced Strategy**

Memory Congestion

GPU TLP

**CPU Performance**

GPU Latency Tolerance -

Results Summary:

+24% CPU & -11% GPU

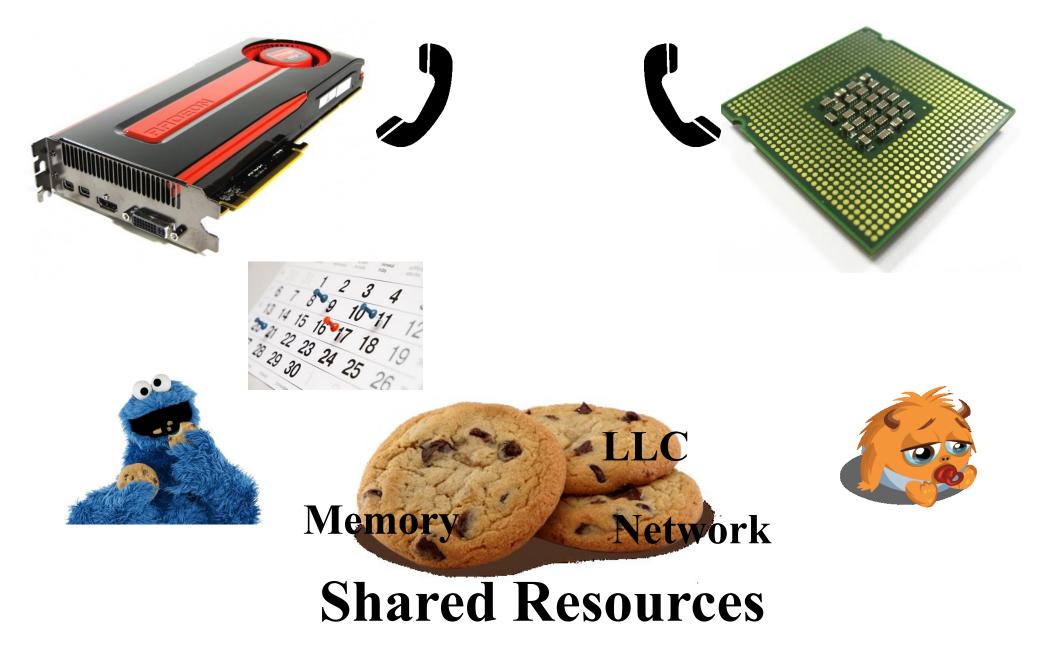

#### **CPU-centric Strategy**

**CPU-GPU Balanced Strategy**

Memory Congestion

GPU TLP

**CPU Performance**

GPU Latency Tolerance

IF Latency Tolerance

GPU TLP

Results Summary:

+24% CPU & -11% GPU

**CPU-centric Strategy**

**CPU-GPU Balanced Strategy**

Memory Congestion

GPU TLP

**CPU Performance**

GPU Latency Tolerance

IF Latency Tolerance

GPU TLP

Results Summary:

+24% CPU & -11% GPU

**Results Summary:**

+7% both CPU & GPU

Onur Kayıran<sup>1</sup>,

Nachiappan CN<sup>1</sup>, Adwait Jog<sup>1</sup>, Rachata Ausavarungnirun<sup>2</sup>,

Mahmut T. Kandemir<sup>1</sup>, Gabriel H. Loh<sup>3</sup>, Onur Mutlu<sup>2</sup>, Chita R. Das<sup>1</sup>

Penn State

Carnegie Mellon

AMD Research

Onur Kayıran<sup>1</sup>,

Nachiappan CN<sup>1</sup>, Adwait Jog<sup>1</sup>, Rachata Ausavarungnirun<sup>2</sup>,

Mahmut T. Kandemir<sup>1</sup>, Gabriel H. Loh<sup>3</sup>, Onur Mutlu<sup>2</sup>, Chita R. Das<sup>1</sup>

Carnegie Mellon

Penn State

Carnegie Mellon

AMD Research

Today

Session 1B – Main Auditorium

@ 3 pm