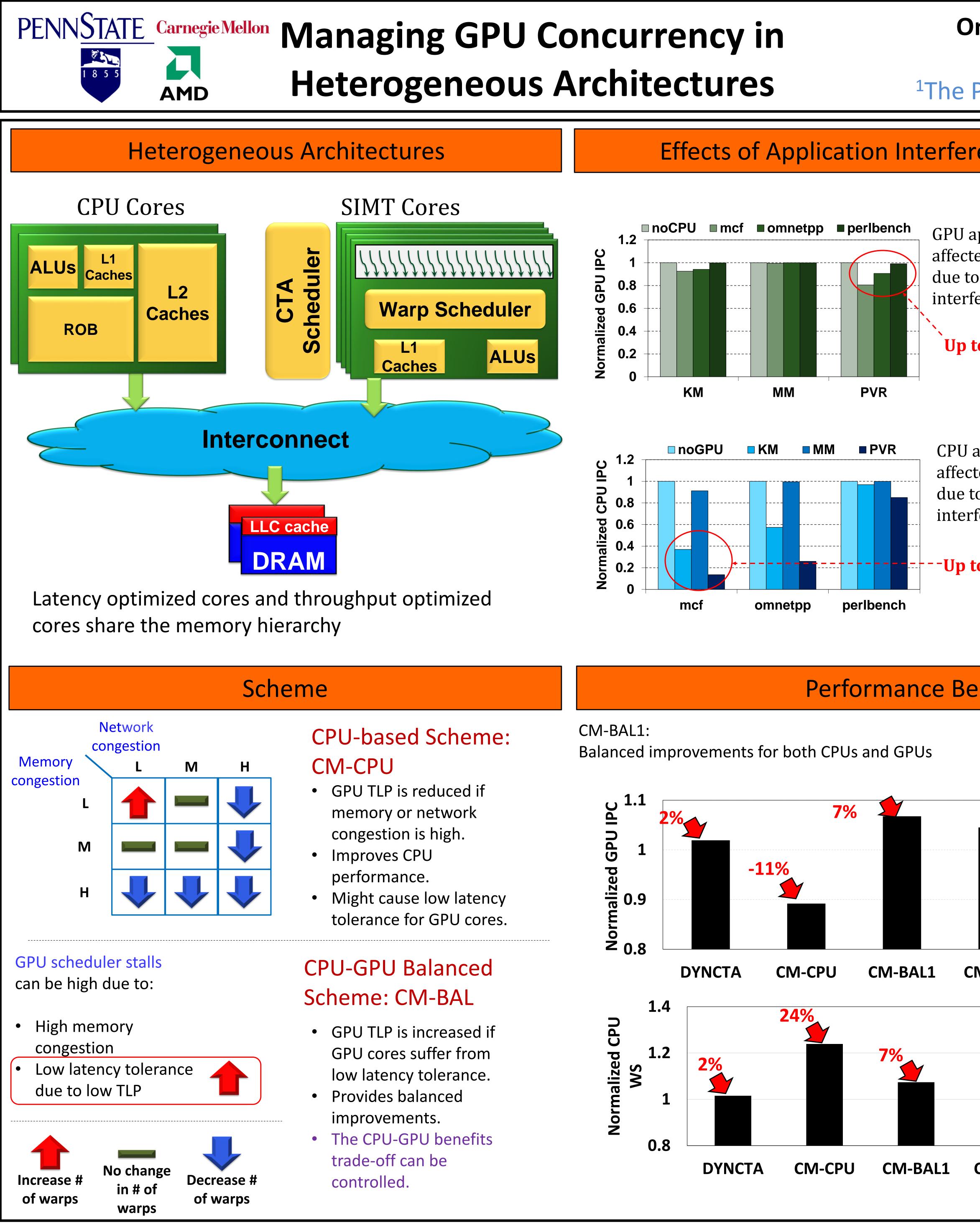

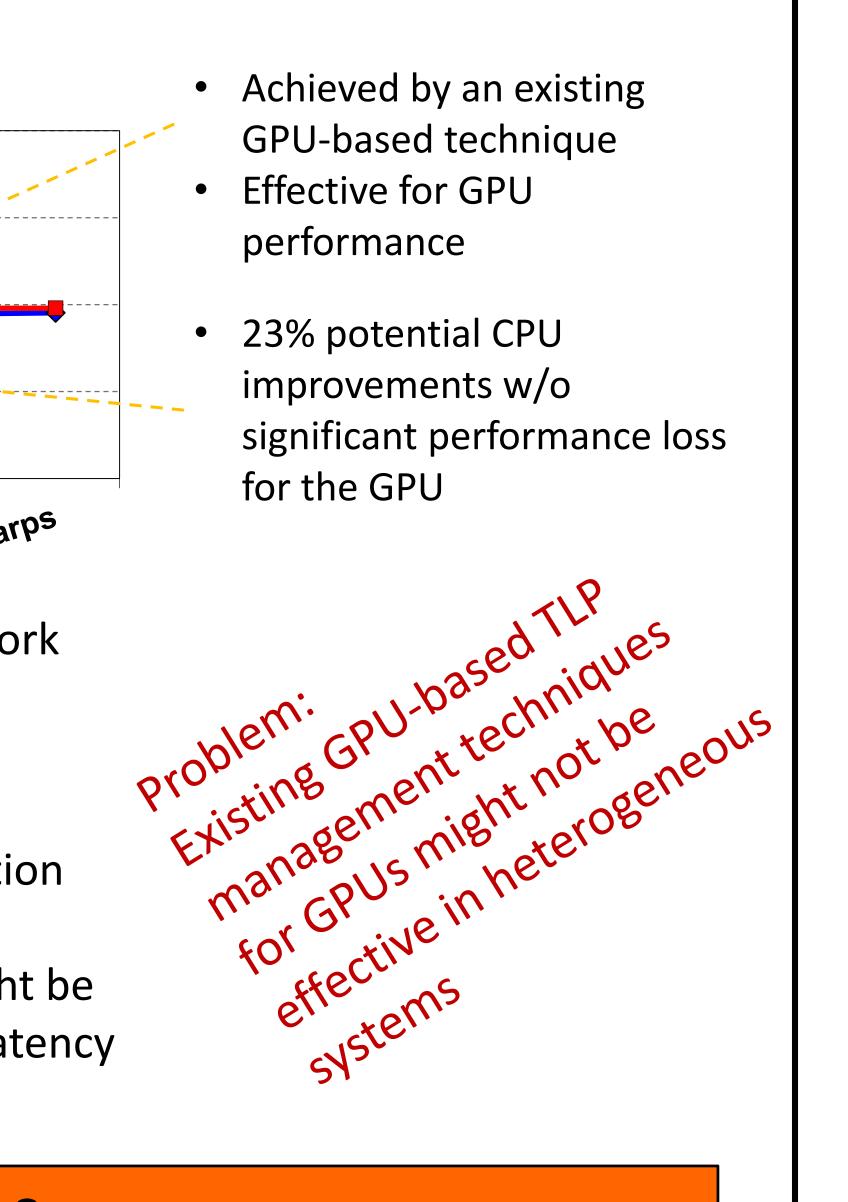

## **Effects of Application Interference** Latency Tolerance of CPUs vs. GPUs ◆GPU IPC -CPU IPC GPU applications are IPC affected moderately .5 σ due to CPU nalize interference ວັ 0.5 X **Up to 20%** 0 1 warp 4 warps 6 warps 8 warps 16 warps A8 warps High GPU TLP causes memory and network CPU applications are congestion affected significantly problem. due to GPU High memory congestion degrades CPU interference performance • GPU cores can tolerate memory congestion -Up to 85% due to multi-threading • The optimal TLP for CPUs and GPUs might be different due to the disparity between latency tolerance of CPUs and GPUs

# **Performance Benefits** CM-BAL4: Tuned to favor CPU applications -11% Existing Works CM-BAL4 CM-BAL2 CM-BAL3 CPU-based Scheme 19% **CPU-GPU** Balanced Scheme CM-BAL2 CM-BAL3 CM-BAL4

**Onur Kayıran<sup>1</sup>** Nachiappan CN<sup>1</sup> Adwait Jog<sup>1</sup> Rachata Ausavarungnirun<sup>2</sup> Mahmut T. Kandemir<sup>1</sup> Gabriel H. Loh<sup>3</sup> Onur Mutlu<sup>2</sup> Chita R. Das<sup>1</sup> <sup>1</sup>The Pennsylvania State University <sup>2</sup>Carnegie Mellon University <sup>3</sup>AMD Research

# Summary