# **Highly Concurrent Latency-Tolerant Register Files for GPUs**

MOHAMMAD SADROSADATI, Institute for Research in Fundamental Sciences (IPM) AMIRHOSSEIN MIRHOSSEINI, University of Michigan ALI HAJIABADI, Sharif University of Technology SEYED BORNA EHSANI, Sharif University of Technology HAJAR FALAHATI, Institute for Research in Fundamental Sciences (IPM) HAMID SARBAZI-AZAD, Sharif University of Technology and Institute for Research in Fundamental Sciences (IPM) MARIO DRUMOND, EPFL BABAK FALSAFI, EPFL RACHATA AUSAVARUNGNIRUN, CMU ONUR MUTLU, ETH Zürich and CMU

Graphics Processing Units (GPUs) employ large register files to accommodate all active threads and accelerate context switching. Unfortunately, register files are a scalability bottleneck for future GPUs due to long access latency, high power consumption, and large silicon area provisioning. Prior work proposes hierarchical register file to reduce the register file power consumption by caching registers in a smaller register file cache. Unfortunately, this approach does not improve register access latency due to the low hit rate in the register file cache.

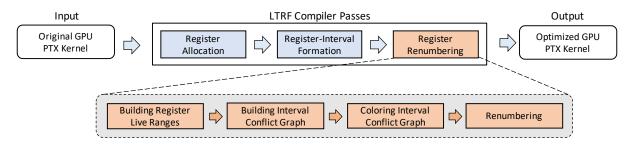

In this paper, we propose the Latency-Tolerant Register File (LTRF) architecture to achieve low latency in a two-level hierarchical structure while keeping power consumption low. We observe that compile-time interval analysis enables us to divide GPU program execution into intervals with an accurate estimate of a warp's aggregate register working-set within each interval. The key idea of LTRF is to prefetch the estimated register working-set from the main register file to the register file cache under software control, at the beginning of each interval, and overlap the prefetch latency with the execution of other warps. We observe that register bank conflicts while prefetching the registers could greatly reduce the effectiveness of LTRF. Therefore, we devise a compile-time register renumbering technique to reduce the likelihood of register bank conflicts. Our experimental results show that LTRF enables high-capacity yet long-latency main GPU register files, paving the way for various optimizations. As an example optimization, we implement the main register file with emerging high-density high-latency memory technologies, enabling 8× larger capacity and improving overall GPU performance by 34%.

$\texttt{CCS Concepts:} \bullet \textbf{Hardware} \rightarrow \textbf{Power and energy}; \bullet \textbf{Computer systems organization} \rightarrow \textit{Single instruction, multiple data};$

Additional Key Words and Phrases: GPUs, Register Files, Bank Conflicts, Register Renumbering, Latency Tolerance, Parallelism, High Performance

Authors' addresses: Mohammad Sadrosadati, Institute for Research in Fundamental Sciences (IPM), m.sadr89@gmail.com; Amirhossein Mirhosseini, University of Michigan; Ali Hajiabadi, Sharif University of Technology; Seyed Borna Ehsani, Sharif University of Technology; Hajar Falahati, Institute for Research in Fundamental Sciences (IPM); Hamid Sarbazi-Azad, Sharif University of Technology and Institute for Research in Fundamental Sciences (IPM); Mario Drumond, EPFL; Babak Falsafi, EPFL; Rachata Ausavarungnirun, CMU; Onur Mutlu, ETH Zürich and CMU.

© X Association for Computing Machinery. 0734-2071/X/1-ART1 \$15.00 https://doi.org/10.1145/nnnnnnnnnn

ACM Trans. Comput. Syst., Vol. 1, No. 1, Article 1. Publication date: January X.

ACM acknowledges that this contribution was authored or co-authored by an employee, contractor, or affiliate of the United States government. As such, the United States government retains a nonexclusive, royalty-free right to publish or reproduce this article, or to allow others to do so, for government purposes only.

#### **ACM Reference Format:**

#### 1 INTRODUCTION

Graphics Processing Units (GPUs) are commonly-used accelerators, optimizing silicon organization with dense arithmetic for data-parallel workloads. Modern GPU microarchitecture relies on managing execution resources for a large number of Single-Instruction-Multiple-Data (SIMD) threads to exploit this arithmetic density and overlap the long memory access latency with computation [136]. Unfortunately, the maximum parallelism in GPUs is fundamentally limited by the register file capacity as the register file must accommodate all simultaneously running threads [2, 49–51, 98, 115, 187].

GPU register files face the difficult challenge of optimizing latency, bandwidth, and power consumption, while having maximal capacity. Prior work proposes increasing the register file capacity in various ways: compression [98], virtualization [65, 184], or silicon technologies for high-density memory cells [69, 70, 103, 107, 108, 115, 187]. While such proposals increase capacity without sacrificing power consumption, they typically result in higher register access latencies.

Register file caching [49, 50] is a promising approach to enhancing capacity while lowering power consumption and effective access latency. Unfortunately, existing proposals for register file caching do *not* achieve high enough hit rates in the register cache due to *three* key problems. First, the high degree of thread-level parallelism (TLP) in GPUs causes threads to displace each other's registers in the cache. Second, registers house temporary values that are often renamed, which reduces temporal locality in the cache. Third, because register names are *not* spatially correlated, there is no spatial locality in a register cache. Due to these reasons, register file caching is ineffective at hiding latency in GPUs (§ 7).

Our goal is to improve the effectiveness of register file caching in GPUs. To this end, we observe that registers can be effectively prefetched into the register cache using compile-time interval analysis to hide the long access latency of the main register file. An interval is a subgraph in a program's control-flow graph that has a *single* entry point. Intervals have been widely used by optimizing compilers to identify loops [58]. We use interval analysis and software prefetching to fetch the entire set of required registers of an interval into the register cache and thus avoid the main register file access latency during the execution of the interval.

We propose the *Latency-Tolerant Register File (LTRF)*, a two-level hierarchical register file that employs a low-latency/low-power first-level register file cache backed up by a high-latency/high-capacity second-level main register file. LTRF uses a compiler-driven software mechanism to prefetch a warp's register working-set into the register cache at the start of an interval. By fetching *all* registers in the working-set together and overlapping the prefetch latency of one warp with the execution of another, LTRF hides a substantial fraction of the access latency of the main register file during the execution of the interval.

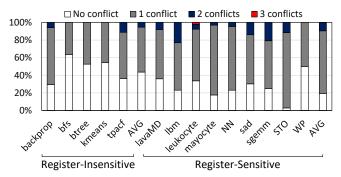

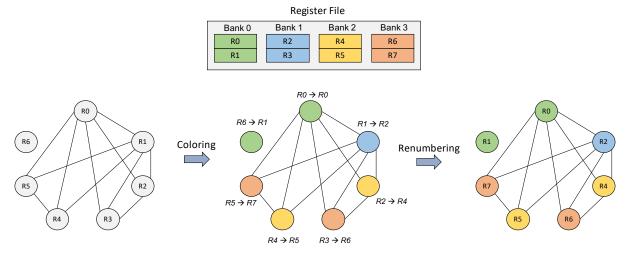

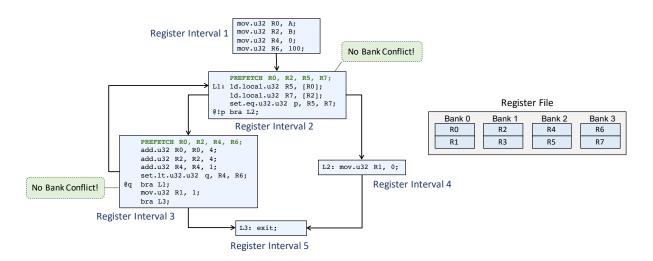

To accelerate register prefetching operations, it is crucial to avoid main register file bank conflicts. As the main register file banks are single ported, the bank conflicts increase the prefetch latency significantly. To resolve the main register file bank conflicts, we also devise a compile-time register renumbering technique on top of LTRF, while preserving the correctness of the program.

By using LTRF, we enable high-capacity yet long-latency main register files, paving the way for various optimizations. As an example optimization, we implement the main register file with high-density emerging memory technologies, e.g., domain wall memory [6, 9, 115, 141, 163, 177, 181], enabling 8× larger capacity and improving overall GPU performance by 31% while reducing register file power consumption by 46%. In contrast, the state-of-the-art register file caching schemes reduce GPU performance by 14%, on average, if the register file is enlarged by 8×, as prior designs do *not* focus on tolerating the latency of the main register file.

This paper makes the following contributions:

- We show that prior proposals for register file caching do *not* achieve high enough hit rates to effectively hide the long latencies of large main register files (§ 7).

- We introduce LTRF, a latency-tolerant hierarchical register file design, which enables high-capacity yet long-latency main register files. The key idea is to 1) estimate the register working set of a program's execution during an interval, using compile-time interval analysis, 2) prefetch the estimated register working-set from the main register file to the register file cache under software control, at the beginning of each interval, and overlap the prefetch latency with the execution of other warps.

- We devise a compile-time register-renumbering technique to mitigate the overhead of register bank conflicts in register prefetching operations.

- Our evaluations show that an optimized version of LTRF, when implemented with an 8× larger yet 6.3× slower main register file, improves overall GPU throughput by 31%, on average (up to 86%). LTRF performance is within 5% of an ideal 8×-capacity main register file that has no latency overhead.

# 2 BACKGROUND AND MOTIVATION

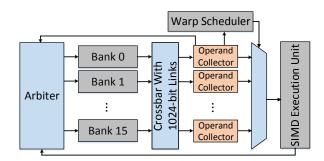

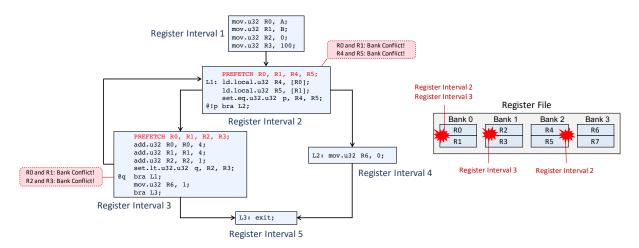

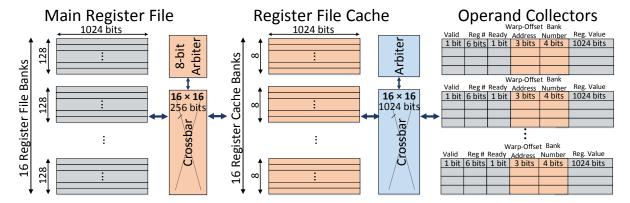

Figure 1 illustrates a conventional GPU register file architecture [105] in a streaming multiprocessor (SM). To accommodate a large number of active threads, a GPU employs a register file of megabytes in size. For example, GP100 (NVIDIA Pascal) has a register file of 14.3 megabytes in total [138]. The register file is heavily banked (16 banks) and it allows concurrent accesses from many threads (up to 512 threads). Each bank stores registers from multiple warps. When the GPU issues an instruction, an operand collector concurrently accesses and gathers data associated with each thread in the issued warp's instruction through an arbiter and a large and wide crossbar, as shown in Figure 1. The warp scheduler arbitrates among *ready* warps (i.e., a warp whose operands are collected) and issues the warp's instruction to the SIMD units.

Fig. 1. Conventional GPU register file architecture.

In this section, we demonstrate the increasing demand for larger register file capacity, analyze shortcomings of prior register caching mechanisms for GPUs, and motivate the case for a design that provides high capacity without significantly increasing power consumption, on-chip die area, or access latency exposed to the GPU core.

### 2.1 Factors that Limit GPU Performance

When a warp encounters a long-latency memory instruction, the GPU selects another *ready* warp to be scheduled for execution, in order to prevent the GPU core from stalling. While the applications with high TLP are more likely to contain more ready warps and are able to hide long-latency stalls more effectively, these applications with high TLP demand a large register file in order to realize their maximum TLP. To illustrate the impact of

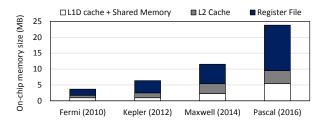

Fig. 2. Capacity of on-chip memory components across generations of NVIDIA GPUs from 2010-2016.

the register file size on an application's TLP, we recompile 35 workloads in CUDA SDK [15], Rodinia [31], and Parboil [173] benchmark suites with the *maxregcount* attribute (i.e., the attribute that enables the use of the maximum number of registers for each GPU function, i.e., 64 and 256 for Fermi and Maxwell respectively) enabled in the NVIDIA GPU compiler, nvcc. Doing so enables us to measure the number of registers applications would require if there were *no* register file size constraints.

Table 1 reports the average and maximum register file capacity needed for our benchmarks to achieve the maximum TLP provided by the two GPU products. This experiment shows that a larger register file would directly translate into a larger number of executing threads, thereby increasing TLP, on average. The table corroborates our intuition that TLP is indeed limited by the number of registers and many applications benefit from compiler optimization when given a larger register file [114, 125, 193]. The results also show that the recent version of the CUDA compiler used for Maxwell employs more aggressive compiler optimization techniques (e.g., loop unrolling) and as such enhances register usage and TLP compared to Fermi.

Table 1. The average and maximum register file capacity required to maximize TLP for 35 workloads in CUDA SDK [15], Rodinia [31], and Parboil [173] benchmark suites in the NVIDIA Fermi and Maxwell architectures.

| GPU                           | Average required   | Maximum required   |  |  |

|-------------------------------|--------------------|--------------------|--|--|

| (baseline register file size) | register file size | register file size |  |  |

| Fermi (128KB)                 | 184KB (1.4×)       | 324KB (2.5×)       |  |  |

| Maxwell (256KB)               | 588KB (2.3×)       | 1504KB (5.9×)      |  |  |

# 2.2 Register File Scalability

While modern GPUs integrate more execution resources with increases in silicon density and memory bandwidth in each chip generation, the register file accounts for an increasingly larger fraction of on-chip storage, as shown in Figure 2. For NVIDIA Pascal [138], more than 60% of the on-chip storage area, amounting to 14.3 MB is dedicated to the register file. GPU register files face the difficult challenge of optimizing latency, bandwidth, and power consumption, while having maximal capacity [1, 49, 50, 59, 65, 69, 70, 98, 103, 107, 108, 115, 159, 160, 184, 186, 187]. Larger register files are slower, take up more silicon area and consume more power. Increasing concurrency by adding more banks exacerbates complexity and power consumption with the addition of a larger crossbar. Prior work attempts to reduce the power consumption of the register file while keeping the register access latency almost unchanged. As a result, the reduction in the power consumption is limited by the access latency of the register file. In this section, we measure the impact of various register file design parameters and configurations on register file access latency and overall GPU throughput.

Table 2 illustrates register file designs with varying parameters, including cell technology, number of banks, bank size, and network topology, relative to a baseline high performance SRAM-based design shown in Configuration

Table 2. Various register file designs with different configurations; all the numbers including number of banks ( $1 \times = 16$ ), bank size ( $1 \times = 16KB$ ), capacity, area, power consumption, capacity per area, capacity per power, and access latency are normalized to the baseline GPU register file with 256KB size and 16 banks.

| Config. | Cell Technology | #Banks | Bank Size | Network      | Cap. | Area  | Power | Cap./Area | Cap./Power | Latency |

|---------|-----------------|--------|-----------|--------------|------|-------|-------|-----------|------------|---------|

| #1      | HP SRAM         | 1×     | 1×        | Crossbar     | 1×   | 1×    | 1×    | 1×        | 1×         | 1×      |

| #2      | HP SRAM         | 1×     | 8×        | Crossbar     | 8×   | 8×    | 8×    | 1×        | 1×         | 1.25×   |

| #3      | HP SRAM         | 8×     | 1×        | F. Butterfly | 8×   | 8×    | 8×    | 1×        | 1×         | 1.5×    |

| #4      | LSTP SRAM       | 1×     | 8×        | Crossbar     | 8×   | 8×    | 3.2×  | 1×        | 2.5×       | 1.6×    |

| #5      | LSTP SRAM       | 8×     | 1×        | F. Butterfly | 8×   | 8×    | 3.2×  | 1×        | 2.5×       | 2.8×    |

| #6      | TFET SRAM       | 8×     | 1×        | F. Butterfly | 8×   | 8×    | 1.05× | 1×        | 7.6×       | 5.3×    |

| #7      | DWM             | 8×     | 1×        | F. Butterfly | 8×   | 0.25× | 0.65× | 32×       | 12×        | 6.3×    |

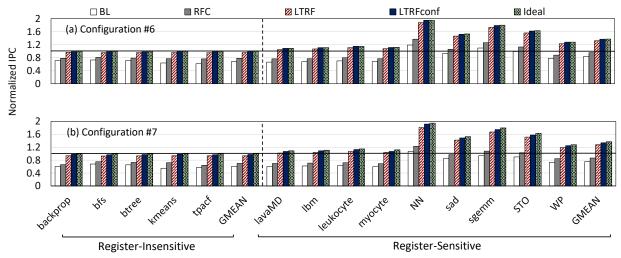

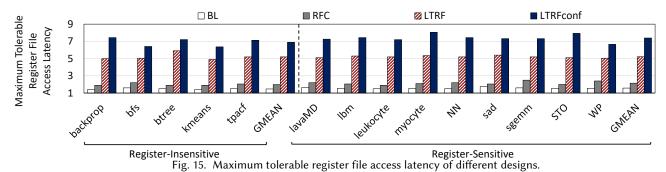

#1. The table also presents results for emerging memory cell technologies that enable a larger trade-off space between area, power and latency. We use high-performance (HP) CMOS, low-standby-power (LSTP) CMOS, tunnel-field-effect transistors (TFET), and domain-wall memory (DWM) for the cell technology [6, 9, 23, 41, 48, 100, 103, 115, 122, 124, 141, 150, 163, 166, 178, 181, 182, 188]. To obtain these results, we first use CACTI [124] (the non-pipelined register file bank models) and NVSim [41] to extract timing, area and power, and then feed them as parameters to GPGPU-Sim [15] to measure the average register file access latencies. The results include queuing delays incurred due to bank conflicts (our system configuration is presented in § 6). Note that we use the flattened butterfly topology [84] to reduce the overhead of the crossbar network when we increase the number of banks by  $8\times$  in our implementations. We make two key observations from Table 2. First, register file designs (such as design #7) that minimize area and power consumption while optimizing for capacity (i.e., bits/area) exhibit higher access latency. Second, while some alternative cell technologies (e.g., DWM [115, 181]) can dramatically improve capacity and power consumption, they incur prohibitively long access latencies (e.g., as long as  $6.3\times$  compared to the baseline register file).

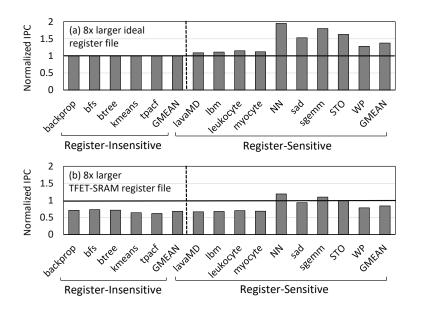

To illustrate the potential benefit of using a large register file, Figure 3(a) plots performance (in IPC) for a high-capacity register file in the ideal case, which has the same latency as the baseline register file from Table2. We categorize our workloads into two groups: *register-insensitive* and *register-sensitive*. Register-insensitive workloads are the ones where the register file size is *not* the bottleneck for higher TLP; i.e., increasing the register file size does *not* improve TLP. We observe that increasing the register file size from 256KB to 2MB *without* increasing the register file access latency, improves IPC by 10%-95% (37%, on average) for register-sensitive workloads. We find that the IPC improvements are due to both more registers per thread and more warps executing in parallel. Figure 3(b) plots performance (in IPC) for a high-capacity register file implemented using TFET-SRAM, normalized to the baseline register file from Table 2.<sup>1</sup> We observe that when real latencies are modeled, much of the gain from higher capacity and TLP is offset by higher latency, and overall performance *reduces* despite the higher register file capacity. We conclude that register file access latency is important for performance and should be kept in check while increasing register file capacity.

# 2.3 Register File Caching

One method to increase the size of the register file while keeping access latency low is to cache registers in a smaller structure, i.e., register file caching. Although there is significant previous work on register file caches for CPUs [21, 37, 39, 73, 121, 135, 139, 165, 176, 196, 197], and vector processors [24, 77, 154], register file caching has *not* been thoroughly investigated in GPU designs. Gebhart et al. [49] are the first to introduce register file caches for GPUs to filter some of the accesses to the main register file and thus reduce the dynamic access energy

<sup>&</sup>lt;sup>1</sup>We choose a 2MB TFET-SRAM register file as it consumes a similar amount of power as our baseline 256KB register file (see Table 2).

Fig. 3. Performance effect of increasing the register file size by  $8\times$ , normalized to the IPC of the baseline architecture with a 256KB register file; (a) the ideal case where the access latency of  $8\times$  larger register file is equal to the access latency of a 256KB register file, and (b) a practical solution for  $8\times$  larger register file using TFET-SRAM, that consumes power almost the same as the a 256KB baseline register files, at the price of 5.3X longer access latencies.

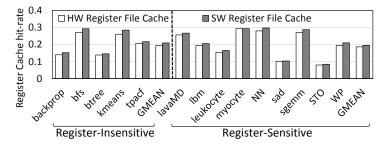

of the main register file. The authors' design works almost the same way as a conventional cache structure and exploits temporal locality. However, as Figure 4 shows, for a 16KB register cache, the register cache hit rate is low: between 8% and 30%.

Fig. 4. Hit rate in hardware [49] and software [50] register file caches.

We find that the hardware register cache hit rate is low due to the following reasons:

- Different warps can displace each other's registers in the cache due to the high warp switching rate in GPUs. This thrashing effect is also observed in SMs' local data caches [10, 12–14, 49, 63, 64, 71, 72, 78, 80, 97, 102, 117, 119, 120, 134, 152, 158, 161, 162, 179, 191?, 192].

- (2) We find that many registers are used to only communicate results between a few instructions. As a result, these registers do *not* have good temporal locality.

(3) There is no notion of "spatial locality" in register accesses (i.e., there is no logical order among different registers).

Follow-up work [50] proposes a software-managed hierarchical register file (SHRF) that aims to reduce data movement between the main register file and the register cache. However, as the main objective is to reduce dynamic energy consumption of the baseline large monolithic register file, the authors [50] aim to reduce the total number of accesses to the main register file, regardless of whether or not those accesses occur during the execution of a warp. In particular, SHRF reduces the extra register file accesses caused by register file cache write-back/reloads, by adding specialized instructions, aided by a new register allocation mechanism, to manage register movement. However, Figure 4 shows that the software approach does *not* significantly improve the hit rate compared to a baseline hardware register cache [49] as it mostly focuses on reducing the number of background (i.e., write-back/reload) register accesses, rather than accesses that are needed by program instructions.

#### 2.4 Summary and Goals

In this work, we leverage two observations we have provided in this section. First, the register file is one of the limiting factors in the scalability of GPUs in terms of TLP. Second, making the register file considerably larger is very difficult without sacrificing either latency or power consumption. Register caching can reduce the register access latency and thus enable aggressive power optimization techniques without degrading GPU performance. However, register caching has *not* been thoroughly studied in the context of GPUs and the existing schemes mainly aim to reduce power consumption, rather than completely hide the main register file access latency. Therefore, these designs are inefficient as they do not offer high register cache hit rates. In fact, they hurt performance if used with considerably slow main register files (see § 7).

In this paper, we aim to architect a *latency-tolerant* hierarchical register file for GPUs that can have very high capacity. Our goal is to 1) enable very high-capacity yet also high-latency main register files, while improving performance, and thus 2) open the design space for many power/area optimization techniques in the main register file that likely increase the register access latency (and thus would otherwise be unacceptable).

# 3 LATENCY-TOLERANT REGISTER FILE

To make the register file very high capacity and at the same time latency-tolerant, we propose a new register file caching mechanism that aims to 1) bring the warps' registers into the register file cache *before* they are accessed by the warps (i.e., register prefetching) and 2) service all register accesses from the register file cache. As a result, the warps see the latency of a fast register cache and *not* the slow main register file. We find that a near-perfect register prefetching mechanism can be implemented based on two key observations. First, the register working-set is known at compile-time as there is no indirection or aliasing in register accesses. Second, long register access latency can be hidden by the execution of other active warps.

LTRF takes advantage of these two observations that enable a new register prefetching scheme. § 3.1 provides an overview of our register prefetching scheme. § 3.2 and § 3.3 provide an overview of the architectural and compiler support required for our software-driven prefetching scheme, respectively.

#### 3.1 Register Prefetching Scheme

We define a prefetch operation to specify which registers should be prefetched from the main register file. A prefetch operation brings the register working-set of a subgraph of the application control flow graph (CFG) into the register cache. The working-set is composed of the registers that, depending on the dynamic control flow, *might be* accessed between two prefetch operations. We call subgraphs of the CFG created by prefetch operations (bounded by prefetch operations) *prefetch subgraphs*. Finding an optimal placement of prefetch operations is not only impossible in polynomial time, but also requires information available only during runtime because

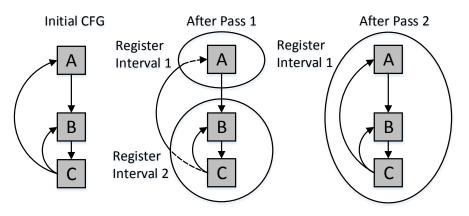

of dynamic warp interleavings. We propose a heuristic algorithm that employs the concept of *intervals* [58], subgraphs of the CFG with a single entry point, which offers compile-time analysis within a reasonable amount of time. We modify the classic interval analysis algorithm, used to find the subgraphs of the CFG with a single entry point, and introduce the concept of *register-intervals* as suitable prefetch subgraphs for prefetching registers. A *register-interval* is a subgraph of the CFG that 1) has a single control flow entry point and 2) requires, at most, a given number of registers.

Our scheme brings the register working-set into the cache at the beginning of each register-interval and *guarantees* that *all* register accesses made inside that register-interval will be serviced from the register file cache. See § 3.2 and 3.3 for more details about the proposed register prefetching scheme.

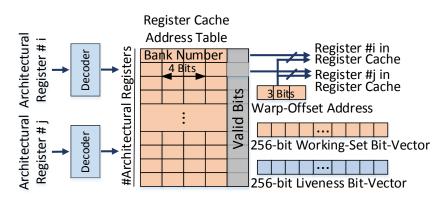

#### 3.2 Architectural Support

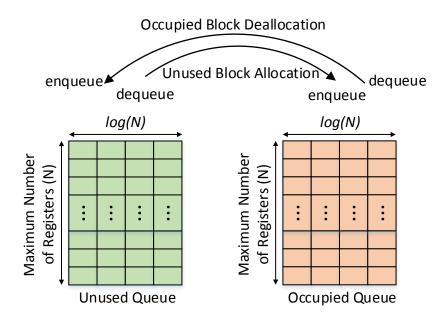

To reduce the register file cache size, we limit the number of active warps that run concurrently and maintain a pool of inactive warps; the inactive warps remain dormant and are not allocated space in the register file cache. Furthermore, we partition our register file cache and allocate each partition to an active warp, thus preventing active warps from contending for register file cache space, and thus from evicting each other's registers. We size the dedicated caching space for each warp according to the maximum number of registers the warp can access throughout the execution of a prefetch subgraph. This parameter also sets an upper bound for the size of a prefetch subgraph working-set. By ensuring no register cache evictions occur during the execution of a prefetch subgraph, we guarantee that register movement happens only with prefetch operations or when a warp becomes active/inactive.

We deploy a two-level warp scheduler, similar to the one used in [49, 133], to schedule execution of active warps. The scheduler issues instructions from active warps in a fair manner (e.g., round-robin). Whenever a warp encounters a long latency operation, such as a data cache miss, it becomes inactive and gets replaced by another one from the active pool. The two-level scheduler enables the use of a smaller register file cache that needs to accommodate only the working-sets of the *active* warps, and a warp's register working-set is swapped in and out of the register file cache as warp becomes active/inactive.

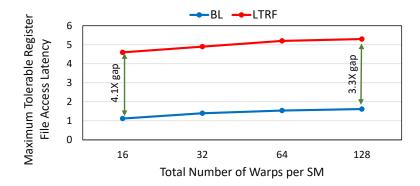

Reducing the number of *active* warps provides two positive benefits: it 1) does *not* limit TLP since inactive warps still maintain live state in the *main* register file, and thus can be quickly activated, 2) can potentially improve performance by reducing the L1 data cache thrashing effect and by preventing *all* warps from stalling at the same time [78, 80, 133, 152, 162]. In LTRF, warp activations are not cost-free as the register working-set of the inactive warp needs to be prefetched before the warp becomes active. Hence, if we cannot hide the warp activation latency, we might negatively affect performance. In § 7.2, we quantitatively show that this is not the case. LTRF requires a small number of active warps to hide the warp activation latency, allowing a GPU to tolerate higher latency accesses to the main register file.<sup>2</sup>

Prefetch operations use bit-vectors to identify the registers that should be cached for each prefetch subgraph, enabling support for various cache sizes. The prefetch bit-vector size is equal to the maximum number of registers the CUDA compiler can allocate to a thread. For example, in the latest CUDA versions, the compiler can allocate up to 256 registers to each thread, requiring a 256-bit vector for each prefetch operation. The instruction fetch unit needs to know in advance when it is going to process a prefetch bit-vector. We consider two approaches. The first embeds an extra bit in each instruction to indicate whether a prefetch bit-vector follows that instruction. Prior work [50] has similar requirements and the authors show that, in general, the cost of embedding the extra bit is negligible. The second approach is to add an explicit instruction that is always followed by the bit-vector.<sup>3</sup>

<sup>&</sup>lt;sup>2</sup>We discuss the design of the main register file and the register cache in detail in the conference version [157].

$<sup>^{3}</sup>$ We show in the conference version [157] that code-size and performance overheads are negligible with either of the approaches.

When a warp becomes inactive, we must keep track of which registers should be written back and refetched once the warp becomes active again. In LTRF, we simply write back and refetch the *entire* register working-set of the active prefetch subgraph.

In order to improve the efficiency of the basic LTRF design, we devise operand-liveness aware LTRF (called LTRF+), which considers the liveness of the registers to save register file cache space. The key idea of LTRF+ is to avoid writing-back/re-fetching dead registers. To this end, each read operand has to be extended with an additional bit, called the *dead operand bit* as defined in [49], which indicates whether the corresponding operand will be dead after the execution of the corresponding instruction. This information can be conservatively known at compile-time, using static liveness analysis. These bits are used to update the liveness bit vector. The liveness bit vector keeps track of the liveness status of all registers at the current point of execution. A register becomes live when it is written to and dead when an instruction indicates it is dead via the dead operand bit. When a warp becomes inactive, LTRF+ writes back only the live registers to the main register file. When a warp becomes active, LTRF+ fetches only the live registers from the main register file. LTRF+ needs to only allocate space for them in the register file cache.

### 3.3 Compiler Support

When a warp reaches the beginning of a *prefetch subgraph*, it is paused until all of its working-set registers are loaded into the register cache. Therefore, prefetch operations may have long latencies that can potentially impose large performance overheads, and hence, they should happen infrequently. In order to address this issue, we introduce *register-intervals* as effective prefetch subgraphs and partition the CFG into register-intervals. A register-interval is a subgraph of the CFG with only two constraints. First, it needs to have only one control flow entry point. Second, the number of registers used in a register-interval should *not* exceed the size of a partition in the register cache.<sup>4</sup> The primary difference between register-intervals and other similar concepts, such as *strands* [50], is that complex control flow structures (e.g., backward branches) are allowed inside a register-interval and they do not cause the termination of the register-interval. By relaxing such constraints, register-intervals provide two main benefits. First, register-intervals can have more static instructions and thus the number of prefetch operations can be minimized. Second, our mechanism aims to fit a loop within a single register-interval in order to increase the dynamic length of the register-intervals.

We employ classic interval analysis methods [58] to form register-intervals. The original interval concept [58], used in classic compiler algorithms, partitions the CFG into smaller disjoint subgraphs, each with exactly one entry point. These intervals are typically used to identify loops and determine if the CFG is reducible. We constrain the formation algorithm to guarantee that the register working-set of each interval can fit into a register file cache partition. As a result, the register-intervals constructed by our algorithm might be smaller than the intervals formed by the original algorithm and may terminate at arbitrary points. Thus, we modified the original algorithm to construct intervals at arbitrary starting points.

Our register-interval formation algorithm is a multi-pass algorithm. Algorithm 1 shows the first pass. The algorithm tries to compose register-intervals with as many basic blocks as possible. Therefore, it initializes the first register-interval with the entry basic block (line 8) and iteratively attempts to add subsequent blocks to it (lines 9-25). A candidate block must satisfy two conditions to be successfully added: 1) it must be entered only from the current register-interval, 2) the register file cache space allocated for a warp must be enough to house both the active registers already in the register-interval and the ones added by the new block. The algorithm stops when it cannot find any basic blocks that meet these conditions (line 13). After it finishes the first register-interval, it creates new register-intervals out of all the basic blocks with incoming edges from that

<sup>&</sup>lt;sup>4</sup>We provide dedicated space for each active warp in the register file cache.

Algorithm 1 Register-Interval Formation: Pass 1.

### Input: Application Control Flow Graph (CFG) Output: Register-Interval CFG

#### 1: Initialize:

- 2: **for each** basic block : BB **do**

- 3: BB.input\_list ← empty() // List of all register in the register cache at the begining of BB

- 4: BB.register-interval  $\leftarrow$  Unknown

- 5: end for

- 6: Working-Set  $\leftarrow$  empty()

- 7: entry\_block.register-interval ← new register-interval() // Each CFG has an entry basic block

- 8: Working-Set.insert(entry\_block)

- 9: while (!Working-Set.empty()) do

- 10: BB  $\leftarrow$  a basic block from Working-Set

- 11: TRAVERSE(BB)

- 12:  $i \leftarrow BB.register-interval$

- 13: while (∃ basic block h for which h.register-interval==Unknown & all of h predecessors belong to i & union(output\_list of all S predecessors).size()≤N) // N is the maximum number of registers allowed in the register-interval (i.e., size of a partition in the register file cache) do

- 14: h.register-interval  $\leftarrow$  i

- 15: h.input\_list ← union(output\_list of all h predecessors)

- 16: TRAVERSE(h)

- 17: end while

- 18: **for each**  $S \in i.successors()$  **do**

- 19: **if** (S.register-interval==Unknown) **then**

- 20: S.register-interval  $\leftarrow$  new register-interval()

- 21: S.input\_list  $\leftarrow$  empty()

- 22: Working-Set.insert(S)

- 23: end if

- 24: end for

- 25: end while

#### 26: **procedure** TRAVERSE(BB)

- 27: register\_list ← BB.input\_list

- 28: **for each** instruction in BB **do**

- 29: update register\_list

- 30: **if** (register\_list.size()>N) **then**

- 31: cut BB and introduce a new basic block : BB1

- 32: BB1.register-interval  $\leftarrow$  new register-interval()

- 33: BB1.input\_list  $\leftarrow$  empty()

- 34: Working-Set.insert(BB1)

- 35: BB.output\_list ← register\_list // List of all registers in the register file cache at the end of BB

- 36: exit

- 37: end if

- 38: end for

- 39: end procedure

register-interval (lines 18-24). When a register-interval is completely formed, all of the basic blocks that have incoming edges from that register-interval become new register-intervals' headers. If a single basic block's active registers do *not* fit into the remaining register file cache space for that register-interval, the basic block is split across two or more register-intervals (lines 30-37). We also split the basic blocks at function calls (each function call becomes a separate register-interval). Algorithm 1 is not multi-pass and ends when all basic blocks of the control flow graph are assigned to register-intervals. After executing Algorithm 1, the CFG is transformed into a Register-Interval CFG where the nodes represent the register-intervals rather than basic blocks.

| Algorithm 2 Register-Interval Formation: Pass 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input: Register-Interval CFG<br>Output: Reduced Register-Interval CFG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1: Initialize:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2: for each register-interval : i do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $3:$ i.register-interval $\leftarrow$ Unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4: end for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5: Working-Set $\leftarrow$ empty()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6: entry_register-interval.next_level_register-interval $\leftarrow$ new next_level_register-interval()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7: Working-Set.insert(entry register-interval)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8: while (!Working-Set.empty()) do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9: i ← a register-interval from Working-Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10: ii ← i.next_level_register-interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11: $ii.register_list \leftarrow i.register_list$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12: while ( $\exists$ register-interval h for which h.next_level_register-interval==Unknown & all of h predecessors belong to ii of the second secon |

| $union(register_list of all h predecessors).size() \le N) // N$ is the maximum number of registers allowed in the register-interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (i.e., size of a partition in the register file cache) <b>do</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13: h.next_level_register-interval ← ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14: ii.register_list ← union(ii.register_list & h.register_list)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

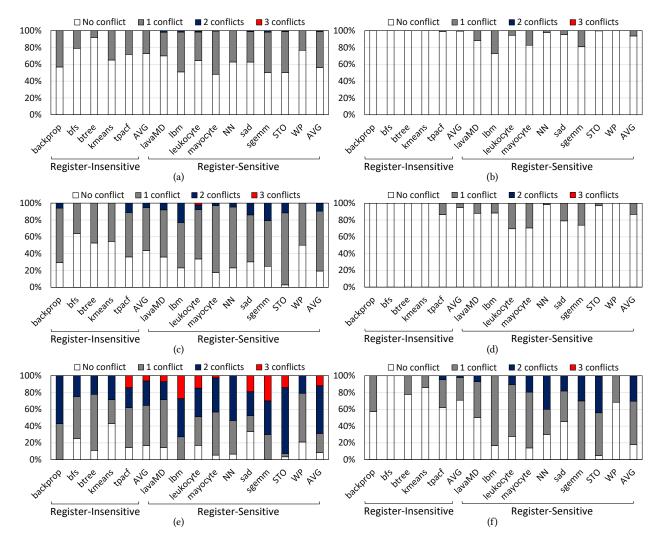

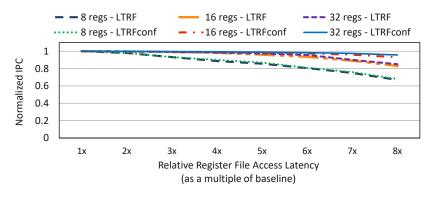

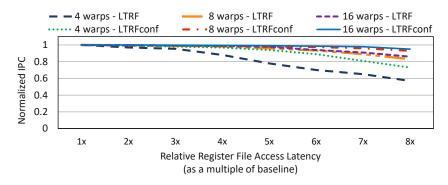

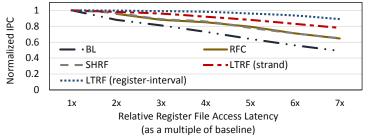

| 15: end while                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |