# Memory Systems and Memory-Centric Computing Systems Lec 3 Topic 2: Memory Reliability and Security

Prof. Onur Mutlu

omutlu@gmail.com

https://people.inf.ethz.ch/omutlu

11 July 2018

HiPEAC ACACES Summer School 2018

**Carnegie Mellon**

#### What Will You Learn in This Course?

- Memory Systems and Memory-Centric Computing Systems

- □ July 9-13, 2018

- Topic 1: Main Memory Trends and Basics

- Topic 2: Memory Reliability & Security: RowHammer and Beyond

- Topic 3: In-memory Computation

- Topic 4: Low-Latency and Low-Energy Memory

- Topic 5 (unlikely): Enabling and Exploiting Non-Volatile Memory

- Topic 6 (unlikely): Flash Memory and SSD Scaling

- Major Overview Reading:

- Mutlu and Subramaniam, "Research Problems and Opportunities in Memory Systems," SUPERFRI 2014.

# Security Implications

It's like breaking into an apartment by repeatedly slamming a neighbor's door until the vibrations open the door you were after

# Understanding RowHammer

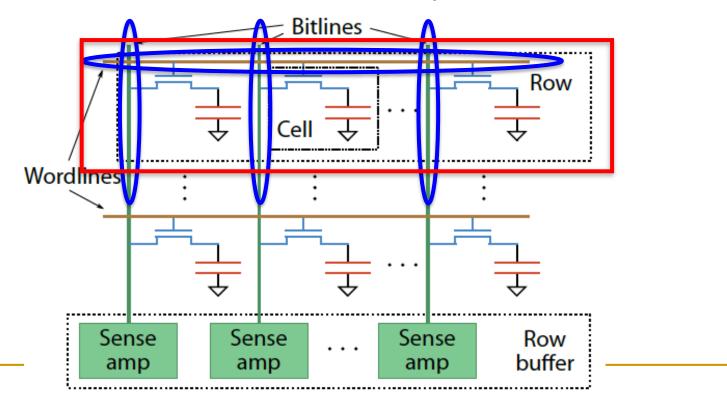

## Root Causes of Disturbance Errors

- Cause 1: Electromagnetic coupling

- Toggling the wordline voltage briefly increases the voltage of adjacent wordlines

- Slightly opens adjacent rows → Charge leakage

- Cause 2: Conductive bridges

- Cause 3: Hot-carrier injection

Confirmed by at least one manufacturer

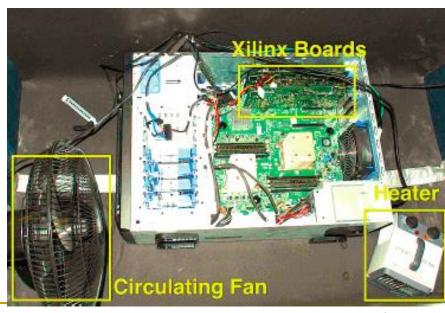

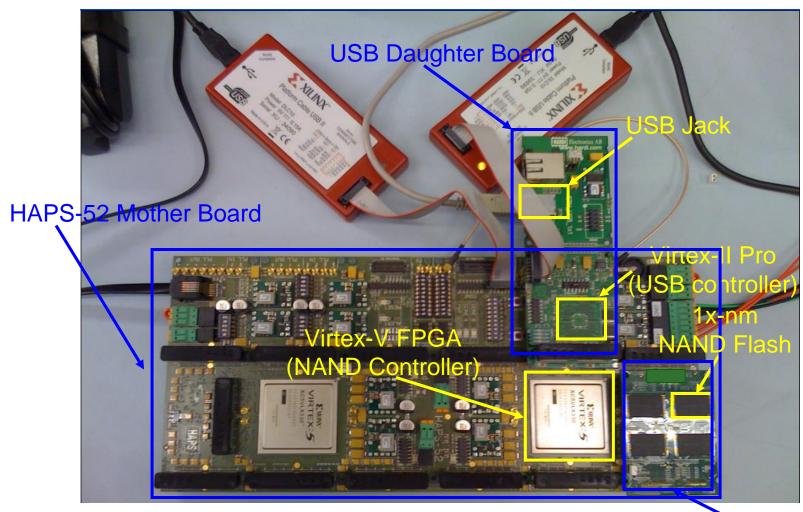

# Experimental DRAM Testing Infrastructure

Flipping Bits in Memory Without Accessing

Them: An Experimental Study of DRAM

Disturbance Errors (Kim et al., ISCA 2014)

Adaptive-Latency DRAM: Optimizing DRAM

Timing for the Common-Case (Lee et al.,

HPCA 2015)

AVATAR: A Variable-Retention-Time (VRT)

Aware Refresh for DRAM Systems (Qureshi et al., DSN 2015)

An Experimental Study of Data Retention

Behavior in Modern DRAM Devices:

Implications for Retention Time Profiling

Mechanisms (Liu et al., ISCA 2013)

The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study (Khan et al., SIGMETRICS 2014)

# Experimental DRAM Testing Infrastructure

#### RowHammer Characterization Results

- 1. Most Modules Are at Risk

- 2. Errors vs. Vintage

- 3. Error = Charge Loss

- 4. Adjacency: Aggressor & Victim

- 5. Sensitivity Studies

- 6. Other Results in Paper

- 7. Solution Space

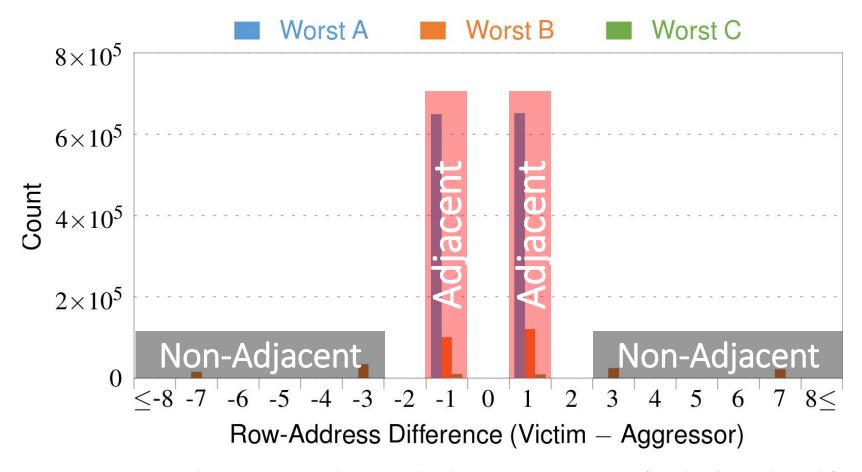

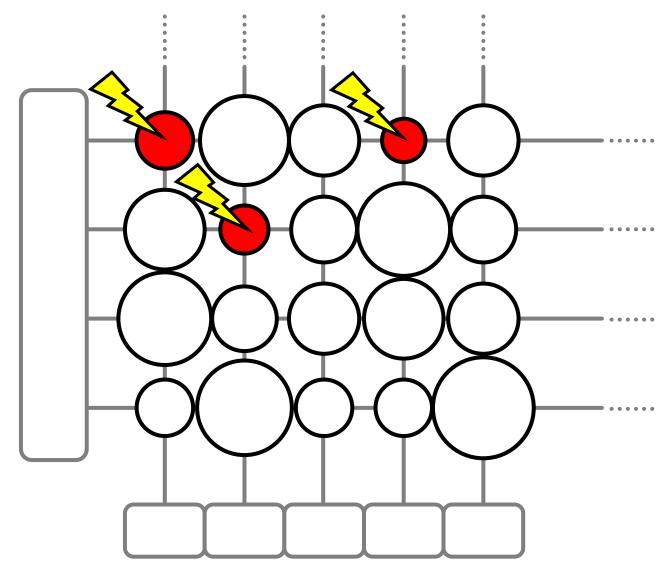

# 4. Adjacency: Aggressor & Victim

Note: For three modules with the most errors (only first bank)

Most aggressors & victims are adjacent

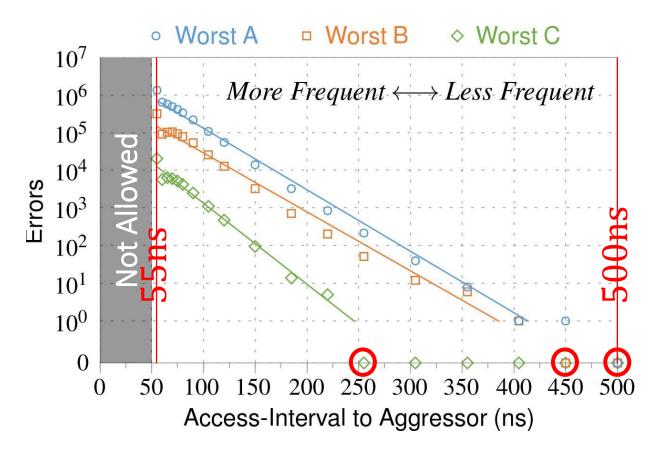

# Access Interval (Aggressor)

Note: For three modules with the most errors (only first bank)

Less frequent accesses → Fewer errors

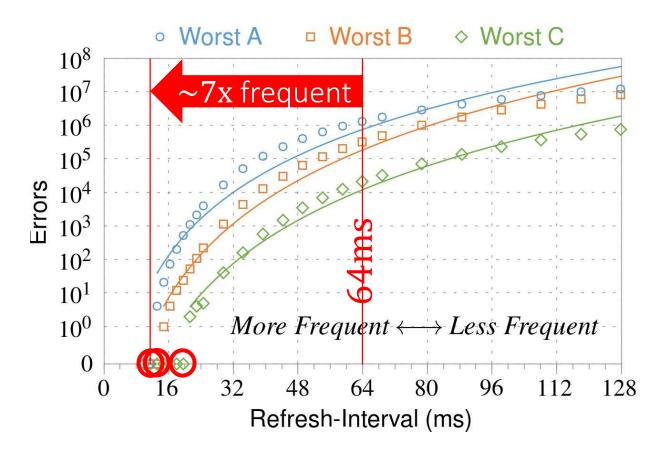

# 2 Refresh Interval

Note: Using three modules with the most errors (only first bank)

*More frequent refreshes*  $\rightarrow$  *Fewer errors*

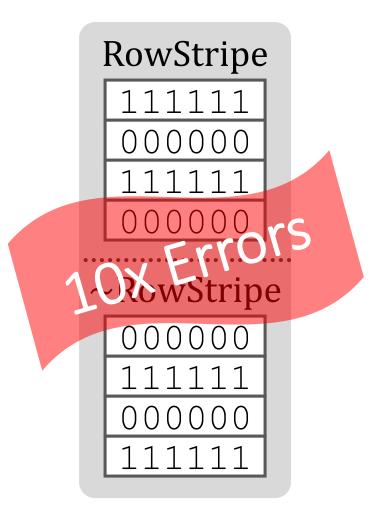

# B Data Pattern

# Solid 11111 ~Solid 00000 00000 00000 00000

Errors affected by data stored in other cells

# 6. Other Results (in Paper)

- Victim Cells ≠ Weak Cells (i.e., leaky cells)

- Almost no overlap between them

- Errors not strongly affected by temperature

- Default temperature: 50°C

- At 30°C and 70°C, number of errors changes <15%</li>

- Errors are repeatable

- Across ten iterations of testing, >70% of victim cells had errors in every iteration

# 6. Other Results (in Paper) cont'd

- As many as 4 errors per cache-line

- Simple ECC (e.g., SECDED) cannot prevent all errors

- Number of cells & rows affected by aggressor

- Victims cells per aggressor: ≤110

- Victims rows per aggressor: ≤9

- Cells affected by two aggressors on either side

- Very small fraction of victim cells (<100) have an error when either one of the aggressors is toggled

# More on RowHammer Analysis

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

"Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors"

Proceedings of the 41st International Symposium on Computer Architecture (ISCA), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data]

# Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly\* Jeremie Kim<sup>1</sup> Chris Fallin\* Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup>

Carnegie Mellon University <sup>2</sup>Intel Labs

SAFARI

# Retrospective on RowHammer & Future

Onur Mutlu,

"The RowHammer Problem and Other Issues We May Face as **Memory Becomes Denser**"

Invited Paper in Proceedings of the Design, Automation, and Test in Europe Conference (DATE), Lausanne, Switzerland, March 2017. [Slides (pptx) (pdf)]

#### The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser

Onur Mutlu ETH Zürich onur.mutlu@inf.ethz.ch https://people.inf.ethz.ch/omutlu

# Challenge and Opportunity for Future

# Fundamentally Secure, Reliable, Safe Computing Architectures

# Future Memory Reliability/Security Challenges

# Future of Main Memory

■ DRAM is becoming less reliable → more vulnerable

# Large-Scale Failure Analysis of DRAM Chips

- Analysis and modeling of memory errors found in all of Facebook's server fleet

- Justin Meza, Qiang Wu, Sanjeev Kumar, and Onur Mutlu,

"Revisiting Memory Errors in Large-Scale Production Data

Centers: Analysis and Modeling of New Trends from the Field"

Proceedings of the 45th Annual IEEE/IFIP International Conference on

Dependable Systems and Networks (DSN), Rio de Janeiro, Brazil, June

2015.

[Slides (pptx) (pdf)] [DRAM Error Model]

#### Revisiting Memory Errors in Large-Scale Production Data Centers: Analysis and Modeling of New Trends from the Field

Justin Meza Qiang Wu\* Sanjeev Kumar\* Onur Mutlu Carnegie Mellon University \* Facebook, Inc.

SAFARI

# DRAM Reliability Reducing

Chip density (Gb)

# Aside: SSD Error Analysis in the Field

- First large-scale field study of flash memory errors

- Justin Meza, Qiang Wu, Sanjeev Kumar, and Onur Mutlu,

"A Large-Scale Study of Flash Memory Errors in the Field"

Proceedings of the <u>ACM International Conference on</u>

<u>Measurement and Modeling of Computer Systems</u>

(SIGMETRICS), Portland, OR, June 2015.

[Slides (pptx) (pdf)] [Coverage at ZDNet]

#### A Large-Scale Study of Flash Memory Failures in the Field

Justin Meza

Carnegie Mellon University

meza@cmu.edu

Qiang Wu Facebook, Inc. qwu@fb.com Sanjeev Kumar Facebook, Inc. skumar@fb.com Onur Mutlu Carnegie Mellon University onur@cmu.edu

# Future of Main Memory

- DRAM is becoming less reliable → more vulnerable

- Due to difficulties in DRAM scaling, other problems may also appear (or they may be going unnoticed)

- Some errors may already be slipping into the field

- Read disturb errors (Rowhammer)

- Retention errors

- Read errors, write errors

- ...

- These errors can also pose security vulnerabilities

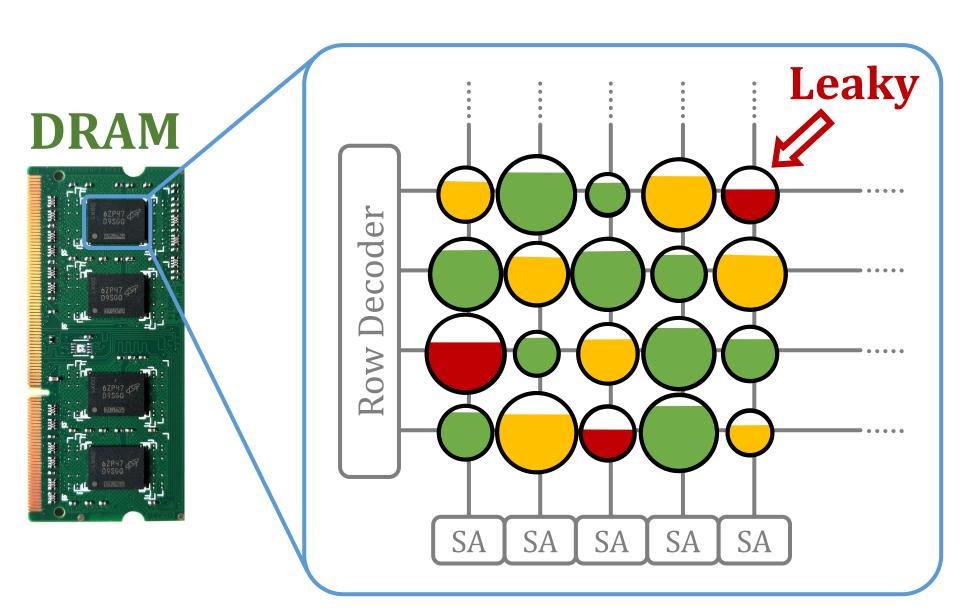

#### DRAM Data Retention Time Failures

Determining the data retention time of a cell/row is getting more difficult

Retention failures may already be slipping into the field

# Analysis of Data Retention Failures [ISCA'13]

Jamie Liu, Ben Jaiyen, Yoongu Kim, Chris Wilkerson, and Onur Mutlu, "An Experimental Study of Data Retention Behavior in Modern DRAM **Devices: Implications for Retention Time Profiling Mechanisms**" Proceedings of the 40th International Symposium on Computer Architecture (ISCA), Tel-Aviv, Israel, June 2013. Slides (ppt) Slides (pdf)

#### An Experimental Study of Data Retention Behavior in **Modern DRAM Devices:** Implications for Retention Time Profiling Mechanisms

Jamie Liu\* 5000 Forbes Ave. Pittsburgh, PA 15213 jamiel@alumni.cmu.edu

Ben Jaiyen<sup>\*</sup> Carnegie Mellon University Carnegie Mellon University 5000 Forbes Ave. Pittsburgh, PA 15213 bjaiyen@alumni.cmu.edu

Yoongu Kim Carnegie Mellon University 5000 Forbes Ave. Pittsburgh, PA 15213 yoonguk@ece.cmu.edu

Chris Wilkerson Intel Corporation 2200 Mission College Blvd. Santa Clara, CA 95054 chris.wilkerson@intel.com

Onur Mutlu Carnegie Mellon University 5000 Forbes Ave. Pittsburgh, PA 15213 onur@cmu.edu

# Two Challenges to Retention Time Profiling

Data Pattern Dependence (DPD) of retention time

Variable Retention Time (VRT) phenomenon

# Two Challenges to Retention Time Profiling

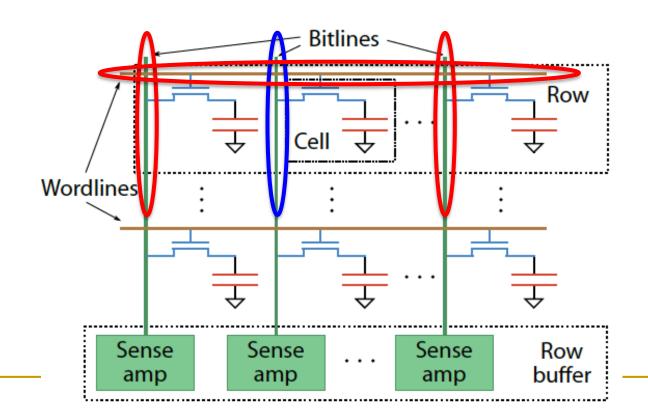

- Challenge 1: Data Pattern Dependence (DPD)

- Retention time of a DRAM cell depends on its value and the values of cells nearby it

- When a row is activated, all bitlines are perturbed simultaneously

SAFARI

# Data Pattern Dependence

- Electrical noise on the bitline affects reliable sensing of a DRAM cell

- The magnitude of this noise is affected by values of nearby cells via

- □ Bitline-bitline coupling → electrical coupling between adjacent bitlines

- □ Bitline-wordline coupling → electrical coupling between each bitline and the activated wordline

SAFARI

# Data Pattern Dependence

- Electrical noise on the bitline affects reliable sensing of a DRAM cell

- The magnitude of this noise is affected by values of nearby cells via

- □ Bitline-bitline coupling → electrical coupling between adjacent bitlines

- □ Bitline-wordline coupling → electrical coupling between each bitline and the activated wordline

- Retention time of a cell depends on data patterns stored in nearby cells

- → need to find the worst data pattern to find worst-case retention time

- → this pattern is location dependent

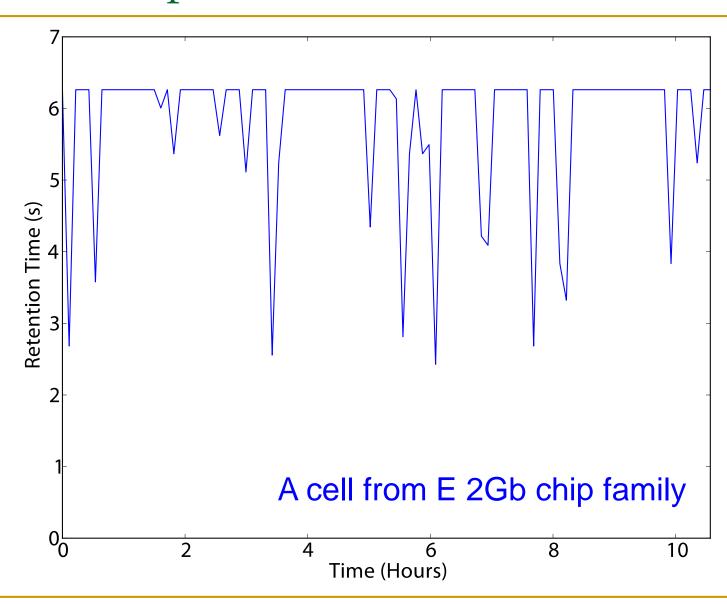

# Two Challenges to Retention Time Profiling

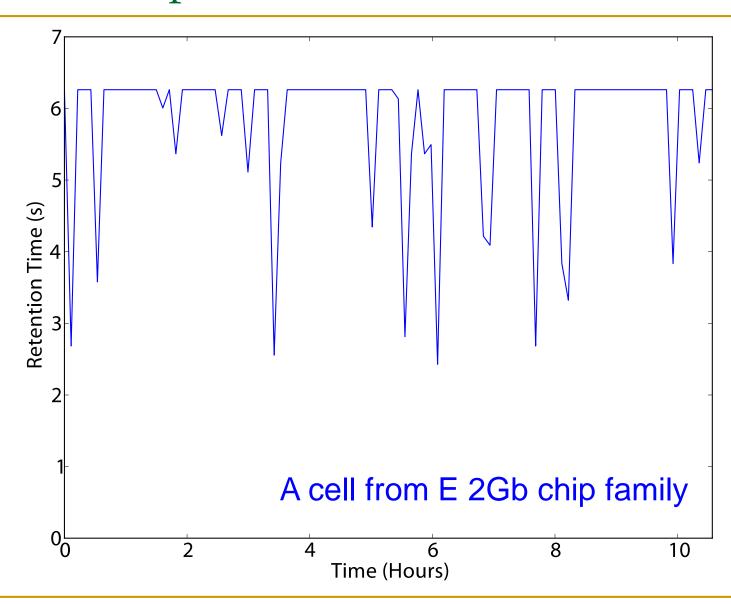

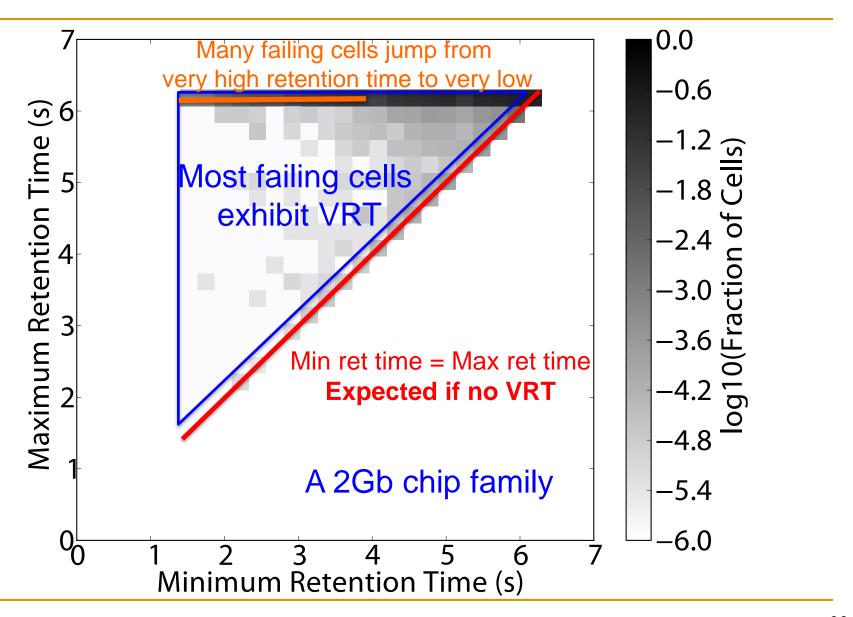

- Challenge 2: Variable Retention Time (VRT)

- Retention time of a DRAM cell changes randomly over time

- a cell alternates between multiple retention time states

- Leakage current of a cell changes sporadically due to a charge trap in the gate oxide of the DRAM cell access transistor

- When the trap becomes occupied, charge leaks more readily from the transistor's drain, leading to a short retention time

- Called Trap-Assisted Gate-Induced Drain Leakage

- □ This process appears to be a random process [<del>Kim+ IEEE TED'11</del>]

- Worst-case retention time depends on a random process

→ need to find the worst case despite this

3(

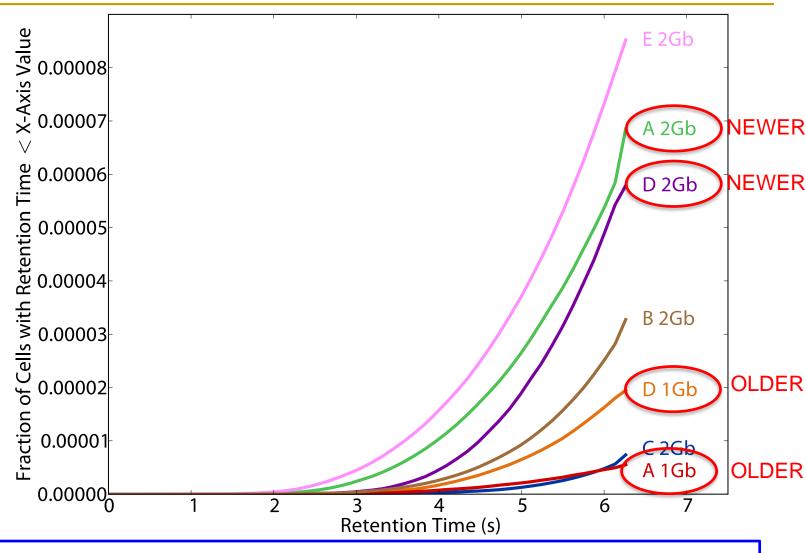

#### Modern DRAM Retention Time Distribution

Newer device families have more weak cells than older ones Likely a result of technology scaling

# An Example VRT Cell

#### Variable Retention Time

## More on Data Retention Failures [ISCA'13]

Jamie Liu, Ben Jaiyen, Yoongu Kim, Chris Wilkerson, and Onur Mutlu, "An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms" Proceedings of the 40th International Symposium on Computer Architecture (ISCA), Tel-Aviv, Israel, June 2013. Slides (ppt) Slides (pdf)

# An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms

Jamie Liu\*

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

jamiel@alumni.cmu.edu

Ben Jaiyen Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

bjaiyen@alumni.cmu.edu

Yoongu Kim

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

yoonguk@ece.cmu.edu

Chris Wilkerson

Intel Corporation

2200 Mission College Blvd.

Santa Clara, CA 95054

chris.wilkerson@intel.com

Onur Mutlu

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

onur@cmu.edu

# Industry Is Writing Papers About It, Too

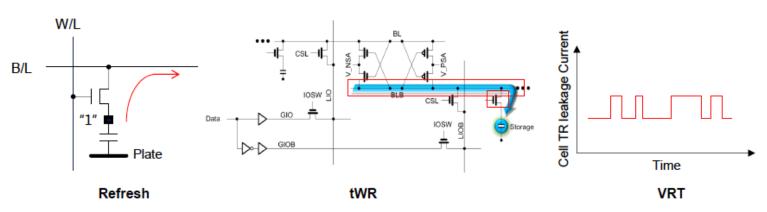

#### DRAM Process Scaling Challenges

#### Refresh

- Difficult to build high-aspect ratio cell capacitors decreasing cell capacitance

- · Leakage current of cell access transistors increasing

#### tWR

- Contact resistance between the cell capacitor and access transistor increasing

- · On-current of the cell access transistor decreasing

- Bit-line resistance increasing

#### VRT

Occurring more frequently with cell capacitance decreasing

# Industry Is Writing Papers About It, Too

#### **DRAM Process Scaling Challenges**

#### Refresh

Difficult to build high-aspect ratio cell capacitors decreasing cell capacitance

THE MEMORY FORUM 2014

# Co-Architecting Controllers and DRAM to Enhance DRAM Process Scaling

Uksong Kang, Hak-soo Yu, Churoo Park, \*Hongzhong Zheng, \*\*John Halbert, \*\*Kuljit Bains, SeongJin Jang, and Joo Sun Choi

Samsung Electronics, Hwasung, Korea / \*Samsung Electronics, San Jose / \*\*Intel

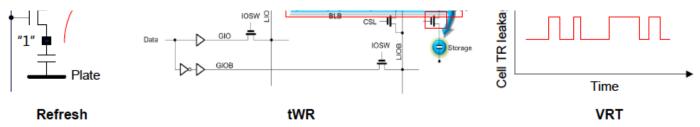

### Refresh Overhead: Performance

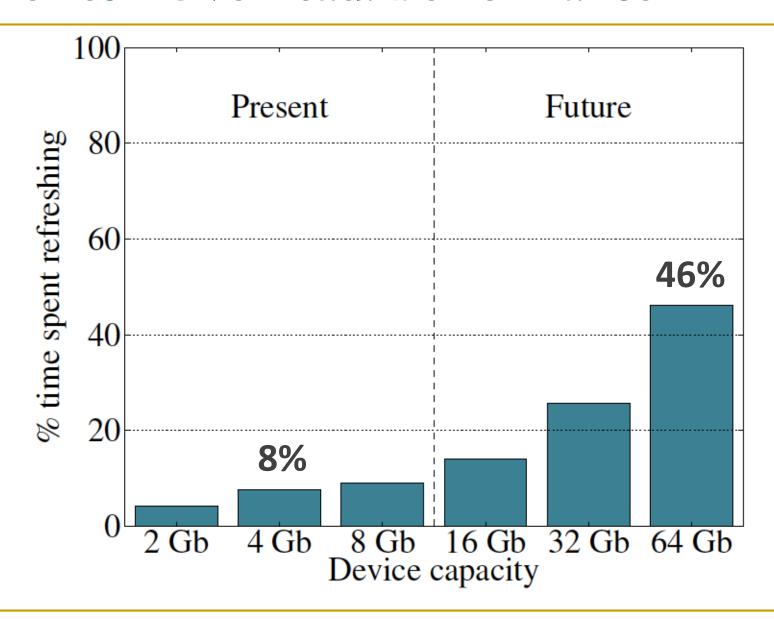

### Refresh Overhead: Energy

#### Retention Time Profile of DRAM

64-128ms

>256ms

128-256ms

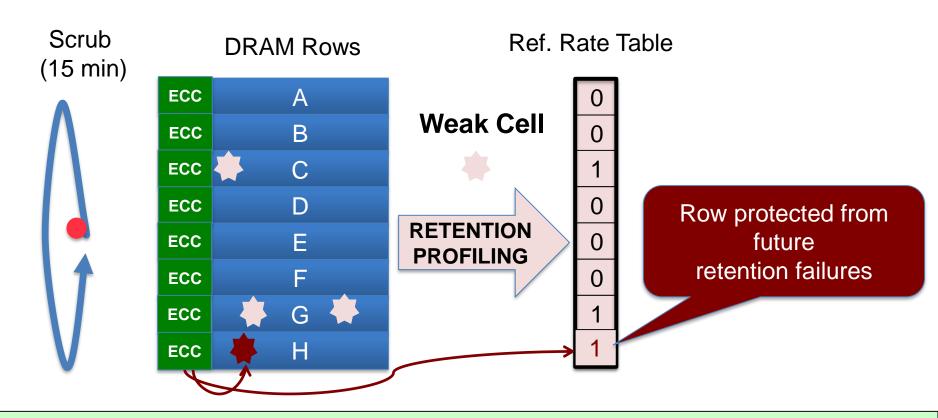

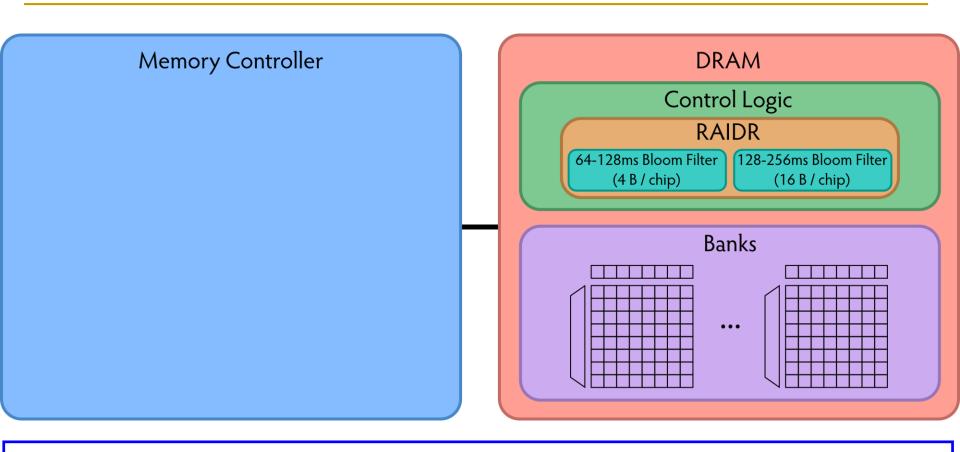

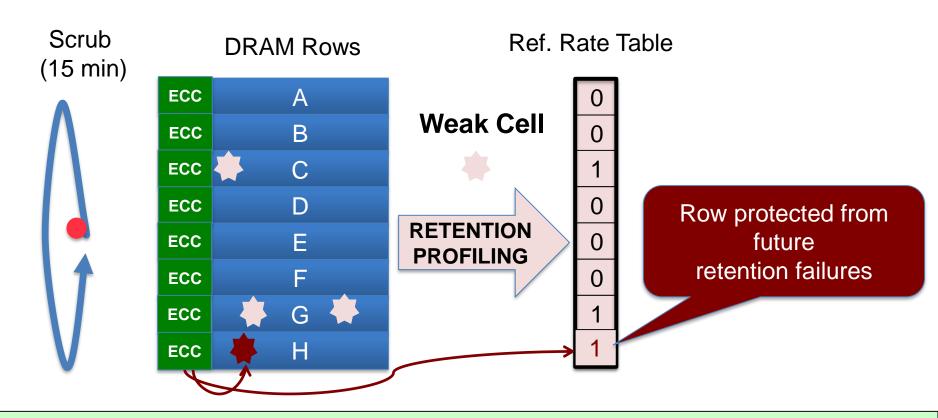

### RAIDR: Eliminating Unnecessary Refreshes

Observation: Most DRAM rows can be refreshed much less often

without losing data [Kim+, EDL'09][Liu+ ISCA'13]

Key idea: Refresh rows containing weak cells more frequently, other rows less frequently

2. Binning: Store rows into bins by retention time in memory controller Efficient storage with Bloom Filters (only 1.25KB for 32GB memory)

Refreshing: Memory conuclidation ifferent rates

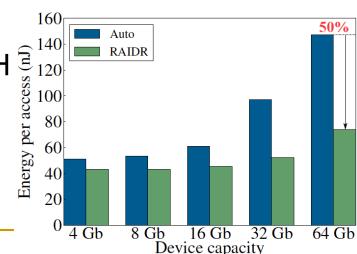

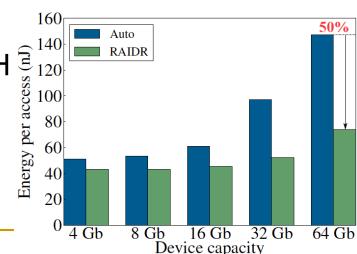

Results: 8-core, 32GB, SPEC, TPC-C, TPC-H

74 6% refresh reduction @ 1.25KB storage

74 6% dynamic/idle power reduction

74 6% refresh reduction @ 1.25KB storage 3. Refreshing: Memory controller refreshes rows in different bins at

- Benefits increase with DRAM capacity

$\approx 1000$  cells @ 256 ms

$\approx 30$  cells @ 128 ms

$^{10}_{2}^{60}$  32 GB DRAM

### More on RAIDR: Perf+Energy Perspective

Jamie Liu, Ben Jaiyen, Richard Veras, and Onur Mutlu, "RAIDR: Retention-Aware Intelligent DRAM Refresh" Proceedings of the <u>39th International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2012. <u>Slides (pdf)</u>

### RAIDR: Retention-Aware Intelligent DRAM Refresh

Jamie Liu Ben Jaiyen Richard Veras Onur Mutlu Carnegie Mellon University

### Finding DRAM Retention Failures

- How can we reliably find the retention time of all DRAM cells?

- Goals: so that we can

- Make DRAM reliable and secure

- Make techniques like RAIDR work

- → improve performance and energy

### Mitigation of Retention Issues sigmetrics'14]

Samira Khan, Donghyuk Lee, Yoongu Kim, Alaa Alameldeen, Chris Wilkerson, and Onur Mutlu,

"The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study"

Proceedings of the <u>ACM International Conference on Measurement and</u> Modeling of Computer Systems (SIGMETRICS), Austin, TX, June 2014. [Slides (pptx) (pdf)] [Poster (pptx) (pdf)] [Full data sets]

### The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study

Samira Khan⁺∗ samirakhan@cmu.edu

Donghyuk Lee<sup>†</sup> donghyuk1@cmu.edu

Yoongu Kim<sup>†</sup> yoongukim@cmu.edu

Alaa R. Alameldeen\* alaa.r.alameldeen@intel.com chris.wilkerson@intel.com

Chris Wilkerson\*

Onur Mutlu<sup>†</sup> onur@cmu.edu

<sup>†</sup>Carnegie Mellon University

\*Intel Labs

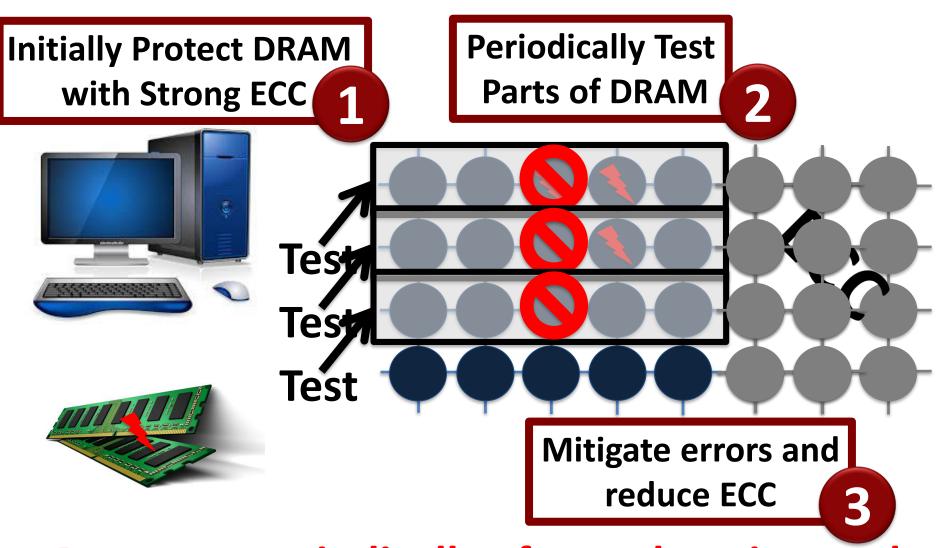

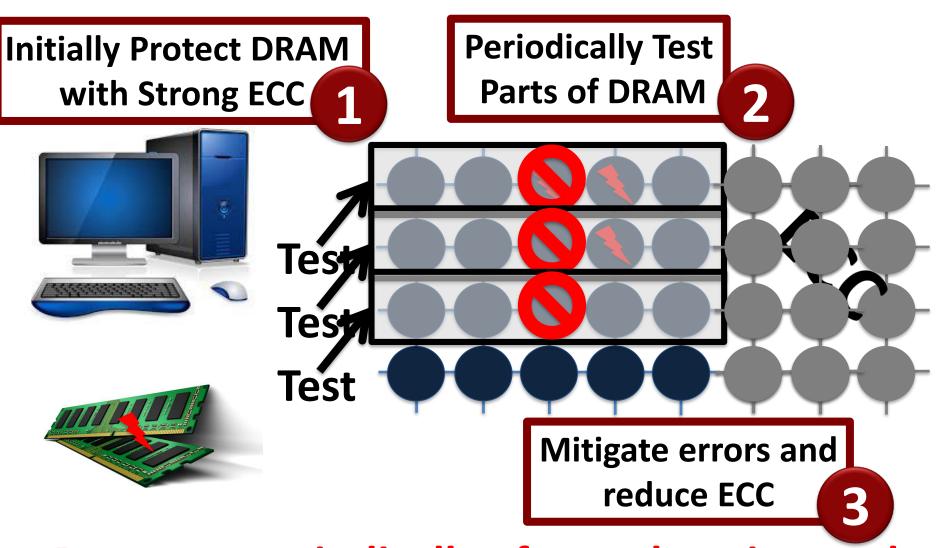

### **Towards an Online Profiling System**

### **Key Observations:**

- Testing alone cannot detect all possible failures

- Combination of ECC and other mitigation techniques is much more effective

- But degrades performance

- Testing can help to reduce the ECC strength

- Even when starting with a higher strength ECC

### **Towards an Online Profiling System**

Run tests periodically after a short interval at smaller regions of memory

### Handling Variable Retention Time [DSN'15]

Moinuddin Qureshi, Dae Hyun Kim, Samira Khan, Prashant Nair, and Onur Mutlu,

"AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM

Systems"

Proceedings of the <u>45th Annual IEEE/IFIP International Conference on</u>

<u>Dependable Systems and Networks</u> (**DSN**), Rio de Janeiro, Brazil, June 2015.

[Slides (pptx) (pdf)]

# AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems

Moinuddin K. Qureshi<sup>†</sup> Dae-Hyun Kim<sup>†</sup>

<sup>†</sup>Georgia Institute of Technology

{moin, dhkim, pnair6}@ece.gatech.edu

Samira Khan‡

Prashant J. Nair<sup>†</sup> Onur Mutlu<sup>‡</sup>

<sup>‡</sup>Carnegie Mellon University

{samirakhan, onur}@cmu.edu

46

#### **AVATAR**

Insight: Avoid retention failures → Upgrade row on ECC error Observation: Rate of VRT >> Rate of soft error (50x-2500x)

**AVATAR** mitigates VRT by increasing refresh rate on error

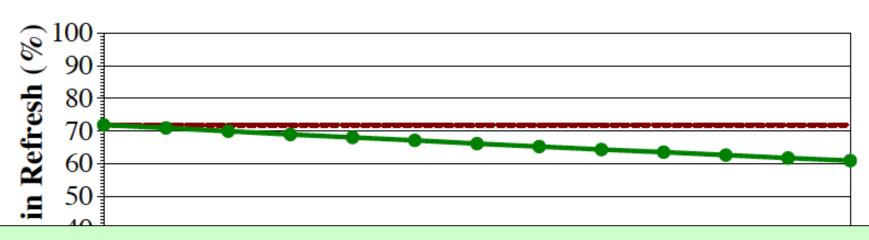

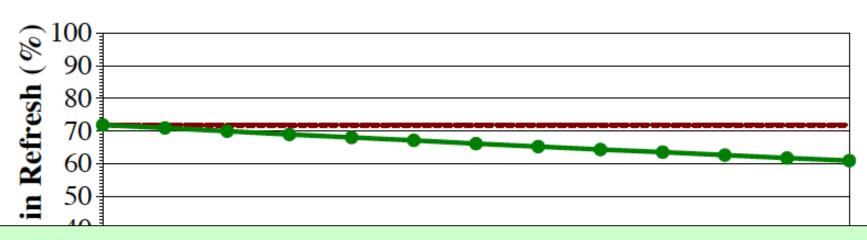

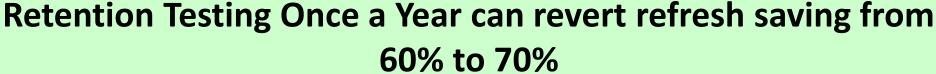

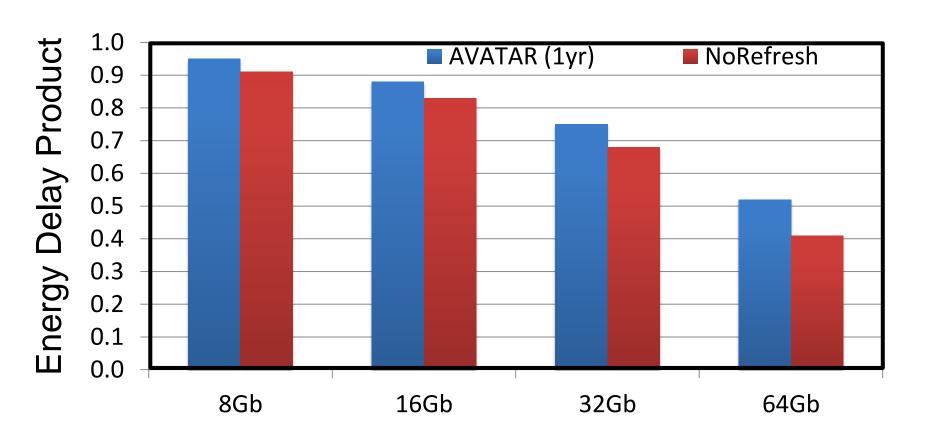

#### **RESULTS: REFRESH SAVINGS**

Retention Testing Once a Year can revert refresh saving from 60% to 70%

AVATAR reduces refresh by 60%-70%, similar to multi rate refresh but with VRT tolerance

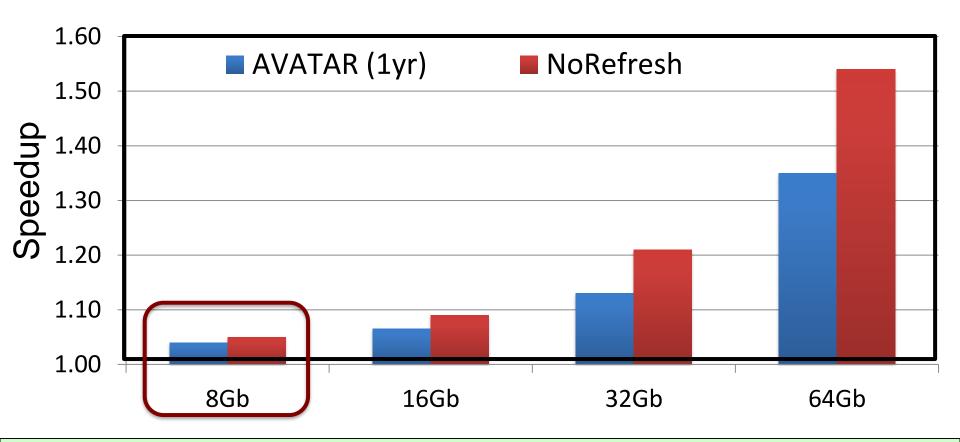

#### **SPEEDUP**

AVATAR gets 2/3<sup>rd</sup> the performance of NoRefresh. More gains at higher capacity nodes

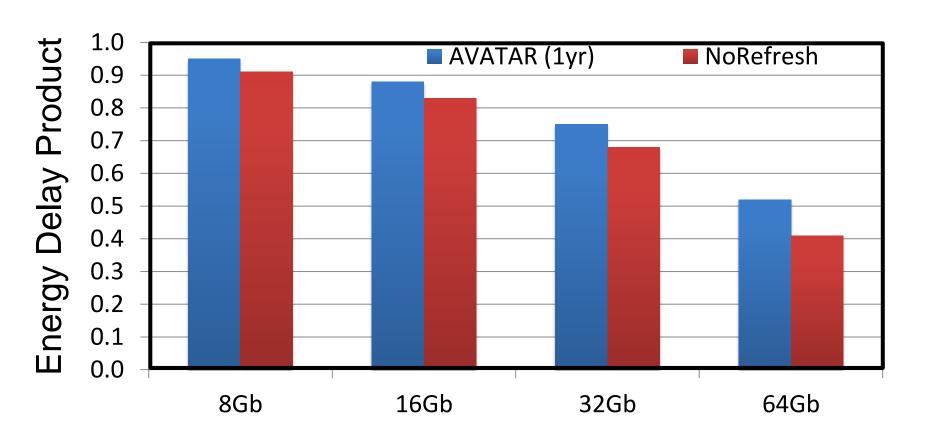

#### **ENERGY DELAY PRODUCT**

# AVATAR reduces EDP, Significant reduction at higher capacity nodes

### Handling Data-Dependent Failures [DSN'16]

Samira Khan, Donghyuk Lee, and Onur Mutlu,

"PARBOR: An Efficient System-Level Technique to Detect Data-Dependent Failures in DRAM"

Proceedings of the 45th Annual IEEE/IEIP International Conference on

Proceedings of the <u>45th Annual IEEE/IFIP International Conference on</u>

<u>Dependable Systems and Networks</u> (**DSN**), Toulouse, France, June 2016.

[<u>Slides (pptx) (pdf)</u>]

# PARBOR: An Efficient System-Level Technique to Detect Data-Dependent Failures in DRAM

Samira Khan\* Donghyuk Lee<sup>†‡</sup> Onur Mutlu<sup>\*†</sup>

\*University of Virginia <sup>†</sup>Carnegie Mellon University <sup>‡</sup>Nvidia \*ETH Zürich

51

### Handling Data-Dependent Failures [MICRO'17]

Samira Khan, Chris Wilkerson, Zhe Wang, Alaa R. Alameldeen, Donghyuk Lee, and Onur Mutlu,

<u>"Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content"</u>

Proceedings of the <u>50th International Symposium on Microarchitecture</u> (**MICRO**), Boston, MA, USA, October 2017.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Poster (pptx) (pdf)]

# Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content

Samira Khan\* Chris Wilkerson<sup>†</sup> Zhe Wang<sup>†</sup> Alaa R. Alameldeen<sup>†</sup> Donghyuk Lee<sup>‡</sup> Onur Mutlu\*

\*University of Virginia <sup>†</sup>Intel Labs <sup>‡</sup>Nvidia Research \*ETH Zürich

SAFARI 52

### Handling Both DPD and VRT [ISCA'17]

- Minesh Patel, Jeremie S. Kim, and Onur Mutlu,

"The Reach Profiler (REAPER): Enabling the Mitigation of DRAM

Retention Failures via Profiling at Aggressive Conditions"

Proceedings of the 44th International Symposium on Computer

Architecture (ISCA), Toronto, Canada, June 2017.

[Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

- First experimental analysis of (mobile) LPDDR4 chips

- Analyzes the complex tradeoff space of retention time profiling

- Idea: enable fast and robust profiling at higher refresh intervals & temperatures

# The Reach Profiler (REAPER): Enabling the Mitigation of DRAM Retention Failures via Profiling at Aggressive Conditions

Minesh Patel<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> Onur Mutlu<sup>§‡</sup> ETH Zürich <sup>‡</sup>Carnegie Mellon University

53

# The Reach Profiler (REAPER):

Enabling the Mitigation of DRAM Retention Failures via Profiling at Aggressive Conditions

### Minesh Patel Jeremie S. Kim Onur Mutlu

Carnegie Mellon

### **Leaky Cells**

### **Periodic DRAM Refresh**

Performance + Energy Overhead

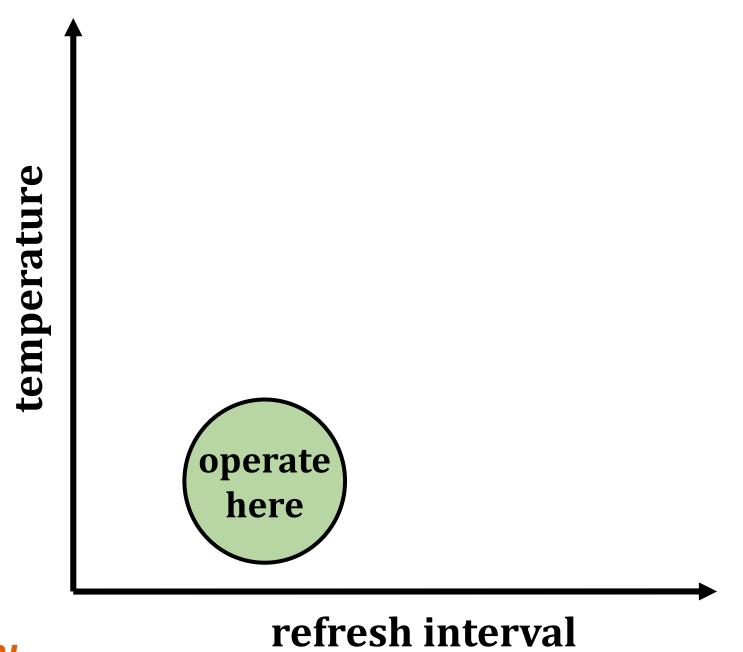

# Goal: find *all* retention failures for a refresh interval T > default (64ms)

### Process, voltage, temperature

Variable retention time

Data pattern dependence

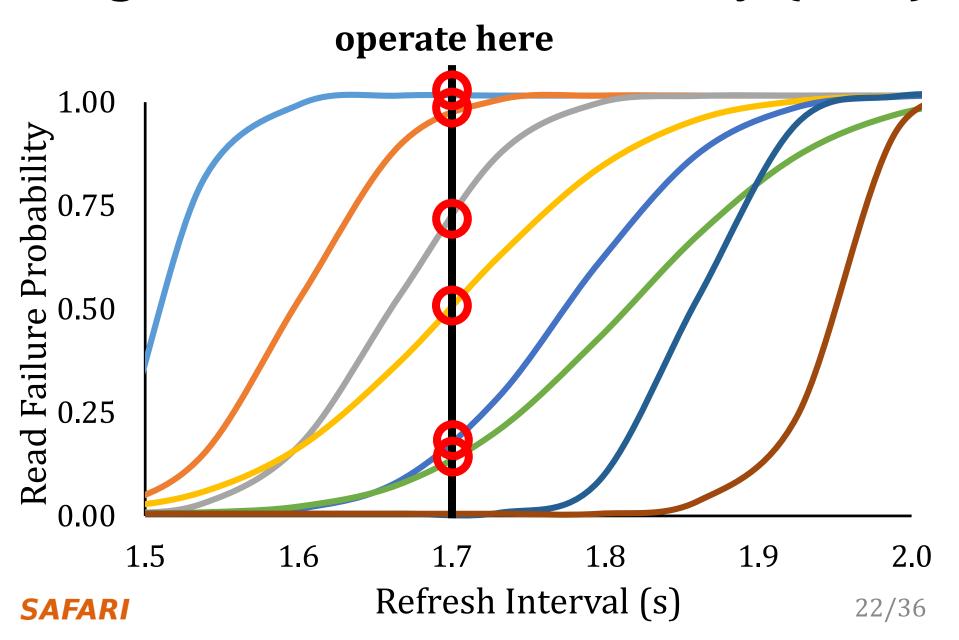

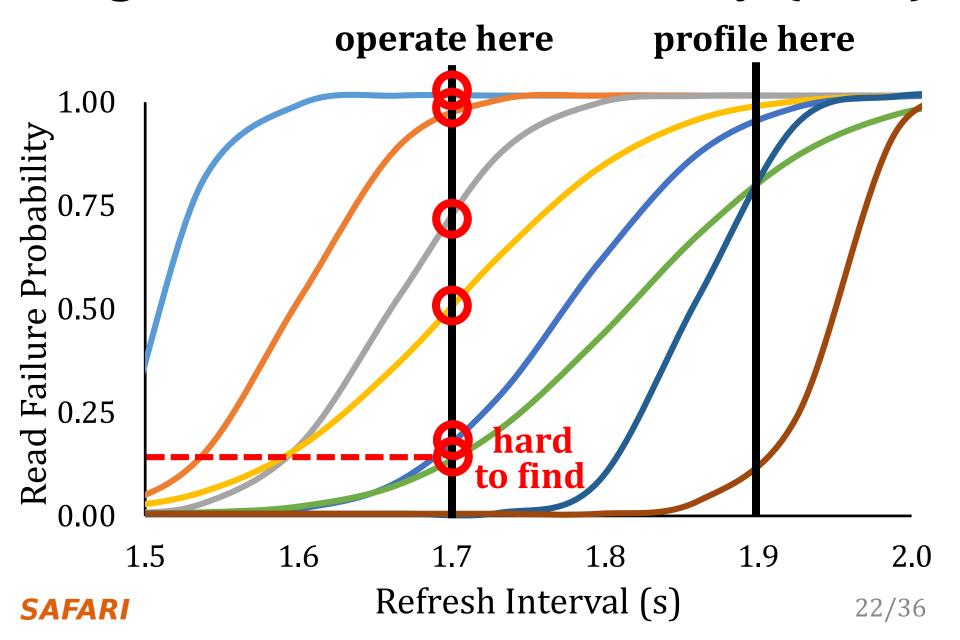

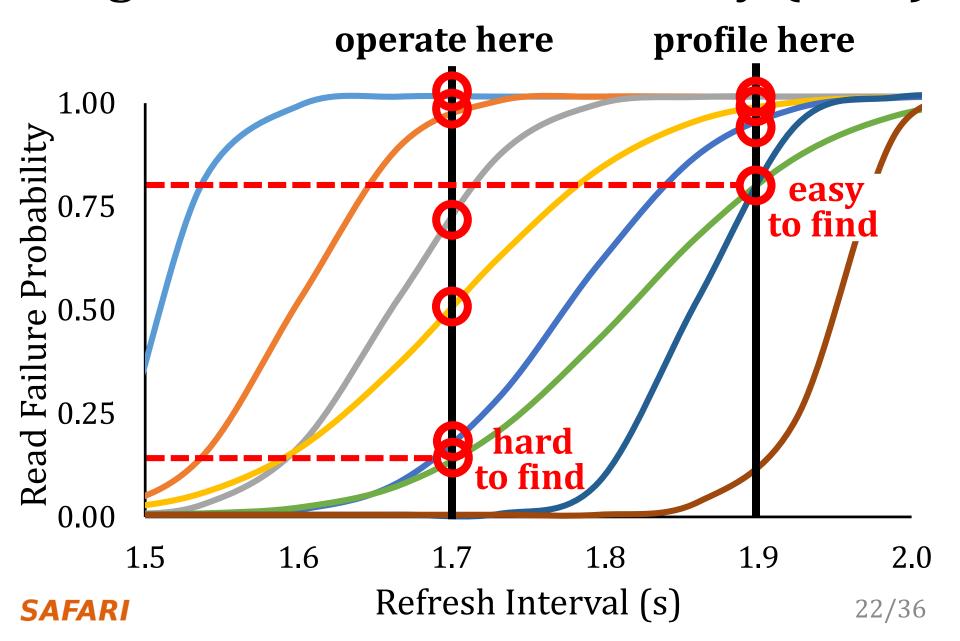

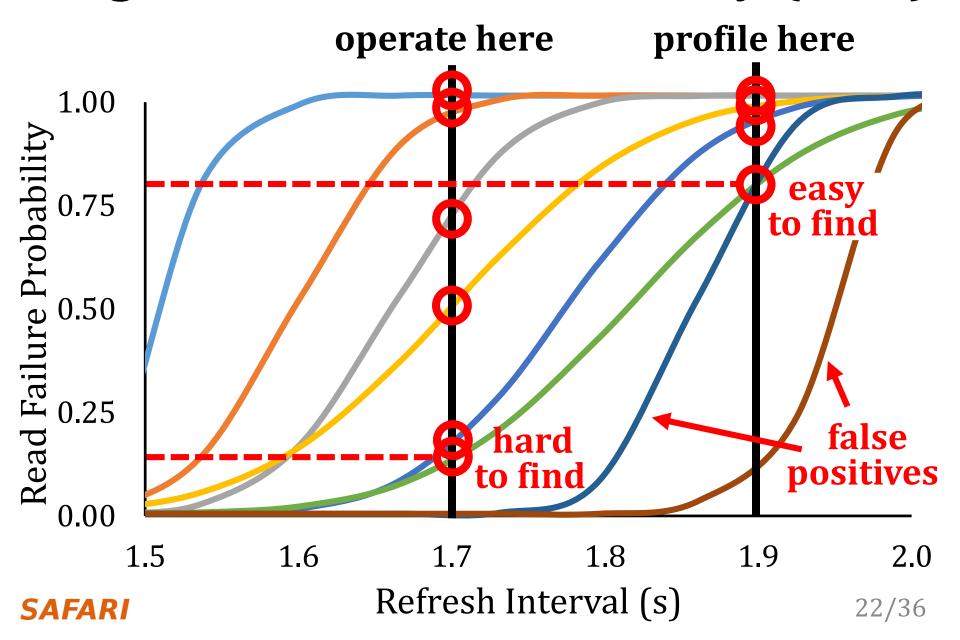

# Characterization of 368 LPDDR4 DRAM Chips

1

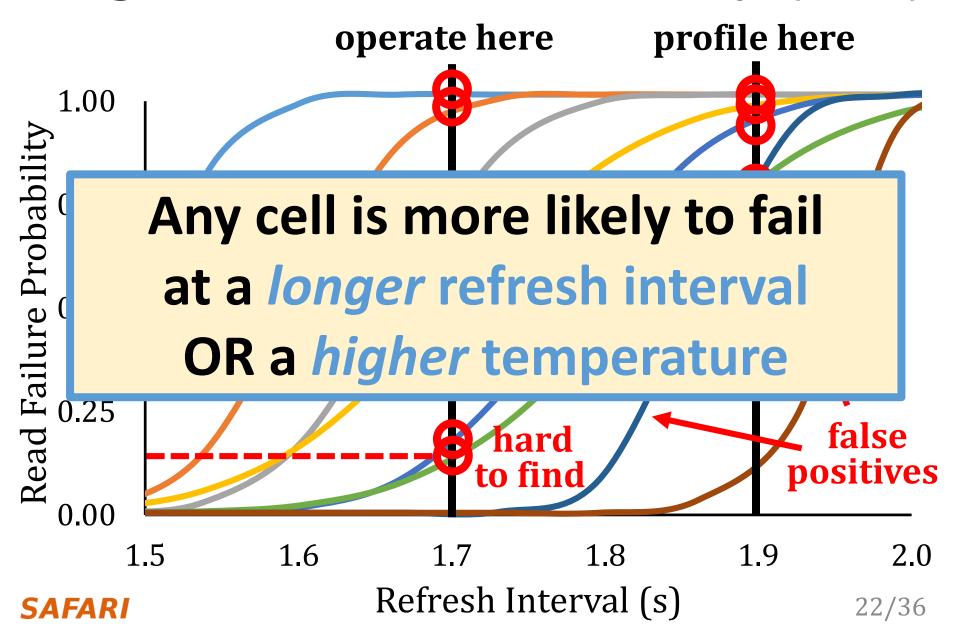

Cells are more likely to fail at an increased (refresh interval | temperature)

2

Complex tradeoff space between profiling (speed & coverage & false positives)

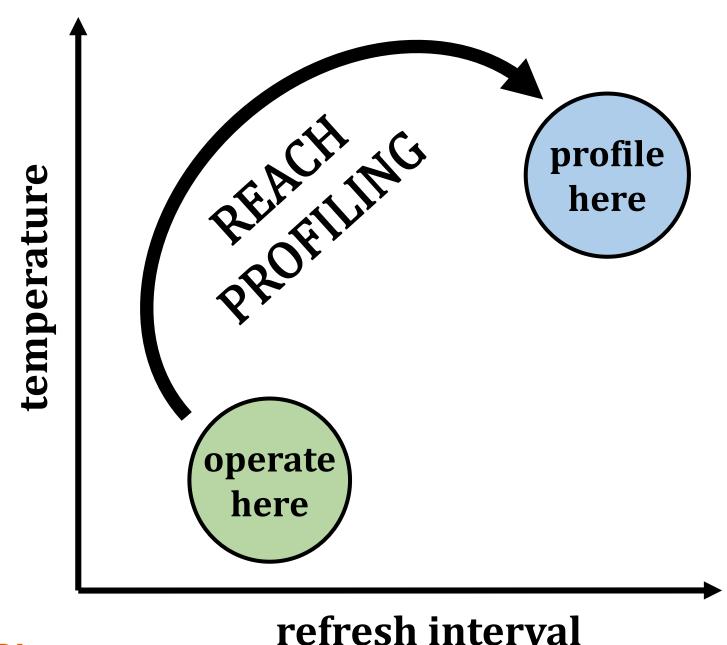

# Reach Profiling

A new DRAM retention failure profiling methodology

+ Faster and more reliable than current approaches

+ Enables longer refresh intervals

SAFARI

### **REAPER Outline**

- 1. DRAM Refresh Background

- 2. Failure Profiling Challenges

- 3. Current Approaches

- 4. LPDDR4 Characterization

- 5. Reach Profiling

- 6. End-to-end Evaluation

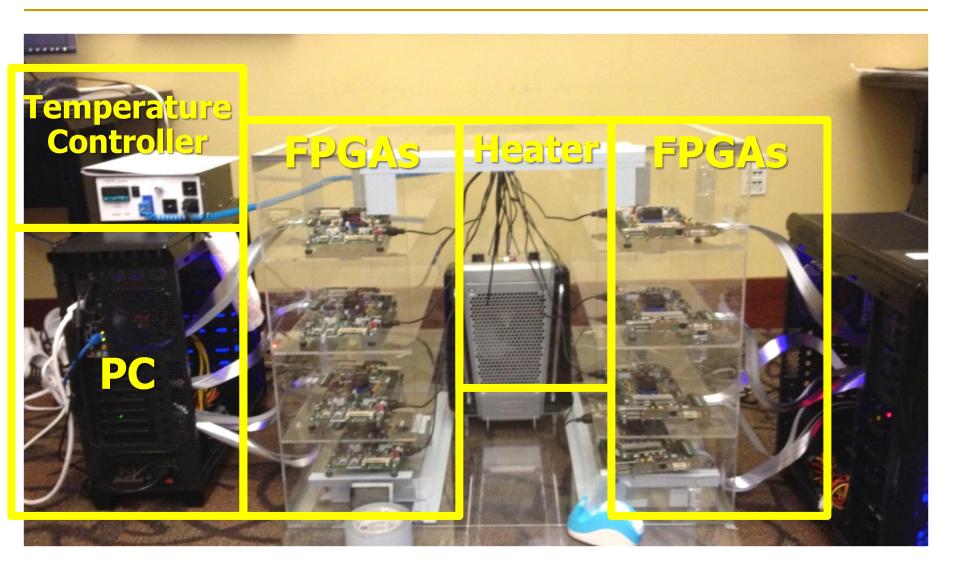

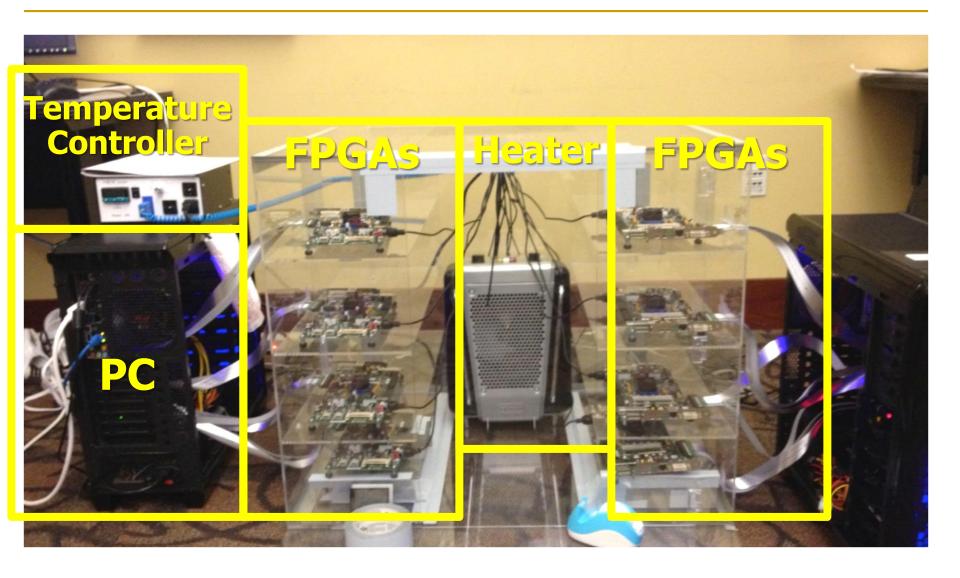

## Experimental Infrastructure

### 368 2y-nm LPDDR4 DRAM chips

- 4Gb chip size

- From 3 major DRAM vendors

### Thermally controlled testing chamber

- Ambient temperature range: {40°C 55°C} ± 0.25°C

- DRAM temperature is held at 15°C above ambient

### LPDDR4 Studies

- 1. Temperature

- 2. Data Pattern Dependence

- 3. Retention Time Distributions

- 4. Variable Retention Time

- 5. Individual Cell Characterization

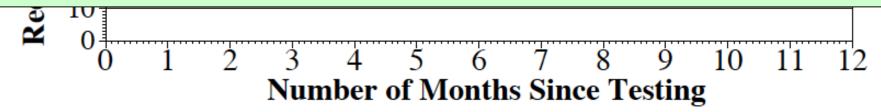

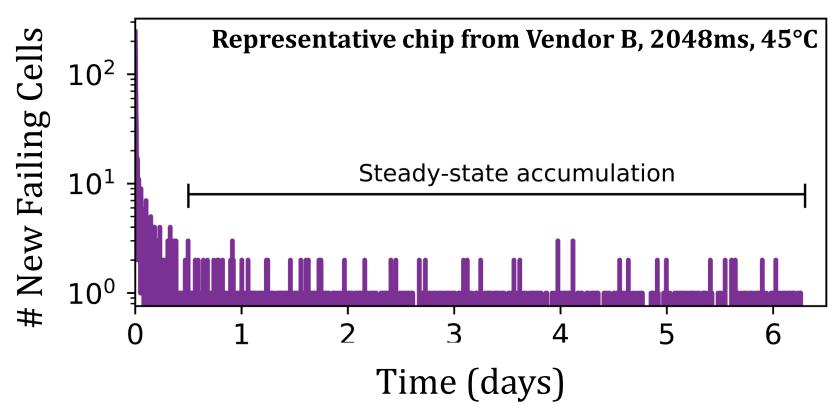

## Long-term Continuous Profiling

- New failing cells continue to appear over time

- Attributed to variable retention time (VRT)

- The set of failing cells changes over time

## Long-term Continuous Profiling

Error correction codes (ECC) and online profiling are necessary to manage new failing cells

- New failing cells continue to appear over time

- Attributed to variable retention time (VRT)

- The set of failing cells changes over time

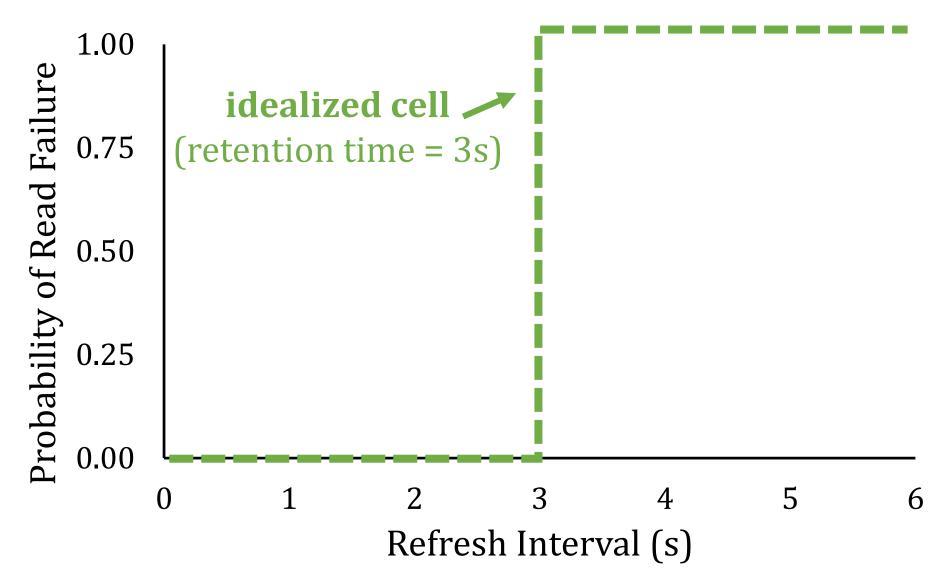

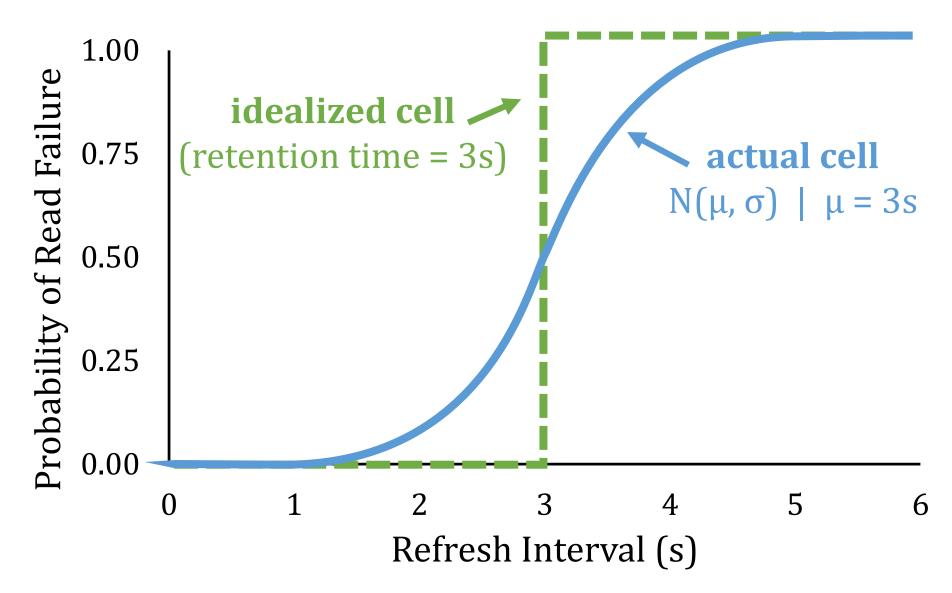

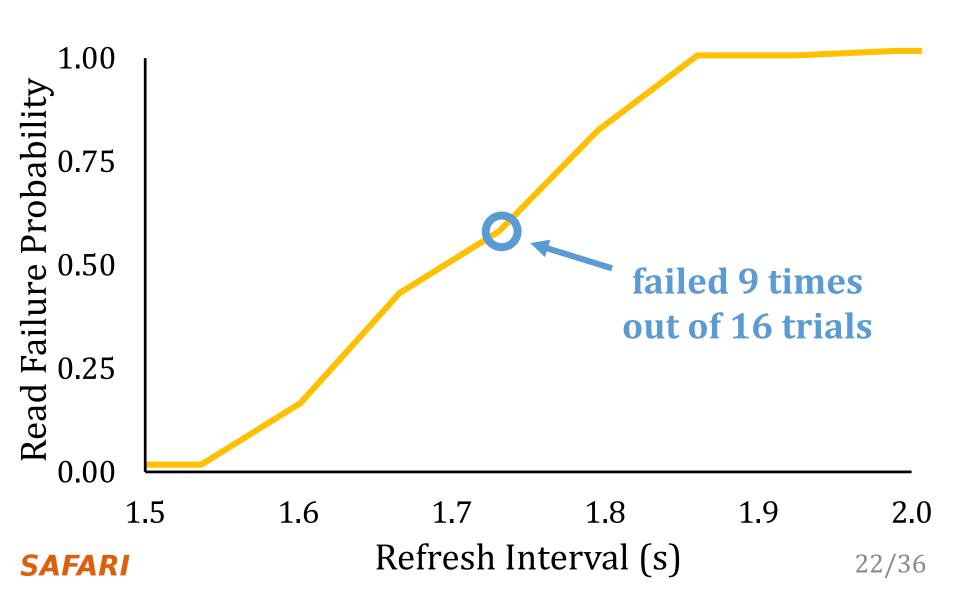

### Single-cell Failure Probability (Cartoon)

### Single-cell Failure Probability (Cartoon)

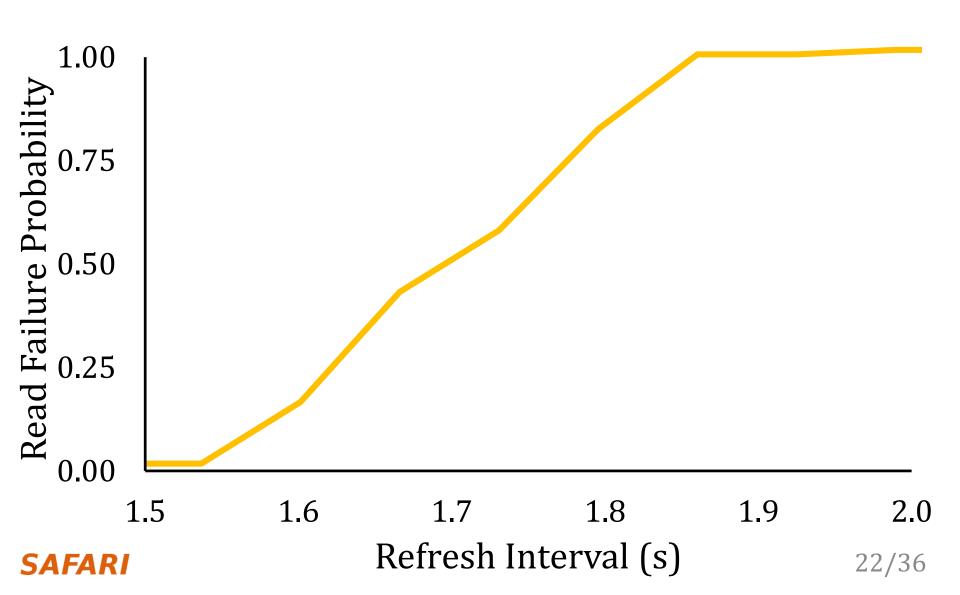

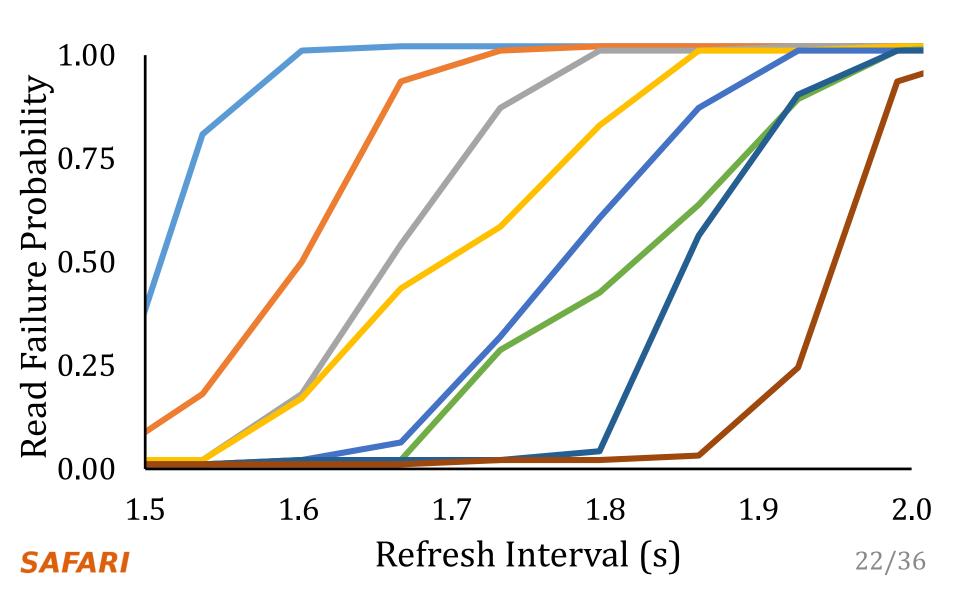

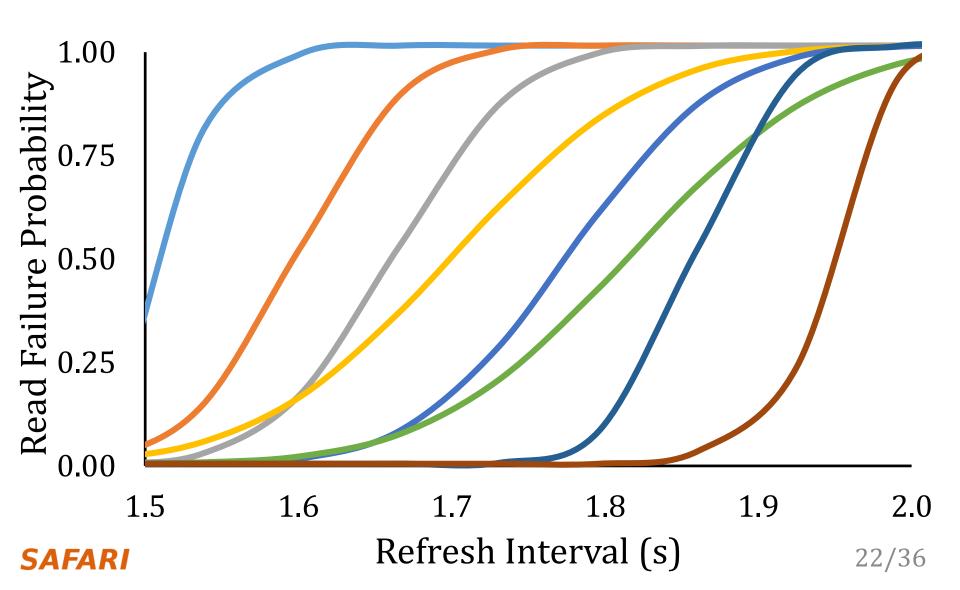

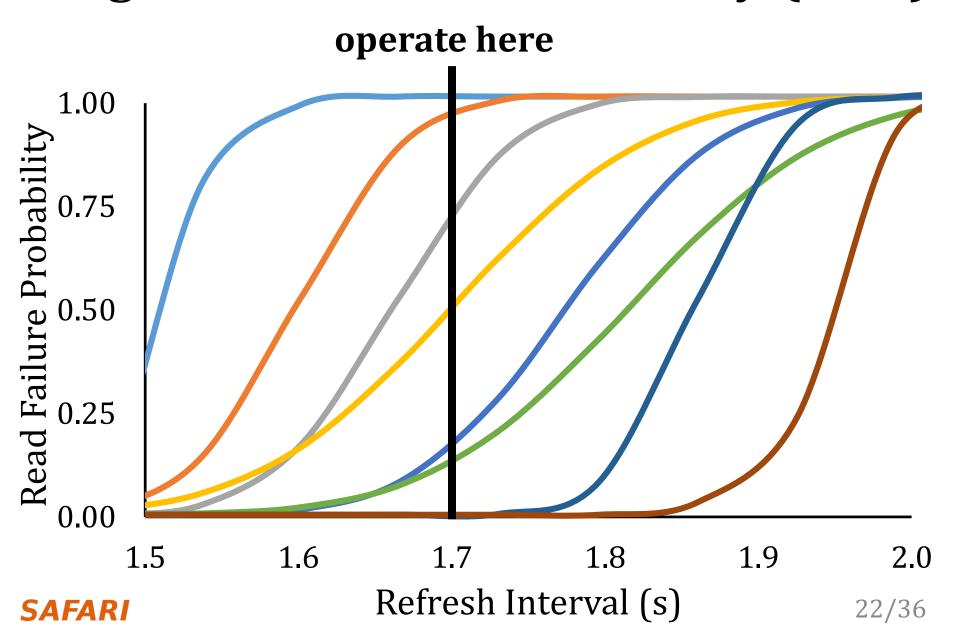

## Single-cell Failure Probability (Real)

## Single-cell Failure Probability (Real)

## Single-cell Failure Probability (Real)

## **REAPER Outline**

- 1. DRAM Refresh Background

- 2. Failure Profiling Challenges

- 3. Current Approaches

- 4. LPDDR4 Characterization

- 5. Reach Profiling

- 6. End-to-end Evaluation

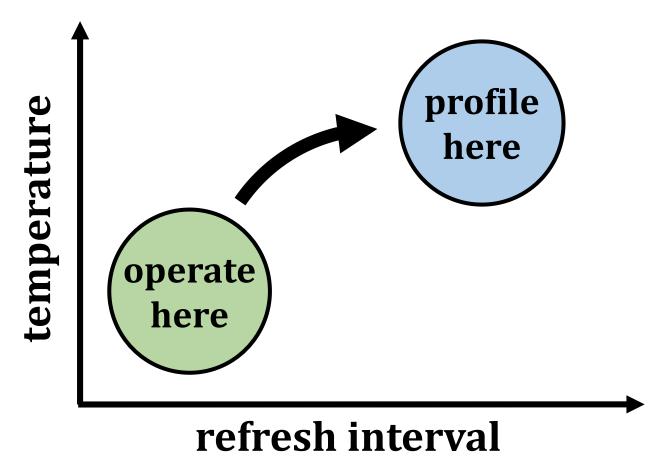

## Reach Profiling

**Key idea:** profile at a *longer refresh interval* and/or a *higher temperature*

SAFARI

## Reach Profiling

**Key idea:** profile at a *longer refresh interval* and/or a *higher temperature*

## Reach Profiling

**Key idea:** profile at a longer refresh interval and/or a higher temperature

#### Pros

- Fast + Reliable: reach profiling searches for cells where they are most likely to fail

#### Cons

- False Positives: profiler may identify cells that fail under profiling conditions, but not under operating conditions

## Towards an Implementation

Reach profiling is a general methodology

3 key questions for an implementation:

What are desirable profiling conditions?

How often should the system profile?

What information does the profiler need?

## Three Key Profiling Metrics

1. Runtime: how long profiling takes

**2. Coverage:** portion of all possible failures discovered by profiling

3. False positives: number of cells observed to fail during profiling but never during actual operation

## Three Key Profiling Metrics

1. Runtime: how long profiling takes

**2. Coverage:** portion of all possible failures discovered by profiling

We explore how these three metrics change under **many** different profiling conditions

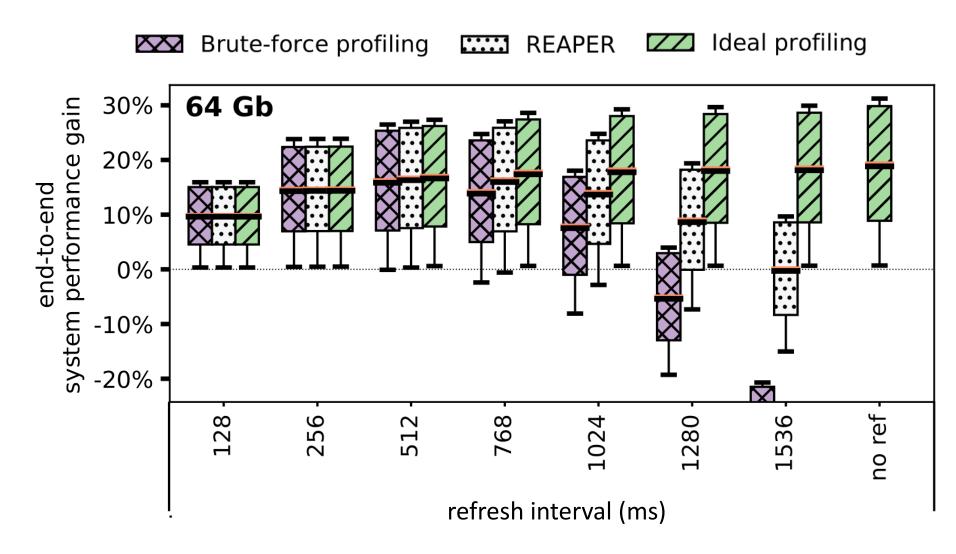

## **Evaluation Methodology**

#### Simulators

- Performance: Ramulator [Kim+, CAL'15]

- Energy: DRAMPower [Chandrasekar+, DSD'11]

#### Configuration

- 4-core (4GHz), 8MB LLC

- LPDDR4-3200, 4 channels, 1 rank/channel

#### Workloads

- 20 random 4-core benchmark mixes

- SPEC CPU2006 benchmark suite

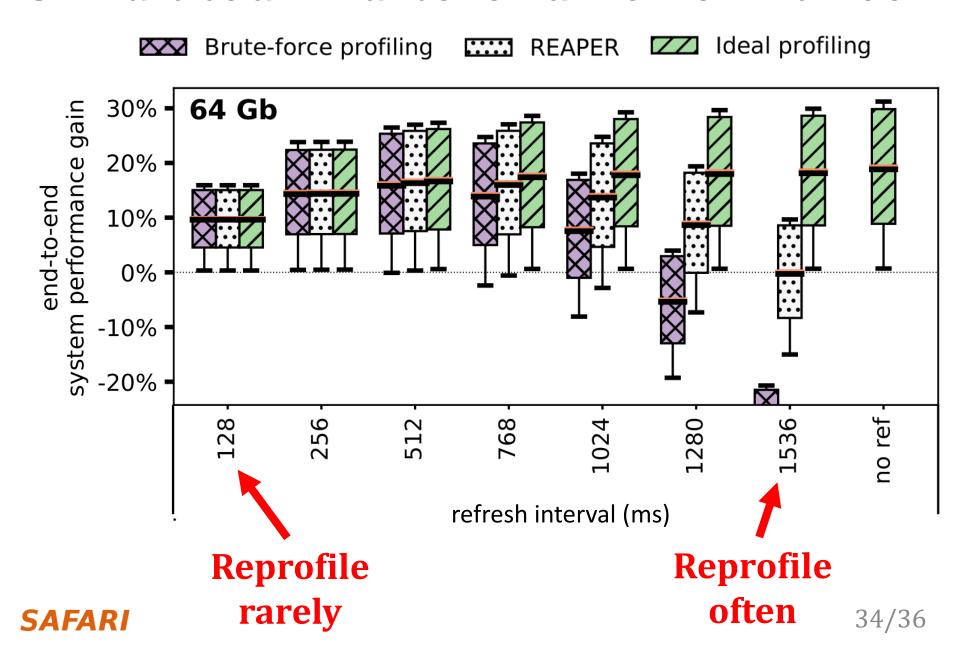

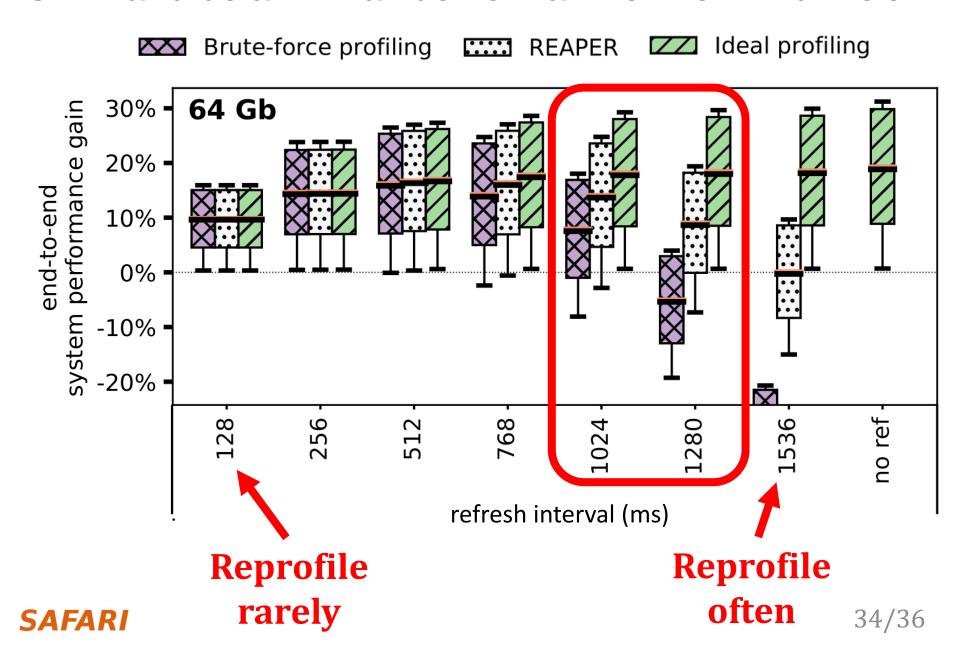

Brute-force profiling

**Ideal** profiling

## On average, REAPER enables:

16.3% system performance improvement 36.4% DRAM power reduction

REAPER enables longer refresh intervals, which are unreasonable using brute-force profiling

rarely

## Other Analyses in the Paper

#### Detailed LPDDR4 characterization data

- Temperature dependence effects

- Retention time distributions

- Data pattern dependence

- Variable retention time

- Individual cell failure distributions

#### Profiling tradeoff space characterization

- Runtime, coverage, and false positive rate

- Temperature and refresh interval

- Probabilistic model for tolerable failure rates

- Detailed results for end-to-end evaluations

## **REAPER Summary**

#### **Problem**:

- •DRAM refresh performance and energy overhead is high

- •Current approaches to retention failure profiling are slow or unreliable

#### **Goals**:

- 1. Thoroughly analyze profiling tradeoffs

- 2. Develop a **fast** and **reliable** profiling mechanism

#### **Key Contributions**:

- 1. First detailed characterization of 368 LPDDR4 DRAM chips

- 2. Reach profiling: Profile at a longer refresh interval or higher temperature than target conditions, where cells are more likely to fail

#### **Evaluation:**

- •2.5x faster profiling with 99% coverage and 50% false positives

- •REAPER enables 16.3% system performance improvement and 36.4%

#### **DRAM** power reduction

•Enables longer refresh intervals that were previously unreasonable

### Handling Both DPD and VRT [ISCA'17]

- Minesh Patel, Jeremie S. Kim, and Onur Mutlu,

"The Reach Profiler (REAPER): Enabling the Mitigation of DRAM

Retention Failures via Profiling at Aggressive Conditions"

Proceedings of the 44th International Symposium on Computer

Architecture (ISCA), Toronto, Canada, June 2017.

[Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

- First experimental analysis of (mobile) LPDDR4 chips

- Analyzes the complex tradeoff space of retention time profiling

- Idea: enable fast and robust profiling at higher refresh intervals & temperatures

## The Reach Profiler (REAPER): Enabling the Mitigation of DRAM Retention Failures via Profiling at Aggressive Conditions

Minesh Patel<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> Onur Mutlu<sup>§‡</sup> ETH Zürich <sup>‡</sup>Carnegie Mellon University

95

## The DRAM Latency PUF:

Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern Commodity DRAM Devices

<u>Jeremie S. Kim</u> Minesh Patel Hasan Hassan Onur Mutlu

**HPCA 2018**

QR Code for the paper

https://people.inf.ethz.ch/omutlu/pub/dram-latency-puf hpca18.pdf

Carnegie Mellon

## How Do We Keep Memory Secure?

- DRAM

- Flash memory

- Emerging Technologies

- Phase Change Memory

- STT-MRAM

- RRAM, memristors

- **...**

## Solution Direction: Principled Designs

# Design fundamentally secure computing architectures

Predict and prevent such safety issues

## How Do We Keep Memory Secure?

- Understand: Solid methodologies for failure modeling and discovery

- Modeling based on real device data small scale and large scale

- Metrics for secure architectures

- Architect: Principled co-architecting of system and memory

- Good partitioning of duties across the stack

- Patch-ability in the field

- Design & Test: Principled electronic design, automation, testing

- Design for security

- High coverage and good interaction with reliability methods

#### Understand and Model with Experiments (DRAM)

#### Understand and Model with Experiments (Flash)

[DATE 2012, ICCD 2012, DATE 2013, ITJ 2013, ICCD 2013, SIGMETRICS 2014, HPCA 2015, DSN 2015, MSST 2015, JSAC 2016, HPCA 2017, DFRWS 2017, PIEEE'17, HPCA'18, SIGMETRICS'18]

NAND Daughter Board

## Understanding Flash Memory Reliability

Proceedings of the IEEE, Sept. 2017

## Error Characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives

This paper reviews the most recent advances in solid-state drive (SSD) error characterization, mitigation, and data recovery techniques to improve both SSD's reliability and lifetime.

By Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu

https://arxiv.org/pdf/1706.08642

## Understanding Flash Memory Reliability

Justin Meza, Qiang Wu, Sanjeev Kumar, and Onur Mutlu, "A Large-Scale Study of Flash Memory Errors in the Field" Proceedings of the ACM International Conference on Measurement and Modeling of Computer Systems (SIGMETRICS), Portland, OR, June 2015.

[Slides (pptx) (pdf)] [Coverage at ZDNet] [Coverage on The Register] [Coverage on TechSpot] [Coverage on The Tech Report]

#### A Large-Scale Study of Flash Memory Failures in the Field

Justin Meza

Carnegie Mellon University

meza@cmu.edu

Qiang Wu Facebook, Inc. qwu@fb.com Sanjeev Kumar Facebook, Inc. skumar@fb.com Onur Mutlu Carnegie Mellon University onur@cmu.edu

#### NAND Flash Vulnerabilities [HPCA'17]

#### HPCA, Feb. 2017

#### Vulnerabilities in MLC NAND Flash Memory Programming: Experimental Analysis, Exploits, and Mitigation Techniques

Yu Cai<sup>†</sup> Saugata Ghose<sup>†</sup> Yixin Luo<sup>‡†</sup> Ken Mai<sup>†</sup> Onur Mutlu<sup>§†</sup> Erich F. Haratsch<sup>‡</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>Seagate Technology <sup>§</sup>ETH Zürich

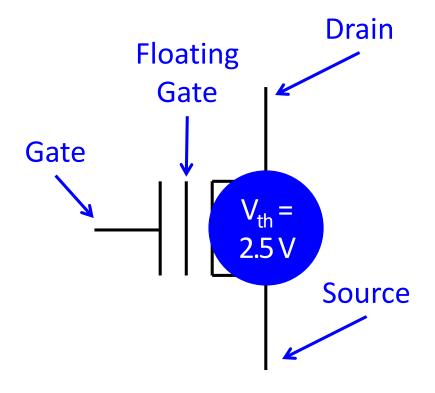

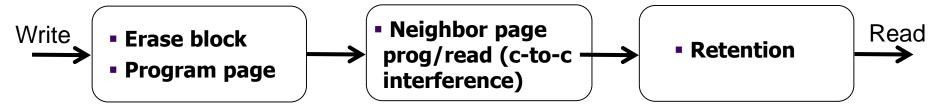

Modern NAND flash memory chips provide high density by storing two bits of data in each flash cell, called a multi-level cell (MLC). An MLC partitions the threshold voltage range of a flash cell into four voltage states. When a flash cell is programmed, a high voltage is applied to the cell. Due to parasitic capacitance coupling between flash cells that are physically close to each other, flash cell programming can lead to cell-to-cell program interference, which introduces errors into neighboring flash cells. In order to reduce the impact of cell-to-cell interference on the reliability of MLC NAND flash memory, flash manufacturers adopt a two-step programming method, which programs the MLC in two separate steps. First, the flash memory partially programs the least significant bit of the MLC to some intermediate threshold voltage. Second, it programs the most significant bit to bring the MLC up to its full voltage state.

In this paper, we demonstrate that two-step programming exposes new reliability and security vulnerabilities. We expe-

belongs to a different flash memory *page* (the unit of data programmed and read at the same time), which we refer to, respectively, as the least significant bit (LSB) page and the most significant bit (MSB) page [5].

A flash cell is programmed by applying a large voltage on the control gate of the transistor, which triggers charge transfer into the floating gate, thereby increasing the threshold voltage. To precisely control the threshold voltage of the cell, the flash memory uses *incremental step pulse programming* (ISPP) [12, 21, 25, 41]. ISPP applies multiple short pulses of the programming voltage to the control gate, in order to increase the cell threshold voltage by some small voltage amount ( $V_{step}$ ) after each step. Initial MLC designs programmed the threshold voltage in *one shot*, issuing all of the pulses back-to-back to program *both* bits of data at the same time. However, as flash memory scales down, the distance between neighboring flash cells decreases, which

https://people.inf.ethz.ch/omutlu/pub/flash-memory-programming-vulnerabilities hpca17.pdf

## 3D NAND Flash Reliability I [HPCA'18]

Yixin Luo, Saugata Ghose, Yu Cai, Erich F. Haratsch, and Onur Mutlu,

"HeatWatch: Improving 3D NAND Flash Memory Device

Reliability by Exploiting Self-Recovery and Temperature-Awareness"

Proceedings of the <u>24th International Symposium on High-Performance</u> <u>Computer Architecture</u> (**HPCA**), Vienna, Austria, February 2018. [<u>Lightning Talk Video</u>]

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

## HeatWatch: Improving 3D NAND Flash Memory Device Reliability by Exploiting Self-Recovery and Temperature Awareness

```

Yixin Luo<sup>†</sup> Saugata Ghose<sup>†</sup> Yu Cai<sup>‡</sup> Erich F. Haratsch<sup>‡</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>Seagate Technology <sup>§</sup>ETH Zürich

```

## 3D NAND Flash Reliability II [SIGMETRICS'18]

Yixin Luo, Saugata Ghose, Yu Cai, Erich F. Haratsch, and Onur Mutlu, "Improving 3D NAND Flash Memory Lifetime by Tolerating Early Retention Loss and Process Variation" Proceedings of the <u>ACM International Conference on Measurement and Modeling of Computer Systems</u> (SIGMETRICS), Irvine, CA, USA, June 2018.

[Abstract]

## Improving 3D NAND Flash Memory Lifetime by Tolerating Early Retention Loss and Process Variation

Yixin Luo<sup>†</sup> Saugata Ghose<sup>†</sup> Yu Cai<sup>†</sup> Erich F. Haratsch<sup>‡</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>Seagate Technology <sup>§</sup>ETH Zürich

#### If Time Permits: NAND Flash Vulnerabilities

Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu,

"Error Characterization, Mitigation, and Recovery in Flash Memory Based Solid State Drives"

**Proceedings of the IEEE**, September 2017.

Cai+, "Error Patterns in MLC NAND Flash Memory: Measurement, Characterization, and Analysis," DATE 2012.

Cai+, "Flash Correct-and-Refresh: Retention-Aware Error Management for Increased Flash Memory Lifetime," ICCD 2012.

Cai+, "Threshold Voltage Distribution in MLC NAND Flash Memory: Characterization, Analysis and Modeling," DATE 2013.

Cai+, "Error Analysis and Retention-Aware Error Management for NAND Flash Memory," Intel Technology Journal 2013.

Cai+, "Program Interference in MLC NAND Flash Memory: Characterization, Modeling, and Mitigation," ICCD 2013.

Cai+, "Neighbor-Cell Assisted Error Correction for MLC NAND Flash Memories," SIGMETRICS 2014.

Cai+,"Data Retention in MLC NAND Flash Memory: Characterization, Optimization and Recovery," HPCA 2015.

Cai+, "Read Disturb Errors in MLC NAND Flash Memory: Characterization and Mitigation," DSN 2015.

Luo+, "WARM: Improving NAND Flash Memory Lifetime with Write-hotness Aware Retention Management," MSST 2015.

Meza+, "A Large-Scale Study of Flash Memory Errors in the Field," SIGMETRICS 2015.

Luo+, "Enabling Accurate and Practical Online Flash Channel Modeling for Modern MLC NAND Flash Memory," IEEE JSAC 2016.

Cai+, "Vulnerabilities in MLC NAND Flash Memory Programming: Experimental Analysis, Exploits, and Mitigation Techniques," HPCA 2017.

Fukami+, "Improving the Reliability of Chip-Off Forensic Analysis of NAND Flash Memory Devices," DFRWS EU 2017.

Luo+, "HeatWatch: Improving 3D NAND Flash Memory Device Reliability by Exploiting Self-Recovery and Temperature-Awareness," HPCA 2018.

Luo+, "Improving 3D NAND Flash Memory Lifetime by Tolerating Early Retention Loss and Process Variation," SIGMETRICS 2018.

Cai+, "Error Characterization, Mitigation, and Recovery in Flash Memory Based Solid State Drives," Proc. IEEE 2017.

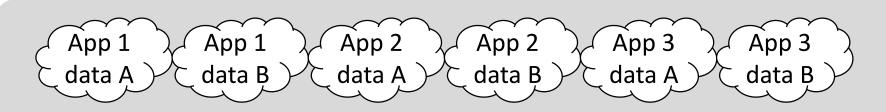

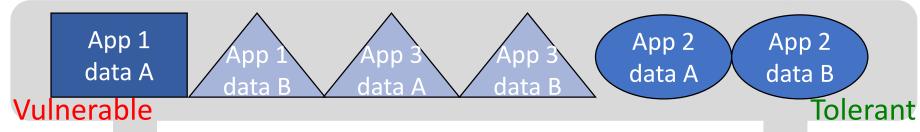

#### There are Two Other Solution Directions

New Technologies: Replace or (more likely) augment DRAM

with a different technology

Non-volatile memories

Embracing Un-reliability:

Design memories with different reliability and store data intelligently across them

[Luo+ DSN 2014]

Aigorithm

Program/Language

System Software

SW/HW Interface

Micro-architecture

Logic

Devices

Electrons

**...**

Fundamental solutions to security require co-design across the hierarchy

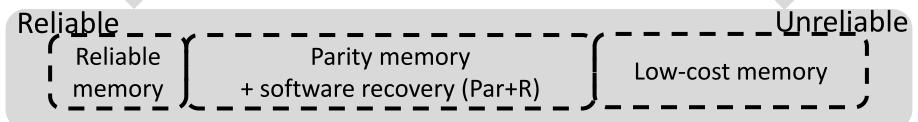

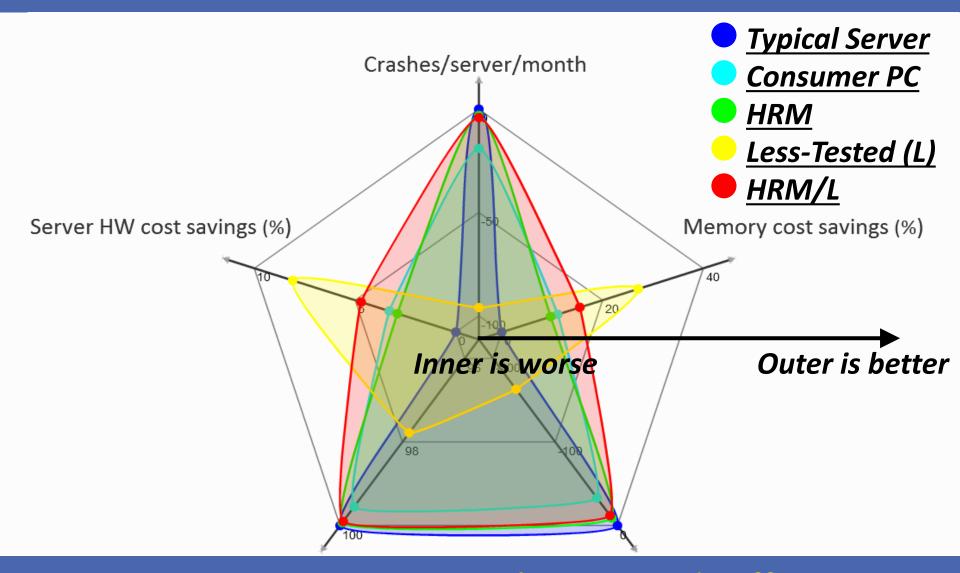

### Exploiting Memory Error Tolerance with Hybrid Memory Systems

Vulnerable data

Tolerant data

Reliable memory

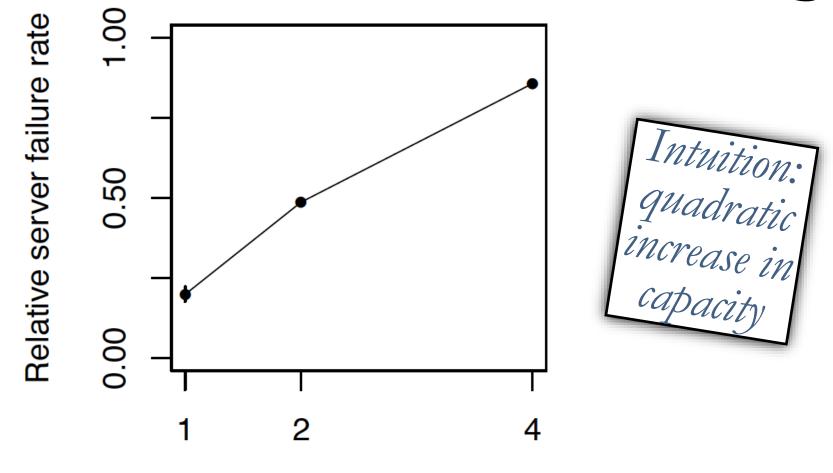

Low-cost memory

On Microsoft's Web Search workload Reduces server hardware cost by 4.7 % Achieves single server availability target of 99.90 %

Heterogeneous-Reliability Memory [DSN 2014]

### Heterogeneous-Reliability Memory

Step 1: Characterize and classify application memory error tolerance

Step 2: Map application data to the HRM system enabled by SW/HW cooperative solutions

### **Evaluation Results**

### More on Heterogeneous-Reliability Memory

Yixin Luo, Sriram Govindan, Bikash Sharma, Mark Santaniello, Justin Meza, Aman Kansal, Jie Liu, Badriddine Khessib, Kushagra Vaid, and Onur Mutlu, "Characterizing Application Memory Error Vulnerability to Optimize Data Center Cost via Heterogeneous-Reliability Memory"

Proceedings of the 44th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Atlanta, GA, June 2014. [Summary]

[Slides (pptx) (pdf)] [Coverage on ZDNet]

### Characterizing Application Memory Error Vulnerability to Optimize Datacenter Cost via Heterogeneous-Reliability Memory

Yixin Luo Sriram Govindan\* Bikash Sharma\* Mark Santaniello\* Justin Meza Aman Kansal\* Jie Liu\* Badriddine Khessib\* Kushagra Vaid\* Onur Mutlu Carnegie Mellon University, yixinluo@cs.cmu.edu, {meza, onur}@cmu.edu

\*Microsoft Corporation, {srgovin, bsharma, marksan, kansal, jie.liu, bkhessib, kvaid}@microsoft.com

### Summary: Memory Reliability and Security

- Memory reliability is reducing

- Reliability issues open up security vulnerabilities

- Very hard to defend against

- Rowhammer is an example

- Its implications on system security research are tremendous & exciting

- Good news: We have a lot more to do.

- Understand: Solid methodologies for failure modeling and discovery

- Modeling based on real device data small scale and large scale

- Architect: Principled co-architecting of system and memory

- Good partitioning of duties across the stack

- Design & Test: Principled electronic design, automation, testing

- High coverage and good interaction with system reliability methods

113

# Fundamentally Secure, Reliable, Safe Computing Architectures

## Main Memory Needs Intelligent Controllers

### Memory Systems and Memory-Centric Computing Systems Lec 3 Topic 2: Memory Reliability and Security

Prof. Onur Mutlu

omutlu@gmail.com

https://people.inf.ethz.ch/omutlu

11 July 2018

HiPEAC ACACES Summer School 2018

**Carnegie Mellon**

### Flash Memory Reliability and Security

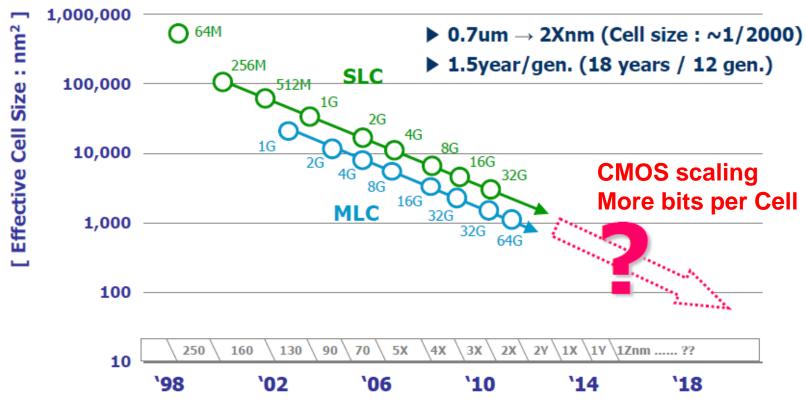

### Evolution of NAND Flash Memory

Seaung Suk Lee, "Emerging Challenges in NAND Flash Technology", Flash Summit 2011 (Hynix)

- Flash memory is widening its range of applications

- Portable consumer devices, laptop PCs and enterprise servers

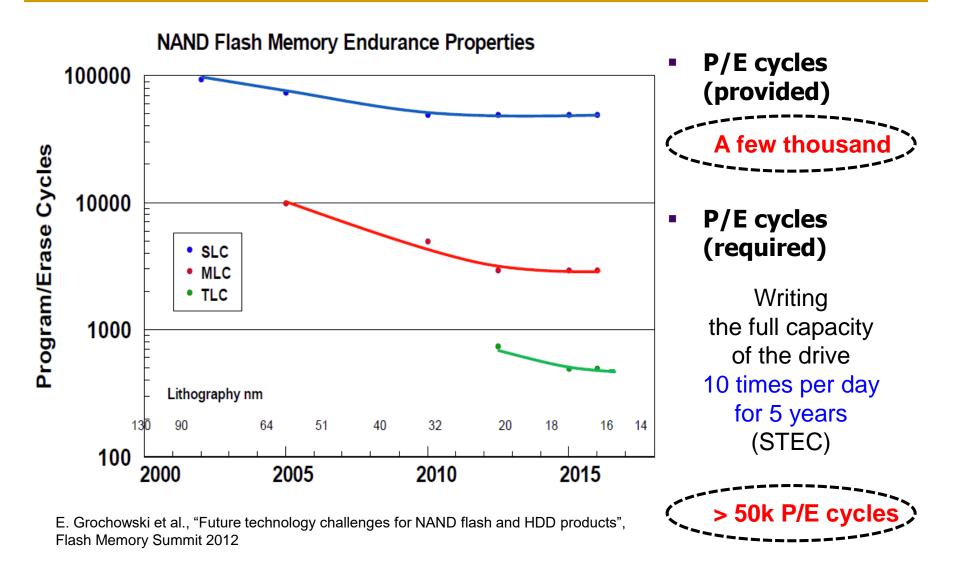

### Flash Challenges: Reliability and Endurance

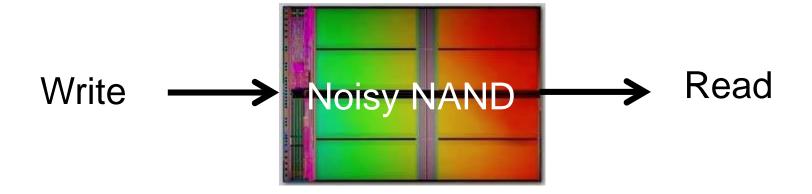

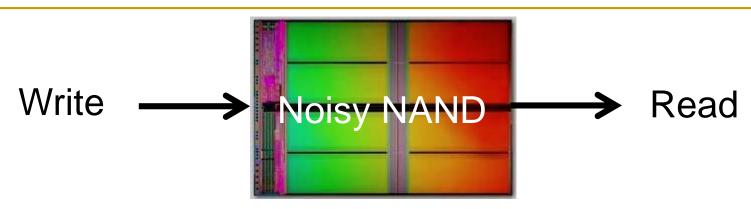

### NAND Flash Memory is Increasingly Noisy

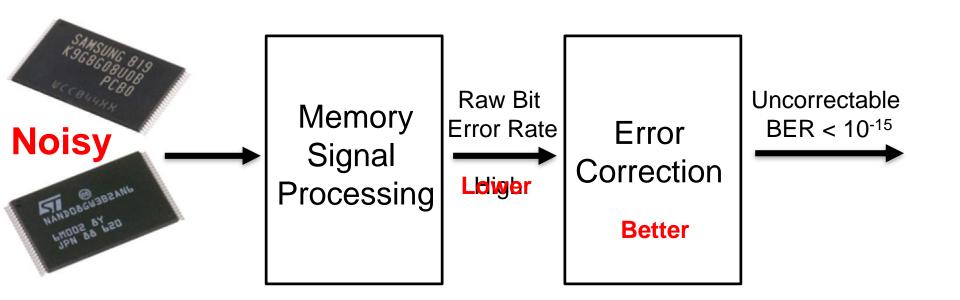

### Future NAND Flash-based Storage Architecture

#### **Our Goals:**

Build reliable error models for NAND flash memory

Design efficient reliability mechanisms based on the model

### NAND Flash Error Model

#### **Experimentally characterize and model dominant errors**

Cai et al., "Error Patterns in MLC NAND Flash Memory: Measurement, Characterization, and Analysis", **DATE 2012**Luo et al., "Enabling Accurate and Practical Online Flash Channel Modeling for Modern MLC NAND Flash Memory", **JSAC 2016**

Cai et al., "Threshold voltage distribution in MLC NAND Flash Memory: Characterization, Analysis, and Modeling", **DATE 2013**

Cai et al., "Vulnerabilities in MLC NAND Flash Memory Programming: Experimental Analysis, Exploits, and Mitigation Techniques", **HPCA 2017**  Cai et al., "Program Interference in MLC NAND Flash Memory: Characterization, Modeling, and Mitigation", ICCD 2013

Cai et al., "Neighbor-Cell Assisted Error Correction in MLC NAND Flash Memories", **SIGMETRICS 2014**

Cai et al., "Read Disturb Errors in MLC NAND Flash Memory: Characterization and Mitigation", **DSN 2015**

Cai et al., "Flash Correct-and-Refresh: Retention-aware error management for increased flash memory lifetime", ICCD 2012

Cai et al., "Error Analysis and Retention-Aware Error Management for NAND Flash Memory", **ITJ 2013**

Cai et al., "Data Retention in MLC NAND Flash Memory: Characterization, Optimization and Recovery", **HPCA 2015**

### Our Goals and Approach

#### Goals:

- Understand error mechanisms and develop reliable predictive models for MLC NAND flash memory errors

- Develop efficient error management techniques to mitigate errors and improve flash reliability and endurance

#### Approach:

- Solid experimental analyses of errors in real MLC NAND flash memory → drive the understanding and models

- □ Understanding, models, and creativity → drive the new techniques

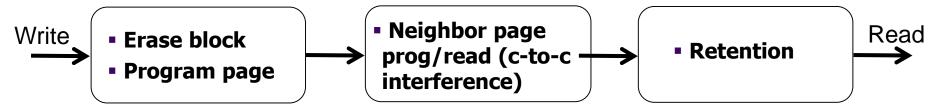

### Experimental Testing Platform

[DATE 2012, ICCD 2012, DATE 2013, ITJ 2013, ICCD 2013, SIGMETRICS 2014, HPCA 2015, DSN 2015, MSST 2015, JSAC 2016, HPCA 2017, DFRWS 2017, PIEEE 2017, HPCA 2018, SIGMETRICS 2018]

NAND Daughter Board

Cai+, "Error Characterization, Mitigation, and Recovery in Flash Memory Based Solid State Drives," Proc. IEEE 2017.

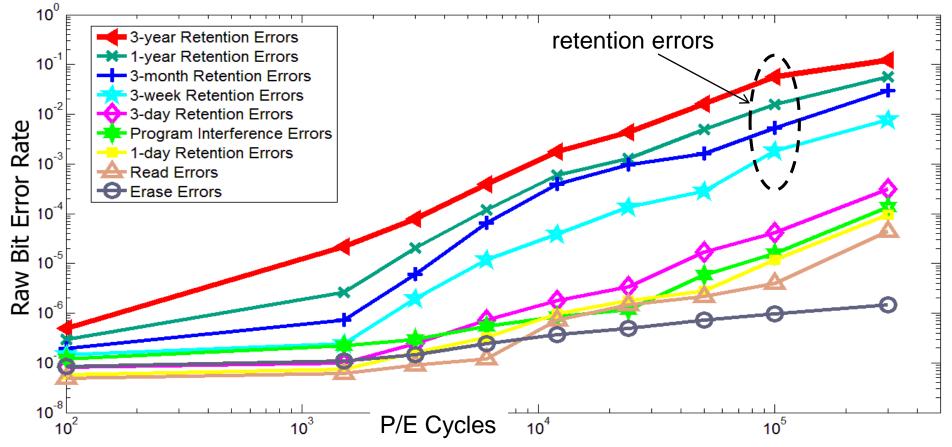

### NAND Flash Error Types

- Four types of errors [Cai+, DATE 2012]

- Caused by common flash operations

- Read errors

- Erase errors

- Program (interference) errors

- Caused by flash cell losing charge over time

- Retention errors

- Whether an error happens depends on required retention time

- Especially problematic in MLC flash because threshold voltage window to determine stored value is smaller

### Observations: Flash Error Analysis

- Raw bit error rate increases exponentially with P/E cycles

- Retention errors are dominant (>99% for 1-year ret. time)

- Retention errors increase with retention time requirement

### More on Flash Error Analysis

Yu Cai, Erich F. Haratsch, Onur Mutlu, and Ken Mai,

"Error Patterns in MLC NAND Flash Memory:

Measurement, Characterization, and Analysis"

Proceedings of the Design, Automation, and Test in Europe

Conference (DATE), Dresden, Germany, March 2012. Slides

(ppt)

### Error Patterns in MLC NAND Flash Memory: Measurement, Characterization, and Analysis

Yu Cai<sup>1</sup>, Erich F. Haratsch<sup>2</sup>, Onur Mutlu<sup>1</sup> and Ken Mai<sup>1</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA

<sup>2</sup>LSI Corporation, 1110 American Parkway NE, Allentown, PA

<sup>1</sup>{yucai, onur, kenmai}@andrew.cmu.edu, <sup>2</sup>erich.haratsch@lsi.com

#### Solution to Retention Errors

- Refresh periodically

- Change the period based on P/E cycle wearout

- Refresh more often at higher P/E cycles

- Use a combination of in-place and remapping-based refresh

Cai et al. "Flash Correct-and-Refresh: Retention-Aware Error Management for Increased Flash Memory Lifetime", ICCD 2012.

### Flash Correct-and-Refresh [ICCD'12]

Yu Cai, Gulay Yalcin, Onur Mutlu, Erich F. Haratsch, Adrian Cristal, Osman Unsal, and Ken Mai,

"Flash Correct-and-Refresh: Retention-Aware Error

Management for Increased Flash Memory Lifetime"

Proceedings of the 30th IEEE International Conference on Computer Design (ICCD), Montreal, Quebec, Canada, September 2012. Slides (ppt)(pdf)

### Flash Correct-and-Refresh: Retention-Aware Error Management for Increased Flash Memory Lifetime

Yu Cai<sup>1</sup>, Gulay Yalcin<sup>2</sup>, Onur Mutlu<sup>1</sup>, Erich F. Haratsch<sup>3</sup>, Adrian Cristal<sup>2</sup>, Osman S. Unsal<sup>2</sup> and Ken Mai<sup>1</sup>DSSC, Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA

<sup>2</sup>Barcelona Supercomputing Center, C/Jordi Girona 29, Barcelona, Spain

<sup>3</sup>LSI Corporation, 1110 American Parkway NE, Allentown, PA

### Many Errors and Their Mitigation [PIEEE'17]

Table 3 List of Different Types of Errors Mitigated by NAND Flash Error Mitigation Mechanisms

|                                                               | Error Type                            |                                   |                                                 |                                         |                                       |

|---------------------------------------------------------------|---------------------------------------|-----------------------------------|-------------------------------------------------|-----------------------------------------|---------------------------------------|

| Mitigation<br>Mechanism                                       | <i>P/E Cycling</i> [32,33,42] (§IV-A) | <b>Program</b> [40,42,53] (§IV-B) | Cell-to-Cell Interference [32,35,36,55] (§IV-C) | Data Retention [20,32,34,37,39] (§IV-D) | Read Disturb<br>[20,32,38,62] (§IV-E) |

| Shadow Program Sequencing [35,40] (Section V-A)               |                                       |                                   | X                                               |                                         |                                       |

| Neighbor-Cell Assisted Error<br>Correction [36] (Section V-B) |                                       |                                   | X                                               |                                         |                                       |

| <b>Refresh</b> [34,39,67,68] (Section V-C)                    |                                       |                                   |                                                 | X                                       | X                                     |

| Read-Retry [33,72,107] (Section V-D)                          | X                                     |                                   |                                                 | X                                       | X                                     |

| Voltage Optimization<br>[37,38,74] (Section V-E)              | X                                     |                                   |                                                 | X                                       | X                                     |

| Hot Data Management<br>[41,63,70] (Section V-F)               | X                                     | X                                 | X                                               | X                                       | X                                     |

| Adaptive Error Mitigation<br>[43,65,77,78,82] (Section V-G)   | X                                     | X                                 | X                                               | X                                       | X                                     |

Cai+, "Error Characterization, Mitigation, and Recovery in Flash Memory Based Solid State Drives," Proc. IEEE 2017.

### Many Errors and Their Mitigation [PIEEE'17]

Proceedings of the IEEE, Sept. 2017

### Error Characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives

This paper reviews the most recent advances in solid-state drive (SSD) error characterization, mitigation, and data recovery techniques to improve both SSD's reliability and lifetime.

By Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu

https://arxiv.org/pdf/1706.08642

### One Issue: Read Disturb in Flash Memory

- All scaled memories are prone to read disturb errors

- DRAM

- SRAM

- Hard Disks: Adjacent Track Interference

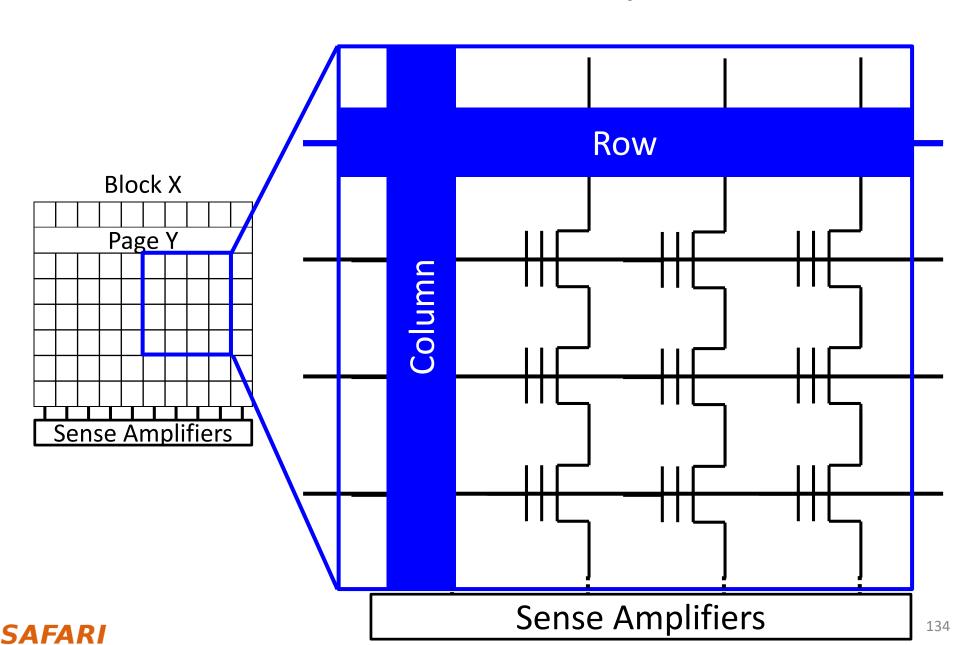

- NAND Flash

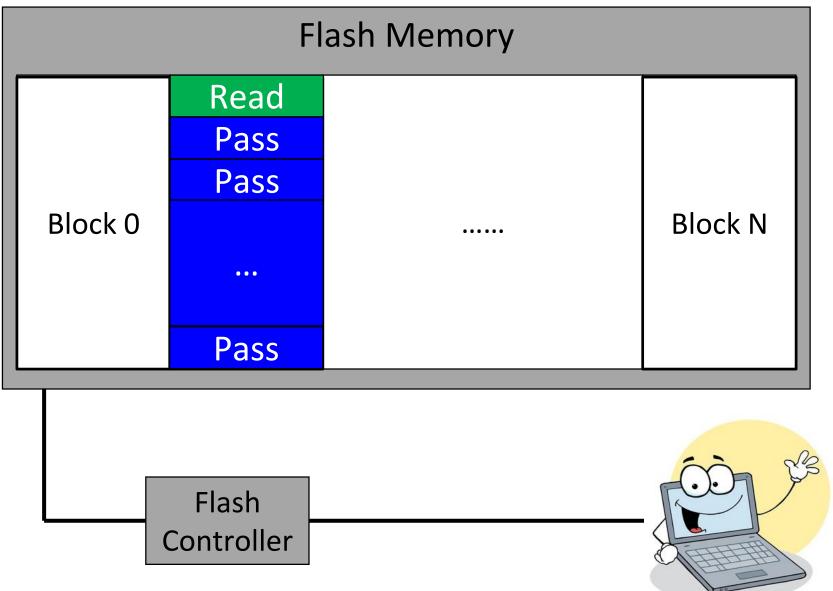

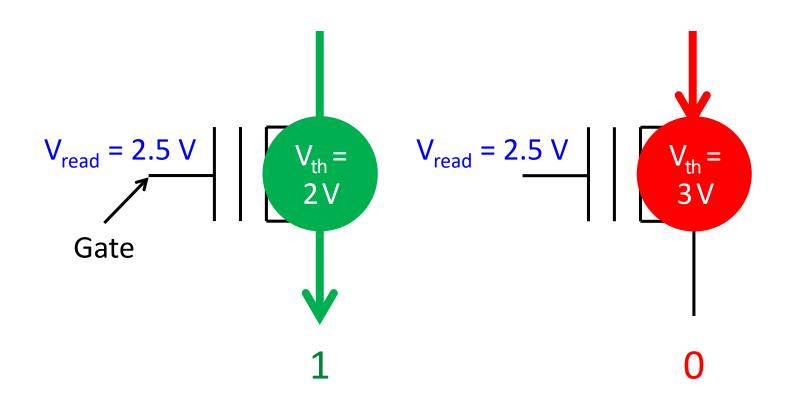

### NAND Flash Memory Background

### Flash Cell Array

### Flash Cell

Floating Gate Transistor (Flash Cell)

### Flash Read

### Flash Pass-Through

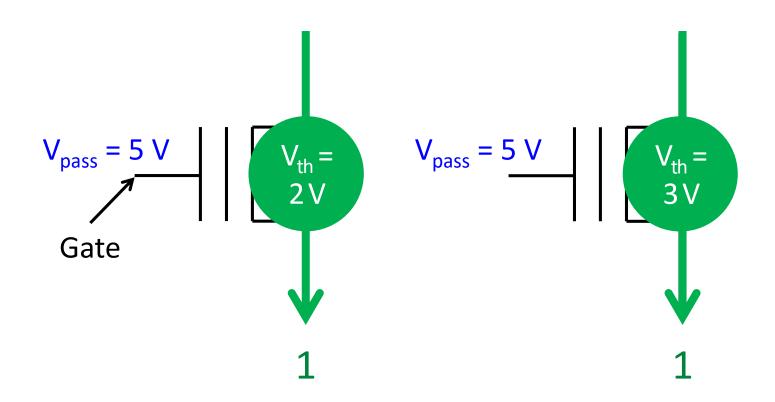

### Read from Flash Cell Array

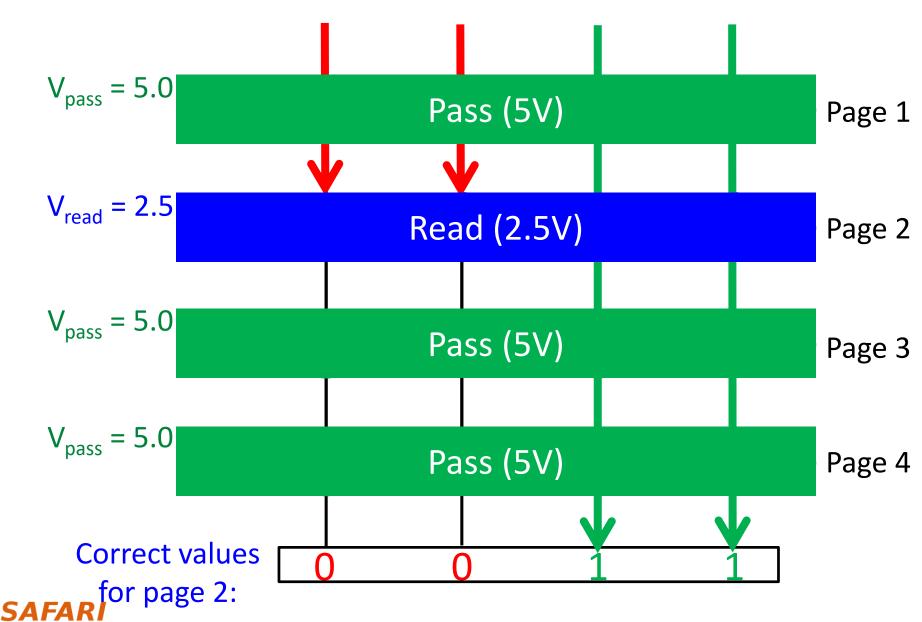

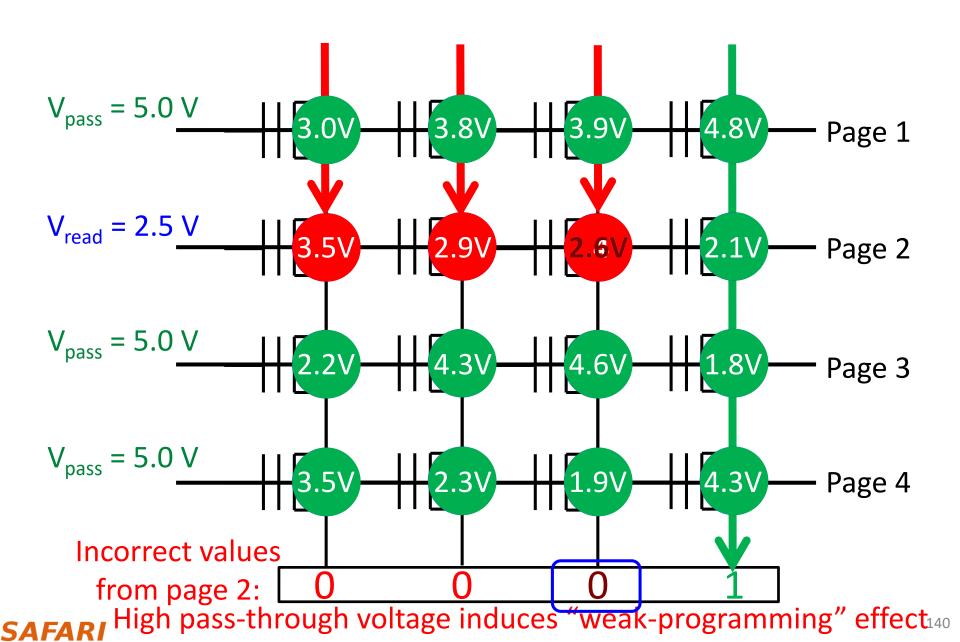

### Read Disturb Problem: "Weak Programming" Effect

### Read Disturb Problem: "Weak Programming" Effect

### Executive Summary [DSN'15]

- Read disturb errors limit flash memory lifetime today

- Apply a high pass-through voltage ( $V_{pass}$ ) to multiple pages on a read

- Repeated application of  $V_{pass}$  can alter stored values in unread pages

- We characterize read disturb on real NAND flash chips

- Slightly lowering V<sub>pass</sub> greatly reduces read disturb errors

- Some flash cells are more prone to read disturb

- Technique 1: Mitigate read disturb errors online

- $-V_{pass}$  Tuning dynamically finds and applies a lowered  $V_{pass}$  per block

- Flash memory lifetime improves by 21%

- Technique 2: Recover after failure to prevent data loss

- Read Disturb Oriented Error Recovery (RDR) selectively corrects cells more susceptible to read disturb errors

- Reduces raw bit error rate (RBER) by up to 36%

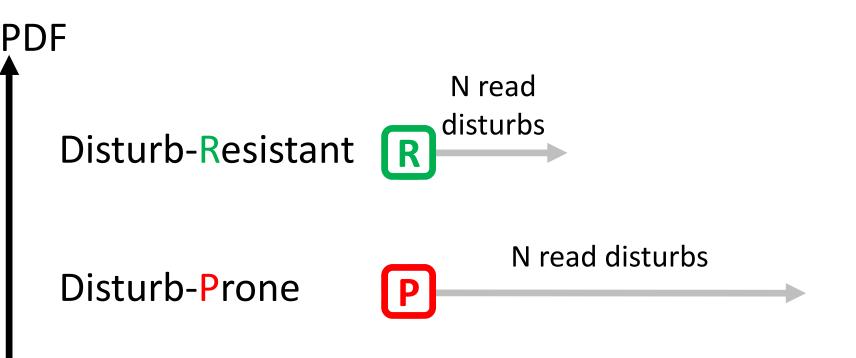

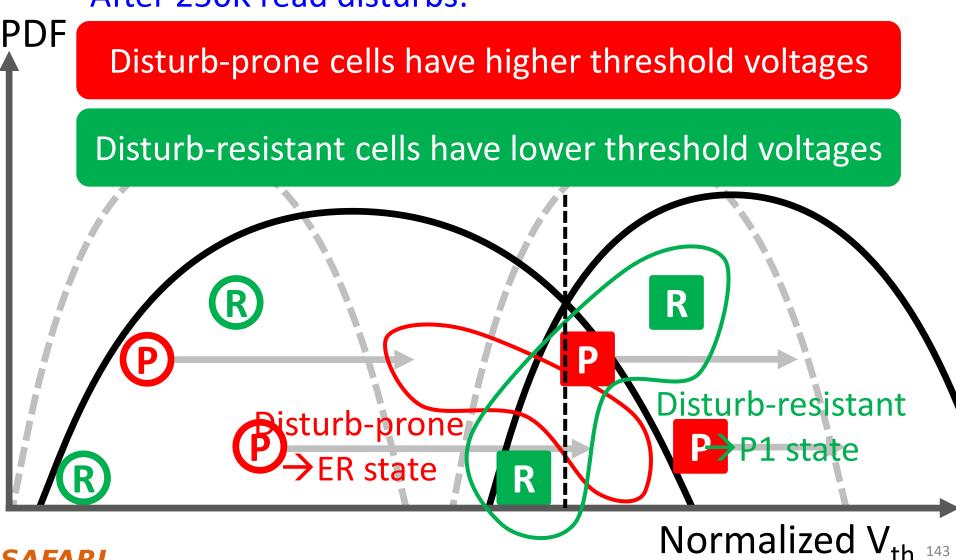

### Read Disturb Prone vs. Resistant Cells

### Observation 2: Some Flash Cells Are More Prone to Read Disturb

After 250K read disturbs:

### Read Disturb Oriented Error Recovery (RDR)

- Triggered by an uncorrectable flash error

- —Back up all valid data in the faulty block

- Disturb the faulty page 100K times (more)

- -Compare V<sub>th</sub>'s before and after read disturb

- -Select cells susceptible to flash errors  $(V_{ref}-\sigma < V_{th} < V_{ref}-\sigma)$

- Predict among these susceptible cells

- Cells with more  $V_{th}$  shifts are disturb-prone  $\rightarrow$  Higher  $V_{th}$  state

- Cells with less V<sub>th</sub> shifts are disturb-resistant → Lower V<sub>th</sub> state

Reduces total error count by up to 36% @ 1M read disturbs ECC can be used to correct the remaining errors

#### More on Flash Read Disturb Errors [DSN'15]

Yu Cai, Yixin Luo, Saugata Ghose, Erich F. Haratsch, Ken Mai, and Onur Mutlu,

"Read Disturb Errors in MLC NAND Flash Memory: Characterization and Mitigation"

Proceedings of the <u>45th Annual IEEE/IFIP International</u>

<u>Conference on Dependable Systems and Networks</u> (**DSN**), Rio de Janeiro, Brazil, June 2015.

# Read Disturb Errors in MLC NAND Flash Memory: Characterization, Mitigation, and Recovery

Yu Cai, Yixin Luo, Saugata Ghose, Erich F. Haratsch\*, Ken Mai, Onur Mutlu Carnegie Mellon University, \*Seagate Technology yucaicai@gmail.com, {yixinluo, ghose, kenmai, onur}@cmu.edu

#### Large-Scale SSD Error Analysis [sigmetrics'15]

- First large-scale field study of flash memory errors

- Justin Meza, Qiang Wu, Sanjeev Kumar, and Onur Mutlu, "A Large-Scale Study of Flash Memory Errors in the Field" Proceedings of the <u>ACM International Conference on Measurement and Modeling of Computer Systems</u> (SIGMETRICS), Portland, OR, June 2015.

[Slides (pptx) (pdf)] [Coverage at ZDNet] [Coverage on The Register] [Coverage on TechSpot] [Coverage on The Tech Report]

#### A Large-Scale Study of Flash Memory Failures in the Field

Justin Meza Carnegie Mellon University meza@cmu.edu Qiang Wu Facebook, Inc. gwu@fb.com

Sanjeev Kumar Facebook, Inc. skumar@fb.com Onur Mutlu Carnegie Mellon University onur@cmu.edu

#### Another Lecture: NAND Flash Reliability

Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu,

"Error Characterization, Mitigation, and Recovery in Flash Memory Based Solid State Drives"

**Proceedings of the IEEE**, September 2017.

Cai+, "Error Patterns in MLC NAND Flash Memory: Measurement, Characterization, and Analysis," DATE 2012.

Cai+, "Flash Correct-and-Refresh: Retention-Aware Error Management for Increased Flash Memory Lifetime," ICCD 2012.

Cai+, "Threshold Voltage Distribution in MLC NAND Flash Memory: Characterization, Analysis and Modeling," DATE 2013.

Cai+, "Error Analysis and Retention-Aware Error Management for NAND Flash Memory," Intel Technology Journal 2013.

Cai+, "Program Interference in MLC NAND Flash Memory: Characterization, Modeling, and Mitigation," ICCD 2013.

Cai+, "Neighbor-Cell Assisted Error Correction for MLC NAND Flash Memories," SIGMETRICS 2014.

Cai+,"Data Retention in MLC NAND Flash Memory: Characterization, Optimization and Recovery," HPCA 2015.

Cai+, "Read Disturb Errors in MLC NAND Flash Memory: Characterization and Mitigation," DSN 2015.

Luo+, "WARM: Improving NAND Flash Memory Lifetime with Write-hotness Aware Retention Management," MSST 2015.

Meza+, "A Large-Scale Study of Flash Memory Errors in the Field," SIGMETRICS 2015.

Luo+, "Enabling Accurate and Practical Online Flash Channel Modeling for Modern MLC NAND Flash Memory," IEEE JSAC 2016.

Cai+, "Vulnerabilities in MLC NAND Flash Memory Programming: Experimental Analysis, Exploits, and Mitigation Techniques," HPCA 2017.

Fukami+, "Improving the Reliability of Chip-Off Forensic Analysis of NAND Flash Memory Devices," DFRWS EU 2017.

Luo+, "HeatWatch: Improving 3D NAND Flash Memory Device Reliability by Exploiting Self-Recovery and Temperature-Awareness," HPCA 2018.

Luo+, "Improving 3D NAND Flash Memory Lifetime by Tolerating Early Retention Loss and Process Variation," SIGMETRICS 2018.

Cai+, "Error Characterization, Mitigation, and Recovery in Flash Memory Based Solid State Drives," Proc. IEEE 2017.

#### NAND Flash Vulnerabilities [HPCA'17]

#### HPCA, Feb. 2017

#### Vulnerabilities in MLC NAND Flash Memory Programming: Experimental Analysis, Exploits, and Mitigation Techniques

Yu Cai<sup>†</sup> Saugata Ghose<sup>†</sup> Yixin Luo<sup>‡†</sup> Ken Mai<sup>†</sup> Onur Mutlu<sup>§†</sup> Erich F. Haratsch<sup>‡</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>Seagate Technology <sup>§</sup>ETH Zürich

Modern NAND flash memory chips provide high density by storing two bits of data in each flash cell, called a multi-level cell (MLC). An MLC partitions the threshold voltage range of a flash cell into four voltage states. When a flash cell is programmed, a high voltage is applied to the cell. Due to parasitic capacitance coupling between flash cells that are physically close to each other, flash cell programming can lead to cell-to-cell program interference, which introduces errors into neighboring flash cells. In order to reduce the impact of cell-to-cell interference on the reliability of MLC NAND flash memory, flash manufacturers adopt a two-step programming method, which programs the MLC in two separate steps. First, the flash memory partially programs the least significant bit of the MLC to some intermediate threshold voltage. Second, it programs the most significant bit to bring the MLC up to its full voltage state.

In this paper, we demonstrate that two-step programming exposes new reliability and security vulnerabilities. We expe-

belongs to a different flash memory *page* (the unit of data programmed and read at the same time), which we refer to, respectively, as the least significant bit (LSB) page and the most significant bit (MSB) page [5].

A flash cell is programmed by applying a large voltage on the control gate of the transistor, which triggers charge transfer into the floating gate, thereby increasing the threshold voltage. To precisely control the threshold voltage of the cell, the flash memory uses *incremental step pulse programming* (ISPP) [12, 21, 25, 41]. ISPP applies multiple short pulses of the programming voltage to the control gate, in order to increase the cell threshold voltage by some small voltage amount ( $V_{step}$ ) after each step. Initial MLC designs programmed the threshold voltage in *one shot*, issuing all of the pulses back-to-back to program *both* bits of data at the same time. However, as flash memory scales down, the distance between neighboring flash cells decreases, which

https://people.inf.ethz.ch/omutlu/pub/flash-memory-programming-vulnerabilities hpca17.pdf

#### NAND Flash Errors: A Modern Survey

Proceedings of the IEEE, Sept. 2017

### Error Characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives

This paper reviews the most recent advances in solid-state drive (SSD) error characterization, mitigation, and data recovery techniques to improve both SSD's reliability and lifetime.

By Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu

https://arxiv.org/pdf/1706.08642

#### Summary: Memory Reliability and Security

- Memory reliability is reducing

- Reliability issues open up security vulnerabilities

- Very hard to defend against

- Rowhammer is an example

- Its implications on system security research are tremendous & exciting

- Good news: We have a lot more to do.

- Understand: Solid methodologies for failure modeling and discovery

- Modeling based on real device data small scale and large scale

- Architect: Principled co-architecting of system and memory

- Good partitioning of duties across the stack

- Design & Test: Principled electronic design, automation, testing

- High coverage and good interaction with system reliability methods

# Other Works on Flash Memory

#### NAND Flash Error Model

#### **Experimentally characterize and model dominant errors**

Cai et al., "Error Patterns in MLC NAND Flash Memory: Measurement, Characterization, and Analysis", **DATE 2012**Luo et al., "Enabling Accurate and Practical Online Flash Channel Modeling for Modern MLC NAND Flash Memory", **JSAC 2016**

Cai et al., "Threshold voltage distribution in MLC NAND Flash Memory: Characterization, Analysis, and Modeling", **DATE 2013**

Cai et al., "Vulnerabilities in MLC NAND Flash Memory Programming: Experimental Analysis, Exploits, and Mitigation Techniques", **HPCA 2017**  Cai et al., "Program Interference in MLC NAND Flash Memory: Characterization, Modeling, and Mitigation", ICCD 2013

Cai et al., "Neighbor-Cell Assisted Error Correction in MLC NAND Flash Memories", **SIGMETRICS 2014**

Cai et al., "Read Disturb Errors in MLC NAND Flash Memory: Characterization and Mitigation", **DSN 2015**

Cai et al., "Flash Correct-and-Refresh: Retention-aware error management for increased flash memory lifetime", ICCD 2012

Cai et al., "Error Analysis and Retention-Aware Error Management for NAND Flash Memory, **ITJ 2013**

Cai et al., "Data Retention in MLC NAND Flash Memory: Characterization, Optimization and Recovery" , **HPCA 2015**

#### Threshold Voltage Distribution

Yu Cai, Erich F. Haratsch, Onur Mutlu, and Ken Mai, "Threshold Voltage Distribution in MLC NAND Flash Memory: Characterization, Analysis and Modeling" Proceedings of the <u>Design, Automation, and Test in Europe</u> Conference (DATE), Grenoble, France, March 2013. <u>Slides</u> (ppt)

## Threshold Voltage Distribution in MLC NAND Flash Memory: Characterization, Analysis, and Modeling

Yu Cai<sup>1</sup>, Erich F. Haratsch<sup>2</sup>, Onur Mutlu<sup>1</sup> and Ken Mai<sup>1</sup>

<sup>1</sup>DSSC, Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA

<sup>2</sup>LSI Corporation, 1110 American Parkway NE, Allentown, PA

<sup>1</sup>{yucai, onur, kenmai}@andrew.cmu.edu, <sup>2</sup>erich.haratsch@lsi.com

#### Program Interference and Vref Prediction

Yu Cai, Onur Mutlu, Erich F. Haratsch, and Ken Mai,

"Program Interference in MLC NAND Flash Memory:

Characterization, Modeling, and Mitigation"

Proceedings of the 31st IEEE International Conference on

Computer Design (ICCD), Asheville, NC, October 2013.

Slides (pptx) (pdf) Lightning Session Slides (pdf)

#### Program Interference in MLC NAND Flash Memory: Characterization, Modeling, and Mitigation

Yu Cai<sup>1</sup>, Onur Mutlu<sup>1</sup>, Erich F. Haratsch<sup>2</sup> and Ken Mai<sup>1</sup>

Data Storage Systems Center, Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA

LSI Corporation, San Jose, CA

yucaicai@gmail.com, {omutlu, kenmai}@andrew.cmu.edu

#### Neighbor-Assisted Error Correction

Yu Cai, Gulay Yalcin, Onur Mutlu, Eric Haratsch, Osman Unsal,

Adrian Cristal, and Ken Mai,

"Neighbor-Cell Assisted Error Correction for MLC NAND Flash Memories"

Proceedings of the <u>ACM International Conference on</u>

<u>Measurement and Modeling of Computer Systems</u>

(**SIGMETRICS**), Austin, TX, June 2014. <u>Slides (ppt) (pdf)</u>

## Neighbor-Cell Assisted Error Correction for MLC NAND Flash Memories

Yu Cai<sup>1</sup>, Gulay Yalcin<sup>2</sup>, Onur Mutlu<sup>1</sup>, Erich F. Haratsch<sup>4</sup>,

Osman Unsal<sup>2</sup>, Adrian Cristal<sup>2,3</sup>, and Ken Mai<sup>1</sup>

<sup>1</sup>Electrical and Computer Engineering Department, Carnegie Mellon University

<sup>2</sup>Barcelona Supercomputing Center, Spain

<sup>3</sup>IIIA – CSIC – Spain National Research Council

<sup>4</sup>LSI Corporation yucaicai@gmail.com, {omutlu, kenmai}@ece.cmu.edu, {gulay.yalcin, adrian.cristal, osman.unsal}@bsc.es

#### Data Retention

Yu Cai, Yixin Luo, Erich F. Haratsch, Ken Mai, and Onur Mutlu,

"Data Retention in MLC NAND Flash Memory: Characterization,

Optimization and Recovery"

Proceedings of the 21st International Symposium on High-Performance

Computer Architecture (HPCA), Bay Area, CA, February 2015.

[Slides (pptx) (pdf)]

# Data Retention in MLC NAND Flash Memory: Characterization, Optimization, and Recovery

Yu Cai, Yixin Luo, Erich F. Haratsch\*, Ken Mai, Onur Mutlu

Carnegie Mellon University, \*LSI Corporation

yucaicai@gmail.com, yixinluo@cs.cmu.edu, erich.haratsch@lsi.com, {kenmai, omutlu}@ece.cmu.edu

#### SSD Error Analysis in the Field

- First large-scale field study of flash memory errors

- Justin Meza, Qiang Wu, Sanjeev Kumar, and Onur Mutlu,

"A Large-Scale Study of Flash Memory Errors in the Field"

Proceedings of the ACM International Conference on

Measurement and Modeling of Computer Systems

(SIGMETRICS), Portland, OR, June 2015.

[Slides (pptx) (pdf)] [Coverage at ZDNet] [Coverage on The Register] [Coverage on TechSpot] [Coverage on The Tech Report]

#### A Large-Scale Study of Flash Memory Failures in the Field

Justin Meza Carnegie Mellon University meza@cmu.edu Qiang Wu Facebook, Inc. qwu@fb.com Sanjeev Kumar Facebook, Inc. skumar@fb.com Onur Mutlu Carnegie Mellon University onur@cmu.edu

#### Flash Memory Programming Vulnerabilities

Yu Cai, Saugata Ghose, Yixin Luo, Ken Mai, Onur Mutlu, and Erich F. Haratsch,

"Vulnerabilities in MLC NAND Flash Memory Programming:

Experimental Analysis, Exploits, and Mitigation Techniques"

Proceedings of the 23rd International Symposium on High-Performance

Computer Architecture (HPCA) Industrial Session, Austin, TX, USA,

February 2017.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

## **Vulnerabilities in MLC NAND Flash Memory Programming: Experimental Analysis, Exploits, and Mitigation Techniques**

Yu Cai $^{\dagger}$  Saugata Ghose $^{\dagger}$  Yixin Luo $^{\ddagger\dagger}$  Ken Mai $^{\dagger}$  Onur Mutlu $^{\S\dagger}$  Erich F. Haratsch $^{\ddagger}$   $^{\dagger}$  Carnegie Mellon University  $^{\ddagger}$  Seagate Technology  $^{\S}$  ETH Zürich

#### Accurate and Online Channel Modeling

Yixin Luo, Saugata Ghose, Yu Cai, Erich F. Haratsch, and <u>Onur Mutlu</u>,

"Enabling Accurate and Practical Online Flash Channel Modeling

for Modern MLC NAND Flash Memory"

to appear in <u>IEEE Journal on Selected Areas in Communications</u> (JSAC),

2016.

# Enabling Accurate and Practical Online Flash Channel Modeling for Modern MLC NAND Flash Memory

Yixin Luo, Saugata Ghose, Yu Cai, Erich F. Haratsch, Onur Mutlu

#### 3D NAND Flash Reliability I [HPCA'18]

Yixin Luo, Saugata Ghose, Yu Cai, Erich F. Haratsch, and Onur Mutlu,

"HeatWatch: Improving 3D NAND Flash Memory Device

Reliability by Exploiting Self-Recovery and Temperature-Awareness"

Proceedings of the <u>24th International Symposium on High-Performance</u> <u>Computer Architecture</u> (**HPCA**), Vienna, Austria, February 2018. [<u>Lightning Talk Video</u>]

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

## HeatWatch: Improving 3D NAND Flash Memory Device Reliability by Exploiting Self-Recovery and Temperature Awareness

```

Yixin Luo<sup>†</sup> Saugata Ghose<sup>†</sup> Yu Cai<sup>‡</sup> Erich F. Haratsch<sup>‡</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>Seagate Technology <sup>§</sup>ETH Zürich

```

#### 3D NAND Flash Reliability II [SIGMETRICS'18]

Yixin Luo, Saugata Ghose, Yu Cai, Erich F. Haratsch, and Onur Mutlu, "Improving 3D NAND Flash Memory Lifetime by Tolerating Early Retention Loss and Process Variation" Proceedings of the <u>ACM International Conference on Measurement and Modeling of Computer Systems</u> (SIGMETRICS), Irvine, CA, USA, June 2018.

[Abstract]

## Improving 3D NAND Flash Memory Lifetime by Tolerating Early Retention Loss and Process Variation

Yixin Luo<sup>†</sup> Saugata Ghose<sup>†</sup> Yu Cai<sup>†</sup> Erich F. Haratsch<sup>‡</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>Seagate Technology <sup>§</sup>ETH Zürich

# Backup Slides

## More on DRAM Refresh

#### Tackling Refresh: Solutions

- Parallelize refreshes with accesses [Chang+ HPCA'14]

- Eliminate unnecessary refreshes [Liu+ ISCA'12]

- Exploit device characteristics

- Exploit data and application characteristics

- Reduce refresh rate and detect+correct errors that occur [Khan+ SIGMETRICS'14]

- Understand retention time behavior in DRAM [Liu+ ISCA'13]

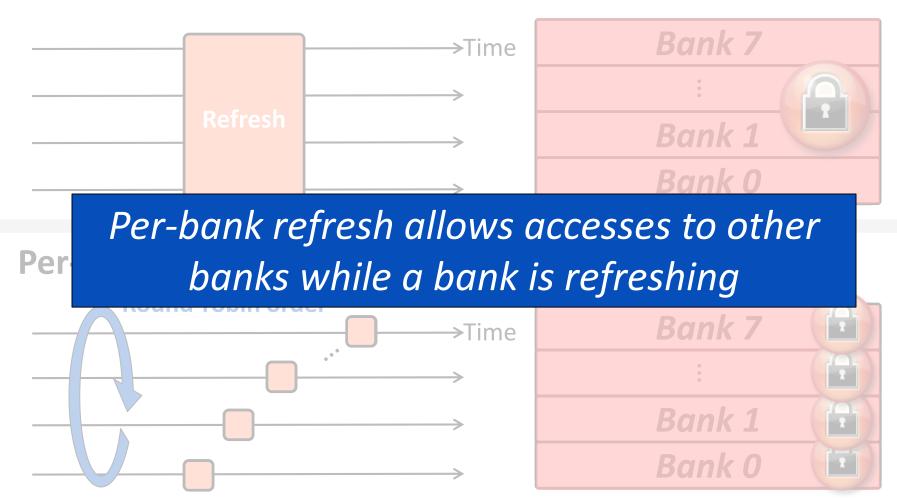

#### **Summary: Refresh-Access Parallelization**

- DRAM refresh interferes with memory accesses

- Degrades system performance and energy efficiency

- Becomes exacerbated as DRAM density increases

- Goal: Serve memory accesses in parallel with refreshes to reduce refresh interference on demand requests

- Our mechanisms:

- 1. Enable more parallelization between refreshes and accesses across different banks with new per-bank refresh scheduling algorithms

- 2. Enable serving accesses concurrently with refreshes in the same bank by exploiting parallelism across DRAM subarrays

- Improve system performance and energy efficiency for a wide variety of different workloads and DRAM densities

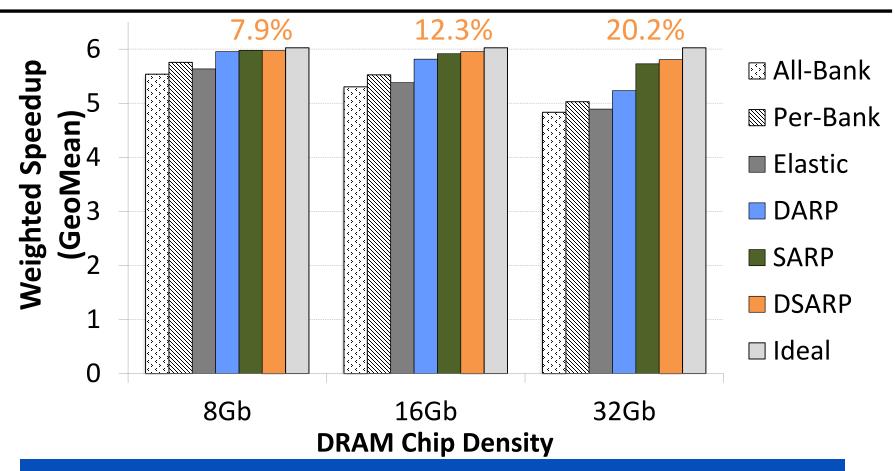

- 20.2% and 9.0% for 8-core systems using 32Gb DRAM at low cost

- Very close to the ideal scheme without refreshes

#### **Refresh Penalty**

#### **Existing Refresh Modes**

All-bank refresh in commodity DRAM (DDRx)

#### **Shortcomings of Per-Bank Refresh**

- Problem 1: Refreshes to different banks are scheduled in a strict round-robin order

- The static ordering is hardwired into DRAM chips

- Refreshes busy banks with many queued requests when other banks are idle

- <u>Key idea</u>: Schedule per-bank refreshes to idle banks opportunistically in a dynamic order

#### Our First Approach: DARP

- Dynamic Access-Refresh Parallelization (DARP)

- An improved scheduling policy for per-bank refreshes

- Exploits refresh scheduling flexibility in DDR DRAM

- Component 1: Out-of-order per-bank refresh

- Avoids poor static scheduling decisions

- Dynamically issues per-bank refreshes to idle banks

- Component 2: Write-Refresh Parallelization

- Avoids refresh interference on latency-critical reads

- Parallelizes refreshes with a batch of writes

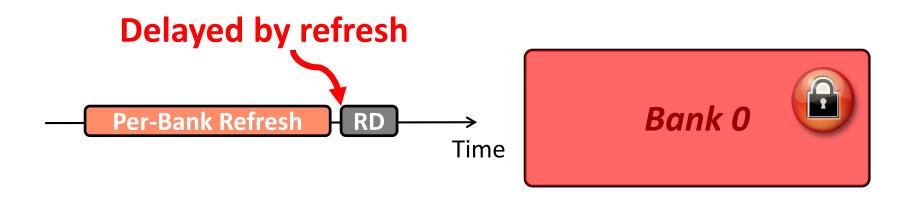

#### **Shortcomings of Per-Bank Refresh**

Problem 2: Banks that are being refreshed cannot concurrently serve memory requests

#### **Shortcomings of Per-Bank Refresh**

- Problem 2: Refreshing banks cannot concurrently serve memory requests

- <u>Key idea</u>: Exploit subarrays within a bank to parallelize refreshes and accesses across subarrays

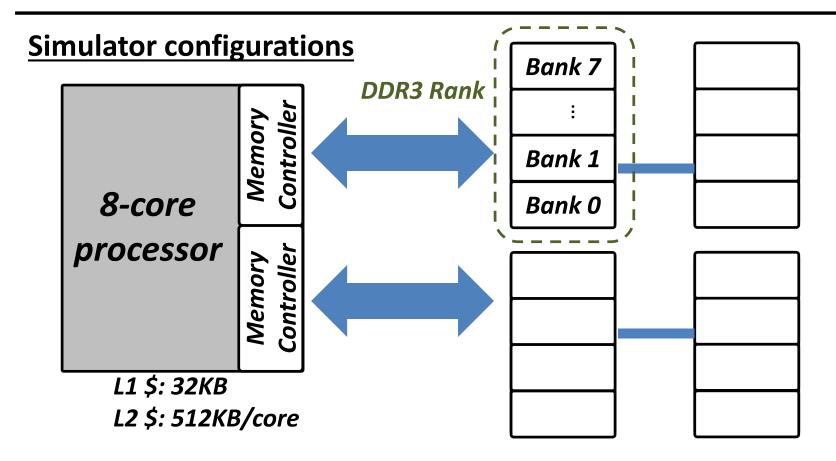

#### Methodology

- 100 workloads: SPEC CPU2006, STREAM, TPC-C/H, random access

- System performance metric: Weighted speedup

#### **Comparison Points**

- All-bank refresh [DDR3, LPDDR3, ...]

- Per-bank refresh [LPDDR3]

- Elastic refresh [Stuecheli et al., MICRO '10]:

- Postpones refreshes by a time delay based on the predicted rank idle time to avoid interference on memory requests

- Proposed to schedule all-bank refreshes without exploiting per-bank refreshes

- Cannot parallelize refreshes and accesses within a rank

- Ideal (no refresh)

#### **System Performance**

2. Consistent system performance improvement across DRAM densities (within **0.9%, 1.2%, and 3.8%** of ideal)

#### **Energy Efficiency**

Consistent reduction on energy consumption

#### More Information on Refresh-Access Parallelization

Kevin Chang, Donghyuk Lee, Zeshan Chishti, Alaa Alameldeen, Chris Wilkerson, Yoongu Kim, and Onur Mutlu,

"Improving DRAM Performance by Parallelizing Refreshes with

Proceedings of the <u>20th International Symposium on High-Performance</u> <u>Computer Architecture</u> (**HPCA**), Orlando, FL, February 2014.

[Summary] [Slides (pptx) (pdf)]

# Reducing Performance Impact of DRAM Refresh by Parallelizing Refreshes with Accesses

Kevin Kai-Wei Chang Donghyuk Lee Zeshan Chishti†

Alaa R. Alameldeen† Chris Wilkerson† Yoongu Kim Onur Mutlu

Carnegie Mellon University †Intel Labs

Accesses"

#### Tackling Refresh: Solutions

- Parallelize refreshes with accesses [Chang+ HPCA'14]

- Eliminate unnecessary refreshes [Liu+ ISCA'12]

- Exploit device characteristics

- Exploit data and application characteristics

- Reduce refresh rate and detect+correct errors that occur [Khan+ SIGMETRICS'14]

- Understand retention time behavior in DRAM [Liu+ ISCA'13]

#### Most Refreshes Are Unnecessary

Retention Time Profile of DRAM looks like this:

64-128ms

>256ms

128-256ms

#### RAIDR: Eliminating Unnecessary Refreshes

#### 64-128ms

#### >256ms

1.25KB storage in controller for 32GB DRAM memory

#### 128-256ms

Can reduce refreshes by ~75%

→ reduces energy consumption and improves performance

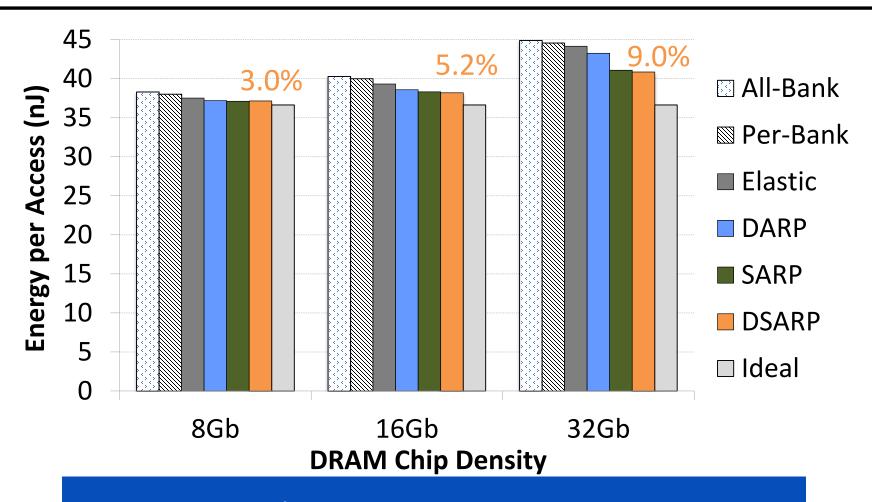

#### RAIDR: Baseline Design

Refresh control is in DRAM in today's auto-refresh systems

RAIDR can be implemented in either the controller or DRAM

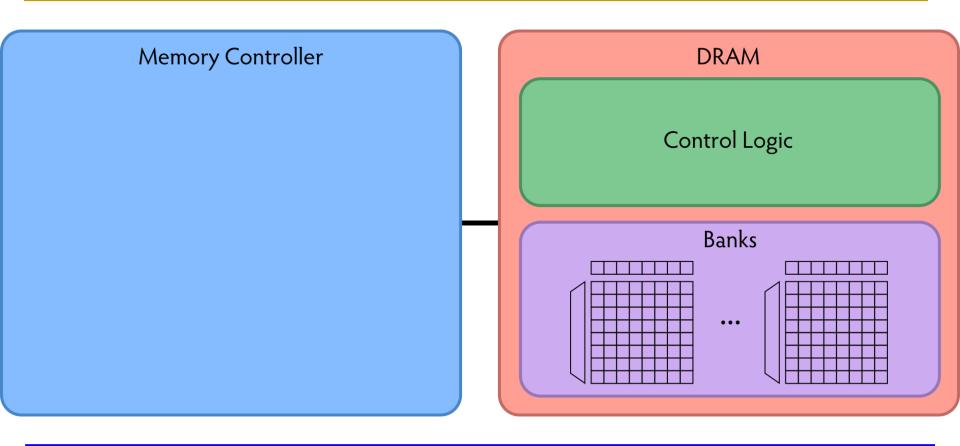

#### RAIDR in Memory Controller: Option 1

#### Overhead of RAIDR in DRAM controller:

1.25 KB Bloom Filters, 3 counters, additional commands issued for per-row refresh (all accounted for in evaluations)

## RAIDR in DRAM Chip: Option 2

#### Overhead of RAIDR in DRAM chip:

Per-chip overhead: 20B Bloom Filters, 1 counter (4 Gbit chip)

Total overhead: 1.25KB Bloom Filters, 64 counters (32 GB DRAM)

#### RAIDR: Results and Takeaways

- System: 32GB DRAM, 8-core; SPEC, TPC-C, TPC-H workloads

- RAIDR hardware cost: 1.25 kB (2 Bloom filters)

- Refresh reduction: 74.6%

- Dynamic DRAM energy reduction: 16%

- Idle DRAM power reduction: 20%

- Performance improvement: 9%

- Benefits increase as DRAM scales in density

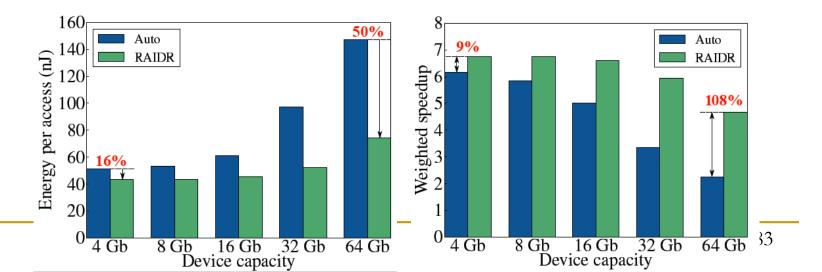

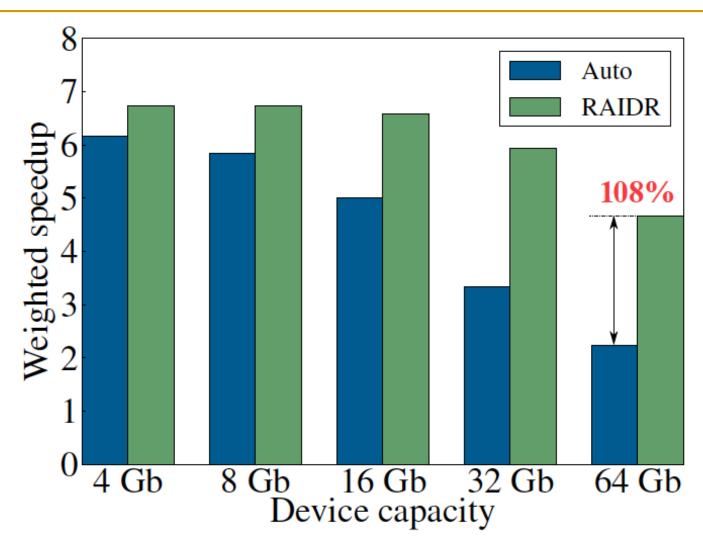

#### DRAM Device Capacity Scaling: Performance

RAIDR performance benefits increase with DRAM chip capacity

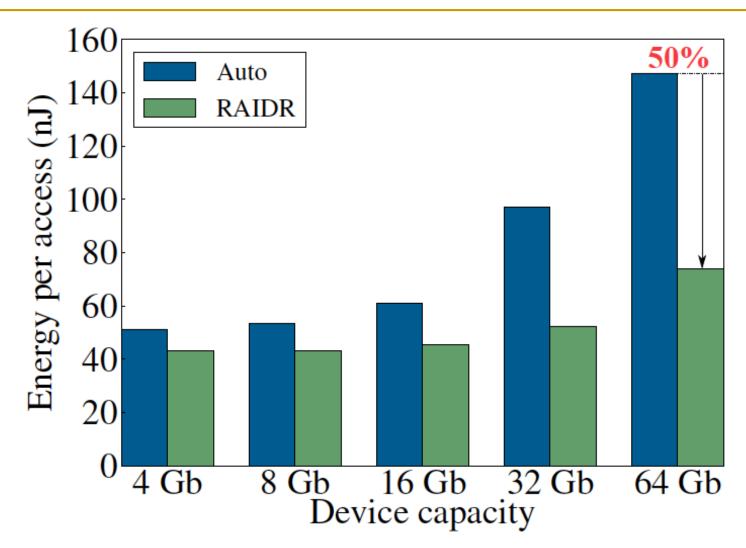

#### DRAM Device Capacity Scaling: Energy

RAIDR energy benefits increase with DRAM chip capacity

## RAIDR: Eliminating Unnecessary Refreshes

Observation: Most DRAM rows can be refreshed much less often

without losing data [Kim+, EDL'09][Liu+ ISCA'13]

Key idea: Refresh rows containing weak cells more frequently, other rows less frequently

2. Binning: Store rows into bins by retention time in memory controller Efficient storage with Bloom Filters (only 1.25KB for 32GB memory)

Refreshing: Memory conuclidation ifferent rates

Results: 8-core, 32GB, SPEC, TPC-C, TPC-H

74 6% refresh reduction @ 1.25KB storage

74 6% dynamic/idle power reduction

74 6% refresh reduction @ 1.25KB storage 3. Refreshing: Memory controller refreshes rows in different bins at

- Benefits increase with DRAM capacity

$\approx 1000$  cells @ 256 ms

$\approx 30$  cells @ 128 ms

$^{10}_{2}^{60}$  32 GB DRAM

#### More on RAIDR

Jamie Liu, Ben Jaiyen, Richard Veras, and Onur Mutlu, "RAIDR: Retention-Aware Intelligent DRAM Refresh" Proceedings of the <u>39th International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2012. <u>Slides (pdf)</u>

#### RAIDR: Retention-Aware Intelligent DRAM Refresh

Jamie Liu Ben Jaiyen Richard Veras Onur Mutlu Carnegie Mellon University

### Tackling Refresh: Solutions

- Parallelize refreshes with accesses [Chang+ HPCA'14]

- Eliminate unnecessary refreshes [Liu+ ISCA'12]

- Exploit device characteristics

- Exploit data and application characteristics

- Reduce refresh rate and detect+correct errors that occur [Khan+ SIGMETRICS'14]

- Understand retention time behavior in DRAM [Liu+ ISCA'13]

### Motivation: Understanding Retention

- Past works require accurate and reliable measurement of retention time of each DRAM row

- To maintain data integrity while reducing refreshes

- Assumption: worst-case retention time of each row can be determined and stays the same at a given temperature

- Some works propose writing all 1's and 0's to a row, and measuring the time before data corruption

- Question:

- Can we reliably and accurately determine retention times of all DRAM rows?

189

## Two Challenges to Retention Time Profiling

Data Pattern Dependence (DPD) of retention time

Variable Retention Time (VRT) phenomenon

## An Example VRT Cell

### VRT: Implications on Profiling Mechanisms

- Problem 1: There does not seem to be a way of determining if a cell exhibits VRT without actually observing a cell exhibiting VRT

- VRT is a memoryless random process [Kim+ JJAP 2010]

- Problem 2: VRT complicates retention time profiling by DRAM manufacturers

- Exposure to very high temperatures can induce VRT in cells that were not previously susceptible

- → can happen during soldering of DRAM chips

- → manufacturer's retention time profile may not be accurate

- One option for future work: Use ECC to continuously profile DRAM online while aggressively reducing refresh rate

- Need to keep ECC overhead in check

#### More on DRAM Retention Analysis

Jamie Liu, Ben Jaiyen, Yoongu Kim, Chris Wilkerson, and Onur Mutlu, "An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms" Proceedings of the 40th International Symposium on Computer Architecture (ISCA), Tel-Aviv, Israel, June 2013. Slides (ppt) Slides (pdf)

# An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms

Jamie Liu<sup>\*</sup>

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

jamiel@alumni.cmu.edu

Ben Jaiyen<sup>\*</sup>

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

bjaiyen@alumni.cmu.edu

Yoongu Kim

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

yoonguk@ece.cmu.edu

Chris Wilkerson

Intel Corporation

2200 Mission College Blvd.

Santa Clara, CA 95054

chris.wilkerson@intel.com

Onur Mutlu

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

onur@cmu.edu

### Tackling Refresh: Solutions

- Parallelize refreshes with accesses [Chang+ HPCA'14]

- Eliminate unnecessary refreshes [Liu+ ISCA'12]

- Exploit device characteristics

- Exploit data and application characteristics

- Reduce refresh rate and detect+correct errors that occur [Khan+ SIGMETRICS'14]

- Understand retention time behavior in DRAM [Liu+ ISCA'13]

#### **Towards an Online Profiling System**

#### **Key Observations:**

- Testing alone cannot detect all possible failures

- Combination of ECC and other mitigation techniques is much more effective

- But degrades performance

- Testing can help to reduce the ECC strength

- Even when starting with a higher strength ECC

#### **Towards an Online Profiling System**

Run tests periodically after a short interval at smaller regions of memory

#### More on Online Profiling of DRAM

Samira Khan, Donghyuk Lee, Yoongu Kim, Alaa Alameldeen, Chris Wilkerson, and Onur Mutlu,

"The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study"

Proceedings of the <u>ACM International Conference on Measurement and</u> Modeling of Computer Systems (SIGMETRICS), Austin, TX, June 2014. [Slides (pptx) (pdf)] [Poster (pptx) (pdf)] [Full data sets]

#### The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study

Samira Khan⁺∗ samirakhan@cmu.edu

Donghyuk Lee<sup>†</sup> donghyuk1@cmu.edu

Yoongu Kim<sup>†</sup> yoongukim@cmu.edu

Alaa R. Alameldeen\* alaa.r.alameldeen@intel.com chris.wilkerson@intel.com

Chris Wilkerson\*

Onur Mutlu<sup>†</sup> onur@cmu.edu

<sup>†</sup>Carnegie Mellon University

\*Intel Labs

# How Do We Make RAIDR Work in the Presence of the VRT Phenomenon?

#### Making RAIDR Work w/ Online Profiling & ECC

Moinuddin Qureshi, Dae Hyun Kim, Samira Khan, Prashant Nair, and Onur Mutlu,