# How to Build an Impactful Research Group

Onur Mutlu

omutlu@gmail.com

https://people.inf.ethz.ch/omutlu

19 July 2020

**DAC Early Career Workshop Panel**

**Carnegie Mellon**

# Intro & Research Group

#### A Bit About Myself

#### Onur Mutlu

- Full Professor @ ETH Zurich, since September 2015

- □ Strecker Professor @ Carnegie Mellon University ECE/CS, 2009-2016, 2016-...

- PhD from UT-Austin, worked at Google, VMware, Microsoft Research, Intel, AMD

- https://people.inf.ethz.ch/omutlu/

- omutlu@gmail.com (Best way to reach me)

- https://people.inf.ethz.ch/omutlu/projects.htm

#### Research and Teaching in:

- Computer architecture, computer systems, hardware security, bioinformatics

- Memory and storage systems

- Hardware security, safety, predictability

- Fault tolerance

- Hardware/software cooperation

- Architectures for bioinformatics, health, medicine

- **...**

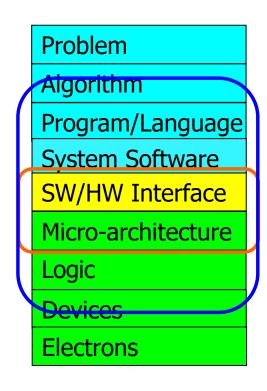

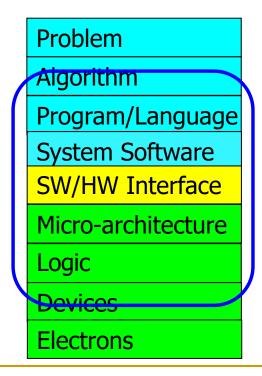

#### The Transformation Hierarchy

Computer Architecture (expanded view)

Computer Architecture (narrow view)

#### Axiom

To achieve the highest energy efficiency and performance:

#### we must take the expanded view

of computer architecture

Co-design across the hierarchy:

Algorithms to devices

Specialize as much as possible within the design goals

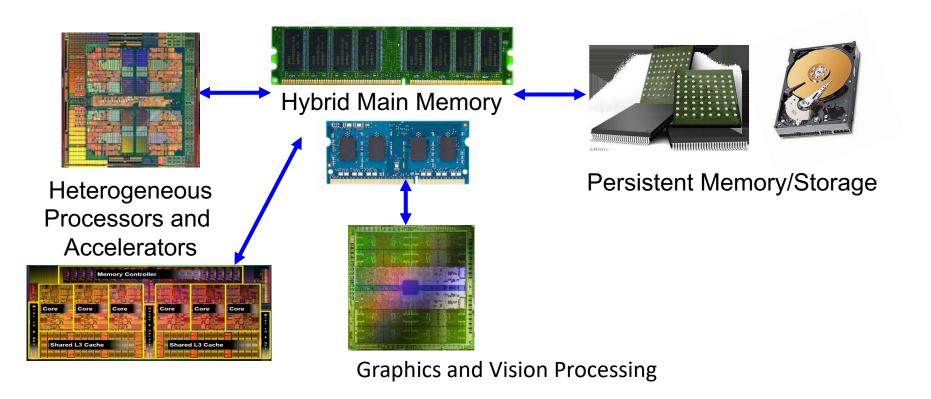

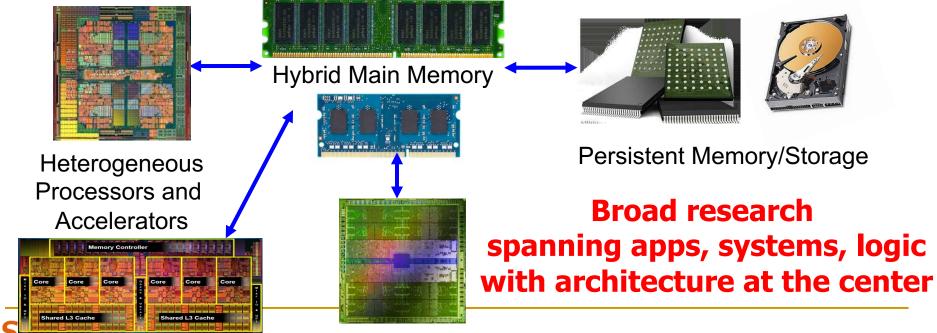

#### Current Research Mission

#### Computer architecture, HW/SW, systems, bioinformatics, security

#### **Build fundamentally better architectures**

#### Current Research Focus Areas

#### Research Focus: Computer architecture, HW/SW, bioinformatics, security

- Memory and storage (DRAM, flash, emerging), interconnects

- Heterogeneous & parallel systems, GPUs, systems for data analytics

- System/architecture interaction, new execution models, new interfaces

- Hardware security, energy efficiency, fault tolerance, performance

- Genome sequence analysis & assembly algorithms and architectures

- Biologically inspired systems & system design for bio/medicine

**Graphics and Vision Processing**

#### Research & Teaching: Some Overview Talks

https://www.youtube.com/onurmutlulectures

- Future Computing Architectures

- https://www.youtube.com/watch?v=kgiZISOcGFM&list=PL5Q2soXY2Zi8D 5MGV6EnXEJHnV2YFBJI&index=1

- Enabling In-Memory Computation

- https://www.youtube.com/watch?v=njX 14584Jw&list=PL5Q2soXY2Zi8D 5MGV6EnXEJHnV2YFBJl&index=16

- Accelerating Genome Analysis

- https://www.youtube.com/watch?v=hPnSmfwu2-A&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=9

- Rethinking Memory System Design

- https://www.youtube.com/watch?v=F7xZLNMIY1E&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=3

- Intelligent Architectures for Intelligent Machines

- https://www.youtube.com/watch?v=n8Aj\_A0WSq8&list=PL5Q2soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=22

#### Accelerated Memory Course (~6.5 hours)

#### ACACES 2018

- Memory Systems and Memory-Centric Computing Systems

- Taught by Onur Mutlu July 9-13, 2018

- □ ~6.5 hours of lectures

- Website for the Course including Videos, Slides, Papers

- https://people.inf.ethz.ch/omutlu/acaces2018.html

- https://www.youtube.com/playlist?list=PL5Q2soXY2Zi-HXxomthrpDpMJm05P6J9x

#### All Papers are at:

- https://people.inf.ethz.ch/omutlu/projects.htm

- Final lecture notes and readings (for all topics)

#### An Interview on Research and Education

- Computing Research and Education (@ ISCA 2019)

- https://www.youtube.com/watch?v=8ffSEKZhmvo&list=PL5Q2 soXY2Zi\_4oP9LdL3cc8G6NIjD2Ydz

- Maurice Wilkes Award Speech (10 minutes)

- https://www.youtube.com/watch?v=tcQ3zZ3JpuA&list=PL5Q2 soXY2Zi8D\_5MGV6EnXEJHnV2YFBJl&index=15

#### SAFARI Research Group

Think BIG, Aim HIGH!

https://safari.ethz.ch

#### SAFARI Newsletter April 2020 Edition

https://safari.ethz.ch/safari-newsletter-april-2020/

View in your browser

Think Big, Aim High

Dear SAFARI friends,

# SAFARI Research Group

33 © = 1 Professor, 2 Lecturers & Senior Researchers, 3 Senior Researchers, 12 PhD Students, 5 Masters, 8 PhD/Bachelors Interns, 2 Admins

Think BIG, Aim HIGH!

SAFARI

https://safari.ethz.ch

# SAFARI Group Members @ ETH Zurich

Dr. Mohammed Alser

Dr. Lois Orosa

Dr. Yaohua Wang

Dr. Juan Gómez-Luna

7 Post-doctoral Researchers

12 PhD Students + 2 at CMU

5 Interns

8 Master's and Bachelor's Researchers

Jeremie Kim

Hasan Hassan

Minesh Patel

Ivan Puddu

Lukas Breitwieser

Giray Yaqlikci

Can Firtina

de Oliveira

Nika Mansouri

Skanda Koppula

Konstantinos Kanellopoulos

Nisa Bostanci

Ataberk Olgun

Rokneddin Azizi

Christina Giannoula

Taha Shahroodi

#### SAFARI PhD and Post-Doc Alumni

- https://safari.ethz.ch/safari-alumni/

- Nandita Vijaykumar (Univ. of Toronto, Assistant Professor)

- Kevin Hsieh (Microsoft Research)

- Justin Meza (Facebook)

- Mohammed Alser (ETH Zurich)

- Yixin Luo (Google)

- Kevin Chang (Facebook)

- Rachata Ausavarungnirun (KMUNTB, Assistant Professor)

- Gennady Pekhimenko (Univ. of Toronto, Assistant Professor)

- Vivek Seshadri (Microsoft Research)

- Donghyuk Lee (NVIDIA Research)

- Yoongu Kim (Google)

- Lavanya Subramanian (Intel Labs → Facebook)

- Samira Khan (Univ. of Virginia, Assistant Professor)

- Saugata Ghose (Univ. of Illinois, Assistant Professor)

#### Example Research Topics (I)

#### Processing Data Where It Makes Sense: Enabling In-Memory Computation

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>b,c</sup>

<sup>a</sup>ETH Zürich

<sup>b</sup>Carnegie Mellon University

<sup>c</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, <a href="Processing Data Where It Makes Sense: Enabling In-Memory">"Processing Data Where It Makes Sense: Enabling In-Memory</a>

<a href="Computation">Computation</a>

Invited paper in <u>Microprocessors and Microsystems</u> (**MICPRO**), June 2019. [arXiv version]

# Example Research Topics (I)

#### A Workload and Programming Ease Driven Perspective of Processing-in-Memory

Saugata Ghose<sup>†</sup> Amirali Boroumand<sup>†</sup> Jeremie S. Kim<sup>†</sup>§ Juan Gómez-Luna<sup>§</sup> Onur Mutlu<sup>§†</sup>

†Carnegie Mellon University §ETH Zürich

Saugata Ghose, Amirali Boroumand, Jeremie S. Kim, Juan Gomez-Luna, and Onur Mutlu, "Processing-in-Memory: A Workload-Driven Perspective"

Invited Article in IBM Journal of Research & Development, Special Issue on Hardware for Artificial Intelligence, to appear in November 2019.

[Preliminary arXiv version]

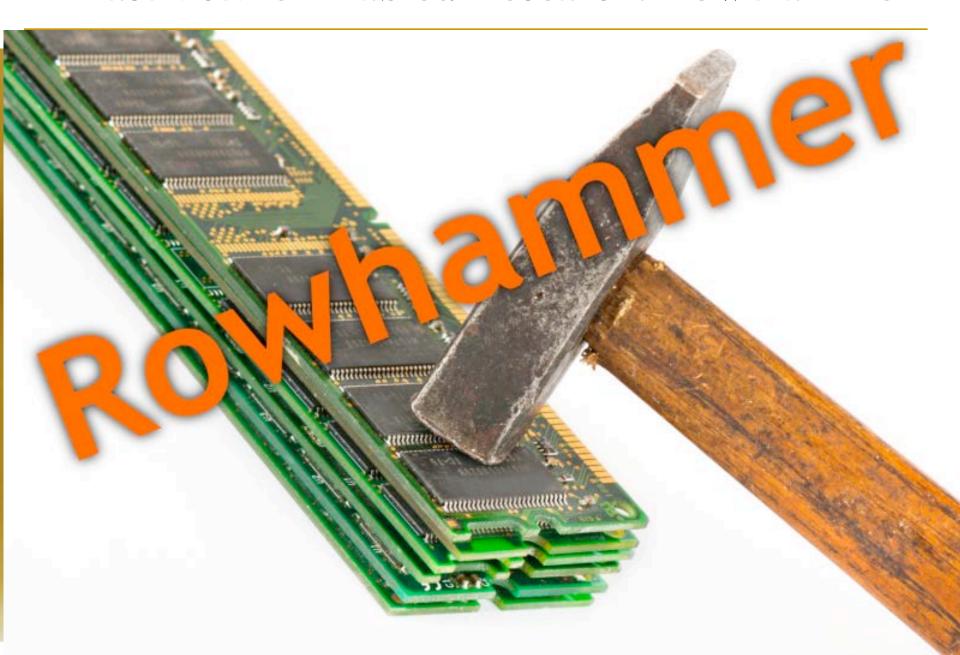

#### Example Research Topics (II)

Onur Mutlu,

"The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser"

Invited Paper in Proceedings of the <u>Design, Automation, and Test in</u> <u>Europe Conference</u> (**DATE**), Lausanne, Switzerland, March 2017. [Slides (pptx) (pdf)]

# The RowHammer Problem and Other Issues We May Face as Memory Becomes Denser

Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

https://people.inf.ethz.ch/omutlu

# Example Research Topics (III)

Onur Mutlu,

"Memory Scaling: A Systems Architecture

Perspective"

Technical talk at <u>MemCon 2013</u> (**MEMCON**), Santa Clara, CA, August 2013. [Slides (pptx) (pdf)]

[Video] [Coverage on StorageSearch]

#### Memory Scaling: A Systems Architecture Perspective

Onur Mutlu

Carnegie Mellon University

onur@cmu.edu

http://users.ece.cmu.edu/~omutlu/

#### Example Research Topics (IV)

Proceedings of the IEEE, Sept. 2017

# Error Characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives

This paper reviews the most recent advances in solid-state drive (SSD) error characterization, mitigation, and data recovery techniques to improve both SSD's reliability and lifetime.

By Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu

# Example Research Topics (V)

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

<u>IEEE Transactions on Computer-Aided Design of Integrated</u>

<u>Circuits and Systems</u> (TCAD) Special Issue on Top Picks in Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

# RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> §ETH Zürich <sup>‡</sup>Carnegie Mellon University

SAFARI 21

#### Teaching: Online Courses and Lectures

- Undergraduate Digital Design & Computer

Architecture Course Lecture

Videos (2020, 2019, 2018, 2017, 2015, 2014, 2013)

- Graduate Computer Architecture Course Lecture

Videos (2019, 2018, 2017, 2015, 2013)

- Seminar in Computer Architecture Course Lecture

Videos (Spring 2020, Fall 2019, Spring 2019, 2018)

- Parallel Computer Architecture Course

Materials (Lecture Videos)

- https://people.inf.ethz.ch/omutlu/teaching.html

- https://www.youtube.com/onurmutlulectures

- https://www.youtube.com/user/cmu18447

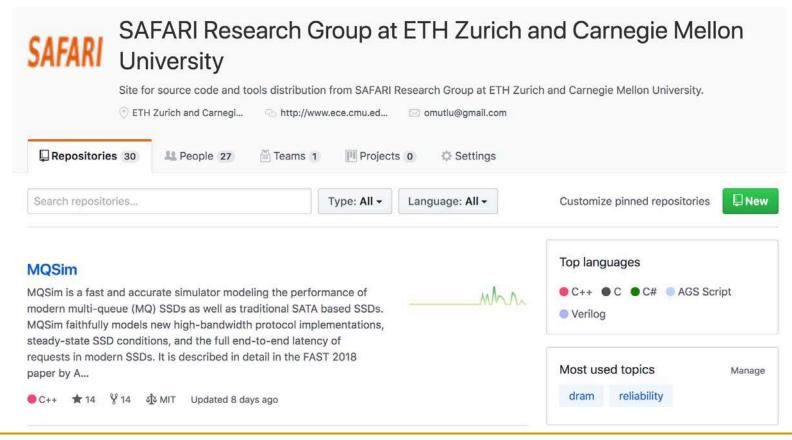

# Some Open Source Tools (I)

- Rowhammer Program to Induce RowHammer Errors

- https://github.com/CMU-SAFARI/rowhammer

- Ramulator Fast and Extensible DRAM Simulator

- https://github.com/CMU-SAFARI/ramulator

- MemSim Simple Memory Simulator

- https://github.com/CMU-SAFARI/memsim

- NOCulator Flexible Network-on-Chip Simulator

- https://github.com/CMU-SAFARI/NOCulator

- SoftMC FPGA-Based DRAM Testing Infrastructure

- https://github.com/CMU-SAFARI/SoftMC

- Other open-source software from my group

- https://github.com/CMU-SAFARI/

SAFARI

http://www.ece.cmu.edu/~safari/tools.html

# Some Open Source Tools (II)

- MQSim A Fast Modern SSD Simulator

- https://github.com/CMU-SAFARI/MQSim

- Mosaic GPU Simulator Supporting Concurrent Applications

- https://github.com/CMU-SAFARI/Mosaic

- IMPICA Processing in 3D-Stacked Memory Simulator

- https://github.com/CMU-SAFARI/IMPICA

- SMLA Detailed 3D-Stacked Memory Simulator

- https://github.com/CMU-SAFARI/SMLA

- HWASim Simulator for Heterogeneous CPU-HWA Systems

- https://github.com/CMU-SAFARI/HWASim

- Other open-source software from my group

- https://github.com/CMU-SAFARI/

- http://www.ece.cmu.edu/~safari/tools.html

#### More Open Source Tools (III)

- A lot more open-source software from my group

- https://github.com/CMU-SAFARI/

- http://www.ece.cmu.edu/~safari/tools.html

#### ramulator-pim

A fast and flexible simulation infrastructure for exploring general-purpose processing-in-memory (PIM) architectures. Ramulator-PIM combines a widely-used simulator for out-of-order and in-order processors (ZSim) with Ramulator, a DRAM simulator with memory models for DDRx, LPDDRx, GDDRx, WIOx, HBMx, and HMCx. Ramulator is described in the IEEE ...

●C++ ♀11 ☆29 ①6 ₺0 Updated 19 days ago

#### **SMASH**

SMASH is a hardware-software cooperative mechanism that enables highly-efficient indexing and storage of sparse matrices. The key idea of SMASH is to compress sparse matrices with a hierarchical bitmap compression format that can be accelerated from hardware.

Described by Kanellopoulos et al. (MICRO '19) https://people.inf.ethz.ch/omutlu/pub/SMA...

●C ೪1 ☆6 ①0 \$70 Updated on May 17

#### MQSim

MQSim is a fast and accurate simulator modeling the performance of modern multi-queue (MQ) SSDs as well as traditional SATA based SSDs. MQSim faithfully models new high-bandwidth protocol implementations, steady-state SSD conditions, and the full end-to-end latency of requests in modern SSDs. It is described in detail in the FAST 2018 paper by A...

C++ ♠ MIT ♀ 54 ☆ 62 ① 10 ₺ 1 Updated on May 15

#### Apollo

Apollo is an assembly polishing algorithm that attempts to correct the errors in an assembly. It can take multiple set of reads in a single run and polish the assemblies of genomes of any size. Described in the Bioinformatics journal paper (2020) by Firtina et al. at https://people.inf.ethz.ch/omutlu/pub/apollotechnology-independent-genome-asse...

🖰 • C++ 🟚 GPL-3.0 ម្វា 🕁 12 🕦 0 រា្ច 0 Updated on May 10

#### ramulator

A Fast and Extensible DRAM Simulator, with built-in support for modeling many different DRAM technologies including DDRx, LPDDRx, GDDRx, WIOx, HBMx, and various academic proposals. Described in the IEEE CAL 2015 paper by Kim et al. at

http://users.ece.cmu.edu/~omutlu/pub/ramulator\_dram\_simulator-ieee-cal15.pdf

#### Shifted-Hamming-Distance

Source code for the Shifted Hamming Distance (SHD)

filtering mechanism for sequence alignment. Described

in the Bioinformatics journal paper (2015) by Xin et al. at

http://users.ece.cmu.edu/~omutlu/pub/shiftedhamming-distance\_bioinformatics15\_proofs.pdf

● C ஹ GPL-2.0 ಳ 5 ☆ 20 ① 0 ൂ 1 Updated on Mar 29

#### SneakySnake

The first and the only pre-alignment filtering algorithm that works on all modern high-performance computing architectures. It works efficiently and fast on CPU, FPGA, and GPU architectures and that greatly (by more than two orders of magnitude) expedites sequence alignment calculation. Described by Alser et al. (preliminary version at https://a...

#### AirLift

AirLift is a tool that updates mapped reads from one reference genome to another. Unlike existing tools, It accounts for regions not shared between the two reference genomes and enables remapping across all parts of the references. Described by Kim et al. (preliminary version at http://arxiv.org/abs/1912.08735)

●C ♀O ☆3 ①O ℷъO Updated on Feb 19

#### **GPGPUSim-Ramulator**

The source code for GPGPUSim+Ramulator simulator. In this version, GPGPUSim uses Ramulator to simulate the DRAM. This simulator is used to produce some of the

#### Papers

All are available at

https://people.inf.ethz.ch/omutlu/projects.htm

http://scholar.google.com/citations?user=7XyGUGkAAAAJ&hl=en

https://people.inf.ethz.ch/omutlu/acaces2018.html

# Revisiting the Entire Stack

Algorithm

Program/Language

System Software

SW/HW Interface

Micro-architecture

Logic

Devices

Electrons

# Panel Questions

#### Question 1: Best Practices

Which are the best practices that you would suggest to your peers as the essential one for the success of an academic team?

#### Before I Start...

- There is no single way of having impact.

- The following is my way, methods and principles.

- There definitely are other ways.

- The critical thing is finding the way that works well for you and your goals.

- That you can own, cherish and optimize

#### Principle: Personalized Methods

# Find the methods that work for you

# Motivation & Mindset

# Start out with the right motivation and mindset

#### Motivation Sets The Culture and Goals

- Mindset 1: change the world positively, have high influence

- Mindset 2: enable students to achieve a potential that they did not even think they could ever achieve

- Not papers

- Not fame

- Not money

- **...**

- Motivation correction may be needed at times be ready

Principle: Team of Excellence

# Get motivated students

# Build a team of excellence

Principle: Learning and Scholarship

# Focus on learning and scholarship

### Some Basics of Research

Slides used in several of my courses:

e.g., <a href="https://www.youtube.com/watch?v=M0y\_Nvb9rGA">https://www.youtube.com/watch?v=M0y\_Nvb9rGA</a>

### How To Do Research & Advanced Dev.

- We will talk a lot about this in this course

- Learning by example

- Reading and evaluating strong and seminal papers & designs

- Learning by doing

- Semester-long research/design projects, masters' projects,

PhD thesis

- Learning by open, critical discussions

- Paper reading groups, frequent brainstorming and discussions

- Design sessions

- Collaborations

# Create an environment that values free exploration, openness, collaboration, hard work, creativity

#### What Is The Goal of Research?

- To generate new insight

- that can enable what previously did not exist

Research is a hunt for insight that can eventually impact the world

### Focus on Insight Encourage New Ideas

### Some Basic Advice for Good Research

- Choose great problems to solve: Have great taste

- Difficult

- Important

- High impact

- Read heavily and critically

- Think big (out of the box)

- Do not restrain yourself to tweaks or constraints of today

- Yet, think about adoption issues

- Aim high

- Write and present extremely well

# Many Principles on the Previous Slide

Principle: Bar

### Set the Bar High

### Set the Bar High

- The goal should be to enable students to achieve a potential that they did not even think they could ever achieve

- "Think big, aim high, enable positive change"

- Reward good, positive behavior that helps with this culture

- Recommended reading:

- Hamming, "You and Your Research," Talk at Bell Labs, 1986.

- https://www.cs.virginia.edu/~robins/YouAndYourResearch.html

**Fundamentals** and scholarship are critical (hypes come and go) Principle: Focus on Big Problems

**Choose Great Problems** and quide your group toward them (but give them freedom)

### Principle: Teaching and Research

Teaching drives Research Research drives Teaching

49

### More on Teaching and Research

- Care about teaching immensely

- Teaching and research are two sides of the same coin → scholarship

- Both long-term and short-term is affected by teaching

- Research motivates teaching motivates research

- I introduce RowHammer, Processing in Memory,

Meltdown/Spectre, DRAM Refresh, Various Technology Scaling problems, and research examples in my Freshman course:

- https://safari.ethz.ch/digitaltechnik/spring2020/

- All courses can have research examples

### Principle: Focus on Communication

**Emphasize** Clarity and Rigor in Communication (critical for high impact)

### Do Everything to Have High Impact

Engage with companies

- Engage and collaborate with researchers who fit your mindset

- Collaborate, not fight

Strive for the highest excellence

Foster collaboration (within group) (across groups) (with companies)

Principle: Reach Out

### Inspire and Reach Out

### Principle: Reach Out

- Give talks

- Educate others on your work and research

- Listen to everyone

- Especially your students

- Teach, educate, collaborate

Principle: Feedback

## Receive & Address Feedback (but do not get derailed)

### Principle: Receive & Address Feedback

- Address reviewer feedback

- Take them positively

- They can be helpful

- Feedback is not always right

- Need to apply corrections to it

- Do not let rejection derail you be ready for it

- Remind and encourage your students:

- https://www.sciencealert.com/these-8-papers-were-rejectedbefore-going-on-to-win-the-nobel-prize

Principle: Resilience

### Be Resilient

Principle: Passion

### Follow Your Passion

# Follow Your Passion (Do not get derailed by naysayers)

Principle: Learning and Scholarship

# The quality of your work defines your impact

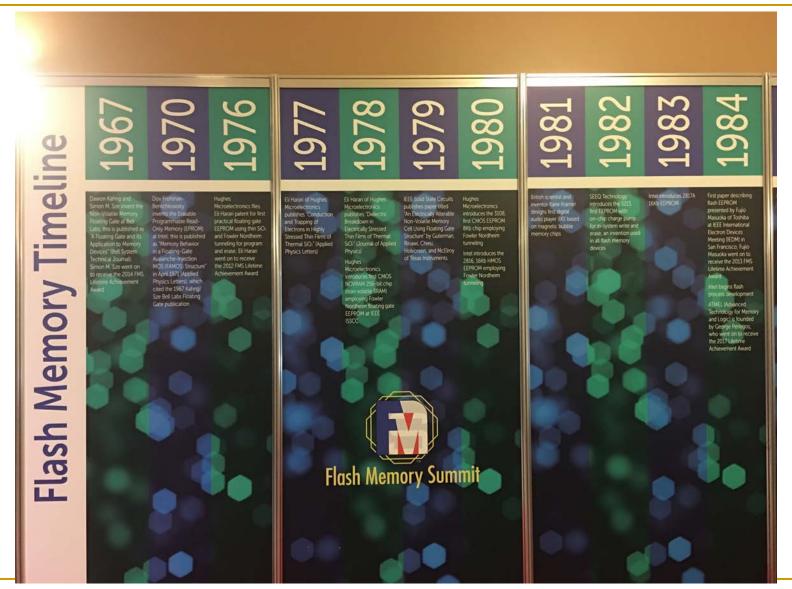

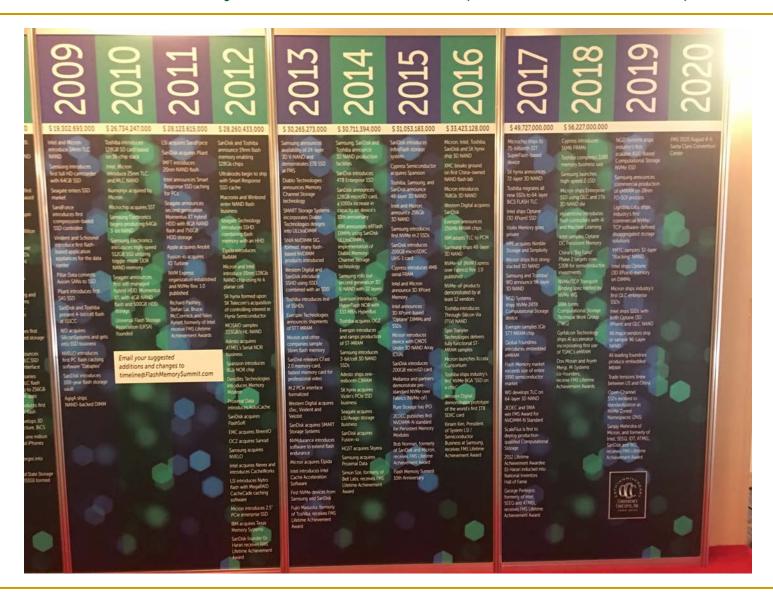

### If In Doubt, See Other Doubtful Technologies

- A very "doubtful" emerging technology

- for at least two decades

Proceedings of the IEEE, Sept. 2017

### Error Characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives

This paper reviews the most recent advances in solid-state drive (SSD) error characterization, mitigation, and data recovery techniques to improve both SSD's reliability and lifetime.

By Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu

### Flash Memory Timeline (1967-2019)

### Flash Memory Timeline (1967-2019)

### Four Key Current Directions

Fundamentally Secure/Reliable/Safe Architectures

- Fundamentally Energy-Efficient Architectures

- Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency and Predictable Architectures

Architectures for AI/ML, Genomics, Medicine, Health

### Our Dream (circa 2007)

- An embedded device that can perform comprehensive genome analysis in real time (within a minute)

- Which of these DNAs does this DNA segment match with?

- What is the likely genetic disposition of this patient to this drug?

**.**..

### New Genome Sequencing Technologies

## Nanopore sequencing technology and tools for genome assembly: computational analysis of the current state, bottlenecks and future directions

Damla Senol Cali ™, Jeremie S Kim, Saugata Ghose, Can Alkan, Onur Mutlu

Briefings in Bioinformatics, bby017, https://doi.org/10.1093/bib/bby017

Published: 02 April 2018 Article history ▼

Oxford Nanopore MinION

Senol Cali+, "Nanopore Sequencing Technology and Tools for Genome Assembly: Computational Analysis of the Current State, Bottlenecks and Future Directions," Briefings in Bioinformatics, 2018.

[Preliminary arxiv.org version]

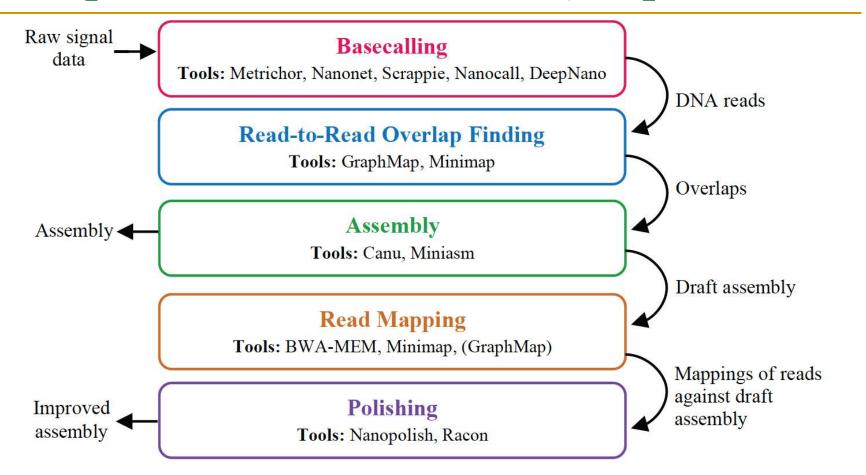

### Nanopore Genome Assembly Pipeline

Figure 1. The analyzed genome assembly pipeline using nanopore sequence data, with its five steps and the associated tools for each

step.

Senol Cali+, "Nanopore Sequencing Technology and Tools for Genome Assembly," Briefings in Bioinformatics, 2018. 68

### GateKeeper: FPGA-Based Alignment Filtering

Mohammed Alser, Hasan Hassan, Hongyi Xin, Oguz Ergin, Onur Mutlu, and Can Alkan

"GateKeeper: A New Hardware Architecture for Accelerating Pre-Alignment in DNA Short Read Mapping" Bioinformatics, [published online, May 31], 2017.

Source Code

Online link at Bioinformatics Journal

### GateKeeper: a new hardware architecture for accelerating pre-alignment in DNA short read mapping

Mohammed Alser ™, Hasan Hassan, Hongyi Xin, Oğuz Ergin, Onur Mutlu ™, Can Alkan ™

Bioinformatics, Volume 33, Issue 21, 1 November 2017, Pages 3355–3363,

https://doi.org/10.1093/bioinformatics/btx342

Published: 31 May 2017 Article history ▼

SAFARI

### Current State: Shouji [Alser+, Bioinformatics 2019]

Mohammed Alser, Hasan Hassan, Akash Kumar, Onur Mutlu, and Can Alkan, "Shouji: A Fast and Efficient Pre-Alignment Filter for Sequence Alignment" Bioinformatics, [published online, March 28], 2019.

Source Code

Online link at Bioinformatics Journal

Bioinformatics, 2019, 1–9 doi: 10.1093/bioinformatics/btz234 Advance Access Publication Date: 28 March 2019 Original Paper

#### Sequence alignment

### Shouji: a fast and efficient pre-alignment filter for sequence alignment

Mohammed Alser<sup>1,2,3,\*</sup>, Hasan Hassan<sup>1</sup>, Akash Kumar<sup>2</sup>, Onur Mutlu<sup>1,3,\*</sup> and Can Alkan<sup>3,\*</sup>

<sup>1</sup>Computer Science Department, ETH Zürich, Zürich 8092, Switzerland, <sup>2</sup>Chair for Processor Design, Center For Advancing Electronics Dresden, Institute of Computer Engineering, Technische Universität Dresden, 01062 Dresden, Germany and <sup>3</sup>Computer Engineering Department, Bilkent University, 06800 Ankara, Turkey

Associate Editor: Inanc Birol

SAFARI

<sup>\*</sup>To whom correspondence should be addressed.

### In-Memory DNA Sequence Analysis

Jeremie S. Kim, Damla Senol Cali, Hongyi Xin, Donghyuk Lee, Saugata Ghose, Mohammed Alser, Hasan Hassan, Oguz Ergin, Can Alkan, and Onur Mutlu, "GRIM-Filter: Fast Seed Location Filtering in DNA Read Mapping Using Processing-in-Memory Technologies" <u>BMC Genomics</u>, 2018.

Proceedings of the <u>16th Asia Pacific Bioinformatics Conference</u> (**APBC**), Yokohama, Japan, January 2018. arxiv.org Version (pdf)

# GRIM-Filter: Fast seed location filtering in DNA read mapping using processing-in-memory technologies

Jeremie S. Kim<sup>1,6\*</sup>, Damla Senol Cali<sup>1</sup>, Hongyi Xin<sup>2</sup>, Donghyuk Lee<sup>3</sup>, Saugata Ghose<sup>1</sup>, Mohammed Alser<sup>4</sup>, Hasan Hassan<sup>6</sup>, Oguz Ergin<sup>5</sup>, Can Alkan<sup>4\*</sup> and Onur Mutlu<sup>6,1\*</sup>

From The Sixteenth Asia Pacific Bioinformatics Conference 2018 Yokohama, Japan. 15-17 January 2018

Principle: Passion

### Follow Your Passion

# Build Infrastructure to Enable Your Passion (Big Projects)

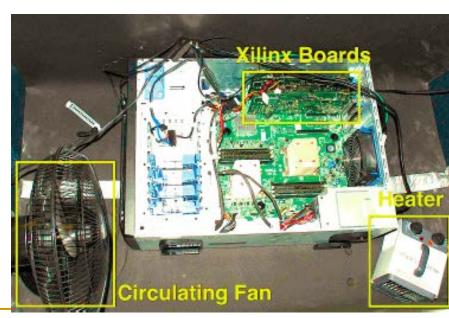

## Example: Our DRAM Infrastructure (since 2012)

Flipping Bits in Memory Without Accessing

Them: An Experimental Study of DRAM

Disturbance Errors (Kim et al., ISCA 2014)

Adaptive-Latency DRAM: Optimizing DRAM

Timing for the Common-Case (Lee et al.,

HPCA 2015)

AVATAR: A Variable-Retention-Time (VRT)

Aware Refresh for DRAM Systems (Qureshi et al., DSN 2015)

An Experimental Study of Data Retention

Behavior in Modern DRAM Devices:

Implications for Retention Time Profiling

Mechanisms (Liu et al., ISCA 2013)

The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study (Khan et al., SIGMETRICS 2014)

## Example: Our DRAM Infrastructure (since 2012)

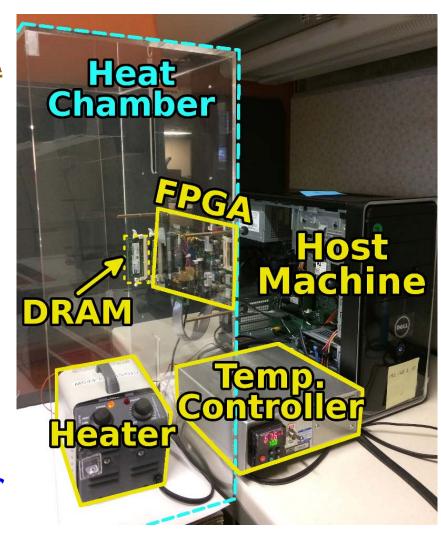

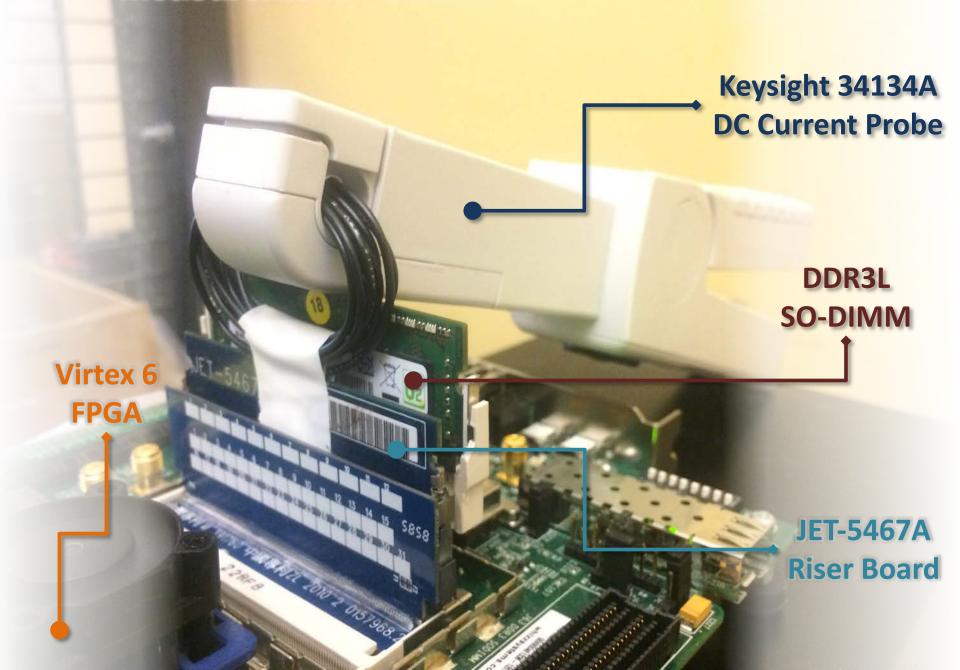

# SoftMC: Open Source DRAM Infrastructure

Hasan Hassan et al., "SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies," HPCA 2017.

- Flexible

- Easy to Use (C++ API)

- Open-source github.com/CMU-SAFARI/SoftMC

## SoftMC [HPCA 2017]

https://github.com/CMU-SAFARI/SoftMC

# SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

```

Hasan Hassan Nandita Vijaykumar Samira Khan Saugata Ghose Kevin Chang Gennady Pekhimenko Donghyuk Lee Quz Ergin Onur Mutlu Onur Mutlu Nandita Vijaykumar Samira Khan Saugata Ghose Kevin Chang Gennady Pekhimenko Onur Mutlu Nandita Vijaykumar Samira Khan Saugata Ghose Nandita Vijaykumar Samira Khan Saugata Ghose Kevin Chang Gennady Pekhimenko Onur Mutlu Nandita Vijaykumar Samira Khan Saugata Ghose Kevin Chang Samira Khan Saugata Ghose Kevin Chang Saugata Ghose Nandita Vijaykumar Samira Khan Saugata Ghose Nandita Vijaykumar Samira Khan Saugata Ghose Saugata

```

```

<sup>1</sup>ETH Zürich <sup>2</sup>TOBB University of Economics & Technology <sup>3</sup>Carnegie Mellon University <sup>4</sup>University of Virginia <sup>5</sup>Microsoft Research <sup>6</sup>NVIDIA Research

```

#### SAFARI

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

"Flipping Bits in Memory Without Accessing Them: An

Experimental Study of DRAM Disturbance Errors"

Proceedings of the 41st International Symposium on Computer

Architecture (ISCA), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data]

# Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly\* Jeremie Kim<sup>1</sup> Chris Fallin\* Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup>

Carnegie Mellon University <sup>2</sup>Intel Labs

SAFARI 79

Onur Mutlu and Jeremie Kim,"RowHammer: A Retrospective"

<u>IEEE Transactions on Computer-Aided Design of Integrated</u> <u>Circuits and Systems</u> (**TCAD**) Special Issue on Top Picks in Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

# RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> §ETH Zürich <sup>‡</sup>Carnegie Mellon University

SAFARI 80

Jeremie S. Kim, Minesh Patel, A. Giray Yaglikci, Hasan Hassan, Roknoddin Azizi, Lois Orosa, and <u>Onur Mutlu</u>,

<u>"Revisiting RowHammer: An Experimental Analysis of Modern Devices and Mitigation Techniques"</u>

Proceedings of the <u>47th International Symposium on Computer</u> <u>Architecture</u> (**ISCA**), Valencia, Spain, June 2020.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Talk Video (20 minutes)]

[Lightning Talk Video (3 minutes)]

# Revisiting RowHammer: An Experimental Analysis of Modern DRAM Devices and Mitigation Techniques

Jeremie S. Kim<sup>§†</sup> Minesh Patel<sup>§</sup> A. Giray Yağlıkçı<sup>§</sup> Hasan Hassan<sup>§</sup> Roknoddin Azizi<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§†</sup>

§ETH Zürich †Carnegie Mellon University

Pietro Frigo, Emanuele Vannacci, Hasan Hassan, Victor van der Veen, Onur Mutlu, Cristiano Giuffrida, Herbert Bos, and Kaveh Razavi, "TRRespass: Exploiting the Many Sides of Target Row Refresh" Proceedings of the 41st IEEE Symposium on Security and Privacy (S&P), San Francisco, CA, USA, May 2020.

[Slides (pptx) (pdf)]

[Talk Video (17 minutes)]

Source Code

[Web Article]

Best paper award.

# TRRespass: Exploiting the Many Sides of Target Row Refresh

Pietro Frigo\*† Emanuele Vannacci\*† Hasan Hassan§ Victor van der Veen¶ Onur Mutlu<sup>§</sup> Cristiano Giuffrida\* Herbert Bos\* Kaveh Razavi\*

\*Vrije Universiteit Amsterdam

§ETH Zürich

Qualcomm Technologies Inc.

#### Infrastructure Enabled Research: Refresh

Jamie Liu, Ben Jaiyen, Yoongu Kim, Chris Wilkerson, and Onur Mutlu, "An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms" Proceedings of the 40th International Symposium on Computer Architecture (ISCA), Tel-Aviv, Israel, June 2013. Slides (ppt) Slides (pdf)

# An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms

Jamie Liu\*

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

jamiel@alumni.cmu.edu

Ben Jaiyen\*

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

bjaiyen@alumni.cmu.edu

Yoongu Kim

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

yoonguk@ece.cmu.edu

Chris Wilkerson

Intel Corporation

2200 Mission College Blvd.

Santa Clara, CA 95054

chris.wilkerson@intel.com

Onur Mutlu

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

onur@cmu.edu

# Infrastructure Enabled Research: Latency

Donghyuk Lee, Yoongu Kim, Gennady Pekhimenko, Samira Khan, Vivek Seshadri, Kevin Chang, and Onur Mutlu,

"Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case"

Proceedings of the <u>21st International Symposium on High-</u> <u>Performance Computer Architecture</u> (**HPCA**), Bay Area, CA, February 2015.

[Slides (pptx) (pdf)] [Full data sets]

#### Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case

Donghyuk Lee Yoongu Kim Gennady Pekhimenko

Samira Khan Vivek Seshadri Kevin Chang Onur Mutlu

Carnegie Mellon University

SAFARI 84

# Infrastructure Enabled Research: Voltage

Kevin Chang, A. Giray Yaglikci, Saugata Ghose, Aditya Agrawal, Niladrish Chatterjee, Abhijith Kashyap, Donghyuk Lee, Mike O'Connor, Hasan Hassan, and Onur Mutlu,

"Understanding Reduced-Voltage Operation in Modern DRAM Devices: Experimental Characterization, Analysis, and Mechanisms"

Proceedings of the <u>ACM International Conference on Measurement and Modeling</u> of Computer Systems (**SIGMETRICS**), Urbana-Champaign, IL, USA, June 2017.

[Abstract] [POMACS Journal Version (same content, different format)]

[Slides (pptx) (pdf)]

[Full Lecture Video (33 minutes)]

[Full Data Sets and Circuit Model]

#### Understanding Reduced-Voltage Operation in Modern DRAM Chips: Characterization, Analysis, and Mechanisms

Kevin K. Chang<sup>†</sup> Abdullah Giray Yağlıkçı<sup>†</sup> Saugata Ghose<sup>†</sup> Aditya Agrawal<sup>¶</sup> Niladrish Chatterjee<sup>¶</sup> Abhijith Kashyap<sup>†</sup> Donghyuk Lee<sup>¶</sup> Mike O'Connor<sup>¶,‡</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§,†</sup>

†Carnegie Mellon University <sup>¶</sup>NVIDIA <sup>‡</sup>The University of Texas at Austin <sup>§</sup>ETH Zürich

#### Infrastructure Enabled Research: ECC

Minesh Patel, Jeremie S. Kim, Hasan Hassan, and Onur Mutlu, "Understanding and Modeling On-Die Error Correction in Modern DRAM: An Experimental Study Using Real Devices" Proceedings of the 49th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Portland, OR, USA, June 2019.

[Slides (pptx) (pdf)]

[Talk Video (26 minutes)]

[Full Talk Lecture (29 minutes)]

[Source Code for EINSim, the Error Inference Simulator]

Best paper award.

# Understanding and Modeling On-Die Error Correction in Modern DRAM: An Experimental Study Using Real Devices

```

Minesh Patel^{\dagger} Jeremie S. Kim^{\ddagger\dagger} Hasan Hassan^{\dagger} Onur Mutlu^{\dagger\ddagger} ^{\dagger} ETH Zürich ^{\ddagger} Carnegie Mellon University

```

Saugata Ghose, A. Giray Yaglikci, Raghav Gupta, Donghyuk Lee, Kais Kudrolli, William X. Liu, Hasan Hassan, Kevin K. Chang, Niladrish Chatterjee, Aditya Agrawal, Mike O'Connor, and Onur Mutlu,

"What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study"

Proceedings of the <u>ACM International Conference on Measurement and Modeling</u> <u>of Computer Systems</u> (**SIGMETRICS**), Irvine, CA, USA, June 2018.

[Abstract]

[POMACS Journal Version (same content, different format)]

[Slides (pptx) (pdf)]

[VAMPIRE DRAM Power Model]

#### What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study

Saugata Ghose<sup>†</sup> Abdullah Giray Yağlıkçı<sup>‡†</sup> Raghav Gupta<sup>†</sup> Donghyuk Lee<sup>§</sup> Kais Kudrolli<sup>†</sup> William X. Liu<sup>†</sup> Hasan Hassan<sup>‡</sup> Kevin K. Chang<sup>†</sup> Niladrish Chatterjee<sup>§</sup> Aditya Agrawal<sup>§</sup> Mike O'Connor<sup>§¶</sup> Onur Mutlu<sup>‡†</sup>

<sup>†</sup>Carnegie Mellon University <sup>‡</sup>ETH Zürich <sup>§</sup>NVIDIA <sup>¶</sup>University of Texas at Austin

SAFARI

#### Infrastructure Enabled Research: PUF

Jeremie S. Kim, Minesh Patel, Hasan Hassan, and Onur Mutlu,

"The DRAM Latency PUF: Quickly Evaluating Physical Unclonable

Functions by Exploiting the Latency-Reliability Tradeoff in

Modern DRAM Devices"

Proceedings of the <u>24th International Symposium on High-Performance</u> <u>Computer Architecture</u> (**HPCA**), Vienna, Austria, February 2018.

[Lightning Talk Video]

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

#### The DRAM Latency PUF:

Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern Commodity DRAM Devices

Jeremie S. Kim<sup>†§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

#### Infrastructure Enabled Research: TRNG

Jeremie S. Kim, Minesh Patel, Hasan Hassan, Lois Orosa, and Onur Mutlu, "D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput"

Proceedings of the 25th International Symposium on High-Performance Computer Architecture (HPCA), Washington, DC, USA, February 2019.

[Slides (pptx) (pdf)]

[Full Talk Video (21 minutes)]

[Full Talk Lecture Video (27 minutes)]

Top Picks Honorable Mention by IEEE Micro.

#### D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

Jeremie S. Kim<sup>‡§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§‡</sup> <sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

90

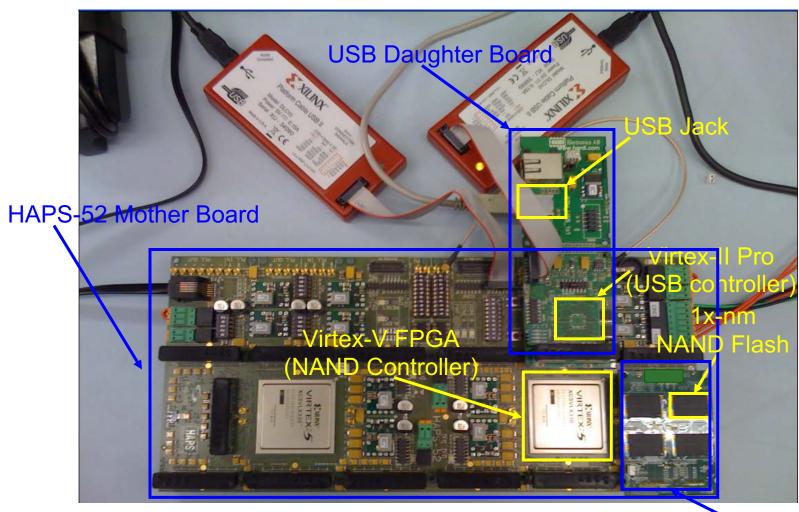

#### Our NAND Flash Infrastructure

[DATE 2012, ICCD 2012, DATE 2013, ITJ 2013, ICCD 2013, SIGMETRICS 2014, HPCA 2015, DSN 2015, MSST 2015, JSAC 2016, HPCA 2017, DFRWS 2017, PIEEE 2017, HPCA 2018, SIGMETRICS 2018]

NAND Daughter Board

#### Infrastructure Enabled Research: SSD Errors

Proceedings of the IEEE, Sept. 2017

# Error Characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives

This paper reviews the most recent advances in solid-state drive (SSD) error characterization, mitigation, and data recovery techniques to improve both SSD's reliability and lifetime.

By Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu

https://arxiv.org/pdf/1706.08642

#### Ramulator – DRAM Simulation Infrastructure

| Segment     | DRAM Standards & Architectures                                                                                                                                                                                               |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Commodity   | DDR3 (2007) [14]; DDR4 (2012) [18]                                                                                                                                                                                           |

| Low-Power   | LPDDR3 (2012) [17]; LPDDR4 (2014) [20]                                                                                                                                                                                       |

| Graphics    | GDDR5 (2009) [15]                                                                                                                                                                                                            |

| Performance | eDRAM [28], [32]; RLDRAM3 (2011) [29]                                                                                                                                                                                        |

| 3D-Stacked  | WIO (2011) [16]; WIO2 (2014) [21]; MCDRAM (2015) [13]; HBM (2013) [19]; HMC1.0 (2013) [10]; HMC1.1 (2014) [11]                                                                                                               |

| Academic    | SBA/SSA (2010) [38]; Staged Reads (2012) [8]; RAIDR (2012) [27]; SALP (2012) [24]; TL-DRAM (2013) [26]; RowClone (2013) [37]; Half-DRAM (2014) [39]; Row-Buffer Decoupling (2014) [33]; SARP (2014) [6]; AL-DRAM (2015) [25] |

Table 1. Landscape of DRAM-based memory

Kim+, "Ramulator: A Flexible and Extensible DRAM Simulator", IEEE CAL 2015.

# Ramulator Paper and Source Code

- Yoongu Kim, Weikun Yang, and Onur Mutlu, "Ramulator: A Fast and Extensible DRAM Simulator" IEEE Computer Architecture Letters (CAL), March 2015. [Source Code]

- Source code is released under the liberal MIT License

- https://github.com/CMU-SAFARI/ramulator

#### Ramulator: A Fast and Extensible DRAM Simulator

Yoongu Kim<sup>1</sup> Weikun Yang<sup>1,2</sup> Onur Mutlu<sup>1</sup>

<sup>1</sup>Carnegie Mellon University <sup>2</sup>Peking University

# Ramulator-PIM Paper and Source Code

Gagandeep Singh, Juan Gomez-Luna, Giovanni Mariani, Geraldo F. Oliveira, Stefano Corda, Sander Stujik, Onur Mutlu, and Henk Corporaal, "NAPEL: Near-Memory Computing Application Performance Prediction via Ensemble Learning"

Proceedings of the 56th Design Automation Conference (DAC), Las Vegas,

[Slides (pptx) (pdf)]

NV, USA, June 2019.

[Poster (pptx) (pdf)]

[Source Code for Ramulator-PIM]

https://github.com/CMU-SAFARI/ramulator-pim

#### ZSim+Ramulator - A Processing-in-Memory Simulation Framework

ZSim+Ramulator is a framework for design space exploration of general-purpose Processing-in-Memory (PIM) architectures. The framework is based on two widely-known simulators: ZSim [1] and Ramulator [2][3].

## Infrastructure Enabled Research: PIM (I)

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu,

"Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks"

Proceedings of the <u>23rd International Conference on Architectural Support for</u>

<u>Programming Languages and Operating Systems</u> (**ASPLOS**), Williamsburg, VA, USA, March 2018.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Poster (pptx) (pdf)] [Lightning Talk Video (2 minutes)] [Full Talk Video (21 minutes)]

### Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup> Saugata Ghose<sup>1</sup> Youngsok Kim<sup>2</sup>

Rachata Ausavarungnirun<sup>1</sup> Eric Shiu<sup>3</sup> Rahul Thakur<sup>3</sup> Daehyun Kim<sup>4,3</sup>

Aki Kuusela<sup>3</sup> Allan Knies<sup>3</sup> Parthasarathy Ranganathan<sup>3</sup> Onur Mutlu<sup>5,1</sup>

# Infrastructure Enabled Research: PIM (II)

## Processing Data Where It Makes Sense: Enabling In-Memory Computation

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>b,c</sup>

<sup>a</sup>ETH Zürich

<sup>b</sup>Carnegie Mellon University

<sup>c</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, <a href="Processing Data Where It Makes Sense: Enabling In-Memory">Processing Data Where It Makes Sense: Enabling In-Memory</a>

Computation"

Invited paper in <u>Microprocessors and Microsystems</u> (**MICPRO**), June 2019.

[arXiv version]

# Infrastructure Enabled Research: PIM (III)

#### A Workload and Programming Ease Driven Perspective of Processing-in-Memory

Saugata Ghose<sup>†</sup> Amirali Boroumand<sup>†</sup> Jeremie S. Kim<sup>†</sup>§ Juan Gómez-Luna<sup>§</sup> Onur Mutlu<sup>§†</sup>

†Carnegie Mellon University §ETH Zürich

Saugata Ghose, Amirali Boroumand, Jeremie S. Kim, Juan Gomez-Luna, and Onur Mutlu, "Processing-in-Memory: A Workload-Driven Perspective"

Invited Article in IBM Journal of Research & Development, Special Issue on

Hardware for Artificial Intelligence, to appear in November 2019.

[Preliminary arXiv version]

SAFARI

# Infrastructure Enabled Research: PIM (IV)

Vivek Seshadri and Onur Mutlu, "In-DRAM Bulk Bitwise Execution Engine" Invited Book Chapter in Advances in Computers, to appear in 2020.

[Preliminary arXiv version]

#### In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

# Question 2: Heterogeneity & Inclusiveness

How much is important the heterogeneity of the group?

What about the inclusion?

# Principle: Diversity & Heterogeneity

- Diversity is very important

- No two people are the same -- everyone brings perspective

- Critical to be diverse, accepting, inclusive, heterogeneous

- Age

- Gender

- Experience level

- Education level

- Geography (maybe natural in our field?)

- Critical for open, expressive culture

- Set a common goal and common culture

Principle: Environment of Freedom & Inclusion

# Create an environment that values free exploration, openness, collaboration, hard work, creativity

# Question 3: Choosing Students

Which are the main characteristics and skills one should take into account when choosing PhD students and researchers for new and (possibly) impactful research groups?

#### How to Select PhD Students & Researchers

- Motivation and Mindset

- Creativity

- Resilience

- Hard work

- Boldness

- Perseverance, commitment

- Intellectual strength

- Openness to feedback

- Communicativeness

- Ability to execute things until the end

- **...**

A PhD is a long road. It is not for everyone. Commitment & resilience are critical.

#### How to Select Students

https://safari.ethz.ch/apply/

# Question 4 and Answer: Mentoring

- Can mentoring young students and managing a group be taught?

- Answer: Yes (and, the mentoring process can be managed)

- Mentoring is a critical part of a PhD

# Question 5 and Answer: Emotional Intelligence

- Emotional intelligence is considered today a key skill for managers and entrepreneurs. Do you believe that is it crucial also for research groups leaders?

- Answer: Yes, absolutely

- Communication, understanding, mindset are all critical

- And part of Emotional Intelligence

# Question 6 and Answer: Hierarchy

- How does the group's internal hierarchy impact work effectiveness? Is a strong hierarchy implying a reduction of diversity and heterogeneity or not?

- Answer: Less hierarchy is better. Yet, tasks of different types of students are different (postdoc vs PhD students)

- Openness and valuing of every single person and idea, regardless of level or experience

- Valuing of mentorship

- Inexperienced folks learn from experienced ones

- Everyone collaborates

- No (artificial) barriers between people

# Food for Thought: Three Quotes

The reasonable man adapts himself to the world; The unreasonable one persists in trying to adapt the world to himself.

Therefore, all progress depends on the unreasonable man.

Progress is impossible without change, and those who cannot change their minds cannot change anything.

**George Bernard Shaw**

My heart is in the work.

**Andrew Carnegie**

# How to Build an Impactful Research Group

Onur Mutlu

omutlu@gmail.com

https://people.inf.ethz.ch/omutlu

19 July 2020

**DAC Early Career Workshop Panel**

**Carnegie Mellon**

# Backup Slides

# Some Resilience Examples from Our Research

# Enabling DRAM to Compute at Low Cost

# RowClone [MICRO'13]

Vivek Seshadri, Yoongu Kim, Chris Fallin, Donghyuk Lee, Rachata

Ausavarungnirun, Gennady Pekhimenko, Yixin Luo, Onur Mutlu, Michael A.

Kozuch, Phillip B. Gibbons, and Todd C. Mowry,

"RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization"

Proceedings of the <u>46th International Symposium on Microarchitecture</u> (**MICRO**), Davis, CA, December 2013. [<u>Slides (pptx) (pdf)</u>] [<u>Lightning Session Slides (pptx) (pdf)</u>] [<u>Poster (pptx) (pdf)</u>]

# RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization

Vivek Seshadri Yoongu Kim Chris Fallin\* Donghyuk Lee vseshadr@cs.cmu.edu yoongukim@cmu.edu cfallin@c1f.net donghyuk1@cmu.edu

Rachata Ausavarungnirun Gennady Pekhimenko Yixin Luo gpekhime@cs.cmu.edu yixinluo@andrew.cmu.edu

Onur Mutlu Phillip B. Gibbons† Michael A. Kozuch† Todd C. Mowry onur@cmu.edu phillip.b.gibbons@intel.com michael.a.kozuch@intel.com tcm@cs.cmu.edu

Carnegie Mellon University †Intel Pittsburgh

# Ambit [MICRO'17]

Vivek Seshadri et al., "<u>Ambit: In-Memory Accelerator</u> for Bulk Bitwise Operations Using Commodity DRAM <u>Technology</u>," MICRO 2017.

Ambit: In-Memory Accelerator for Bulk Bitwise Operations

Using Commodity DRAM Technology

Vivek Seshadri $^{1,5}$  Donghyuk Lee $^{2,5}$  Thomas Mullins $^{3,5}$  Hasan Hassan $^4$  Amirali Boroumand $^5$  Jeremie Kim $^{4,5}$  Michael A. Kozuch $^3$  Onur Mutlu $^{4,5}$  Phillip B. Gibbons $^5$  Todd C. Mowry $^5$

$^1$ Microsoft Research India  $^2$ NVIDIA Research  $^3$ Intel  $^4$ ETH Zürich  $^5$ Carnegie Mellon University

#### SAFARI

# **Ambit**

Vivek Seshadri and Onur Mutlu,

"In-DRAM Bulk Bitwise Execution Engine"

Invited Book Chapter in Advances in Computers, to appear in 2020.

[Preliminary arXiv version]

# In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

# In-Memory Bulk Bitwise Operations

- We can support in-DRAM COPY, ZERO, AND, OR, NOT, MAJ

- At low cost

- Using analog computation capability of DRAM

- Idea: activating multiple rows performs computation

- 30-74X performance and energy improvement

- Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology," MICRO 2017.

New memory technologies enable even more opportunities

# Ambit Sounds Good, No?

#### **Paper summary**

# **Review from ISCA 2016**

The paper proposes to extend DRAM to include bulk, bit-wise logical

operations directly between rows within the DRAM.

#### **Strengths**

- Very clever/novel idea.

- Great potential speedup and efficiency gains.

#### Weaknesses

Probably won't ever be built. Not practical to assume DRAM manufacturers with change DRAM in this way.

#### SAFARI

# Another Review

## **Another Review from ISCA 2016**

#### **Strengths**

The proposed mechanisms effectively exploit the operation of the DRAM to perform efficient bitwise operations across entire rows of the DRAM.

#### Weaknesses

This requires a modification to the DRAM that will only help this type of bitwise operation. It seems unlikely that something like that will be adopted.

#### SAFARI

## Yet Another Review

### **Yet Another Review from ISCA 2016**

#### Weaknesses

The core novelty of Buddy RAM is almost all circuits-related (by exploiting sense amps). I do not find architectural innovation even though the circuits technique benefits architecturally by mitigating memory bandwidth and relieving cache resources within a subarray. The only related part is the new ISA support for bitwise operations at DRAM side and its induced issue on cache coherence.

# RowClone & Bitwise Ops in Real DRAM Chips

# ComputeDRAM: In-Memory Compute Using Off-the-Shelf DRAMs

Fei Gao feig@princeton.edu Department of Electrical Engineering Princeton University Georgios Tziantzioulis georgios.tziantzioulis@princeton.edu Department of Electrical Engineering Princeton University David Wentzlaff

wentzlaf@princeton.edu

Department of Electrical Engineering

Princeton University

# Pinatubo: RowClone and Bitwise Ops in PCM

# Pinatubo: A Processing-in-Memory Architecture for Bulk Bitwise Operations in Emerging Non-volatile Memories

Shuangchen Li<sup>1</sup>\*, Cong Xu<sup>2</sup>, Qiaosha Zou<sup>1,5</sup>, Jishen Zhao<sup>3</sup>, Yu Lu<sup>4</sup>, and Yuan Xie<sup>1</sup>

University of California, Santa Barbara<sup>1</sup>, Hewlett Packard Labs<sup>2</sup> University of California, Santa Cruz<sup>3</sup>, Qualcomm Inc.<sup>4</sup>, Huawei Technologies Inc.<sup>5</sup> {shuangchenli, yuanxie}ece.ucsb.edu<sup>1</sup>

# We Have a Mindset Issue...

- There are many other similar examples from reviews...

- For many other papers...

- And, we are not even talking about JEDEC yet...

- How do we fix the mindset problem?

- By doing more research, education, implementation in alternative processing paradigms

# We need to work on enabling the better future...

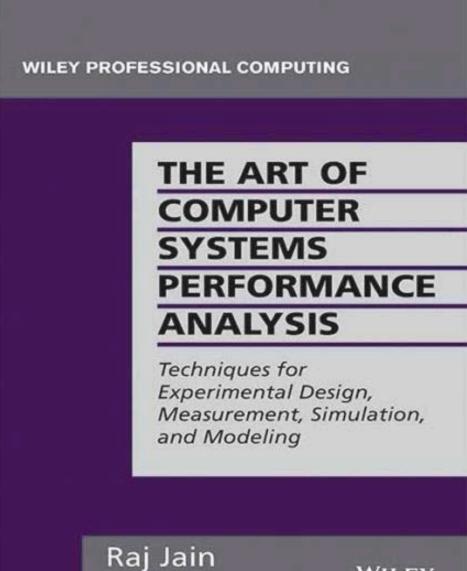

# Aside: A Recommended Book

Raj Jain, "The Art of **Computer Systems** Performance Analysis," Wiley, 1991.

WILEY

#### DECISION MAKER'S GAMES

Even if the performance analysis is correctly done and presented, it may not be enough to persuade your audience—the decision makers—to follow your recommendations. The list shown in Box 10.2 is a compilation of reasons for rejection heard at various performance analysis presentations. You can use the list by presenting it immediately and pointing out that the reason for rejection is not new and that the analysis deserves more consideration. Also, the list is helpful in getting the competing proposals rejected!

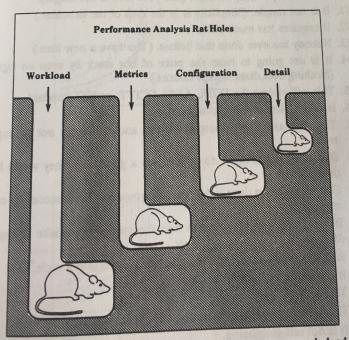

There is no clear end of an analysis. Any analysis can be rejected simply on the grounds that the problem needs more analysis. This is the first reason listed in Dox 19.2. The second most common reason for rejection of an analysis and for endless debate is the workload. Since workloads are always based on the past measurements, their applicability to the current or future environment can always be questioned. Actually workload is one of the four areas of discussion that lead a performance presentation into an endless debate. These "rat holes" and their relative sizes in terms of time consumed are shown in Figure 10.26. Presenting this cartoon at the beginning of a presentation helps to avoid these areas.

FIGURE 10.26 Four issues in performance presentations that commonly lead to endless discussion.

Raj Jain, "The Art of Computer Systems Performance Analysis," Wiley, 1991. Box 10.2 Reasons for Not Accepting the Results of an Analysis

- This needs more analysis.

You need a better understanding of the workload.

- You need a better that the second of the I/O's, packets, jobs, and files, and most of the I/O's, packets, jobs, and files are short.

- 4. It improves performance only for short I/O's, packets, jobs, and files, but who cares for the performance of short I/O's, packets, jobs, and files; its the long ones that impact the system.

- 5. It needs too much memory/CPU/bandwidth and memory/CPU/bandwidth isn't free.

- 6. It only saves us memory/CPU/bandwidth and memory/CPU/bandwidth is cheap.

- 7. There is no point in making the networks (similarly, CPUs/disks/...) faster; our CPUs/disks (any component other than the one being discussed) aren't fast enough to use them.

- 8. It improves the performance by a factor of x, but it doesn't really matter at the user level because everything else is so slow.

- 9. It is going to increase the complexity and cost.

- 10. Let us keep it simple stupid (and your idea is not stupid).

- 11. It is not simple. (Simplicity is in the eyes of the beholder.)

- 12. It requires too much state.

- 13. Nobody has ever done that before. (You have a new idea.)

- 14. It is not going to raise the price of our stock by even an eighth. (Nothing ever does, except rumors.)

- 15. This will violate the IEEE, ANSI, CCITT, or ISO standard.

- 16. It may violate some future standard.

- 17. The standard says nothing about this and so it must not be important.

- 18. Our competitors don't do it. If it was a good idea, they would have done it.

- 19. Our competition does it this way and you don't make money by copying others.

- It will introduce randomness into the system and make debugging difficult.

- 21. It is too deterministic; it may lead the system into a cycle.

- 22. It's not interoperable.

- 23. This impacts hardware.

- 24. That's beyond today's technology.

- 23. It is not soil billiain

- 26. Why change—it's working OK.

Raj Jain, "The Art of Computer Systems Performance Analysis," Wiley, 1991.

# Suggestions to Reviewers

- Be fair; you do not know it all

- Be open-minded; you do not know it all

- Be accepting of diverse research methods: there is no single way of doing research

- Be constructive, not destructive

- Do not have double standards...

#### Do not block or delay scientific progress for non-reasons

# Initial RowHammer Reviews

# Disturbance Errors in DRAM: Demonstration, Characterization, and Prevention

Rejected (R2)

863kB Friday 31 May 2013 2:00:53pm PDT

b9bf06021da54cddf4cd0b3565558a181868b972

You are an **author** of this paper.

+ Abstract + Authors

Review #66A

Review #66B

Review #66C

Review #66D

Review #66E

Review #66F

| OveMer | Nov | WriQua | RevExp |

|--------|-----|--------|--------|

| 1      | 4   | 4      | 4      |

| 5      | 4   | 5      | 3      |

| 2      | 3   | 5      | 4      |

| 1      | 2   | 3      | 4      |

| 4      | 4   | 4      | 3      |

| 2      | 4   | 4      | 3      |

#### SAFARI

# Missing the Point Reviews from Micro 2013

#### PAPER WEAKNESSES

This is an excellent test methodology paper, but there is no micro-architectural or architectural content.

#### PAPER WEAKNESSES

- Whereas they show disturbance may happen in DRAM array, authors don't show it can be an issue in realistic DRAM usage scenario

- Lacks architectural/microarchitectural impact on the DRAM disturbance analysis

#### PAPER WEAKNESSES

The mechanism investigated by the authors is one of many well known disturb mechanisms. The paper does not discuss the root causes to sufficient depth and the importance of this mechanism compared to others. Overall the length of the sections restating known information is much too long in relation to new work.

# Dismissing Science

### Reviews from ISCA 2014

#### PAPER WEAKNESSES

- 1) The disturbance error (a.k.a coupling or cross-talk noise induced error) is a known problem to the DRAM circuit community.

- 2) What you demonstrated in this paper is so called DRAM row ham mering issue you can even find a Youtube video showing this! <a href="http://www.youtube.com/watch?v=i3-gQSnBcdo">http://www.youtube.com/watch?v=i3-gQSnBcdo</a>

- 2) The architectural contribution of this study is too insignificant.

#### PAPER WEAKNESSES

- Row Hammering appears to be well-known, and solutions have already been proposed by industry to address the issue.

- The paper only provides a qualitative analysis of solutions to the problem. A more robust evaluation is really needed to know whether the proposed solution is necessary.

# Final RowHammer Reviews

# Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Accepted

639kB 21 Nov 2013 10:53:11pm CST | f039be2735313b39304ae1c6296523867a485610

You are an **author** of this paper.

|             | OveMer | Nov | WriQua | RevConAnd |

|-------------|--------|-----|--------|-----------|

| Review #41A | 8      | 4   | 5      | 3         |

| Review #41B | 7      | 4   | 4      | 3         |

| Review #41C | 6      | 4   | 4      | 3         |

| Review #41D | 2      | 2   | 5      | 4         |

| Review #41E | 3      | 2   | 3      | 3         |

| Review #41F | 7      | 4   | 4      | 3         |

# Suggestion to Community

# We Need to Fix the Reviewer Accountability Problem

# Suggestion to Community

# Eliminate Double Standards

# Another Recommended Book

# Computer Architecture Today

- You can revolutionize the way computers are built, if you understand both the hardware and the software (and change each accordingly)

- You can invent new paradigms for computation, communication, and storage

- Recommended book: Thomas Kuhn, "The Structure of Scientific Revolutions" (1962)

- Pre-paradigm science: no clear consensus in the field

- Normal science: dominant theory used to explain/improve things (business as usual); exceptions considered anomalies

- Revolutionary science: underlying assumptions re-examined

Suggestion to Researchers: Principle: Passion

# Follow Your Passion (Do not get derailed by naysayers)

Suggestion to Researchers: Principle: Resilience

# Be Resilient

Principle: Learning and Scholarship

# Focus on learning and scholarship

Principle: Learning and Scholarship

# The quality of your work defines your impact

# More Thoughts and Suggestions

Onur Mutlu,

#### "Some Reflections (on DRAM)"

Award Speech for <u>ACM SIGARCH Maurice Wilkes Award</u>, at the **ISCA** Awards Ceremony, Phoenix, AZ, USA, 25 June 2019.

[Slides (pptx) (pdf)]

[Video of Award Acceptance Speech (Youtube; 10 minutes) (Youku; 13 minutes)]

[Video of Interview after Award Acceptance (Youtube; 1 hour 6 minutes) (Youku; 1 hour 6 minutes)]

[News Article on "ACM SIGARCH Maurice Wilkes Award goes to Prof. Onur Mutlu"]

Onur Mutlu,

#### "How to Build an Impactful Research Group"

<u>Design Automation Conference Early Career Workshop</u>, Las Vegas, NV, USA, June 2019.

[Slides (pptx) (pdf)]

# Funding Acknowledgments

- Alibaba, AMD, ASML, Google, Facebook, Hi-Silicon, HP Labs, Huawei, IBM, Intel, Microsoft, Nvidia, Oracle, Qualcomm, Rambus, Samsung, Seagate, VMware

- NSF

- NIH

- GSRC

- SRC

- CyLab