## Some Reflections (on DRAM)

Onur Mutlu <u>omutlu@gmail.com</u> <u>https://people.inf.ethz.ch/omutlu</u> 25 June 2019 Maurice Wilkes Award @ ISCA 2019

- On Maurice Wilkes

- Thanks

- A Sketch of Our DRAM Work

- Looking to the Future

## On Maurice Wilkes (I)

Maurice Wilkes, "The Best Way to Design an Automatic Calculating Machine," Manchester Univ. Computer Inaugural Conf., 1951.

#### THE BEST WAY TO DESIGN AN AUTOMATIC CALCULATING MACHINE

By M. V. Wilkes, M.A., Ph.D., F.R.A.S.

The concept of microcoded/microprogrammed machines

## On Maurice Wilkes (II)

Wilkes, "Slave Memories and Dynamic Storage Allocation," IEEE Trans. On Electronic Computers, 1965.

#### Slave Memories and Dynamic Storage Allocation M. V. WILKES

#### Summary

The use is discussed of a fast core memory of, say, 32 000 words as a slave to a slower core memory of, say, one million words in such a way that in practical cases the effective access time is nearer that of the fast memory than that of the slow memory.

The concept of hardware cache

## Cache in 1962 (Bloom, Cohen, Porter)

Bloom, Cohen, Porter, "Considerations in the Design of a Computer with High Logic-to-Memory Speed Ratio," AIEE Gigacycle Computing Systems Winter Meeting, Jan. 1962.

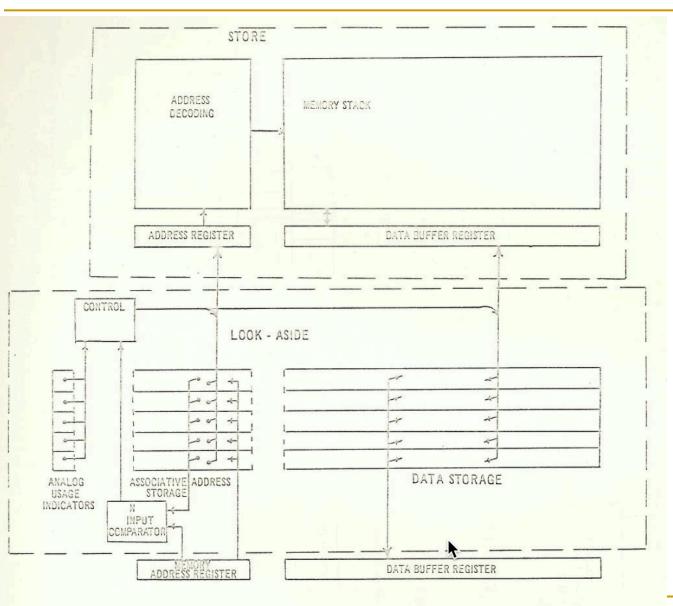

FIGURE 1. MEMORY (In this example, store is destructive read).

It is humbling to receive an award named after a true researcher and pioneer

## Special Thanks to...

- My PhD advisor, Yale Patt

- All my past and current teachers and family

- My students and trainees

- Lavanya Subramanian, Gennady Pekhimenko, Yixin Luo

- Samira Khan, Saugata Ghose

- Tyler Huberty

- Hasan Hassan, Amirali Boroumand

- My collaborators and past research groups

- Funding agencies and many industrial partners

## SAFARI Research Group

# SAFARI Research Group safari.ethz.ch

- On Maurice Wilkes

- Thanks

A Sketch of Our DRAM Work

Looking to the Future

## **DRAM** Controllers

## It All Started with FSB Controllers (2001)

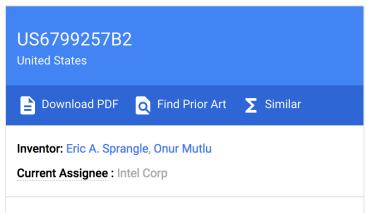

#### Method and apparatus to control memory accesses

#### Abstract

A method and apparatus for accessing memory comprising monitoring memory accesses from a hardware prefetcher and determining whether the memory accesses from the hardware prefetcher are used by an out-of-order core. A front side bus controller switches memory access modes from a minimize memory access latency mode to a maximize memory bus bandwidth mode if a percentage of the memory accesses generated by the hardware prefetcher are used by the out-of-order core.

#### Images (6)

#### Classifications

G06F12/0215 Addressing or allocation; Relocation with look ahead addressing means

#### Worldwide applications

2002 • <u>US</u> 2003 • <del>AU</del> JP DE KR CN WO GB TW 2004 • <del>US</del> 2005 • <del>HK</del>

#### Application US10/079,967 events ⑦

2002-02-21 • Application filed by Intel Corp

2002-02-21 • Priority to US10/079,967

2002-04-25 • Assigned to INTEL CORPORATION <sup>®</sup>

## Memory Performance Attacks [USENIX SEC'07]

Thomas Moscibroda and Onur Mutlu, <u>"Memory Performance Attacks: Denial of Memory Service</u> <u>in Multi-Core Systems"</u> *Proceedings of the <u>16th USENIX Security Symposium</u> (USENIX SECURITY)*, pages 257-274, Boston, MA, August 2007. <u>Slides</u> (ppt)

## Memory Performance Attacks: Denial of Memory Service in Multi-Core Systems

Thomas Moscibroda Onur Mutlu Microsoft Research {moscitho,onur}@microsoft.com

## STFM [MICRO'07]

Onur Mutlu and Thomas Moscibroda, "Stall-Time Fair Memory Access Scheduling for Chip Multiprocessors" Proceedings of the 40th International Symposium on Microarchitecture (MICRO), pages 146-158, Chicago, IL, December 2007. [Summary] [Slides (ppt)]

#### Stall-Time Fair Memory Access Scheduling for Chip Multiprocessors

Onur Mutlu Thomas Moscibroda

Microsoft Research {onur,moscitho}@microsoft.com

## PAR-BS [ISCA'08]

Onur Mutlu and Thomas Moscibroda, <u>"Parallelism-Aware Batch Scheduling: Enhancing both</u> <u>Performance and Fairness of Shared DRAM Systems"</u> *Proceedings of the <u>35th International Symposium on Computer</u> <u>Architecture</u> (ISCA), pages 63-74, Beijing, China, June 2008. [Summary] [Slides (ppt)]*

#### Parallelism-Aware Batch Scheduling: Enhancing both Performance and Fairness of Shared DRAM Systems

Onur Mutlu Thomas Moscibroda Microsoft Research {onur,moscitho}@microsoft.com Variants implemented in Samsung SoC memory controllers

Effective platform level approach and DRAM accesses are crucial to system performance. This paper touches this topics and suggest a superior approach to current known techniques. **Review from ISCA 2008**

## ATLAS Memory Scheduler [HPCA'10]

Yoongu Kim, Dongsu Han, Onur Mutlu, and Mor Harchol-Balter, <u>"ATLAS: A Scalable and High-Performance Scheduling</u> <u>Algorithm for Multiple Memory Controllers"</u> *Proceedings of the <u>16th International Symposium on High-</u> <u>Performance Computer Architecture</u> (HPCA), Bangalore, India, January 2010. <u>Slides (pptx)</u>*

#### ATLAS: A Scalable and High-Performance Scheduling Algorithm for Multiple Memory Controllers

Yoongu Kim Dongsu Han Onur Mutlu Mor Harchol-Balter Carnegie Mellon University

## Thread Cluster Memory Scheduling [MICRO'10]

Yoongu Kim, Michael Papamichael, Onur Mutlu, and Mor Harchol-Balter,

"Thread Cluster Memory Scheduling: Exploiting Differences in Memory Access Behavior"

Proceedings of the <u>43rd International Symposium on</u> Microarchitecture (MICRO), pages 65-76, Atlanta, GA, December 2010. Slides (pptx) (pdf)

Thread Cluster Memory Scheduling: Exploiting Differences in Memory Access Behavior

Yoongu Kim yoonguk@ece.cmu.edu

Michael Papamichael papamix@cs.cmu.edu Onur Mutlu onur@cmu.edu

Mor Harchol-Balter harchol@cs.cmu.edu

Carnegie Mellon University

## BLISS [ICCD'14, TPDS'16]

Lavanya Subramanian, Donghyuk Lee, Vivek Seshadri, Harsha Rastogi, and Onur Mutlu,

"The Blacklisting Memory Scheduler: Achieving High Performance and Fairness at Low Cost"

Proceedings of the 32nd IEEE International Conference on Computer Design (ICCD), Seoul, South Korea, October 2014.

[Slides (pptx) (pdf)]

## The Blacklisting Memory Scheduler: Achieving High Performance and Fairness at Low Cost

Lavanya Subramanian, Donghyuk Lee, Vivek Seshadri, Harsha Rastogi, Onur Mutlu Carnegie Mellon University {lsubrama,donghyu1,visesh,harshar,onur}@cmu.edu

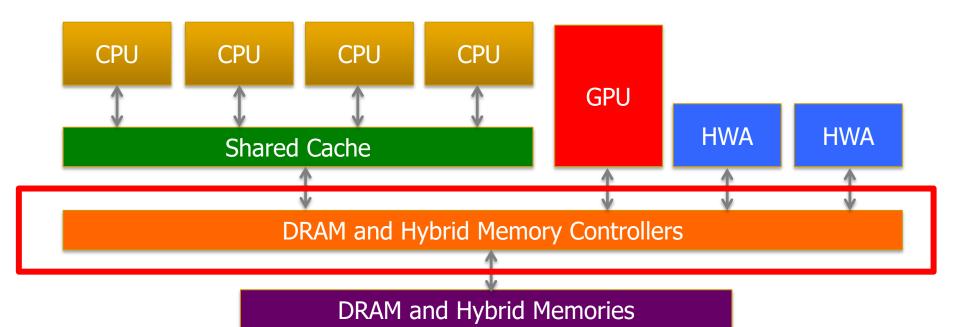

## Staged Memory Scheduling: CPU-GPU [ISCA'12]

Rachata Ausavarungnirun, Kevin Chang, Lavanya Subramanian, Gabriel Loh, and Onur Mutlu,

"Staged Memory Scheduling: Achieving High Performance and Scalability in Heterogeneous Systems" Proceedings of the <u>39th International Symposium on Computer</u> <u>Architecture</u> (ISCA), Portland, OR, June 2012. <u>Slides (pptx)</u>

#### Staged Memory Scheduling: Achieving High Performance and Scalability in Heterogeneous Systems

Rachata Ausavarungnirun<sup>†</sup> Kevin Kai-Wei Chang<sup>†</sup> Lavanya Subramanian<sup>†</sup> Gabriel H. Loh<sup>‡</sup> Onur Mutlu<sup>†</sup>

<sup>†</sup>Carnegie Mellon University {rachata,kevincha,lsubrama,onur}@cmu.edu

SAFARI

<sup>‡</sup>Advanced Micro Devices, Inc. gabe.loh@amd.com

## DASH: Heterogeneous Systems [TACO'16]

Hiroyuki Usui, Lavanya Subramanian, Kevin Kai-Wei Chang, and Onur Mutlu, **"DASH: Deadline-Aware High-Performance Memory Scheduler for Heterogeneous Systems with Hardware Accelerators**" ACM Transactions on Architecture and Code Optimization (TACO), Vol. 12, January 2016. Presented at the <u>11th HiPEAC Conference</u>, Prague, Czech Republic, January 2016. [Slides (pptx) (pdf)] [Source Code]

## DASH: Deadline-Aware High-Performance Memory Scheduler for Heterogeneous Systems with Hardware Accelerators

HIROYUKI USUI, LAVANYA SUBRAMANIAN, KEVIN KAI-WEI CHANG, and ONUR MUTLU, Carnegie Mellon University

## MISE: Predictable Performance [HPCA'13]

Lavanya Subramanian, Vivek Seshadri, Yoongu Kim, Ben Jaiyen, and Onur Mutlu,

"MISE: Providing Performance Predictability and Improving Fairness in Shared Main Memory Systems" Proceedings of the 19th International Symposium on High-Performance Computer Architecture (HPCA), Shenzhen, China, February 2013. Slides (pptx)

#### MISE: Providing Performance Predictability and Improving Fairness in Shared Main Memory Systems

Lavanya Subramanian Vivek Seshadri

ivek Seshadri Yoongu Kim Ben Jaiyen Onur Mutlu Carnegie Mellon University

## ASM: Predictable Performance [MICRO'15]

Lavanya Subramanian, Vivek Seshadri, Arnab Ghosh, Samira Khan, and Onur Mutlu,

"The Application Slowdown Model: Quantifying and Controlling the Impact of Inter-Application Interference at Shared Caches and Main Memory"

Proceedings of the <u>48th International Symposium on Microarchitecture</u> (MICRO), Waikiki, Hawaii, USA, December 2015.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Poster (pptx) (pdf)]

[Source Code]

The Application Slowdown Model: Quantifying and Controlling the Impact of Inter-Application Interference at Shared Caches and Main Memory

> Lavanya Subramanian<sup>\*</sup>§ Vivek Seshadri<sup>\*</sup> Arnab Ghosh<sup>\*†</sup> Samira Khan<sup>\*‡</sup> Onur Mutlu<sup>\*</sup>

\*Carnegie Mellon University §Intel Labs <sup>†</sup>IIT Kanpur <sup>‡</sup>University of Virginia

# Memory Controllers are critical to research

# They will become even more important

## Memory Control is Getting More Complex

- Heterogeneous agents: CPUs, GPUs, and HWAs

- Main memory interference between CPUs, GPUs, HWAs

#### Many goals, many constraints, many metrics ...

## Memory Control w/ Machine Learning [ISCA'08]

Engin Ipek, Onur Mutlu, José F. Martínez, and Rich Caruana,

"Self Optimizing Memory Controllers: A Reinforcement Learning Approach"

Proceedings of the <u>35th International Symposium on Computer Architecture</u> (ISCA), pages 39-50, Beijing, China, June 2008. <u>Slides (pptx)</u>

#### Self-Optimizing Memory Controllers: A Reinforcement Learning Approach

Engin İpek<sup>1,2</sup> Onur Mutlu<sup>2</sup> José F. Martínez<sup>1</sup> Rich Caruana<sup>1</sup>

<sup>1</sup>Cornell University, Ithaca, NY 14850 USA

<sup>2</sup> Microsoft Research, Redmond, WA 98052 USA

# Memory Controllers: Many New Problems

# Main Memory Needs Intelligent Controllers

## DRAM Scaling Issues

## An "Early" Position Paper [IMW'13]

## Onur Mutlu, <u>"Memory Scaling: A Systems Architecture Perspective"</u> *Proceedings of the <u>5th International Memory</u> <u>Workshop</u> (<i>IMW*), Monterey, CA, May 2013. <u>Slides</u> (pptx) (pdf) <u>EETimes Reprint</u>

### Memory Scaling: A Systems Architecture Perspective

Onur Mutlu Carnegie Mellon University onur@cmu.edu http://users.ece.cmu.edu/~omutlu/

#### https://people.inf.ethz.ch/omutlu/pub/memory-scaling\_memcon13.pdf

## Challenges in DRAM Scaling

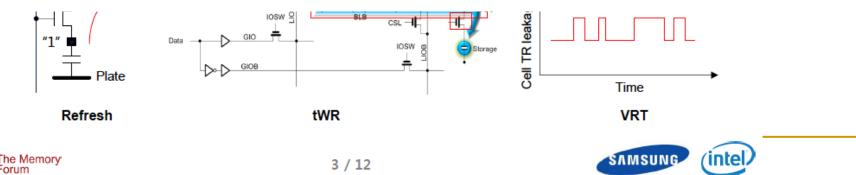

#### Refresh

- Latency

- Bank conflicts/parallelism

- Reliability and vulnerabilities

- Energy & power

- Memory's inability to do more than store data

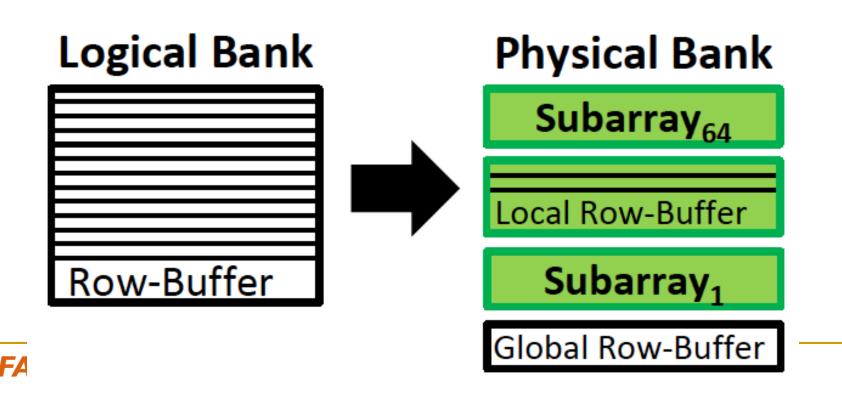

## SALP: Subarray-Level Parallelism [ISCA'12]

- Problem: Bank conflicts are costly for performance and energy

- Goal: Reduce bank conflicts without adding more banks (low cost)

- Observation: A DRAM bank is divided into subarrays

- Idea: Enable mostly-parallel access to different subarrays

## SALP: Subarray-Level Parallelism [ISCA'12]

Yoongu Kim, Vivek Seshadri, Donghyuk Lee, Jamie Liu, and Onur Mutlu,

<u>"A Case for Exploiting Subarray-Level Parallelism</u> (SALP) in DRAM"

Proceedings of the <u>39th International Symposium on</u>

<u>Computer Architecture</u> (**ISCA**), Portland, OR, June 2012. <u>Slides (pptx)</u>

#### A Case for Exploiting Subarray-Level Parallelism (SALP) in DRAM

Yoongu Kim

Vivek Seshadri Donghyuk Lee

Jamie Liu Onur Mutlu

Carnegie Mellon University

## More on SALP [Memory Forum'14]

#### **DRAM Process Scaling Challenges**

#### \* Refresh

Difficult to build high-aspect ratio cell capacitors decreasing cell capacitance

THE MEMORY FORUM 2014

## Co-Architecting Controllers and DRAM to Enhance DRAM Process Scaling

Uksong Kang, Hak-soo Yu, Churoo Park, \*Hongzhong Zheng, \*\*John Halbert, \*\*Kuljit Bains, SeongJin Jang, and Joo Sun Choi

Samsung Electronics, Hwasung, Korea / \*Samsung Electronics, San Jose / \*\*Intel

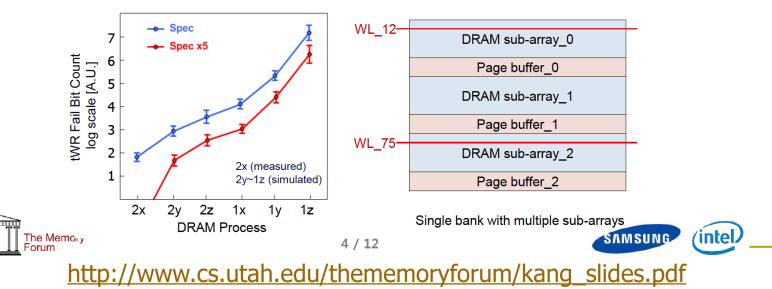

## More on SALP [Memory Forum'14]

#### **Sub-array Level Parallelism with tWR Relaxation**

#### tWR relaxation

SAFAR

- Relaxing tWR results in DRAM yield improvement but can degrade performance requiring new compensating features

- By increasing tWR 5X (from 15ns to 75ns), fail bit counts are expected to reduce by 1 to 2 orders of magnitudes

#### Sub-array level parallelism (SALP)

- Allows a page in another sub-array in the same bank to be opened in parallel with the currently activated sub-array

- Results in performance gain by increasing the row access parallelism within a bank

⇒ Used to compensate for the performance loss caused by tWR relaxation

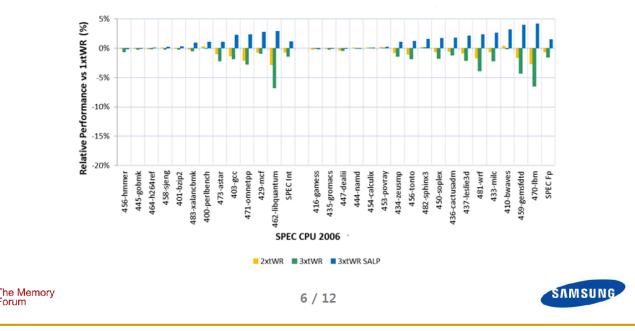

## More on SALP [Memory Forum'14]

#### **Performance Impact of SALP and tWR relaxation**

- Performance simulations run for various workloads when tWR is relaxed by 2X and 3X, and when SALP is applied with 2 sub-banks

- Results show that performance is reduced by ~5% and ~2% in average if tWR is relaxed by 3X and 2X, respectively

- Results also show that performance is compensated, and even improved to up to ~3% in average when SALP is applied, even with tWR relaxed by 3X

**SAFARI**

#### http://www.cs.utah.edu/thememoryforum/kang\_slides.pdf

**inte**

## Low-Cost DRAM Changes Enable Large Parallelism

### Most Recent Example: CROW [ISCA'19]

Hasan Hassan, Minesh Patel, Jeremie S. Kim, A. Giray Yaglikci, Nandita Vijaykumar, Nika Mansourighiasi, Saugata Ghose, and Onur Mutlu,

"CROW: A Low-Cost Substrate for Improving DRAM Performance, Energy Efficiency, and Reliability" Proceedings of the 46th International Symposium on Computer

<u>Architecture</u> (**ISCA**), Phoenix, AZ, USA, June 2019.

#### CROW: A Low-Cost Substrate for Improving DRAM Performance, Energy Efficiency, and Reliability

Hasan Hassan<sup>†</sup>Minesh Patel<sup>†</sup>Jeremie S. Kim<sup>†§</sup>A. Giray Yaglikci<sup>†</sup>Nandita Vijaykumar<sup>†§</sup>Nika Mansouri Ghiasi<sup>†</sup>Saugata Ghose<sup>§</sup>Onur Mutlu<sup>†§</sup>

<sup>†</sup>*ETH Zürich* <sup>§</sup>*Carnegie Mellon University*

## DRAM Refresh Problem

### Most Refreshes Are Unnecessary

Retention Time Profile of DRAM looks like this:

# \_64-128ms >256ms

Location dependent Stored value pattern dependent Time dependent

#### SAFARI

## RAIDR [ISCA'12]

Jamie Liu, Ben Jaiyen, Richard Veras, and Onur Mutlu, "RAIDR: Retention-Aware Intelligent DRAM Refresh" Proceedings of the <u>39th International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2012. <u>Slides (pdf)</u>

#### **RAIDR: Retention-Aware Intelligent DRAM Refresh**

Jamie Liu Ben Jaiyen Richard Veras Onur Mutlu Carnegie Mellon University

#### Infrastructures to Understand and Model DRAM Issues

Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors (Kim et al., ISCA 2014)

Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case (Lee et al., HPCA 2015)

AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems (Qureshi et al., DSN 2015) An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms (Liu et al., ISCA 2013)

The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study (Khan et al., SIGMETRICS 2014)

#### SAFARI

#### Infrastructures to Understand and Model DRAM Issues

#### **SAFARI** Kim+, "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," ISCA 2014.

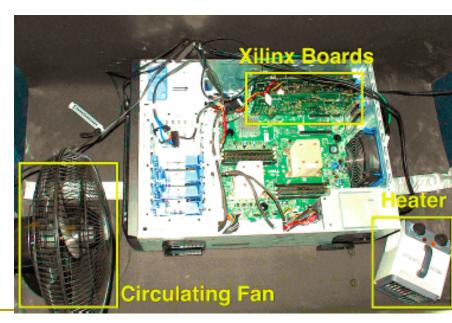

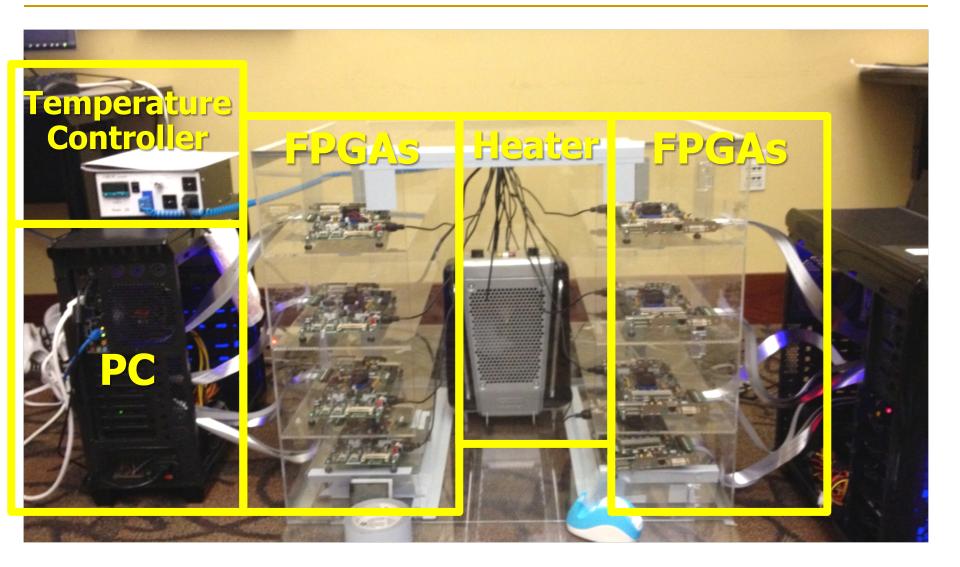

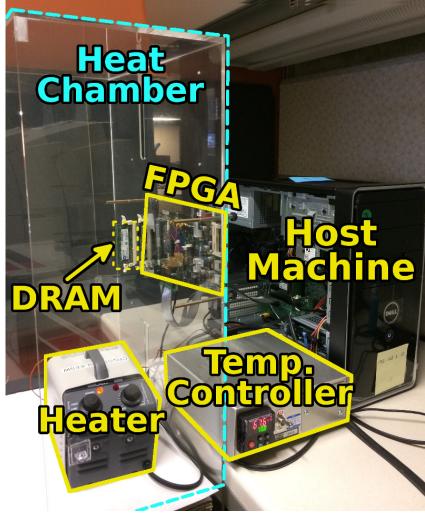

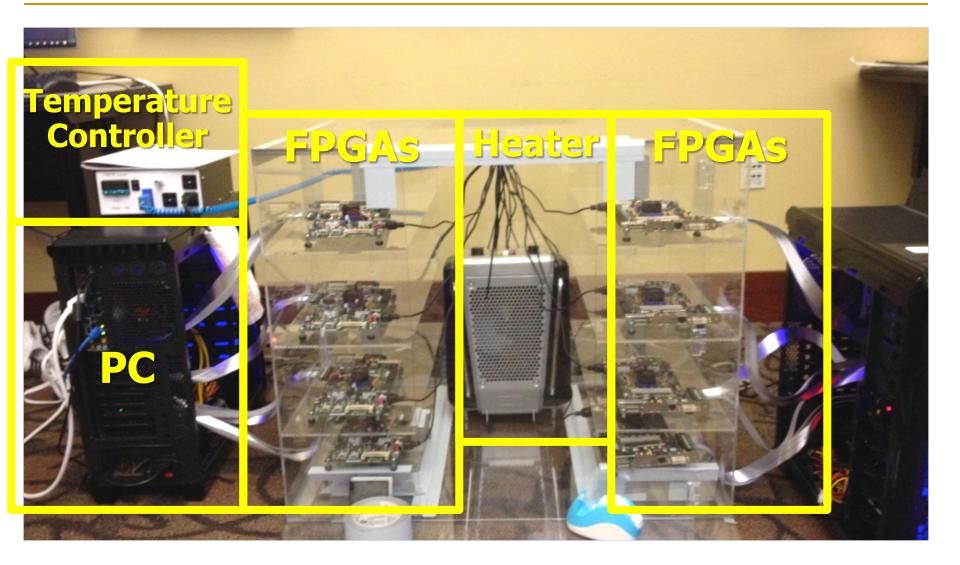

### SoftMC: Open Source DRAM Infrastructure

Hasan Hassan et al., "<u>SoftMC: A</u> <u>Flexible and Practical Open-</u> <u>Source Infrastructure for</u> <u>Enabling Experimental DRAM</u> <u>Studies</u>," HPCA 2017.

- Flexible

- Easy to Use (C++ API)

- Open-source

github.com/CMU-SAFARI/SoftMC

#### SAFARI

https://github.com/CMU-SAFARI/SoftMC

#### SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

Hasan Hassan<sup>1,2,3</sup> Nandita Vijaykumar<sup>3</sup> Samira Khan<sup>4,3</sup> Saugata Ghose<sup>3</sup> Kevin Chang<sup>3</sup> Gennady Pekhimenko<sup>5,3</sup> Donghyuk Lee<sup>6,3</sup> Oguz Ergin<sup>2</sup> Onur Mutlu<sup>1,3</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>TOBB University of Economics & Technology <sup>3</sup>Carnegie Mellon University <sup>4</sup>University of Virginia <sup>5</sup>Microsoft Research <sup>6</sup>NVIDIA Research

#### SAFARI

## Mitigating Refresh Issues

## Analysis of Data Retention Failures [ISCA'13]

Jamie Liu, Ben Jaiyen, Yoongu Kim, Chris Wilkerson, and Onur Mutlu,

"An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms" Proceedings of the <u>40th International Symposium on Computer Architecture</u> (ISCA), Tel-Aviv, Israel, June 2013. <u>Slides (ppt)</u> <u>Slides (pdf)</u>

#### An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms

Jamie Liu\* Ben Jaiyen<sup>\*</sup> Yoongu Kim Carnegie Mellon University Carnegie Mellon University Carnegie Mellon University 5000 Forbes Ave. 5000 Forbes Ave. 5000 Forbes Ave. Pittsburgh, PA 15213 Pittsburgh, PA 15213 Pittsburgh, PA 15213 jamiel@alumni.cmu.edu bjaiyen@alumni.cmu.edu yoonguk@ece.cmu.edu Chris Wilkerson Onur Mutlu Intel Corporation Carnegie Mellon University 2200 Mission College Blvd. 5000 Forbes Ave. Santa Clara, CA 95054 Pittsburgh, PA 15213

onur@cmu.edu

chris.wilkerson@intel.com

## Mitigation of Retention Issues [SIGMETRICS'14]

Samira Khan, Donghyuk Lee, Yoongu Kim, Alaa Alameldeen, Chris Wilkerson, and Onur Mutlu, "The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study" Proceedings of the <u>ACM International Conference on Measurement and</u> Modeling of Computer Systems (SIGMETRICS), Austin, TX, June 2014. [Slides] (pptx) (pdf)] [Poster (pptx) (pdf)] [Full data sets]

#### The Efficacy of Error Mitigation Techniques for DRAM **Retention Failures: A Comparative Experimental Study**

Samira Khan<sup>†</sup>\* samirakhan@cmu.edu

Donghyuk Lee<sup>†</sup> donghyuk1@cmu.edu

Chris Wilkerson\*

Yoongu Kim<sup>†</sup> yoongukim@cmu.edu

Alaa R. Alameldeen\* alaa.r.alameldeen@intel.com chris.wilkerson@intel.com

Onur Mutlu<sup>†</sup> onur@cmu.edu

<sup>†</sup>Carnegie Mellon University \*Intel Labs

SAFARI

## Handling Variable Retention Time [DSN'15]

Moinuddin Qureshi, Dae Hyun Kim, Samira Khan, Prashant Nair, and Onur Mutlu, "AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM <u>Systems</u>" *Proceedings of the <u>45th Annual IEEE/IFIP International Conference on</u> <i>Dependable Systems and Networks* (DSN), Rio de Janeiro, Brazil, June 2015. [Slides (pptx) (pdf)]

#### AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems

Moinuddin K. Qureshi<sup>†</sup> Dae-Hyun Kim<sup>†</sup> <sup>†</sup>Georgia Institute of Technology {*moin, dhkim, pnair6*}@*ece.gatech.edu*  Samira Khan<sup>‡</sup>

Prashant J. Nair<sup>†</sup> Onur Mutlu<sup>‡</sup> <sup>‡</sup>Carnegie Mellon University

{samirakhan, onur}@cmu.edu

## Handling Data-Dependent Failures [DSN'16]

Samira Khan, Donghyuk Lee, and Onur Mutlu,

"PARBOR: An Efficient System-Level Technique to Detect Data-Dependent Failures in DRAM"

Proceedings of the <u>45th Annual IEEE/IFIP International Conference on</u> Dependable Systems and Networks (DSN), Toulouse, France, June 2016.

[Slides (pptx) (pdf)]

#### PARBOR: An Efficient System-Level Technique to Detect Data-Dependent Failures in DRAM

Samira Khan<sup>\*</sup> Donghyuk Lee<sup>†‡</sup> Onur Mutlu<sup>\*†</sup> \*University of Virginia <sup>†</sup>Carnegie Mellon University <sup>‡</sup>Nvidia \*ETH Zürich

## Handling Data-Dependent Failures [MICRO'17]

Samira Khan, Chris Wilkerson, Zhe Wang, Alaa R. Alameldeen, Donghyuk Lee, and Onur Mutlu,

"Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content"

Proceedings of the 50th International Symposium on Microarchitecture (MICRO), Boston, MA, USA, October 2017.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Poster (pptx) (pdf)]

#### Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content

Samira Khan<sup>\*</sup> Chris Wilkerson<sup>†</sup> Zhe Wang<sup>†</sup> Alaa R. Alameldeen<sup>†</sup> Donghyuk Lee<sup>‡</sup> Onur Mutlu<sup>\*</sup> <sup>\*</sup>University of Virginia <sup>†</sup>Intel Labs <sup>‡</sup>Nvidia Research <sup>\*</sup>ETH Zürich

#### **SAFARI**

## Handling Both DPD and VRT [ISCA'17]

- Minesh Patel, Jeremie S. Kim, and Onur Mutlu,

"The Reach Profiler (REAPER): Enabling the Mitigation of DRAM Retention Failures via Profiling at Aggressive Conditions"

Proceedings of the <u>44th International Symposium on Computer</u> Architecture (ISCA), Toronto, Canada, June 2017.

[Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

- First experimental analysis of (mobile) LPDDR4 chips

- Analyzes the complex tradeoff space of retention time profiling

- Idea: enable fast and robust profiling at higher refresh intervals & temperatures

#### The Reach Profiler (REAPER): Enabling the Mitigation of DRAM Retention Failures via Profiling at Aggressive Conditions

Minesh Patel<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> Onur Mutlu<sup>§‡</sup> <sup>§</sup>ETH Zürich <sup>‡</sup>Carnegie Mellon University

#### SAFARI

## Understanding In-DRAM ECC [DSN'19]

Minesh Patel, Jeremie S. Kim, Hasan Hassan, and Onur Mutlu, "Understanding and Modeling On-Die Error Correction in Modern DRAM: An Experimental Study Using Real Devices" Proceedings of the <u>49th Annual IEEE/IFIP International Conference on</u> Dependable Systems and Networks (DSN), Portland, OR, USA, June 2019. [Source Code for EINSim, the Error Inference Simulator] Best paper session.

#### Understanding and Modeling On-Die Error Correction in Modern DRAM: An Experimental Study Using Real Devices

Minesh Patel<sup>†</sup> Jeremie S. Kim<sup>‡†</sup> Hasan Hassan<sup>†</sup> Onur Mutlu<sup>†‡</sup>  $^{\dagger}ETH Z \ddot{u}rich$  <sup>‡</sup>Carnegie Mellon University

# Most Refreshes Can Be Eliminated

# Main Memory Needs Intelligent Controllers

### Principle: Build Infrastructure

# Build Infrastructure to Enable Your Passion

#### Ramulator [IEEE CAL'15]

- Yoongu Kim, Weikun Yang, and Onur Mutlu,

"Ramulator: A Fast and Extensible DRAM Simulator"

<u>IEEE Computer Architecture Letters</u> (CAL), March 2015.

[Source Code]

- Source code is released under the liberal MIT License

<u>https://github.com/CMU-SAFARI/ramulator</u>

#### Ramulator: A Fast and Extensible DRAM Simulator

Yoongu Kim<sup>1</sup> Weikun Yang<sup>1,2</sup> Onur Mutlu<sup>1</sup> <sup>1</sup>Carnegie Mellon University <sup>2</sup>Peking University

## RowHammer

### Infrastructures Enable Scientific Inquiry

#### **SAFARI** Kim+, "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," ISCA 2014.

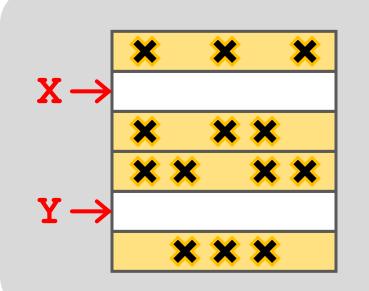

A Curious Observation [Kim et al., ISCA 2014]

# One can predictably induce errors in most DRAM memory chips

#### RowHammer

- One can predictably induce bit flips in commodity DRAM chips

>80% of the tested DRAM chips are vulnerable

- First example of how a simple hardware failure mechanism can create a widespread system security vulnerability

## A Simple Program Can Induce Many Errors

loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop

Download from: <a href="https://github.com/CMU-SAFARI/rowhammer">https://github.com/CMU-SAFARI/rowhammer</a>

#### One Can Take Over an Otherwise-Secure System

Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

> Abstract. Memory isolation is a key property of a reliable and secure computing system — an access to one memory address should not have unintended side effects on data stored

> in other addresses. However, as DRAM process technology

## Project Zero

Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors (Kim et al., ISCA 2014)

News and updates from the Project Zero team at Google

Exploiting the DRAM rowhammer bug to gain kernel privileges (Seaborn, 2015)

Monday, March 9, 2015

Exploiting the DRAM rowhammer bug to gain kernel privileges

## More Security Implications (I)

#### "We can gain unrestricted access to systems of website visitors."

www.iaik.tugraz.at

Not there yet, but ...

ROOT privileges for web apps!

Daniel Gruss (@lavados), Clémentine Maurice (@BloodyTangerine), December 28, 2015 - 32c3, Hamburg, Germany

Rowhammer.js: A Remote Software-Induced Fault Attack in JavaScript (DIMVA'16)

Source: https://lab.dsst.io/32c3-slides/7197.html

29

## More Security Implications (II)

"Can gain control of a smart phone deterministically"

## Hammer And Root

## androids Millions of Androids

Drammer: Deterministic Rowhammer

Attacks on Mobile Platforms, CCS'16

Source: https://fossbytes.com/drammer-rowhammer-attack-android-root-devices/

## More Security Implications (III)

Using an integrated GPU in a mobile system to remotely escalate privilege via the WebGL interface

ars TECHNICA

BIZ & IT TECH SCIENCE POLICY CARS GAMING & CULTURE

####

# Drive-by Rowhammer attack uses GPU to compromise an Android phone

JavaScript based GLitch pwns browsers by flipping bits inside memory chips.

DAN GOODIN - 5/3/2018, 12:00 PM

#### Grand Pwning Unit: Accelerating Microarchitectural Attacks with the GPU

Pietro Frigo Vrije Universiteit Amsterdam p.frigo@vu.nl Cristiano Giuffrida Vrije Universiteit Amsterdam giuffrida@cs.vu.nl Herbert Bos Vrije Universiteit Amsterdam herbertb@cs.vu.nl Kaveh Razavi Vrije Universiteit Amsterdam kaveh@cs.vu.nl

## More Security Implications (IV)

#### Rowhammer over RDMA (I)

ars TECHNICA

BIZ & IT TECH SCIENCE POLICY CARS GAMING & CULTURE

THROWHAMMER —

# Packets over a LAN are all it takes to trigger serious Rowhammer bit flips

The bar for exploiting potentially serious DDR weakness keeps getting lower.

DAN GOODIN - 5/10/2018, 5:26 PM

#### **Throwhammer: Rowhammer Attacks over the Network and Defenses**

Andrei Tatar VU Amsterdam Radhesh Krishnan VU Amsterdam Elias Athanasopoulos University of Cyprus

Herbert Bos VU Amsterdam Kaveh Razavi VU Amsterdam Cristiano Giuffrida VU Amsterdam

## More Security Implications (V)

Rowhammer over RDMA (II)

# Security in a serious way

Nethammer—Exploiting DRAM Rowhammer Bug Through Network Requests

#### Nethammer: Inducing Rowhammer Faults through Network Requests

Moritz Lipp Graz University of Technology

Daniel Gruss Graz University of Technology Misiker Tadesse Aga University of Michigan

Clémentine Maurice Univ Rennes, CNRS, IRISA

Lukas Lamster Graz University of Technology Michael Schwarz Graz University of Technology

Lukas Raab Graz University of Technology

### More Security Implications (VI)

IEEE S&P 2020

#### RAMBleed: Reading Bits in Memory Without Accessing Them

Andrew Kwong University of Michigan ankwong@umich.edu Daniel Genkin University of Michigan genkin@umich.edu Daniel Gruss Graz University of Technology daniel.gruss@iaik.tugraz.at Yuval Yarom University of Adelaide and Data61 yval@cs.adelaide.edu.au

## More Security Implications?

### Seven RowHammer Solutions

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

"Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors"

Proceedings of the <u>41st International Symposium on Computer</u>

<u>Architecture</u> (ISCA), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data]

#### Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly<sup>\*</sup> Jeremie Kim<sup>1</sup> Chris Fallin<sup>\*</sup> Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup> <sup>1</sup>Carnegie Mellon University <sup>2</sup>Intel Labs

## Apple's Patch for RowHammer

#### https://support.apple.com/en-gb/HT204934

Available for: OS X Mountain Lion v10.8.5, OS X Mavericks v10.9.5

Impact: A malicious application may induce memory corruption to escalate privileges

Description: A disturbance error, also known as Rowhammer, exists with some DDR3 RAM that could have led to memory corruption. This issue was mitigated by increasing memory refresh rates.

CVE-ID

CVE-2015-3693 : Mark Seaborn and Thomas Dullien of Google, working from original research by Yoongu Kim et al (2014)

HP, Lenovo, and other vendors released similar patches

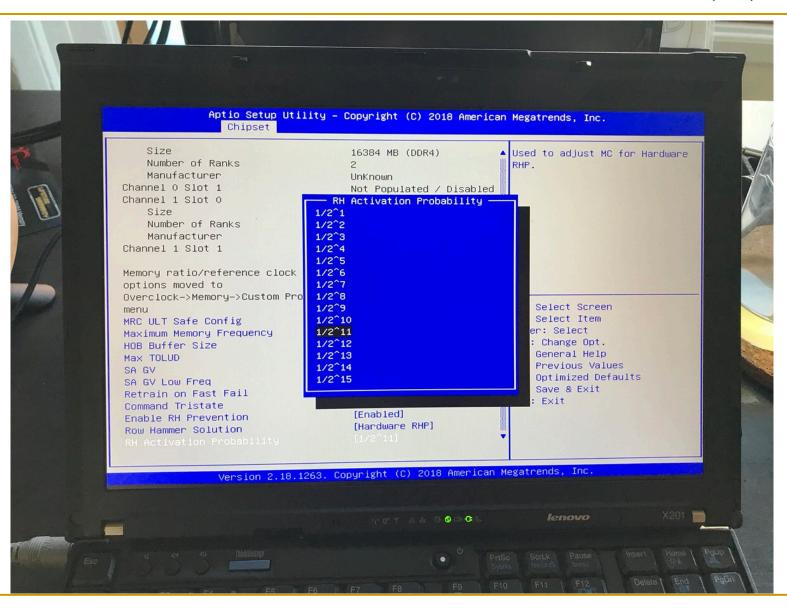

## **Our Solution to RowHammer**

- PARA: <u>Probabilistic Adjacent Row Activation</u>

- Key Idea

- After closing a row, we activate (i.e., refresh) one of its neighbors with a low probability: p = 0.005

- Reliability Guarantee

- When p=0.005, errors in one year:  $9.4 \times 10^{-14}$

- By adjusting the value of p, we can vary the strength of protection against errors

# Probabilistic Activation in Real Life (I)

| Aptio S<br>Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | y – Copyright (C) 2018 American Megatrends, Inc.                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel O Slot O<br>Size<br>Number of Ranks<br>Manufacturer<br>Channel O Slot 1<br>Channel 1 Slot O<br>Size<br>Number of Ranks<br>Manufacturer<br>Channel 1 Slot 1<br>Memory ratio/reference<br>options moved to<br>Overclock->Memory=>CM<br>menu<br>MRC ULT Safe Config<br>Maximum Memory Freque<br>HOB Buffer Size<br>Max TOLUD<br>SA GV<br>SA GV<br>SA GV<br>SA GV<br>SA GV<br>SA GV<br>SA GV<br>SA GV Low Freq<br>Retrain on Fast Fail<br>Command Tristate<br>Enable RH Prevention<br>Row Hammer Solution | [Disabled][Auto][Auto][Auto][Dynamic][Dynamic][Enabled][Enabled][Enabled][Enabled][Enabled][Enabled][Enabled][Enabled][Enabled][Enabled][Enabled][Hardware RHP] |

| Versi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . Copyright (C) 2018 American Megatrends, Inc.                                                                                                                  |

**SAFARI**

https://twitter.com/isislovecruft/status/1021939922754723841

# Probabilistic Activation in Real Life (II)

SAFARI

https://twitter.com/isislovecruft/status/1021939922754723841

# The Original RowHammer Analysis

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

"Flipping Bits in Memory Without Accessing Them: An

Experimental Study of DRAM Disturbance Errors"

Proceedings of the 41st International Symposium on Computer

Architecture (ISCA), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data]

## Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly<sup>\*</sup> Jeremie Kim<sup>1</sup> Chris Fallin<sup>\*</sup> Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup> <sup>1</sup>Carnegie Mellon University <sup>2</sup>Intel Labs

## RowHammer: 5 Years Later

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

<u>IEEE Transactions on Computer-Aided Design of Integrated</u>

<u>Circuits and Systems</u> (TCAD) Special Issue on Top Picks in Hardware and Embedded Security, 2019.

# RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> <sup>§</sup>ETH Zürich <sup>‡</sup>Carnegie Mellon University

# First example of how a simple hardware failure mechanism can create a widespread security vulnerability

# Main Memory Needs Intelligent Controllers for Security

# RowHammer: Retrospective

- New mindset that has enabled a renewed interest in HW security attack research:

- Real (memory) chips are vulnerable, in a simple and widespread manner

→ this causes real security problems

- Hardware reliability  $\rightarrow$  security connection is now mainstream discourse

- Many new RowHammer attacks...

- Tens of papers in top security venues

- More to come as RowHammer is getting worse (DDR4 & beyond)

- Many new RowHammer solutions...

- Apple security release; Memtest86 updated

- Many solution proposals in top venues (latest in ISCA 2019)

- Principled system-DRAM co-design (in original RowHammer paper)

- More to come...

# Perhaps Most Importantly...

- RowHammer enabled a shift of mindset in mainstream security researchers

- □ General-purpose hardware is fallible, in a widespread manner

- Its problems are exploitable

- This mindset has enabled many systems security researchers to examine hardware in more depth

- And understand HW's inner workings and vulnerabilities

- It is no coincidence that two of the groups that discovered Meltdown and Spectre heavily worked on RowHammer attacks before

- More to come...

# Initial RowHammer Reviews

#### Disturbance Errors in DRAM: Demonstration, Characterization, and Prevention

5

2

4

Rejected (R2)

7 86

863kB Friday 31 May 2013 2:00:53pm PDT

4

4

3

b9bf06021da54cddf4cd0b3565558a181868b972

You are an **author** of this paper.

+ Abstract

SAFARI

+ AUTHORS

5

5

3

4

4

veMer Nov WriQua RevExp

4

3

2

4

4

|             | 0 |

|-------------|---|

| Review #66A |   |

| Review #66B |   |

| Review #66C |   |

| Review #66D |   |

| Review #66E |   |

| Review #66F |   |

|             |   |

# Missing the Point Reviews from Micro 2013

PAPER WEAKNESSES

This is an excellent test methodology paper, but there is no micro-architectural or architectural content.

PAPER WEAKNESSES

- Whereas they show disturbance may happen in DRAM array, authors don't show it can be an issue in realistic DRAM usage scenario

- Lacks architectural/microarchitectural impact on the DRAM disturbance analysis

#### PAPER WEAKNESSES

The mechanism investigated by the authors is one of many well known disturb mechanisms. The paper does not discuss the root causes to sufficient depth and the importance of this mechanism compared to others. Overall the length of the sections restating known information is much too long in relation to new work.

## More ...

# **Reviews from ISCA 2014**

#### PAPER WEAKNESSES

1) The disturbance error (a.k.a coupling or cross-talk noise induced error) is a known problem to the DRAM circuit community.

2) What you demonstrated in this paper is so called DRAM row hammering issue - you can even find a Youtube video showing this! - <u>http://www.youtube.com</u>/watch?v=i3-gQSnBcdo

2) The architectural contribution of this study is too insignificant.

#### **P**APER WEAKNESSES

Row Hammering appears to be well-known, and solutions have already been proposed by industry to address the issue.

The paper only provides a qualitative analysis of solutions to the problem. A more robust evaluation is really needed to know whether the proposed solution is

# Suggestions to Reviewers

- Be fair; you do not know it all

- Be open-minded; you do not know it all

- Be accepting of diverse research methods: there is no single way of doing research

- Be constructive, not destructive

- Do not have double standards...

Do not block or delay scientific progress for non-reasons

# We Need to Fix the Reviewer Accountability Problem

Suggestion to Community

# Eliminate Double Standards

Suggestion to Researchers: Principle: Passion

# Follow Your Passion (Do not get derailed by naysayers)

Suggestion to Researchers: Principle: Resilience

# **Be Resilient**

# Principle: Learning and Scholarship

# Focus on learning and scholarship

# Principle: Learning and Scholarship

# The quality of your work defines your impact

# Reducing DRAM Latency

# Donghyuk Lee's PhD Thesis [СМU 2015]

#### Reducing DRAM Latency at Low Cost by Exploiting Heterogeneity

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in

Electrical and Computer Engineering

#### Donghyuk Lee

M.S., Electrical and Computer Engineering, Carnegie Mellon University B.S., Electrical Engineering, Seoul National University

#### SAFaki

# Kevin Chang's PhD Thesis [СМU 2017]

#### Understanding and Improving the Latency of DRAM-Based Memory Systems

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

Electrical and Computer Engineering

#### Kevin K. Chang

M.S., Electrical & Computer Engineering, Carnegie Mellon University **SAFAI** B.S., Electrical & Computer Engineering, Carnegie Mellon University

# Reducing DRAM Energy

# Enabling DRAM to Compute at Low Cost

# RowClone [MICRO'13]

Vivek Seshadri, Yoongu Kim, Chris Fallin, Donghyuk Lee, Rachata Ausavarungnirun, Gennady Pekhimenko, Yixin Luo, Onur Mutlu, Michael A. Kozuch, Phillip B. Gibbons, and Todd C. Mowry,

"RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization" Proceedings of the <u>46th International Symposium on Microarchitecture</u>

(*MICRO*), Davis, CA, December 2013. [<u>Slides (pptx)</u> (pdf)] [<u>Lightning Session</u> <u>Slides (pptx) (pdf)</u>] [<u>Poster (pptx)</u> (pdf)]

## RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization

Vivek Seshadri Yoongu Kim Chris Fallin\* Donghyuk Lee vseshadr@cs.cmu.edu yoongukim@cmu.edu cfallin@c1f.net donghyuk1@cmu.edu Rachata Ausavarungnirun Gennady Pekhimenko Yixin Luo rachata@cmu.edu gpekhime@cs.cmu.edu yixinluo@andrew.cmu.edu Onur Mutlu Phillip B. Gibbons<sup>†</sup> Michael A. Kozuch<sup>†</sup> Todd C. Mowry onur@cmu.edu phillip.b.gibbons@intel.com michael.a.kozuch@intel.com tcm@cs.cmu.edu Carnegie Mellon University <sup>†</sup>Intel Pittsburgh

# Ambit [MICRO'17]

Vivek Seshadri et al., "<u>Ambit: In-Memory Accelerator</u> for Bulk Bitwise Operations Using Commodity DRAM <u>Technology</u>," MICRO 2017.

#### Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology

Vivek Seshadri<sup>1,5</sup> Donghyuk Lee<sup>2,5</sup> Thomas Mullins<sup>3,5</sup> Hasan Hassan<sup>4</sup> Amirali Boroumand<sup>5</sup> Jeremie Kim<sup>4,5</sup> Michael A. Kozuch<sup>3</sup> Onur Mutlu<sup>4,5</sup> Phillip B. Gibbons<sup>5</sup> Todd C. Mowry<sup>5</sup>

<sup>1</sup>Microsoft Research India <sup>2</sup>NVIDIA Research <sup>3</sup>Intel <sup>4</sup>ETH Zürich <sup>5</sup>Carnegie Mellon University

# Ambit

SAFARI

Vivek Seshadri and Onur Mutlu,

<u>"In-DRAM Bulk Bitwise Execution Engine"</u> *Invited Book Chapter in Advances in Computers*, to appear in 2020.

[Preliminary arXiv version]

## In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu ETH Zürich onur.mutlu@inf.ethz.ch

# In-Memory Bulk Bitwise Operations

- We can support in-DRAM COPY, ZERO, AND, OR, NOT, MAJ

- At low cost

- Using analog computation capability of DRAM

- Idea: activating multiple rows performs computation

#### 30-74X performance and energy improvement

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology," MICRO 2017.

New memory technologies enable even more opportunities

# Sounds Good, No?

# **Review from ISCA 2016**

Paper summary

- The paper proposes to extend DRAM to include bulk, bit-wise logical

- operations directly between rows within the DRAM.

Strengths

- Very clever/novel idea.

- Great potential speedup and efficiency gains.

#### Weaknesses

- Probably won't ever be built. Not practical to assume DRAM manufacturers with change DRAM in this way.

## **Another Review from ISCA 2016**

**Strengths**

The proposed mechanisms effectively exploit the operation of the DRAM to perform efficient bitwise operations across entire rows of the DRAM.

Weaknesses

This requires a modification to the DRAM that will only help this type of bitwise operation. It seems unlikely that something like that will be adopted.

# Yet Another Review

## Yet Another Review from ISCA 2016

- Weaknesses

- The core novelty of Buddy RAM is almost all circuits-related (by exploiting sense amps). I do not find architectural innovation even though the circuits technique benefits architecturally by mitigating memory bandwidth and relieving cache resources within a subarray. The only related part is the new ISA support for bitwise operations at DRAM side and its induced issue on cache coherence.

# Aside: A Recommended Book

#### WILEY PROFESSIONAL COMPUTING

Raj Jain

#### THE ART OF COMPUTER SYSTEMS PERFORMANCE ANALYSIS

Techniques for Experimental Design, Measurement, Simulation, and Modeling

WILEY

Raj Jain, "The Art of Computer Systems Performance Analysis," Wiley, 1991.

DECISION MAKER'S GAMES

DECISION MAKER'S GAMES

Even if the performance analysis is correctly done and presented, it may not be enough to persuade your audience—the decision makers—to follow your recommendations. The list shown in Box 10.2 is a compilation of reasons for rejection heard at various performance analysis presentations. You can use the list by presenting it immediately and pointing out that the reason for rejection is not new and that the analysis deserves more consideration. Also, the list is helpful in getting the competing proposals rejected!

There is no clear end of an analysis. Any analysis can be rejected simply on the grounds that the problem needs more analysis. This is the first reason

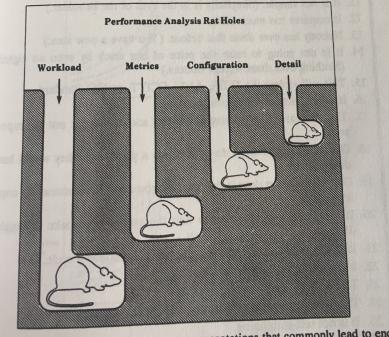

pisted in 2000 ysis and for endless debate is the workload. Since workloads are always based on the past measurements, their applicability to the current or future environment can always be questioned. Actually workload is one of the four areas of discussion that lead a performance presentation into an endless debate. These "rat holes" and their relative sizes in terms of time consumed are shown in Figure 10.26. Presenting this cartoon at the beginning of a presentation helps to avoid these areas.

FIGURE 10.26 Four issues in performance presentations that commonly lead to endless discussion. Raj Jain, "The Art of Computer Systems Performance Analysis," Wiley, 1991. Box 10.2 Reasons for Not Accepting the Results of an Analysis 1. This needs more analysis.

#### 2. You need a b You need a better among only for long I/O's, packets, jobs, and files It improves performance only for long I/O's, packets, jobs, and files

- and most of the I/O's, packets, jobs, and files are short. 4. It improves performance only for short I/O's, packets, jobs, and files,

- It improves performance of short I/O's, packets, jobs, and files, but who cares for the performance of short I/O's, packets, jobs, and files; its the long ones that impact the system.

- 5. It needs too much memory/CPU/bandwidth and memory/CPU/band. width isn't free.

- 6. It only saves us memory/CPU/bandwidth and memory/CPU/band. width is cheap.

- 7. There is no point in making the networks (similarly, CPUs/disks/...) faster; our CPUs/disks (any component other than the one being die cussed) aren't fast enough to use them.

- 8. It improves the performance by a factor of x, but it doesn't really matter at the user level because everything else is so slow.

- 9. It is going to increase the complexity and cost.

- 10. Let us keep it simple stupid (and your idea is not stupid).

- 11. It is not simple. (Simplicity is in the eyes of the beholder.)

- 12. It requires too much state.

- 13. Nobody has ever done that before. (You have a new idea.)

- 14. It is not going to raise the price of our stock by even an eighth. (Nothing ever does, except rumors.)

- 15. This will violate the IEEE, ANSI, CCITT, or ISO standard.

- 16. It may violate some future standard.

- 17. The standard says nothing about this and so it must not be important.

- 18. Our competitors don't do it. If it was a good idea, they would have done it.

- 19. Our competition does it this way and you don't make money by copying others.

- 20. It will introduce randomness into the system and make debugging difficult.

- 21. It is too deterministic; it may lead the system into a cycle.

- 22. It's not interoperable.

- 23. This impacts hardware.

- 24. That's beyond today's technology.

20. IU IS HUMAN

26. Why change-it's working OK.

Raj Jain, "The Art of **Computer Systems** Performance Analysis," Wiley, 1991.

# Into the Future

# Computing is Bottlenecked by Data

# Future Innovations Will Be Even More Bottlenecked by Memory

## We Need Architectures That Handle Data Well

# **Data-centric**

# **Data-driven**

# **Data-aware**

Challenge and Opportunity for Future

# Computing Architectures with

# Minimal Data Movement

## We Need to Revisit the Entire Stack

| Problem            | , |

|--------------------|---|

| Aigorithm          |   |

| Program/Language   |   |

| System Software    |   |

| SW/HW Interface    |   |

| Micro-architecture |   |

| Logic              | J |

| Devices            |   |

| Electrons          |   |

#### We can get there step by step

# Overview of PIM Challenges

SAFAR

## Processing Data Where It Makes Sense: Enabling In-Memory Computation

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>b,c</sup>

<sup>a</sup>ETH Zürich <sup>b</sup>Carnegie Mellon University <sup>c</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "Processing Data Where It Makes Sense: Enabling In-Memory Computation" Invited paper in Microprocessors and Microsystems (MICPRO), June 2019. [arXiv version]

https://arxiv.org/pdf/1903.03988.pdf

#### **SAFARI**

Source: http://spectrum.ieee.org/image/MjYzMzAyMg.jpeg

# Food for Thought: Two Quotes

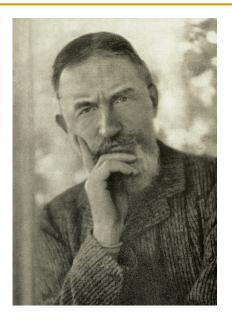

Progress is impossible without change, and those who cannot change their minds cannot change anything.

**George Bernard Shaw**

#### My heart is in the work.

#### **Andrew Carnegie**

Image: By Alvin Langdon Coburn - Illustrated London News, p. 575 (subscription required), PD-US, https://en.wikipedia.org/w/index.php?curid=49887931

# Some Reflections (on DRAM)

Onur Mutlu <u>omutlu@gmail.com</u> <u>https://people.inf.ethz.ch/omutlu</u> 25 June 2019 Maurice Wilkes Award @ ISCA 2019