## Memory Systems and Memory-Centric Computing

Lecture 4.1: Memory-Centric Computing III

Onur Mutlu

omutlu@gmail.com

https://people.inf.ethz.ch/omutlu

18 July 2024

**HiPEAC ACACES Summer School 2024**

## Agenda For Today

- Memory Systems and Memory-Centric Computing

- July 15-19, 2024

- Topic 1: Memory Trends, Challenges, Opportunities, Basics

- Topic 2: Memory-Centric Computing

- Topic 3: Memory Robustness: RowHammer, RowPress & Beyond

- Topic 4: Machine Learning Driven Memory Systems

- Topic 5 (another course): Architectures for Genomics and ML

- Topic 6 (unlikely): Non-Volatile Memories and Storage

- Topic 7 (unlikely): Memory Latency, Predictability & QoS

- Major Overview Reading:

- Mutlu et al., "A Modern Primer on Processing in Memory," Book Chapter on Emerging Computing and Devices, 2022.

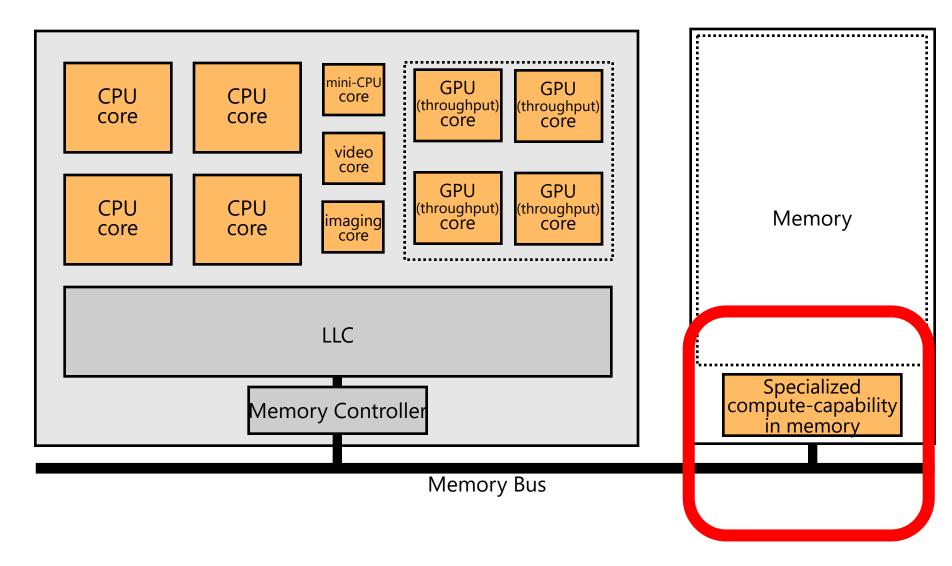

# Processing in Memory: Two Approaches

- 1. Processing using Memory

- 2. Processing **near** Memory

# Processing in Memory: Two Approaches

- 1. Processing using Memory

- 2. Processing near Memory

## PIM Review and Open Problems

## A Modern Primer on Processing in Memory

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b,c</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>d</sup>

SAFARI Research Group

<sup>a</sup>ETH Zürich

<sup>b</sup>Carnegie Mellon University

<sup>c</sup>University of Illinois at Urbana-Champaign

<sup>d</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun,

"A Modern Primer on Processing in Memory"

Invited Book Chapter in Emerging Computing: From Devices to Systems

Looking Beyond Moore and Von Neumann, Springer, to be published in 2021.

## Mindset: Memory as an Accelerator

Memory similar to a "conventional" accelerator

## In-Storage Acceleration of Genome Analytics

## In-Storage Genomic Data Filtering [ASPLOS 2022]

Nika Mansouri Ghiasi, Jisung Park, Harun Mustafa, Jeremie Kim, Ataberk Olgun, Arvid Gollwitzer, Damla Senol Cali, Can Firtina, Haiyu Mao, Nour Almadhoun Alserr, Rachata Ausavarungnirun, Nandita Vijaykumar, Mohammed Alser, and Onur Mutlu, "GenStore: A High-Performance and Energy-Efficient In-Storage Computing

<u>"GenStore: A High-Performance and Energy-Efficient In-Storage Computing System for Genome Sequence Analysis"</u>

Proceedings of the <u>27th International Conference on Architectural Support for</u>

<u>Programming Languages and Operating Systems</u> (**ASPLOS**), Virtual, February-March 2022.

[<u>Lightning Talk Slides (pptx) (pdf)</u>] [<u>Lightning Talk Video</u> (90 seconds)]

## GenStore: A High-Performance In-Storage Processing System for Genome Sequence Analysis

Nika Mansouri Ghiasi<sup>1</sup> Jisung Park<sup>1</sup> Harun Mustafa<sup>1</sup> Jeremie Kim<sup>1</sup> Ataberk Olgun<sup>1</sup> Arvid Gollwitzer<sup>1</sup> Damla Senol Cali<sup>2</sup> Can Firtina<sup>1</sup> Haiyu Mao<sup>1</sup> Nour Almadhoun Alserr<sup>1</sup> Rachata Ausavarungnirun<sup>3</sup> Nandita Vijaykumar<sup>4</sup> Mohammed Alser<sup>1</sup> Onur Mutlu<sup>1</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>Bionano Genomics <sup>3</sup>KMUTNB <sup>4</sup>University of Toronto

## In-Storage Metagenomics [ISCA 2024]

Nika Mansouri Ghiasi, Mohammad Sadrosadati, Harun Mustafa, Arvid Gollwitzer, Can Firtina, Julien Eudine, Haiyu Mao, Joel Lindegger, Meryem Banu Cavlak, Mohammed Alser, Jisung Park, and Onur Mutlu,

"MegIS: High-Performance and Low-Cost Metagenomic Analysis with In-Storage Processing"

Proceedings of the <u>51st Annual International Symposium on Computer</u> <u>Architecture</u> (**ISCA**), Buenos Aires, Argentina, July 2024.

[Slides (pptx) (pdf)]

arXiv version

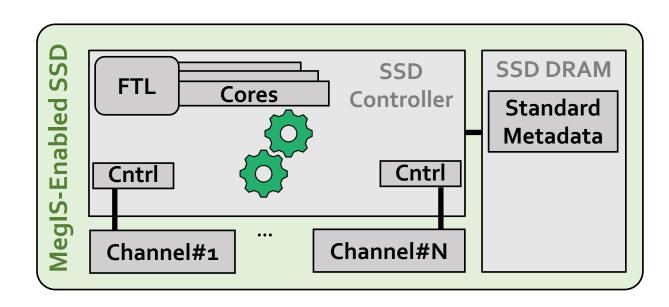

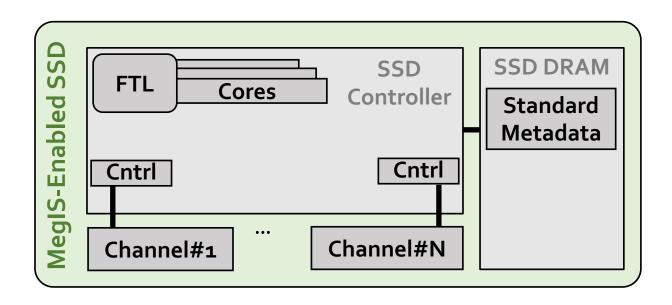

## MegIS: High-Performance, Energy-Efficient, and Low-Cost Metagenomic Analysis with In-Storage Processing

Nika Mansouri Ghiasi<sup>1</sup> Mohammad Sadrosadati<sup>1</sup> Harun Mustafa<sup>1</sup> Arvid Gollwitzer<sup>1</sup> Can Firtina<sup>1</sup> Julien Eudine<sup>1</sup> Haiyu Mao<sup>1</sup> Joël Lindegger<sup>1</sup> Meryem Banu Cavlak<sup>1</sup> Mohammed Alser<sup>1</sup> Jisung Park<sup>2</sup> Onur Mutlu<sup>1</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>POSTECH

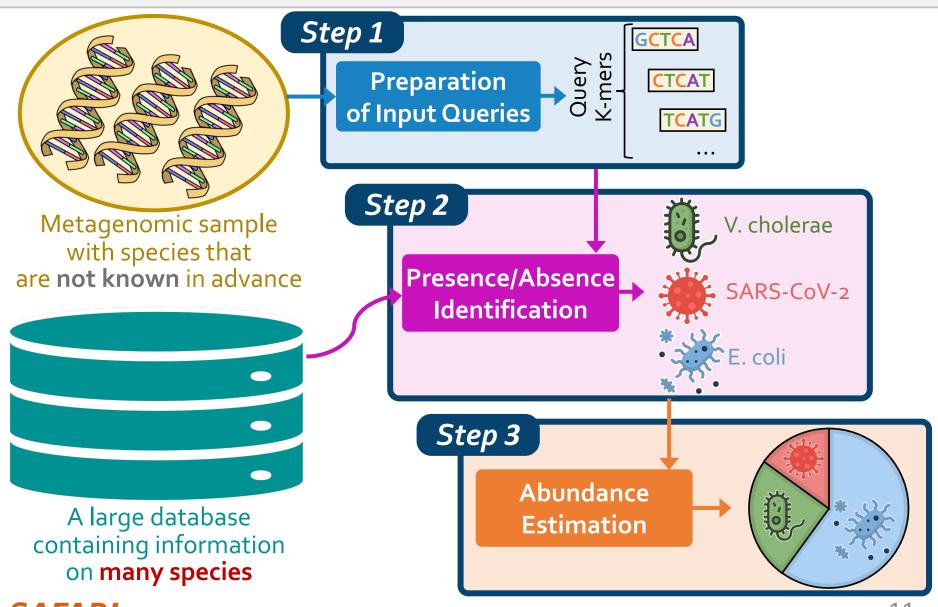

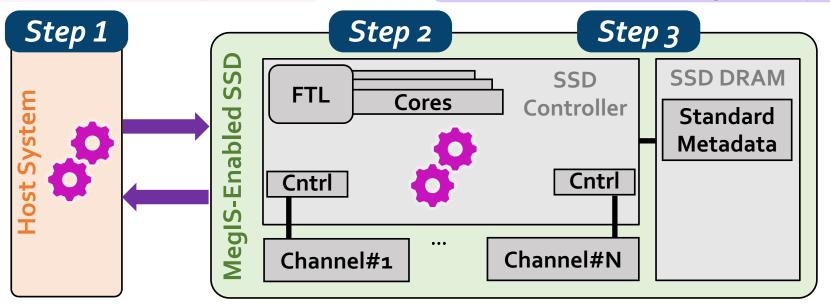

## MegIS: Metagenomics In-Storage

- First in-storage system for end-to-end metagenomic analysis

- Idea: Cooperative in-storage processing for metagenomic analysis

- Hardware/software co-design between

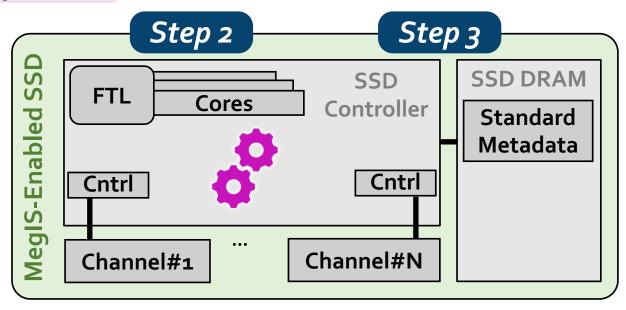

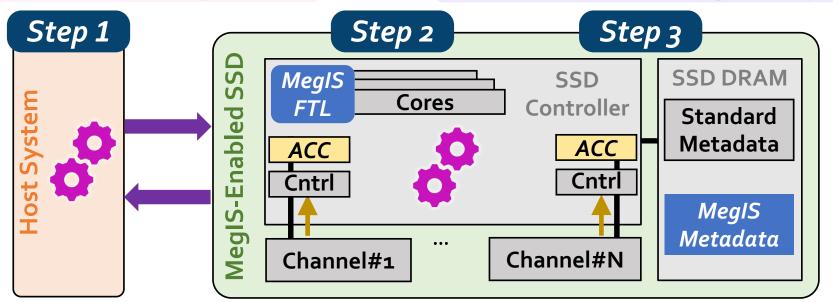

## MegIS's Steps

SAFARI

Host System

#### Task partitioning and mapping

• Each step executes in its most suitable system

#### Task partitioning and mapping

• Each step executes in its most suitable system

#### **Data/computation flow coordination**

- Reduce communication overhead

- Reduce #writes to flash chips

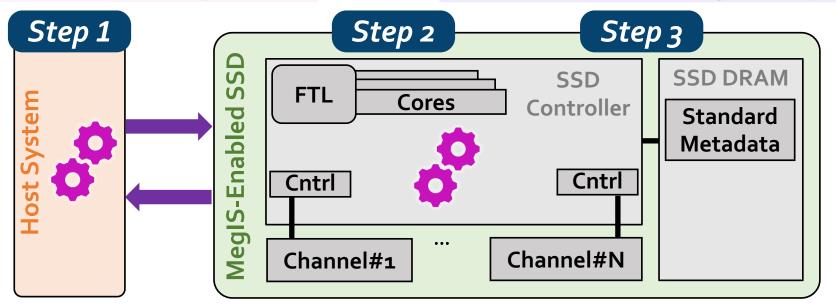

#### Task partitioning and mapping

• Each step executes in its most suitable system

#### Data/computation flow coordination

- Reduce communication overhead

- Reduce #writes to flash chips

#### Storage-aware algorithms

• Enable efficient access patterns to the SSD

#### Task partitioning and mapping

• Each step executes in its most suitable system

#### Data/computation flow coordination

- Reduce communication overhead

- Reduce #writes to flash chips

#### Storage-aware algorithms

• Enable efficient access patterns to the SSD

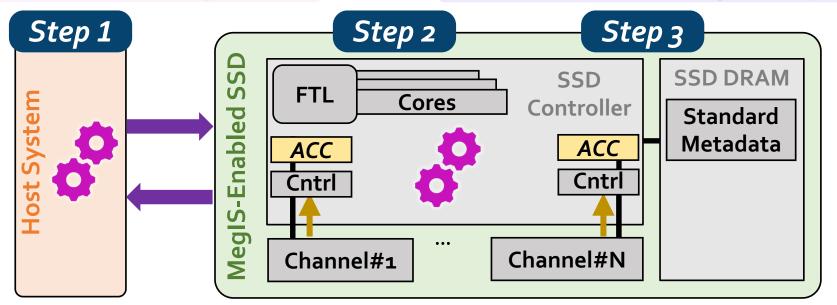

#### Lightweight in-storage accelerators

Minimize SRAM/DRAM buffer spaces needed inside the SSD

#### Task partitioning and mapping

• Each step executes in its most suitable system

#### Data/computation flow coordination

- Reduce communication overhead

- Reduce #writes to flash chips

#### Storage-aware algorithms

• Enable efficient access patterns to the SSD

#### Lightweight in-storage accelerators

Minimize SRAM/DRAM buffer spaces needed inside the SSD

#### Data mapping scheme and Flash Translation Layer (FTL)

- Specialize to the characteristics of metagenomic analysis

- Leverage the SSD's full internal bandwidth

## **Evaluation: Methodology Overview**

#### Performance, Energy, and Power Analysis

#### **Hardware Components**

- Synthesized Verilog model for the in-storage accelerators

- MQSim [Tavakkol+, FAST'18] for SSD's internal operations

- Ramulator [Kim+, CAL'15] for SSD's internal DRAM

#### **Software Components**

Measure on a real system:

- AMD® EPYC® CPU with 128 physical cores

- 1-TB DRAM

#### **Baseline Comparison Points**

- Performance-optimized software, Kraken2 [Genome Biology'19]

- Accuracy-optimized software, Metalign [Genome Biology'20]

- PIM hardware-accelerated tool (using processing-in-memory), Sieve [ISCA'21]

#### **SSD Configurations**

- SSD-C: with SATA3 interface (0.5 GB/s sequential read bandwidth)

- SSD-P: with PCle Gen4 interface (7 GB/s sequential read bandwidth)

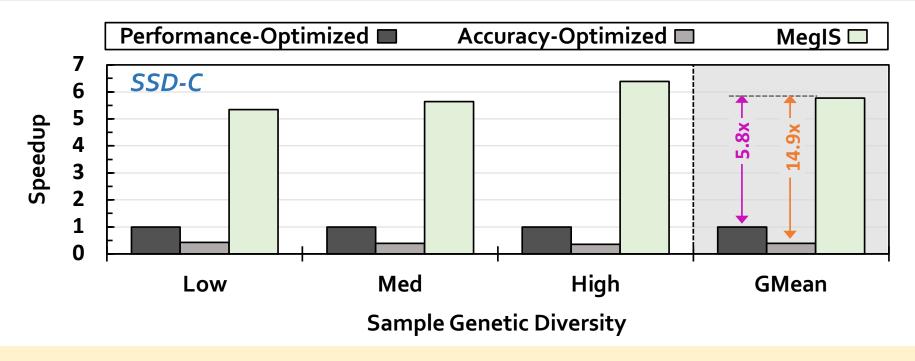

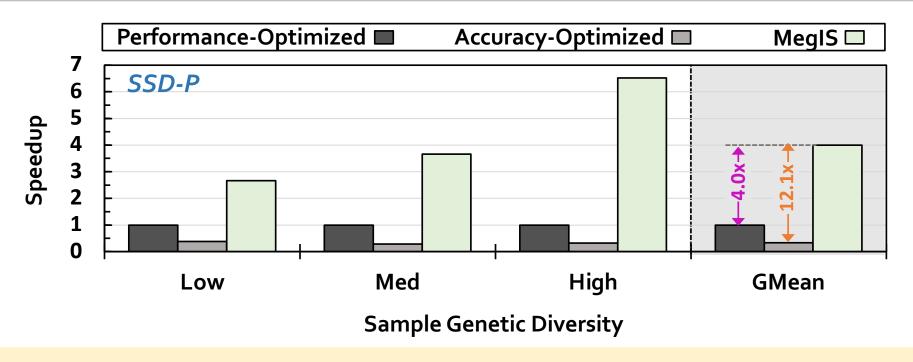

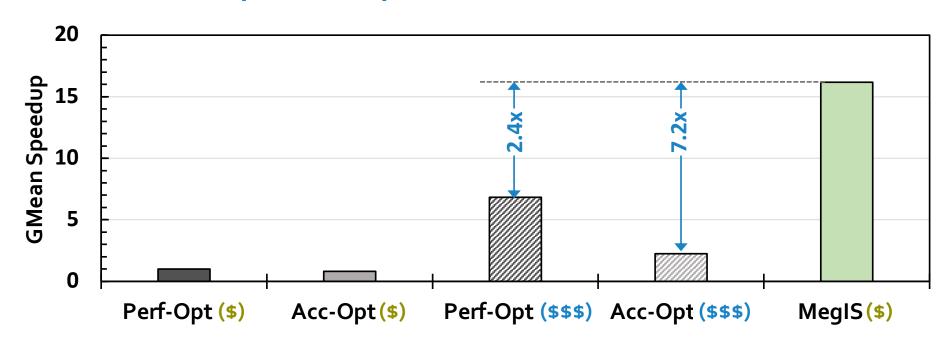

## **Evaluation: Speedup over the Software Baselines**

MegIS provides significant speedup over both

Performance-Optimized and Accuracy-Optimized baselines

### **Evaluation: Speedup over the Software Baselines**

MegIS provides significant speedup over both

Performance-Optimized and Accuracy-Optimized baselines

MegIS improves performance on both cost-optimized and performance-optimized SSDs

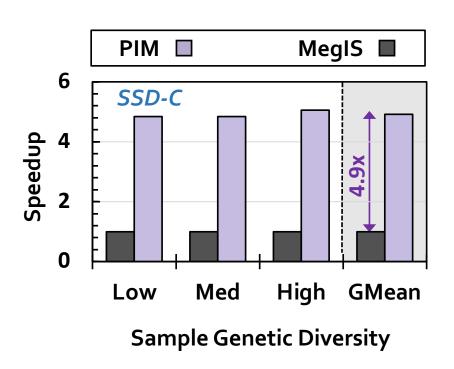

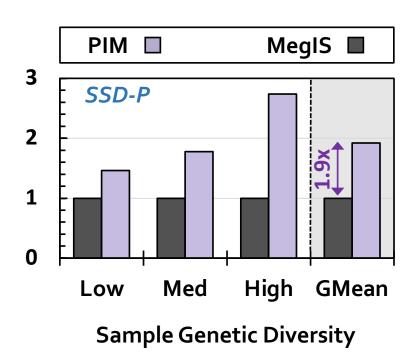

### **Evaluation: Speedup over the PIM Baseline**

MegIS provides significant speedup over the PIM baseline

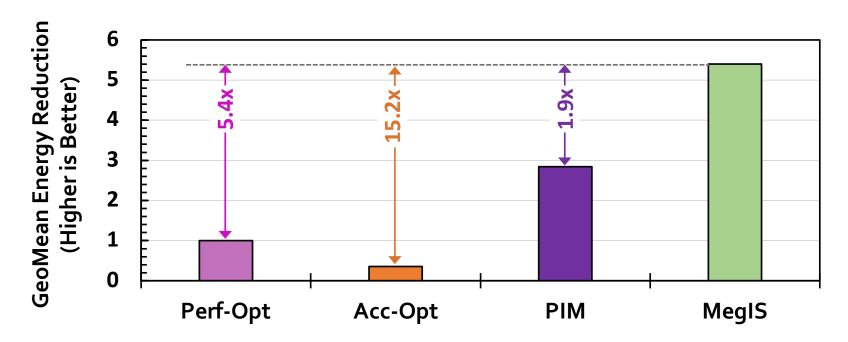

## **Evaluation: Reduction in Energy Consumption**

• On average across different input sets and SSDs

MegIS provides significant energy reduction over

the Performance-Optimized, Accuracy-Optimized, and PIM baselines

## Evaluation: Accuracy, Area, and Power

#### **Accuracy**

- Same accuracy as the accuracy-optimized baseline

- Significantly higher accuracy than the performance-optimized and PIM baselines

- $4.6 5.2 \times$  higher F1 scores

- 3 24% lower L1 norm error

#### **Area and Power**

Total for an 8-channel SSD:

- Area: 0.04 mm<sup>2</sup> (Only 1.7% of the area of three ARM Cortex R4 cores in an SSD controller)

- **Power:** 7.658 mW

## **Evaluation: System Cost-Efficiency**

- Cost-optimized system (\$): With SSD-C and 64-GB DRAM

- Performance-optimized system (\$\$\$): With SSD-P and 1-TB DRAM

MegIS outperforms the baselines even when running on a much less costly system

## **Evaluation: System Cost-Efficiency**

- Cost-optimized system (\$): With SSD-C and 64-GB DRAM

- Performance-optimized system (\$\$\$): With SSD-P and 1-TB DRAM

20

MegIS improves system cost-efficiency and makes metagenomics more accessible for wider adoption

Perf-Opt (\$) Acc-Opt (\$) Perf-Opt (\$\$\$) Acc-Opt (\$\$\$) MegIS (\$

MegIS outperforms the baselines even when running on a much less costly system

## More in the Paper

- MegIS's performance when running in-storage processing operations on the cores existing in the SSD controller

- MegIS's performance when using the same accelerators outside SSD

- Sensitivity analysis with varying

- Database sizes

- Memory capacities

- #SSDs

- #Channels

- #Samples

- MegIS's performance for abundance estimation

## More in the Paper

#### MegIS: High-Performance, Energy-Efficient, and Low-Cost Metagenomic Analysis with In-Storage Processing

Nika Mansouri Ghiasi<sup>1</sup> Mohammad Sadrosadati<sup>1</sup> Harun Mustafa<sup>1</sup> Arvid Gollwitzer<sup>1</sup> Can Firtina<sup>1</sup> Julien Eudine<sup>1</sup> Haiyu Mao<sup>1</sup> Joël Lindegger<sup>1</sup> Meryem Banu Cavlak<sup>1</sup> Mohammed Alser<sup>1</sup> Jisung Park<sup>2</sup> Onur Mutlu<sup>1</sup>

1ETH Zürich <sup>2</sup>POSTECH

- Database sizes

- Memory capacities

- #SSDs

- #Channels

- #Samples

MegIS's performance for abundance estimation

https://arxiv.org/abs/2406.19113

## **MegIS: Summary**

Metagenomic analysis suffers from significant storage I/O data movement overhead

#### MegIS

The *first* **in-storage processing** system for *end-to-end* metagenomic analysis Leverages and orchestrates **processing inside** and **outside** the storage system

#### Improves performance

2.7×-37.2× over performance-optimized software 6.9×-100.2× over accuracy-optimized software 1.5×-5.1× over hardware-accelerated PIM baseline

#### High accuracy

Same as accuracy-optimized

**4.8**× higher F1 scores

over performance-optimized/PIM

#### Reduces energy consumption

5.4× over performance-optimized software

15.2× over accuracy-optimized software

1.9× over hardware-accelerated PIM baseline

#### Low area overhead

1.7% of the three cores in an SSD controller

## MQSim: Simulating Storage [FAST 2018]

Arash Tavakkol, Juan Gomez-Luna, Mohammad Sadrosadati, Saugata Ghose, and Onur Mutlu,

"MQSim: A Framework for Enabling Realistic Studies of Modern Multi-Queue SSD Devices"

Proceedings of the <u>16th USENIX Conference on File and Storage</u> <u>Technologies</u> (**FAST**), Oakland, CA, USA, February 2018.

[Slides (pptx) (pdf)]

Source Code

## MQSim: A Framework for Enabling Realistic Studies of Modern Multi-Queue SSD Devices

Arash Tavakkol<sup>†</sup>, Juan Gómez-Luna<sup>†</sup>, Mohammad Sadrosadati<sup>†</sup>, Saugata Ghose<sup>‡</sup>, Onur Mutlu<sup>†‡</sup>

†ETH Zürich <sup>‡</sup>Carnegie Mellon University

https://github.com/CMU-SAFARI/MQSim

## Tools to Decide What to Execute Where

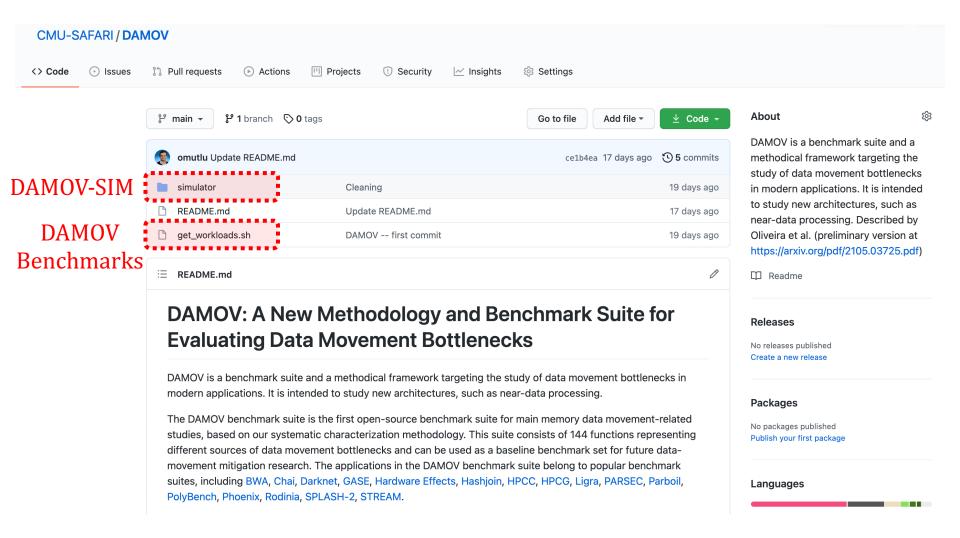

## DAMOV Analysis Methodology & Workloads

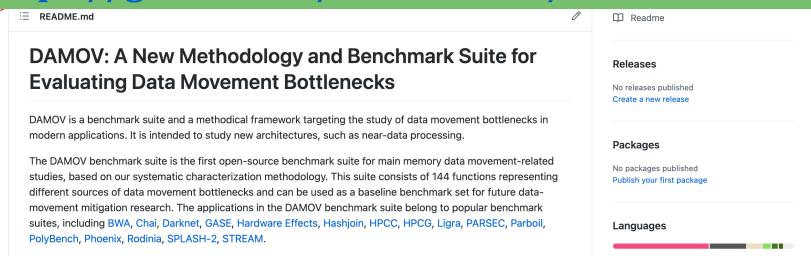

## DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

GERALDO F. OLIVEIRA, ETH Zürich, Switzerland

JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland

LOIS OROSA, ETH Zürich, Switzerland

SAUGATA GHOSE, University of Illinois at Urbana-Champaign, USA

NANDITA VIJAYKUMAR, University of Toronto, Canada

IVAN FERNANDEZ, University of Malaga, Spain & ETH Zürich, Switzerland

MOHAMMAD SADROSADATI, Institute for Research in Fundamental Sciences (IPM), Iran & ETH

Zürich, Switzerland

ONUR MUTLU, ETH Zürich, Switzerland

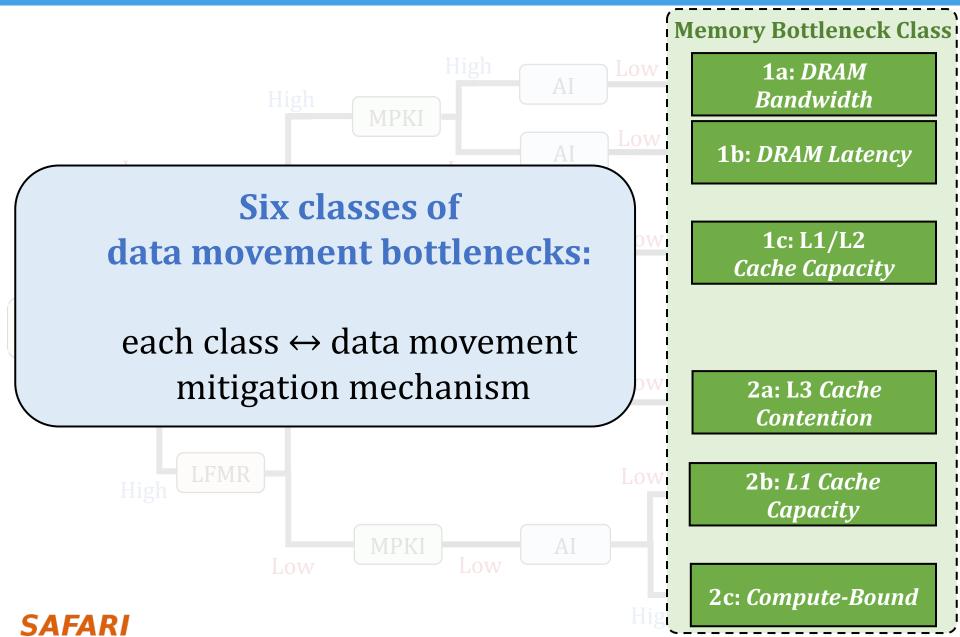

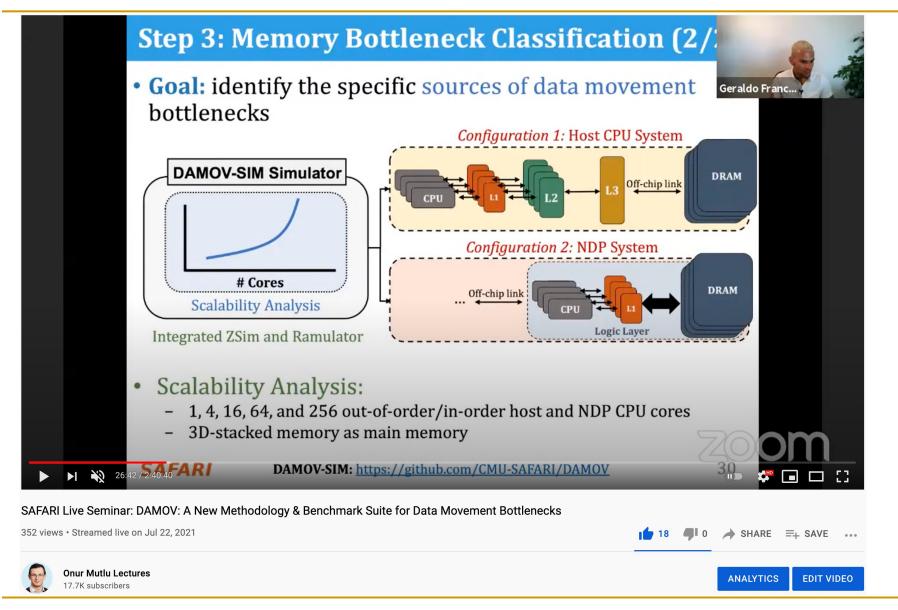

Data movement between the CPU and main memory is a first-order obstacle against improving performance, scalability, and energy efficiency in modern systems. Computer systems employ a range of techniques to reduce overheads tied to data movement, spanning from traditional mechanisms (e.g., deep multi-level cache hierarchies, aggressive hardware prefetchers) to emerging techniques such as Near-Data Processing (NDP), where some computation is moved close to memory. Prior NDP works investigate the root causes of data movement bottlenecks using different profiling methodologies and tools. However, there is still a lack of understanding about the key metrics that can identify different data movement bottlenecks and their relation to traditional and emerging data movement mitigation mechanisms. Our goal is to methodically identify potential sources of data movement over a broad set of applications and to comprehensively compare traditional compute-centric data movement mitigation techniques (e.g., caching and prefetching) to more memory-centric techniques (e.g., NDP), thereby developing a rigorous understanding of the best techniques to mitigate each source of data movement.

With this goal in mind, we perform the first large-scale characterization of a wide variety of applications, across a wide range of application domains, to identify fundamental program properties that lead to data movement to/from main memory. We develop the first systematic methodology to classify applications based on the sources contributing to data movement bottlenecks. From our large-scale characterization of 77K functions across 345 applications, we select 144 functions to form the first open-source benchmark suite (DAMOV) for main memory data movement studies. We select a diverse range of functions that (1) represent different types of data movement bottlenecks, and (2) come from a wide range of application domains. Using NDP as a case study, we identify new insights about the different data movement bottlenecks and use these insights to determine the most suitable data movement mitigation mechanism for a particular application. We open-source DAMOV and the complete source code for our new characterization methodology at https://github.com/CMU-SAFARI/DAMOV.

SAFARI

https://arxiv.org/pdf/2105.03725.pdf

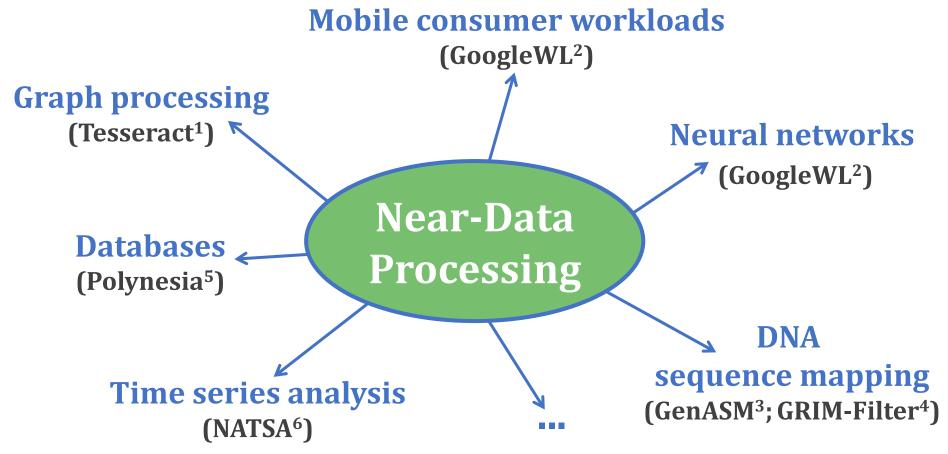

## When to Employ Near-Data Processing?

- [1] Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing," ISCA, 2015

- [2] Boroumand+, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks," ASPLOS, 2018

- [3] Cali+, "GenASM: A High-Performance, Low-Power Approximate String Matching Acceleration Framework for Genome Sequence Analysis," MICRO, 2020

- [4] Kim+, "GRIM-Filter: Fast Seed Location Filtering in DNA Read Mapping Using Processing-in-Memory Technologies," BMC Genomics, 2018

- [5] Boroumand+, "Polynesia: Enabling Effective Hybrid Transactional/Analytical Databases with Specialized Hardware/Software Co-Design," arXiv:2103.00798 [cs.AR], 2021

- [6] Fernandez+, "NATSA: A Near-Data Processing Accelerator for Time Series Analysis," ICCD, 2020

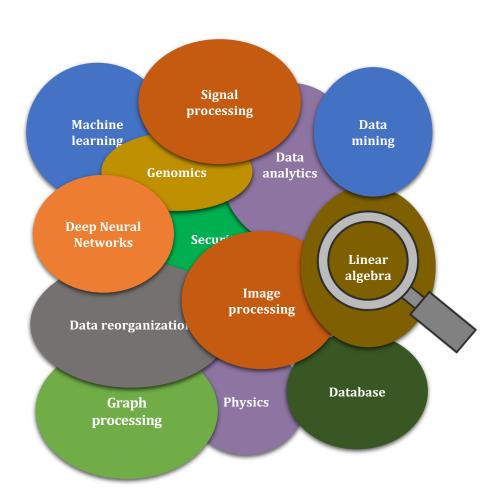

## **Step 1: Application Profiling**

- We analyze 345 applications from distinct domains:

- Graph Processing

- Deep Neural Networks

- Physics

- High-Performance Computing

- Genomics

- Machine Learning

- Databases

- Data Reorganization

- Image Processing

- Map-Reduce

- Benchmarking

- Linear Algebra

## Step 3: Memory Bottleneck Analysis

## DAMOV is Open Source

We open-source our benchmark suite and our toolchain

## DAMOV is Open Source

Benchmark suite and toolchain are open sourced

#### **Get DAMOV at:**

#### https://github.com/CMU-SAFARI/DAMOV

#### More on DAMOV Analysis Methodology & Workloads

#### More on DAMOV Methods & Benchmarks

Geraldo F. Oliveira, Juan Gomez-Luna, Lois Orosa, Saugata Ghose, Nandita Vijaykumar, Ivan fernandez, Mohammad Sadrosadati, and Onur Mutlu,

"DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks"

**IEEE Access**, 8 September 2021. Preprint in <u>arXiv</u>, 8 May 2021.

[arXiv preprint]

[IEEE Access version]

[DAMOV Suite and Simulator Source Code]

[SAFARI Live Seminar Video (2 hrs 40 mins)]

ONUR MUTLU, ETH Zürich, Switzerland

[Short Talk Video (21 minutes)]

## DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

GERALDO F. OLIVEIRA, ETH Zürich, Switzerland

JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland

LOIS OROSA, ETH Zürich, Switzerland

SAUGATA GHOSE, University of Illinois at Urbana-Champaign, USA

NANDITA VIJAYKUMAR, University of Toronto, Canada

IVAN FERNANDEZ, University of Malaga, Spain & ETH Zürich, Switzerland

MOHAMMAD SADROSADATI, ETH Zürich, Switzerland

#### Ramulator 2.0 for PIM Systems

Haocong Luo, Yahya Can Tugrul, F. Nisa Bostanci, Ataberk Olgun, A. Giray Yaglikci, and Onur Mutlu,

"Ramulator 2.0: A Modern, Modular, and Extensible DRAM Simulator" Preprint on arxiv, August 2023.

[arXiv version]

[Ramulator 2.0 Source Code]

## Ramulator 2.0: A Modern, Modular, and Extensible DRAM Simulator

Haocong Luo, Yahya Can Tuğrul, F. Nisa Bostancı, Ataberk Olgun, A. Giray Yağlıkçı, and Onur Mutlu

https://arxiv.org/pdf/2308.11030.pdf

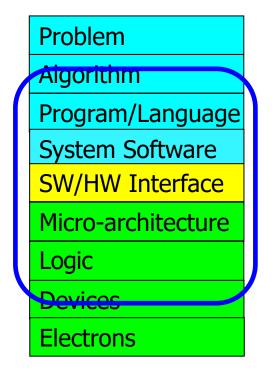

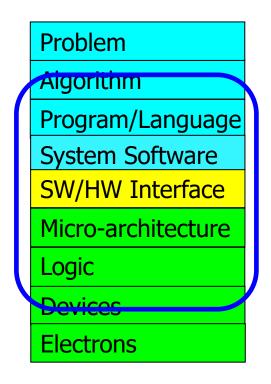

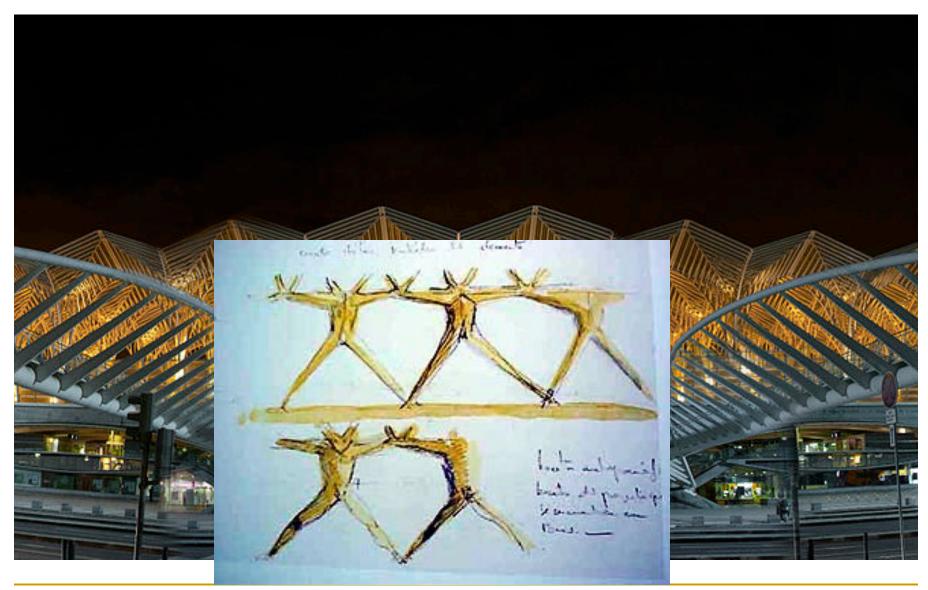

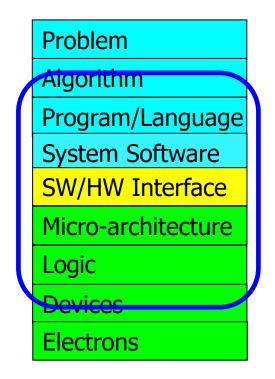

#### We Need to Revisit the Entire Stack

With a memory-centric mindset

We can get there step by step

## PIM Review and Open Problems

## A Modern Primer on Processing in Memory

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b,c</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>d</sup>

SAFARI Research Group

<sup>a</sup>ETH Zürich

<sup>b</sup>Carnegie Mellon University

<sup>c</sup>University of Illinois at Urbana-Champaign

<sup>d</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun,

"A Modern Primer on Processing in Memory"

Invited Book Chapter in Emerging Computing: From Devices to Systems

Looking Beyond Moore and Von Neumann, Springer, to be published in 2021.

## PIM Review and Open Problems (II)

#### A Workload and Programming Ease Driven Perspective of Processing-in-Memory

Saugata Ghose<sup>†</sup> Amirali Boroumand<sup>†</sup> Jeremie S. Kim<sup>†</sup>§ Juan Gómez-Luna<sup>§</sup> Onur Mutlu<sup>§†</sup>

†Carnegie Mellon University §ETH Zürich

Saugata Ghose, Amirali Boroumand, Jeremie S. Kim, Juan Gomez-Luna, and Onur Mutlu, "Processing-in-Memory: A Workload-Driven Perspective"

Invited Article in IBM Journal of Research & Development, Special Issue on Hardware for Artificial Intelligence, to appear in November 2019.

[Preliminary arXiv version]

# Processing in Memory: Adoption Challenges

- 1. Processing using Memory

- 2. Processing **near** Memory

## Eliminating the Adoption Barriers

## How to Enable Adoption of Processing in Memory

## Potential Barriers to Adoption of PIM

- 1. **Applications** & **software** for PIM

- 2. Ease of **programming** (interfaces and compiler/HW support)

- 3. **System** and **security** support: coherence, synchronization, virtual memory, isolation, communication interfaces, ...

- 4. **Runtime** and **compilation** systems for adaptive scheduling, data mapping, access/sharing control, ...

- 5. **Infrastructures** to assess benefits and feasibility

All can be solved with change of mindset

#### We Need to Revisit the Entire Stack

With a memory-centric mindset

We can get there step by step

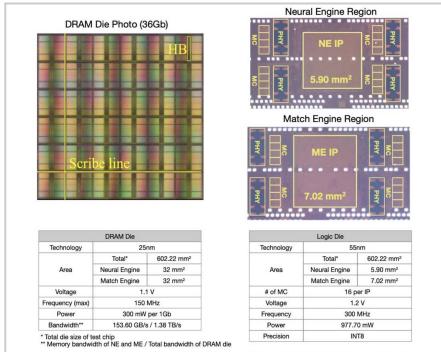

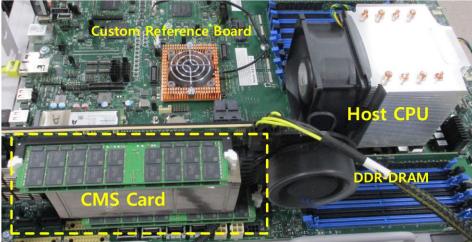

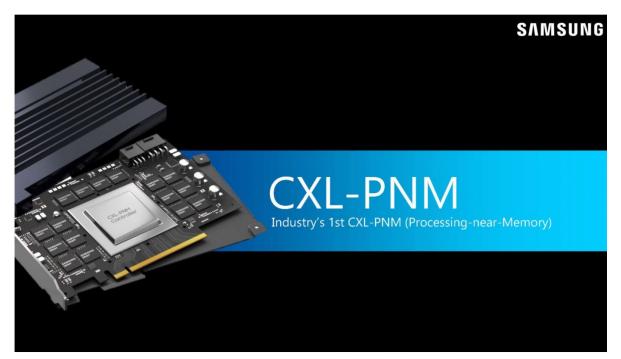

## Processing-in-Memory Landscape Today

[Samsung 2021]

[UPMEM 2019]

## Adoption: How to Keep It Simple?

Junwhan Ahn, Sungjoo Yoo, Onur Mutlu, and Kiyoung Choi,

"PIM-Enabled Instructions: A Low-Overhead,

Locality-Aware Processing-in-Memory Architecture"

Proceedings of the <u>42nd International Symposium on</u>

Computer Architecture (ISCA), Portland, OR, June 2015.

[Slides (pdf)] [Lightning Session Slides (pdf)]

#### PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture

Junwhan Ahn Sungjoo Yoo Onur Mutlu<sup>†</sup> Kiyoung Choi junwhan@snu.ac.kr, sungjoo.yoo@gmail.com, onur@cmu.edu, kchoi@snu.ac.kr

Seoul National University †Carnegie Mellon University

SAFARI

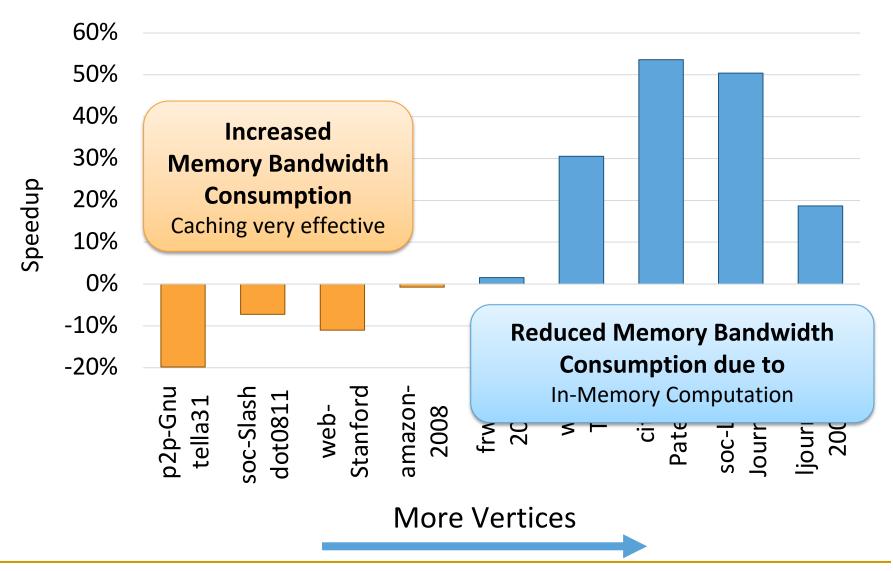

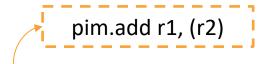

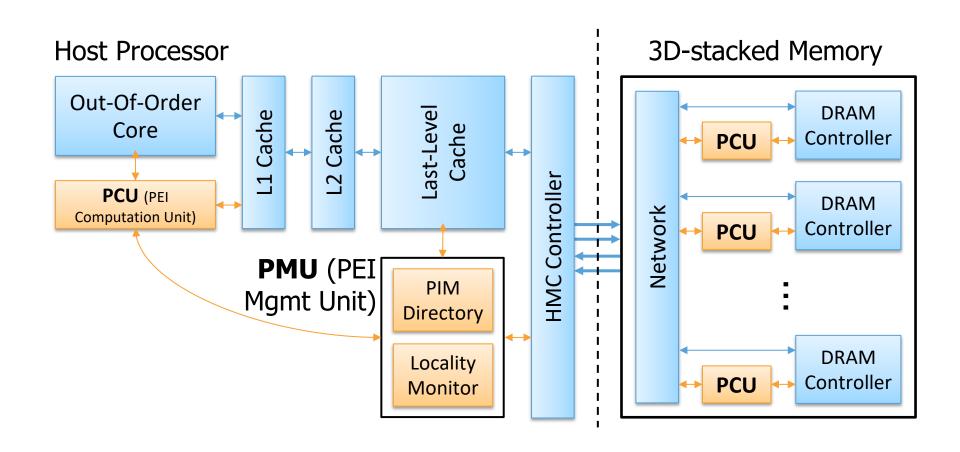

## PEI: PIM-Enabled Instructions (Ideas)

- Goal: Develop mechanisms to get the most out of near-data processing with minimal cost, minimal changes to the system, no changes to the programming model

- Key Idea 1: Expose each PIM operation as a cache-coherent, virtually-addressed host processor instruction (called PEI) that operates on only a single cache block

- $\circ$  e.g., \_\_pim\_add(&w.next\_rank, value)  $\rightarrow$  pim.add r1, (r2)

- No changes sequential execution/programming model

- No changes to virtual memory

- Minimal changes to cache coherence

- No need for data mapping: Each PEI restricted to a single memory module

- Key Idea 2: Dynamically decide where to execute a PEI (i.e., the host processor or PIM accelerator) based on simple locality characteristics and simple hardware predictors

- Execute each operation at the location that provides the best performance

#### Simple PIM Operations as ISA Extensions (II)

```

for (v: graph.vertices) {

value = weight * v.rank;

for (w: v.successors) {

w.next rank += value;

Main Memory

Host Processor

w.next rank

w.next rank

64 bytes in

64 bytes out

```

#### **Conventional Architecture**

#### Simple PIM Operations as ISA Extensions (III)

```

for (v: graph.vertices) {

value = weight * v.rank;

pim.add r1, (r2)

for (w: v.successors) {

pim_add(&w.next_rank, value);

Main Memory

Host Processor

w.next rank

value

8 bytes in

0 bytes out

```

#### Always Executing in Memory? Not A Good Idea

### PEI: PIM-Enabled Instructions (Example)

```

for (v: graph.vertices) {

value = weight * v.rank;

for (w: v.successors) {

__pim_add(&w.next_rank, value);

}

}

pfence();

```

**Table 1: Summary of Supported PIM Operations**

| Operation                | R | W | Input    | Output   | Applications |

|--------------------------|---|---|----------|----------|--------------|

| 8-byte integer increment | О | O | 0 bytes  | 0 bytes  | AT           |

| 8-byte integer min       | O | O | 8 bytes  | 0 bytes  | BFS, SP, WCC |

| Floating-point add       | O | O | 8 bytes  | 0 bytes  | PR           |

| Hash table probing       | O | X | 8 bytes  | 9 bytes  | HJ           |

| Histogram bin index      | O | X | 1 byte   | 16 bytes | HG, RP       |

| Euclidean distance       | O | X | 64 bytes | 4 bytes  | SC           |

| Dot product              | O | X | 32 bytes | 8 bytes  | SVM          |

- Executed either in memory or in the processor: dynamic decision

- Low-cost locality monitoring for a single instruction

- Cache-coherent, virtually-addressed, single cache block only

- Atomic between different PEIs

- Not atomic with normal instructions (use pfence for ordering)

#### PIM-Enabled Instructions

- Key to practicality: single-cache-block restriction

- Each PEI can access at most one last-level cache block

- Similar restrictions exist in atomic instructions

- Benefits

- Localization: each PEI is bounded to one memory module

- Interoperability: easier support for cache coherence and virtual memory

- Simplified locality monitoring: data locality of PEIs can be identified simply by the cache control logic

## Example (Abstract) PEI uArchitecture

Example PEI uArchitecture

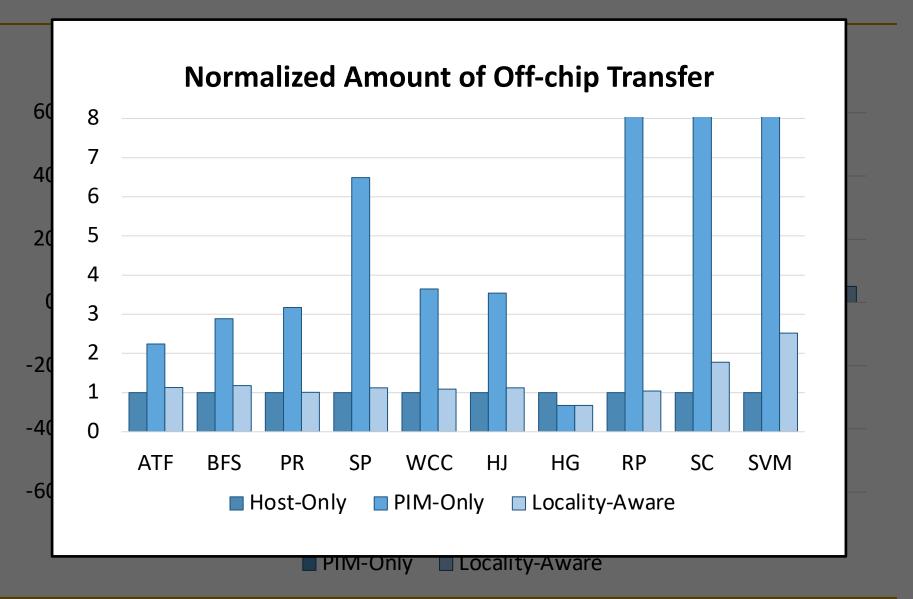

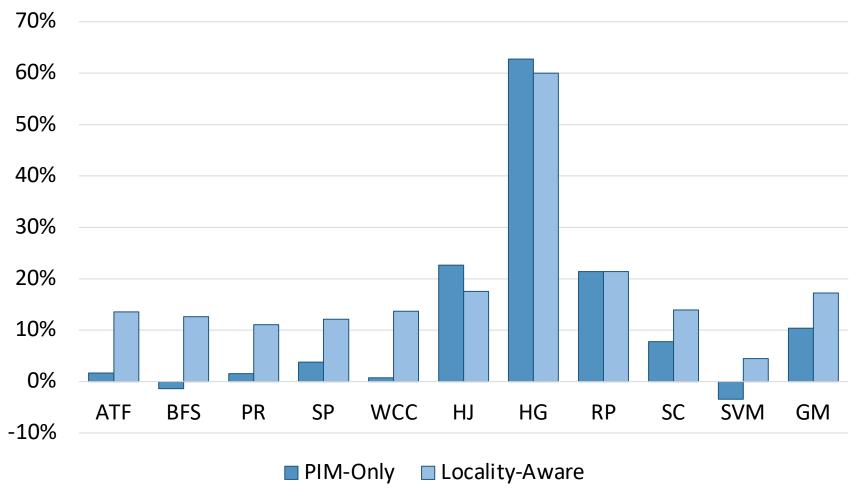

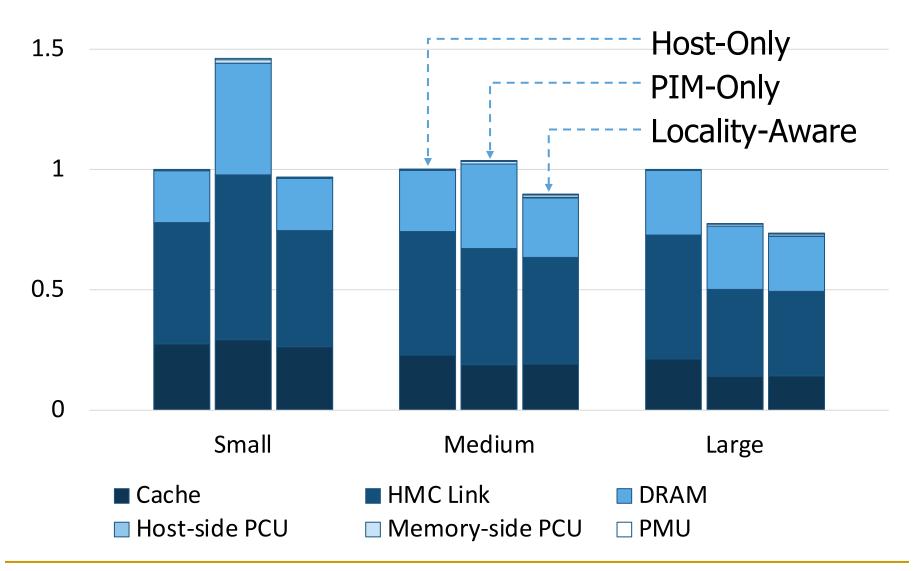

#### PEI: Initial Evaluation Results

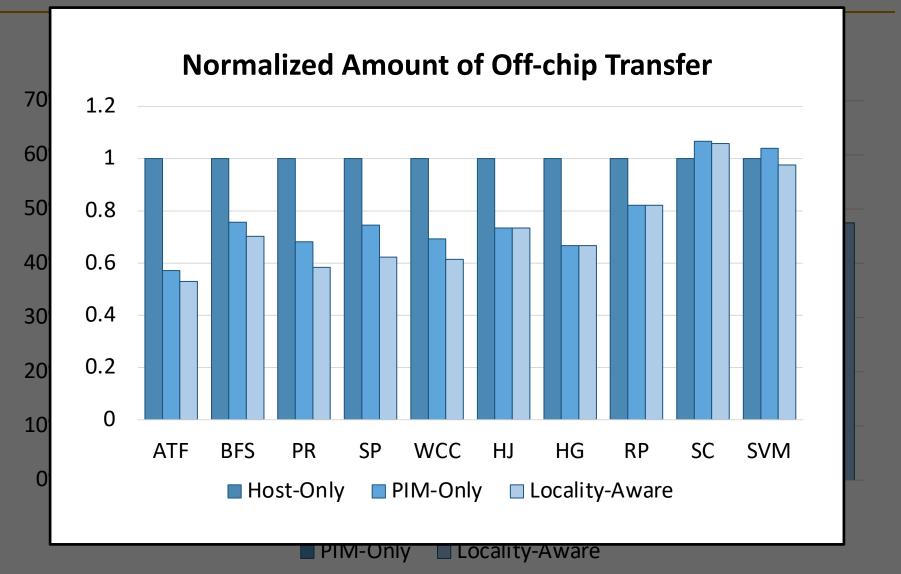

- Initial evaluations with 10 emerging data-intensive workloads

- Large-scale graph processing

- In-memory data analytics

- Machine learning and data mining

- Three input sets (small, medium, large)

for each workload to analyze the impact of data locality

**Table 2: Baseline Simulation Configuration**

| Component                          | Configuration                                       |

|------------------------------------|-----------------------------------------------------|

| Core                               | 16 out-of-order cores, 4 GHz, 4-issue               |

| L1 I/D-Cache                       | Private, 32 KB, 4/8-way, 64 B blocks, 16 MSHRs      |

| L2 Cache                           | Private, 256 KB, 8-way, 64 B blocks, 16 MSHRs       |

| L3 Cache                           | Shared, 16 MB, 16-way, 64 B blocks, 64 MSHRs        |

| On-Chip Network                    | Crossbar, 2 GHz, 144-bit links                      |

| Main Memory                        | 32 GB, 8 HMCs, daisy-chain (80 GB/s full-duplex)    |

| HMC                                | 4 GB, 16 vaults, 256 DRAM banks [20]                |

| - DRAM                             | FR-FCFS, $tCL = tRCD = tRP = 13.75 \text{ ns}$ [27] |

| <ul> <li>Vertical Links</li> </ul> | 64 TSVs per vault with 2 Gb/s signaling rate [23]   |

Pin-based cycle-level x86-64 simulation

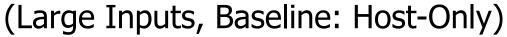

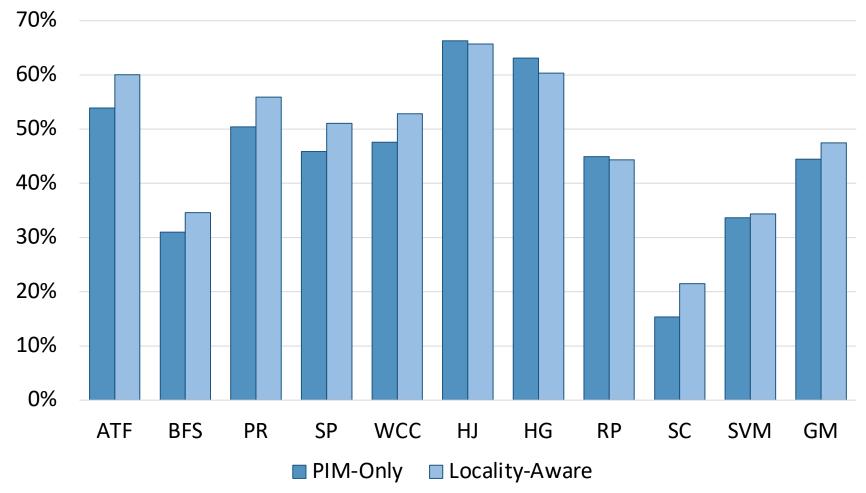

#### Performance Improvement and Energy Reduction:

- 47% average speedup with large input data sets

- 32% speedup with small input data sets

- 25% avg. energy reduction in a single node with large input data sets

## Evaluated Data-Intensive Applications

- Ten emerging data-intensive workloads

- Large-scale graph processing

- Average teenage follower, BFS, PageRank, single-source shortest path, weakly connected components

- In-memory data analytics

- Hash join, histogram, radix partitioning

- Machine learning and data mining

- Streamcluster, SVM-RFE

- Three input sets (small, medium, large) for each workload to show the impact of data locality

## PEI Performance Delta: Large Data Sets

## PEI Performance: Large Data Sets

#### PEI Performance Delta: Small Data Sets

#### PEI Performance: Small Data Sets

#### PEI Performance Delta: Medium Data Sets

## PEI Energy Consumption

## PEI: Advantages & Disadvantages

#### Advantages

- + Simple and low-cost approach to PIM

- + No changes to programming model, virtual memory

- + Dynamically decides where to execute an instruction

#### Disadvantages

- Does not take full advantage of PIM potential

- Single cache block restriction is limiting

## Adoption: How to Keep It Simple?

Junwhan Ahn, Sungjoo Yoo, Onur Mutlu, and Kiyoung Choi,

"PIM-Enabled Instructions: A Low-Overhead,

Locality-Aware Processing-in-Memory Architecture"

Proceedings of the <u>42nd International Symposium on</u>

Computer Architecture (ISCA), Portland, OR, June 2015.

[Slides (pdf)] [Lightning Session Slides (pdf)]

#### PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture

Junwhan Ahn Sungjoo Yoo Onur Mutlu<sup>†</sup> Kiyoung Choi junwhan@snu.ac.kr, sungjoo.yoo@gmail.com, onur@cmu.edu, kchoi@snu.ac.kr

Seoul National University <sup>†</sup>Carnegie Mellon University

SAFARI

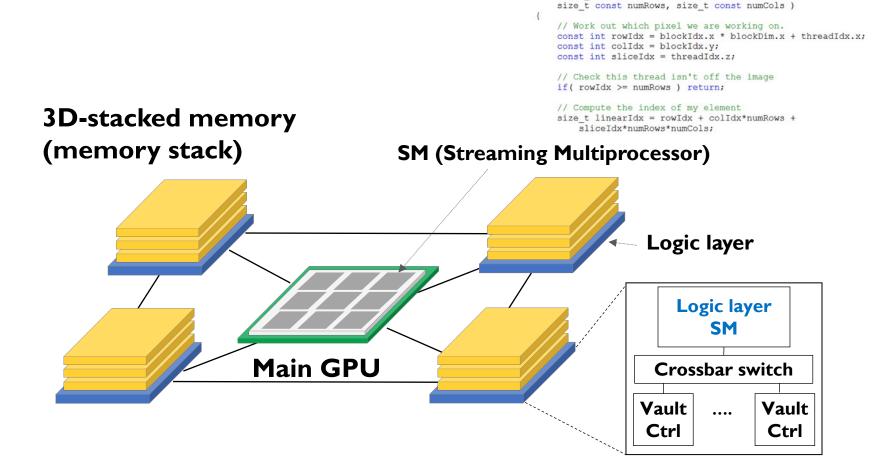

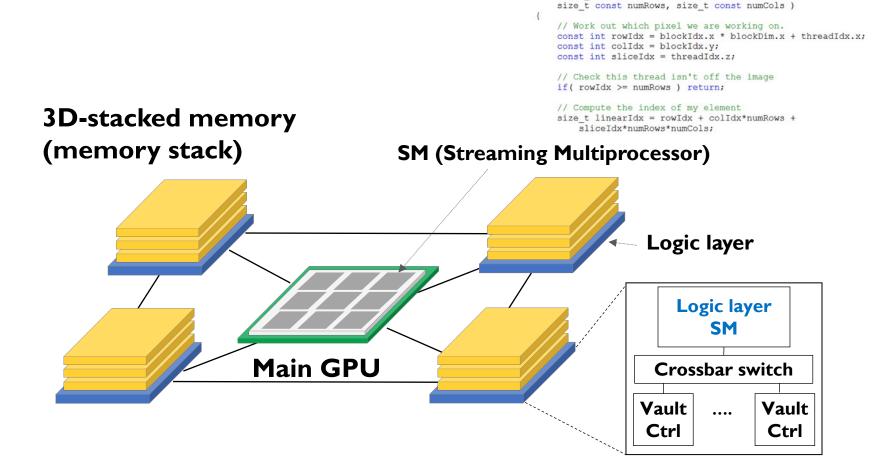

### Adoption: How to Ease **Programmability?** (I)

Kevin Hsieh, Eiman Ebrahimi, Gwangsun Kim, Niladrish Chatterjee, Mike O'Connor, Nandita Vijaykumar, Onur Mutlu, and Stephen W. Keckler, "Transparent Offloading and Mapping (TOM): Enabling Programmer-Transparent Near-Data Processing in GPU Systems"

Proceedings of the <u>43rd International Symposium on Computer</u> <u>Architecture</u> (**ISCA**), Seoul, South Korea, June 2016. [<u>Slides (pptx) (pdf)</u>]

[Lightning Session Slides (pptx) (pdf)]

#### Transparent Offloading and Mapping (TOM): Enabling Programmer-Transparent Near-Data Processing in GPU Systems

Kevin Hsieh<sup>‡</sup> Eiman Ebrahimi<sup>†</sup> Gwangsun Kim<sup>\*</sup> Niladrish Chatterjee<sup>†</sup> Mike O'Connor<sup>†</sup> Nandita Vijaykumar<sup>‡</sup> Onur Mutlu<sup>§‡</sup> Stephen W. Keckler<sup>†</sup> <sup>‡</sup>Carnegie Mellon University <sup>†</sup>NVIDIA \*KAIST <sup>§</sup>ETH Zürich

#### Truly Distributed GPU Processing with PIM

void applyScaleFactorsKernel( uint8\_T \* const out, uint8\_T const \* const in, const double \*factor,

### Adoption: How to Ease Programmability? (II)

Geraldo F. Oliveira, Alain Kohli, David Novo,

Juan Gómez-Luna, Onur Mutlu,

"DaPPA: A Data-Parallel Framework for Processing-in-Memory Architectures,"

in PACT SRC Student Competition, Vienna, Austria, October 2023.

#### DaPPA: A Data-Parallel Framework for Processing-in-Memory Architectures

Geraldo F. Oliveira\* Alain Kohli\* David Novo<sup>‡</sup> Juan Gómez-Luna\* Onur Mutlu\*

\*ETH Zürich <sup>‡</sup>LIRMM, Univ. Montpellier, CNRS

#### Adoption: How to Ease Programmability? (III)

Jinfan Chen, Juan Gómez-Luna, Izzat El Hajj, YuXin Guo, and Onur Mutlu,

"SimplePIM: A Software Framework for Productive and Efficient Processing in Memory"

Proceedings of the <u>32nd International Conference on</u>

<u>Parallel Architectures and Compilation Techniques</u> (**PACT**),

Vienna, Austria, October 2023.

#### SimplePIM: A Software Framework for Productive and Efficient Processing-in-Memory

Jinfan Chen $^1$  Juan Gómez-Luna $^1$  Izzat El Hajj $^2$  Yuxin Guo $^1$  Onur Mutlu $^1$ ETH Zürich  $^2$ American University of Beirut

#### Adoption: How to Ease **Programmability?** (IV)

Geraldo F. Oliveira, Juan Gomez-Luna, Lois Orosa, Saugata Ghose, Nandita Vijaykumar, Ivan fernandez, Mohammad Sadrosadati, and Onur Mutlu, "DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks"

**IEEE Access**, 8 September 2021. Preprint in **arXiv**, 8 May 2021.

[arXiv preprint]

[IEEE Access version]

[DAMOV Suite and Simulator Source Code]

[SAFARI Live Seminar Video (2 hrs 40 mins)]

[Short Talk Video (21 minutes)]

## DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

GERALDO F. OLIVEIRA, ETH Zürich, Switzerland

JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland

LOIS OROSA, ETH Zürich, Switzerland

SAUGATA GHOSE, University of Illinois at Urbana-Champaign, USA

NANDITA VIJAYKUMAR, University of Toronto, Canada

IVAN FERNANDEZ, University of Malaga, Spain & ETH Zürich, Switzerland

MOHAMMAD SADROSADATI, ETH Zürich, Switzerland

ONUR MUTLU, ETH Zürich, Switzerland

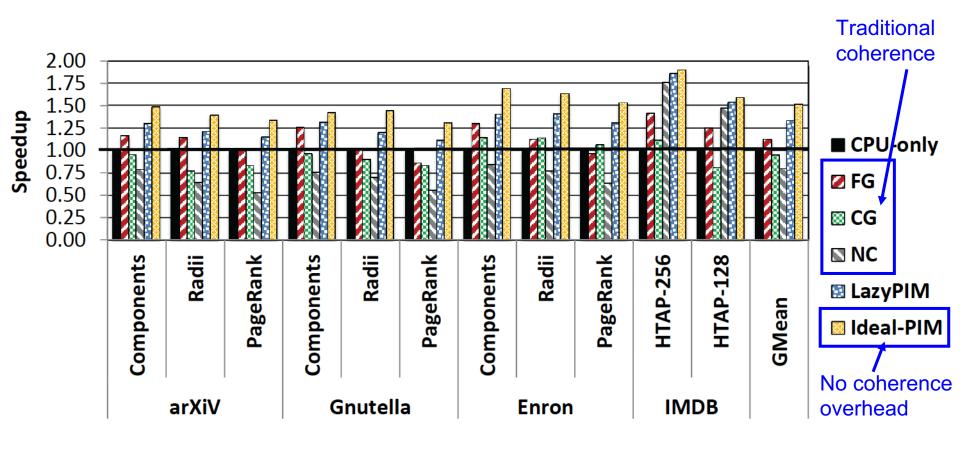

## Adoption: How to Maintain Coherence? (I)

Amirali Boroumand, Saugata Ghose, Minesh Patel, Hasan Hassan, Brandon Lucia, Kevin Hsieh, Krishna T. Malladi, Hongzhong Zheng, and Onur Mutlu, "LazyPIM: An Efficient Cache Coherence Mechanism for Processing-in-Memory"

IEEE Computer Architecture Letters (CAL), June 2016.

#### LazyPIM: An Efficient Cache Coherence Mechanism for Processing-in-Memory

Amirali Boroumand<sup>†</sup>, Saugata Ghose<sup>†</sup>, Minesh Patel<sup>†</sup>, Hasan Hassan<sup>†</sup>, Brandon Lucia<sup>†</sup>, Kevin Hsieh<sup>†</sup>, Krishna T. Malladi<sup>\*</sup>, Hongzhong Zheng<sup>\*</sup>, and Onur Mutlu<sup>‡†</sup>

† Carnegie Mellon University \* Samsung Semiconductor, Inc. § TOBB ETÜ <sup>‡</sup> ETH Zürich

#### Challenge: Coherence for Hybrid CPU-PIM Apps

### Adoption: How to Maintain Coherence? (II)

Amirali Boroumand, Saugata Ghose, Minesh Patel, Hasan Hassan, Brandon Lucia, Kevin Hsieh, Krishna T. Malladi, Hongzhong Zheng, and Onur Mutlu, "CoNDA: Efficient Cache Coherence Support for Near-**Data Accelerators**"

Proceedings of the <u>46th International Symposium on Computer</u> Architecture (ISCA), Phoenix, AZ, USA, June 2019.

#### **CoNDA: Efficient Cache Coherence Support** for Near-Data Accelerators

Amirali Boroumand<sup>†</sup> Saugata Ghose<sup>†</sup> Minesh Patel\* Hasan Hassan\* Brandon Lucia<sup>†</sup> Rachata Ausavarungnirun<sup>†‡</sup> Kevin Hsieh<sup>†</sup> Nastaran Hajinazar<sup>⋄†</sup> Krishna T. Malladi<sup>§</sup> Hongzhong Zheng<sup>§</sup> Onur Mutlu<sup>⋆†</sup>

> <sup>†</sup>Carnegie Mellon University \*ETH Zürich \*Simon Fraser University §Samsung Semiconductor, Inc.

‡KMUTNB

### Adoption: How to Support Synchronization?

Christina Giannoula, Nandita Vijaykumar, Nikela Papadopoulou, Vasileios Karakostas, Ivan Fernandez, Juan Gómez-Luna, Lois Orosa, Nectarios Koziris, Georgios Goumas, Onur Mutlu, "SynCron: Efficient Synchronization Support for Near-Data-Processing Architectures"

Proceedings of the <u>27th International Symposium on High-Performance Computer</u> <u>Architecture</u> (**HPCA**), Virtual, February-March 2021.

[Slides (pptx) (pdf)]

[Short Talk Slides (pptx) (pdf)]

[Talk Video (21 minutes)]

[Short Talk Video (7 minutes)]

### SynCron: Efficient Synchronization Support for Near-Data-Processing Architectures

```

Christina Giannoula<sup>†‡</sup> Nandita Vijaykumar<sup>*‡</sup> Nikela Papadopoulou<sup>†</sup> Vasileios Karakostas<sup>†</sup> Ivan Fernandez<sup>§‡</sup>

Juan Gómez-Luna<sup>‡</sup> Lois Orosa<sup>‡</sup> Nectarios Koziris<sup>†</sup> Georgios Goumas<sup>†</sup> Onur Mutlu<sup>‡</sup>

<sup>†</sup>National Technical University of Athens <sup>‡</sup>ETH Zürich <sup>*</sup>University of Toronto <sup>§</sup>University of Malaga

```

### Adoption: How to Support Virtual Memory?

Kevin Hsieh, Samira Khan, Nandita Vijaykumar, Kevin K. Chang, Amirali Boroumand, Saugata Ghose, and Onur Mutlu, "Accelerating Pointer Chasing in 3D-Stacked Memory: Challenges, Mechanisms, Evaluation" Proceedings of the 34th IEEE International Conference on Computer Design (ICCD), Phoenix, AZ, USA, October 2016.

### Accelerating Pointer Chasing in 3D-Stacked Memory: Challenges, Mechanisms, Evaluation

Kevin Hsieh<sup>†</sup> Samira Khan<sup>‡</sup> Nandita Vijaykumar<sup>†</sup> Kevin K. Chang<sup>†</sup> Amirali Boroumand<sup>†</sup> Saugata Ghose<sup>†</sup> Onur Mutlu<sup>§†</sup> <sup>†</sup> Carnegie Mellon University <sup>‡</sup> University of Virginia <sup>§</sup> ETH Zürich

### Adoption: Evaluation Infrastructures

Haocong Luo, Yahya Can Tugrul, F. Nisa Bostanci, Ataberk Olgun, A. Giray Yaglikci, and Onur Mutlu,

"Ramulator 2.0: A Modern, Modular, and Extensible DRAM Simulator" Preprint on arxiv, August 2023.

[arXiv version]

[Ramulator 2.0 Source Code]

### Ramulator 2.0: A Modern, Modular, and Extensible DRAM Simulator

Haocong Luo, Yahya Can Tuğrul, F. Nisa Bostancı, Ataberk Olgun, A. Giray Yağlıkçı, and Onur Mutlu

https://arxiv.org/pdf/2308.11030.pdf

# Methodologies, Workloads, and Tools for Processing-in-Memory: Enabling the Adoption of Data-Centric Architectures

#### **Geraldo F. Oliveira and Onur Mutlu**

geraldofojunior@gmail.com

https://geraldofojunior.github.io/

### Processing-in-Memory: Challenges

#### To fully support PIM systems, we need to develop:

- 1 Workload characterization methodologies and benchmark suites targeting PIM architectures

- 2 Frameworks that can facilitate the implementation of complex operations and algorithms using PIM primitives

- 3 Compiler support and compiler optimizations targeting PIM architectures

- Operating system support for PIM-aware virtual memory, memory management, data allocation and mapping

- 5 End-to-End System-on-Chip Design Beyond DRAM

The <u>lack of tools</u> and <u>system support</u> for PIM architectures limit the <u>adoption</u> of PIM systems

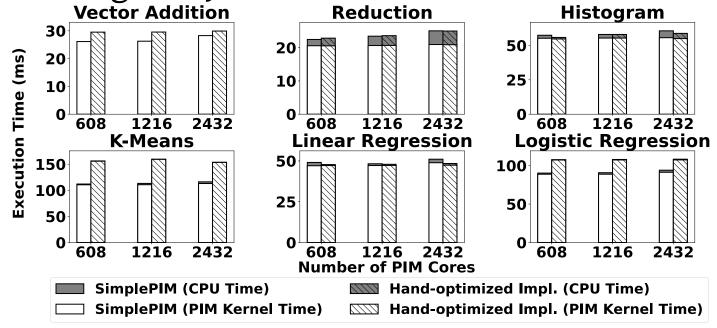

### An Example: SimplePIM Framework

Jinfan Chen, Juan Gómez-Luna, Izzat El Hajj, YuXin Guo, and Onur Mutlu,

"SimplePIM: A Software Framework for Productive and Efficient Processing in Memory"

Proceedings of the <u>32nd International Conference on</u>

<u>Parallel Architectures and Compilation Techniques</u> (**PACT**),

Vienna, Austria, October 2023.

#### SimplePIM: A Software Framework for Productive and Efficient Processing-in-Memory

Jinfan Chen $^1$  Juan Gómez-Luna $^1$  Izzat El Hajj $^2$  Yuxin Guo $^1$  Onur Mutlu $^1$ ETH Zürich  $^2$ American University of Beirut

### **Executive Summary**

- Real PIM hardware is now available, e.g., UPMEM PIM

- However, programming real PIM hardware is challenging, e.g., need to:

- Distribute data across PIM memory banks,

- Manage data transfers between host cores and PIM cores, between PIM cores, and between DRAM bank and PIM scratchpad

- Launch PIM kernels on the PIM cores, etc.

- Synchronize properly between threads

- SimplePIM is a high-level programming framework for real PIM hardware

- Iterators such as map, reduce, and zip

- Collective communication with broadcast, scatter, and gather

- Implementation on UPMEM and evaluation with six different workloads

- Reduction, vector add, histogram, linear/logistic regression, K-means

- 4.4x fewer lines of code compared to hand-optimized code

- Between 15% and 43% faster than hand-optimized code for three workloads

- Source code: <a href="https://github.com/CMU-SAFARI/SimplePIM">https://github.com/CMU-SAFARI/SimplePIM</a>

### The SimplePIM Programming Framework

#### **Our Goal**

Design a high-level programming framework that abstracts hardware-specific complexities and provides a clean yet powerful interface for ease of use and high program performance

- SimplePIM provides standard abstractions to build and deploy applications on PIM systems

- Management interface

- Metadata management for PIM-resident arrays

- Communication interface

- Abstractions for host-PIM and PIM-PIM communication

- Collective communication with broadcast, scatter, and gather

- Processing interface

- Iterators (map, reduce, zip) to implement workloads

### SimpePIM: General Code Optimizations

- Strength reduction

- Loop unrolling

- Avoiding boundary checks

- Function inlining

- Adjustment of data transfer sizes

### More in the Paper

### SimplePIM: A Software Framework for Productive and Efficient Processing-in-Memory

```

Jinfan Chen<sup>1</sup> Juan Gómez-Luna<sup>1</sup> Izzat El Hajj<sup>2</sup> Yuxin Guo<sup>1</sup> Onur Mutlu<sup>1</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>American University of Beirut

```

https://arxiv.org/pdf/2310.01893.pdf

### Productivity Improvement (I)

• Example: Hand-optimized histogram with UPMEM SDK

```

... // Initialize global variables and functions for histogram

int main kernel() {

if (tasklet id == 0)

mem reset(); // Reset the heap

... // Initialize variables and the histogram

T *input buff A = (T^*) mem alloc(2048); // Allocate buffer in scratchpad memory

for (unsigned int byte index = base tasklet; byte index < input size; byte index += stride) {</pre>

// Boundary checking

uint32 t l size bytes = (byte index + 2048 >= input size) ? (input size - byte index) : 2048;

// Load scratchpad with a DRAM block

mram read((const mram ptr void*)(mram base addr A + byte index), input buff A, 1 size bytes);

// Histogram calculation

histogram(hist, bins, input buff A, 1 size bytes/sizeof(uint32 t));

barrier wait(&my barrier); // Barrier to synchronize PIM threads

... // Merging histograms from different tasklets into one histo dpu

// Write result from scratchpad to DRAM

if (tasklet id == 0)

if (bins * sizeof(uint32 t) <= 2048)</pre>

mram write(histo dpu, ( mram ptr void*)mram base addr histo, bins * sizeof(uint32 t));

else

for (unsigned int offset = 0; offset < ((bins * sizeof(uint32 t)) >> 11); offset++) {

mram write(histo dpu + (offset << 9), ( mram ptr void*) (mram base addr histo +</pre>

(offset << 11)), 2048);

return 0;

```

### **Productivity Improvement (II)**

Example: SimplePIM histogram

```

// Programmer-defined functions in the file "histo filepath"

void init func (uint32 t size, void* ptr) {

char* casted value ptr = (char*) ptr;

for (int i = 0; i < size; i++)</pre>

casted value ptr[i] = 0;

void acc func (void* dest, void* src) {

*(uint32 t*)dest += *(uint32 t*)src;

void map to val func (void* input, void* output, uint32 t* key) {

uint32 t d = *((uint32 t*)input);

*(uint32 t*)output = 1;

*key = d * bins >> 12;

// Host side handle creation and iterator call

handle t* handle = simple pim create handle("histo filepath", REDUCE, NULL, 0);

// Transfer (scatter) data to PIM, register as "t1"

simple pim array scatter("t1", src, bins, sizeof(T), management);

// Run histogram on "t1" and produce "t2"

simple pim array red("t1", "t2", sizeof(T), bins, handle, management);

```

### **Productivity Improvement (III)**

Lines of code (LoC) reduction

|                            | SimplePIM | Hand-optimized | LoC Reduction |

|----------------------------|-----------|----------------|---------------|

| Reduction                  | 14        | 83             | 5.93×         |

| <b>Vector Addition</b>     | 14        | 82             | 5.86×         |

| Histogram                  | 21        | 114            | 5•43×         |

| <b>Linear Regression</b>   | 48        | 157            | 3.27×         |

| <b>Logistic Regression</b> | 59        | 176            | 2.98×         |

| K-Means                    | 68        | 206            | 3.03×         |

SimplePIM reduces the number of lines of effective code by a factor of 2.98× to 5.93×

#### **Performance Evaluation**

Weak scaling analysis

SimplePIM achieves comparable performance for reduction, histogram, and linear regression

SimplePIM outperforms hand-optimized implementations for vector addition, logistic regression, and k-means by 10%-37%

#### Truly Distributed GPU Processing with PIM

void applyScaleFactorsKernel( uint8\_T \* const out, uint8\_T const \* const in, const double \*factor,

### Accelerating GPU Execution with PIM (I)

Kevin Hsieh, Eiman Ebrahimi, Gwangsun Kim, Niladrish Chatterjee, Mike O'Connor, Nandita Vijaykumar, Onur Mutlu, and Stephen W. Keckler, "Transparent Offloading and Mapping (TOM): Enabling Programmer-Transparent Near-Data Processing in GPU Systems"

Proceedings of the <u>43rd International Symposium on Computer</u> <u>Architecture</u> (**ISCA**), Seoul, South Korea, June 2016. [Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

#### Transparent Offloading and Mapping (TOM): Enabling Programmer-Transparent Near-Data Processing in GPU Systems

Kevin Hsieh<sup>‡</sup> Eiman Ebrahimi<sup>†</sup> Gwangsun Kim<sup>\*</sup> Niladrish Chatterjee<sup>†</sup> Mike O'Connor<sup>†</sup> Nandita Vijaykumar<sup>‡</sup> Onur Mutlu<sup>§‡</sup> Stephen W. Keckler<sup>†</sup> <sup>‡</sup>Carnegie Mellon University <sup>†</sup>NVIDIA \*KAIST <sup>§</sup>ETH Zürich

### Accelerating GPU Execution with PIM (II)

Ashutosh Pattnaik, Xulong Tang, Adwait Jog, Onur Kayiran, Asit K.

Mishra, Mahmut T. Kandemir, Onur Mutlu, and Chita R. Das,

"Scheduling Techniques for GPU Architectures with Processing-In-Memory Capabilities"

Proceedings of the <u>25th International Conference on Parallel</u>

<u>Architectures and Compilation Techniques</u> (**PACT**), Haifa, Israel,

September 2016.

### Scheduling Techniques for GPU Architectures with Processing-In-Memory Capabilities

Ashutosh Pattnaik<sup>1</sup> Xulong Tang<sup>1</sup> Adwait Jog<sup>2</sup> Onur Kayıran<sup>3</sup>

Asit K. Mishra<sup>4</sup> Mahmut T. Kandemir<sup>1</sup> Onur Mutlu<sup>5,6</sup> Chita R. Das<sup>1</sup>

<sup>1</sup>Pennsylvania State University <sup>2</sup>College of William and Mary

<sup>3</sup>Advanced Micro Devices, Inc. <sup>4</sup>Intel Labs <sup>5</sup>ETH Zürich <sup>6</sup>Carnegie Mellon University

### Accelerating Linked Data Structures

Kevin Hsieh, Samira Khan, Nandita Vijaykumar, Kevin K. Chang, Amirali Boroumand, Saugata Ghose, and Onur Mutlu,

"Accelerating Pointer Chasing in 3D-Stacked Memory:

Challenges, Mechanisms, Evaluation"

Proceedings of the 34th IEEE International Conference on Computer

Design (ICCD), Phoenix, AZ, USA, October 2016.

### Accelerating Pointer Chasing in 3D-Stacked Memory: Challenges, Mechanisms, Evaluation

Kevin Hsieh<sup>†</sup> Samira Khan<sup>‡</sup> Nandita Vijaykumar<sup>†</sup> Kevin K. Chang<sup>†</sup> Amirali Boroumand<sup>†</sup> Saugata Ghose<sup>†</sup> Onur Mutlu<sup>§†</sup> <sup>†</sup> Carnegie Mellon University <sup>‡</sup> University of Virginia <sup>§</sup> ETH Zürich

### Accelerating Dependent Cache Misses

Milad Hashemi, Khubaib, Eiman Ebrahimi, Onur Mutlu, and Yale N. Patt,

"Accelerating Dependent Cache Misses with an Enhanced Memory Controller"

Proceedings of the <u>43rd International Symposium on Computer</u> <u>Architecture</u> (**ISCA**), Seoul, South Korea, June 2016. [Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

### Accelerating Dependent Cache Misses with an Enhanced Memory Controller

Milad Hashemi\*, Khubaib<sup>†</sup>, Eiman Ebrahimi<sup>‡</sup>, Onur Mutlu<sup>§</sup>, Yale N. Patt\*

\*The University of Texas at Austin †Apple ‡NVIDIA §ETH Zürich & Carnegie Mellon University

### Accelerating Runahead Execution

Milad Hashemi, Onur Mutlu, and Yale N. Patt,

"Continuous Runahead: Transparent Hardware Acceleration for Memory Intensive Workloads"

Proceedings of the 49th International Symposium on

Microarchitecture (MICRO), Taipei, Taiwan, October 2016.

[Slides (pptx) (pdf)] [Lightning Session Slides (pdf)] [Poster (pptx) (pdf)]

Best paper session.

### Continuous Runahead: Transparent Hardware Acceleration for Memory Intensive Workloads

Milad Hashemi\*, Onur Mutlu§, Yale N. Patt\*

\*The University of Texas at Austin §ETH Zürich

### Accelerating Climate Modeling

Gagandeep Singh, Dionysios Diamantopoulos, Christoph Hagleitner, Juan Gómez-Luna, Sander Stuijk, Onur Mutlu, and Henk Corporaal, "NERO: A Near High-Bandwidth Memory Stencil Accelerator for Weather Prediction Modeling"

Proceedings of the <u>30th International Conference on Field-Programmable Logic</u> <u>and Applications</u> (**FPL**), Gothenburg, Sweden, September 2020.

[Slides (pptx) (pdf)]

[<u>Lightning Talk Slides (pptx) (pdf)</u>]

[Talk Video (23 minutes)]

Nominated for the Stamatis Vassiliadis Memorial Award.

### NERO: A Near High-Bandwidth Memory Stencil Accelerator for Weather Prediction Modeling

Gagandeep Singh $^{a,b,c}$  Dionysios Diamantopoulos $^c$  Christoph Hagleitner $^c$  Juan Gómez-Luna $^b$  Sander Stuijk $^a$  Onur Mutlu $^b$  Henk Corporaal $^a$  Eindhoven University of Technology  $^b$ ETH Zürich  $^c$ IBM Research Europe, Zurich

### Accelerating DNA Read Mapping

Jeremie S. Kim, Damla Senol Cali, Hongyi Xin, Donghyuk Lee, Saugata Ghose, Mohammed Alser, Hasan Hassan, Oguz Ergin, Can Alkan, and Onur Mutlu,

"GRIM-Filter: Fast Seed Location Filtering in DNA Read Mapping Using Processing-in-Memory Technologies"

**BMC Genomics**, 2018.

Proceedings of the <u>16th Asia Pacific Bioinformatics Conference</u> (**APBC**), Yokohama, Japan, January 2018.

[Slides (pptx) (pdf)]

[Source Code]

[arxiv.org Version (pdf)]

[Talk Video at AACBB 2019]

# GRIM-Filter: Fast seed location filtering in DNA read mapping using processing-in-memory technologies

Jeremie S. Kim<sup>1,6\*</sup>, Damla Senol Cali<sup>1</sup>, Hongyi Xin<sup>2</sup>, Donghyuk Lee<sup>3</sup>, Saugata Ghose<sup>1</sup>, Mohammed Alser<sup>4</sup>, Hasan Hassan<sup>6</sup>, Oguz Ergin<sup>5</sup>, Can Alkan<sup>4\*</sup> and Onur Mutlu<sup>6,1\*</sup>

### Accelerating Approximate String Matching

Damla Senol Cali, Gurpreet S. Kalsi, Zulal Bingol, Can Firtina, Lavanya Subramanian, Jeremie S. Kim, Rachata Ausavarungnirun, Mohammed Alser, Juan Gomez-Luna, Amirali Boroumand, Anant Nori, Allison Scibisz, Sreenivas Subramoney, Can Alkan, Saugata Ghose, and Onur Mutlu, "GenASM: A High-Performance, Low-Power Approximate String Matching Acceleration Framework for Genome Sequence Analysis"

Proceedings of the 53rd International Symposium on Microarchitecture (MICRO), Virtual, October 2020.

[<u>Lighting Talk Video</u> (1.5 minutes)] [<u>Lightning Talk Slides (pptx) (pdf)</u>] [<u>Talk Video</u> (18 minutes)] [<u>Slides (pptx) (pdf)</u>]

#### GenASM: A High-Performance, Low-Power Approximate String Matching Acceleration Framework for Genome Sequence Analysis

Damla Senol Cali<sup>†™</sup> Gurpreet S. Kalsi<sup>™</sup> Zülal Bingöl<sup>▽</sup> Can Firtina<sup>⋄</sup> Lavanya Subramanian<sup>‡</sup> Jeremie S. Kim<sup>⋄†</sup> Rachata Ausavarungnirun<sup>⊙</sup> Mohammed Alser<sup>⋄</sup> Juan Gomez-Luna<sup>⋄</sup> Amirali Boroumand<sup>†</sup> Anant Nori<sup>™</sup> Allison Scibisz<sup>†</sup> Sreenivas Subramoney<sup>™</sup> Can Alkan<sup>▽</sup> Saugata Ghose<sup>\*†</sup> Onur Mutlu<sup>⋄†▽</sup>

† Carnegie Mellon University <sup>™</sup> Processor Architecture Research Lab, Intel Labs <sup>▽</sup> Bilkent University <sup>⋄</sup> ETH Zürich

‡ Facebook <sup>⊙</sup> King Mongkut's University of Technology North Bangkok <sup>\*</sup> University of Illinois at Urbana–Champaign

96

### Accelerating Sequence-to-Graph Mapping

Damla Senol Cali, Konstantinos Kanellopoulos, Joel Lindegger, Zulal Bingol, Gurpreet S. Kalsi, Ziyi Zuo, Can Firtina, Meryem Banu Cavlak, Jeremie Kim, Nika MansouriGhiasi, Gagandeep Singh, Juan Gomez-Luna, Nour Almadhoun Alserr, Mohammed Alser, Sreenivas Subramoney, Can Alkan, Saugata Ghose, and Onur Mutlu, "SeGraM: A Universal Hardware Accelerator for Genomic Sequence-to-Graph and Sequence-to-Sequence Mapping"

Proceedings of the <u>49th International Symposium on Computer Architecture</u> (**ISCA**), New York, June 2022.

arXiv version

### SeGraM: A Universal Hardware Accelerator for Genomic Sequence-to-Graph and Sequence-to-Sequence Mapping

Damla Senol Cali<sup>1</sup> Konstantinos Kanellopoulos<sup>2</sup> Joël Lindegger<sup>2</sup> Zülal Bingöl<sup>3</sup> Gurpreet S. Kalsi<sup>4</sup> Ziyi Zuo<sup>5</sup> Can Firtina<sup>2</sup> Meryem Banu Cavlak<sup>2</sup> Jeremie Kim<sup>2</sup> Nika Mansouri Ghiasi<sup>2</sup> Gagandeep Singh<sup>2</sup> Juan Gómez-Luna<sup>2</sup> Nour Almadhoun Alserr<sup>2</sup> Mohammed Alser<sup>2</sup> Sreenivas Subramoney<sup>4</sup> Can Alkan<sup>3</sup> Saugata Ghose<sup>6</sup> Onur Mutlu<sup>2</sup>

<sup>1</sup>Bionano Genomics <sup>2</sup>ETH Zürich <sup>3</sup>Bilkent University <sup>4</sup>Intel Labs <sup>5</sup>Carnegie Mellon University <sup>6</sup>University of Illinois Urbana-Champaign

### Accelerating Basecalling + Read Mapping

Haiyu Mao, Mohammed Alser, Mohammad Sadrosadati, Can Firtina, Akanksha Baranwal, Damla Senol Cali, Aditya Manglik, Nour Almadhoun Alserr, and Onur Mutlu, "GenPIP: In-Memory Acceleration of Genome Analysis via Tight Integration of Basecalling and Read Mapping"

Proceedings of the <u>55th International Symposium on Microarchitecture</u> (**MICRO**), Chicago, IL, USA, October 2022.

[Slides (pptx) (pdf)]

[Longer Lecture Slides (pptx) (pdf)]

[<u>Lecture Video</u> (25 minutes)]

[arXiv version]

### GenPIP: In-Memory Acceleration of Genome Analysis via Tight Integration of Basecalling and Read Mapping

Haiyu Mao<sup>1</sup> Mohammed Alser<sup>1</sup> Mohammad Sadrosadati<sup>1</sup> Can Firtina<sup>1</sup> Akanksha Baranwal<sup>1</sup> Damla Senol Cali<sup>2</sup> Aditya Manglik<sup>1</sup> Nour Almadhoun Alserr<sup>1</sup> Onur Mutlu<sup>1</sup>

\*\*IETH Zürich\*\*\* \*\*Pionano Genomics\*\*

### Accelerating Basecalling

Taha Shahroodi, Gagandeep Singh, Mahdi Zahedi, Haiyu Mao, Joel Lindegger, Can Firtina, Stephan Wong, Onur Mutlu, and Said Hamdioui,

"Swordfish: A Framework for Evaluating Deep Neural Network-based Basecalling using Computation-In-Memory with Non-Ideal Memristors"

Proceedings of the <u>56th International Symposium on</u>

<u>Microarchitecture</u> (**MICRO**), Toronto, ON, Canada, November 2023.

[<u>Slides (pptx) (pdf)</u>]

[<u>arXiv version</u>]

### Swordfish: A Framework for Evaluating Deep Neural Network-based Basecalling using Computation-In-Memory with Non-Ideal Memristors

Taha Shahroodi<sup>1</sup> Gagandeep Singh<sup>2,3</sup> Mahdi Zahedi<sup>1</sup> Haiyu Mao<sup>3</sup> Joel Lindegger<sup>3</sup> Can Firtina<sup>3</sup> Stephan Wong<sup>1</sup> Onur Mutlu<sup>3</sup> Said Hamdioui<sup>1</sup>

<sup>1</sup>TU Delft <sup>2</sup>AMD Research <sup>3</sup>ETH Zürich

### Accelerating Time Series Analysis (I)

Ivan Fernandez, Ricardo Quislant, Christina Giannoula, Mohammed Alser, Juan Gómez-Luna, Eladio Gutiérrez, Oscar Plata, and Onur Mutlu, "NATSA: A Near-Data Processing Accelerator for Time Series Analysis" Proceedings of the 38th IEEE International Conference on Computer Design (ICCD), Virtual, October 2020.

[Slides (pptx) (pdf)]

[Talk Video (10 minutes)]

Source Code

### NATSA: A Near-Data Processing Accelerator for Time Series Analysis

Ivan Fernandez§ Ricardo Quislant§ Christina Giannoula† Mohammed Alser‡ Juan Gómez-Luna‡ Eladio Gutiérrez§ Oscar Plata§ Onur Mutlu‡

§University of Malaga †National Technical University of Athens

<sup>‡</sup>ETH Zürich

### Accelerating Time Series Analysis (II)

Ivan Fernandez, Christina Giannoula, Aditya Manglik, Ricardo Quislant, Nika Mansouri Ghiasi, Juan Gomez Luna, Eladio Gutierrez, Oscar Plata and Onur Mutlu,

"MATSA: An MRAM-Based Energy-Efficient Accelerator for Time **Series Analysis**"

IEEE Access, March 2024.

[arXiv version]

[IEEE Access version]

### Accelerating Time Series Analysis via Processing using Non-Volatile Memories

Ivan Fernandez<sup>§†¶</sup> \*Christina Giannoula<sup>†‡</sup> \*Aditya Manglik<sup>†</sup> Ricardo Quislant<sup>§</sup> Nika Mansouri Ghiasi<sup>†</sup> Juan Gómez-Luna<sup>†</sup> Eladio Gutierrez<sup>§</sup> Oscar Plata<sup>§</sup> Onur Mutlu<sup>†</sup>

§University of Malaga

†ETH Zürich

Barcelona Supercomputing Center <sup>†</sup>National Technical University of Athens

### Accelerating Graph Pattern Mining

Maciej Besta, Raghavendra Kanakagiri, Grzegorz Kwasniewski, Rachata Ausavarungnirun, Jakub Beránek, Konstantinos Kanellopoulos, Kacper Janda, Zur Vonarburg-Shmaria, Lukas Gianinazzi, Ioana Stefan, Juan Gómez-Luna, Marcin Copik, Lukas Kapp-Schwoerer, Salvatore Di Girolamo, Nils Blach, Marek Konieczny, Onur Mutlu, and Torsten Hoefler,

"SISA: Set-Centric Instruction Set Architecture for Graph Mining on Processing-in-Memory Systems"

Proceedings of the <u>54th International Symposium on Microarchitecture</u> (**MICRO**), Virtual, October 2021.

[Slides (pdf)]

[Talk Video (22 minutes)]

[<u>Lightning Talk Video</u> (1.5 minutes)]

[Full arXiv version]

### SISA: Set-Centric Instruction Set Architecture for Graph Mining on Processing-in-Memory Systems

Maciej Besta<sup>1</sup>, Raghavendra Kanakagiri<sup>2</sup>, Grzegorz Kwasniewski<sup>1</sup>, Rachata Ausavarungnirun<sup>3</sup>, Jakub Beránek<sup>4</sup>, Konstantinos Kanellopoulos<sup>1</sup>, Kacper Janda<sup>5</sup>, Zur Vonarburg-Shmaria<sup>1</sup>, Lukas Gianinazzi<sup>1</sup>, Ioana Stefan<sup>1</sup>, Juan Gómez-Luna<sup>1</sup>, Marcin Copik<sup>1</sup>, Lukas Kapp-Schwoerer<sup>1</sup>, Salvatore Di Girolamo<sup>1</sup>, Nils Blach<sup>1</sup>, Marek Konieczny<sup>5</sup>, Onur Mutlu<sup>1</sup>, Torsten Hoefler<sup>1</sup>

<sup>1</sup>ETH Zurich, Switzerland <sup>2</sup>IIT Tirupati, India <sup>3</sup>King Mongkut's University of Technology North Bangkok, Thailand <sup>4</sup>Technical University of Ostrava, Czech Republic <sup>5</sup>AGH-UST, Poland

### Accelerating HTAP Database Systems

Amirali Boroumand, Saugata Ghose, Geraldo F. Oliveira, and Onur Mutlu,

"Polynesia: Enabling High-Performance and Energy-Efficient Hybrid

<u>Transactional/Analytical Databases with Hardware/Software Co-Design"</u>

*Proceedings of the <u>38th International Conference on Data Engineering</u> (ICDE),

Virtual, May 2022.*

[arXiv version]

[Slides (pptx) (pdf)]

[Short Talk Slides (pptx) (pdf)]

#### Polynesia: Enabling High-Performance and Energy-Efficient Hybrid Transactional/Analytical Databases with Hardware/Software Co-Design

Amirali Boroumand<sup>†</sup> Saugata Ghose<sup>†</sup> Geraldo F. Oliveira<sup>‡</sup> Onur Mutlu<sup>‡</sup>

†Google <sup>†</sup>Univ. of Illinois Urbana-Champaign <sup>‡</sup>ETH Zürich

### Accelerating ML Inference

Amirali Boroumand, Saugata Ghose, Berkin Akin, Ravi Narayanaswami, Geraldo F. Oliveira, Xiaoyu Ma, Eric Shiu, and Onur Mutlu,

"Google Neural Network Models for Edge Devices: Analyzing and

Mitigating Machine Learning Inference Bottlenecks"

Proceedings of the <u>30th International Conference on Parallel Architectures and</u> <u>Compilation Techniques</u> (**PACT**), Virtual, September 2021.

[Slides (pptx) (pdf)]

[Talk Video (14 minutes)]

#### Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks

Amirali Boroumand<sup>†</sup>

Saugata Ghose<sup>‡</sup>

Berkin Akin<sup>§</sup>

Ravi Narayanaswami<sup>§</sup>

Geraldo F. Oliveira<sup>⋆</sup>

Xiaoyu Ma<sup>§</sup>

Eric Shiu<sup>§</sup>

Onur Mutlu<sup>⋆†</sup>

$^\dagger C$ arnegie Mellon Univ.  $^\diamond S$ tanford Univ.  $^\ddagger U$ niv. of Illinois Urbana-Champaign  $^\S G$ oogle  $^\star ETH$  Zürich

### Accelerating Data-Intensive Workloads

Junwhan Ahn, Sungjoo Yoo, Onur Mutlu, and Kiyoung Choi,

"PIM-Enabled Instructions: A Low-Overhead,

Locality-Aware Processing-in-Memory Architecture"

Proceedings of the <u>42nd International Symposium on</u>

Computer Architecture (ISCA), Portland, OR, June 2015.

[Slides (pdf)] [Lightning Session Slides (pdf)]

#### PIM-Enabled Instructions: A Low-Overhead, Locality-Aware Processing-in-Memory Architecture

Junwhan Ahn Sungjoo Yoo Onur Mutlu<sup>†</sup> Kiyoung Choi junwhan@snu.ac.kr, sungjoo.yoo@gmail.com, onur@cmu.edu, kchoi@snu.ac.kr

Seoul National University <sup>†</sup>Carnegie Mellon University

SAFARI

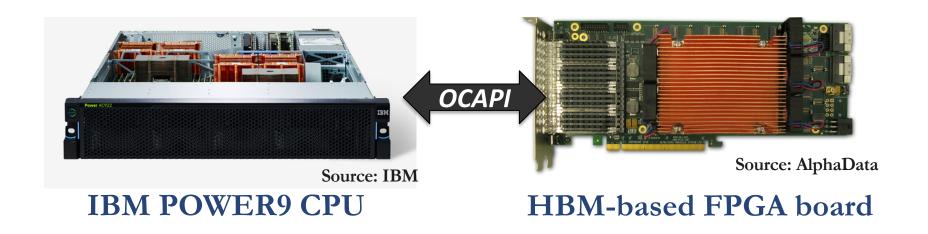

### FPGA-based Processing Near Memory

Gagandeep Singh, Mohammed Alser, Damla Senol Cali, Dionysios

Diamantopoulos, Juan Gómez-Luna, Henk Corporaal, and Onur Mutlu,

"FPGA-based Near-Memory Acceleration of Modern Data-Intensive

Applications"

IEEE Micro (IEEE MICRO), 2021.

## FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications

Gagandeep Singh<sup>⋄</sup> Mohammed Alser<sup>⋄</sup> Damla Senol Cali<sup>⋈</sup>

Dionysios Diamantopoulos<sup>▽</sup> Juan Gómez-Luna<sup>⋄</sup>

Henk Corporaal<sup>⋆</sup> Onur Mutlu<sup>⋄⋈</sup>

<sup>⋄</sup>ETH Zürich <sup>⋈</sup> Carnegie Mellon University \*Eindhoven University of Technology <sup>▽</sup>IBM Research Europe

#### We Need to Revisit the Entire Stack

We can get there step by step

### Security Issues in Processing in Memory

- Does PIM make security better or easier?

- Does PIM make security worse?

- Many interesting questions here

- Some recent papers:

- Evaluating Homomorphic Operations on a Real-World Processing-In-Memory System [IISWC 2023]

- Amplifying Main Memory-Based Timing Covert and Side Channels using Processing-in-Memory Operations [arxiv 2024]

### Homomorphic Operations on Real PIM Systems

Harshita Gupta, Mayank Kabra, Juan Gómez-Luna, Konstantinos Kanellopoulos, and Onur Mutlu,

"Evaluating Homomorphic Operations on a Real-World Processing-In-Memory System"

<u>Proceedings of the 2023 IEEE International Symposium on Workload</u> <u>Characterization</u> Poster Session (**IISWC**), Ghent, Belgium, October 2023.

arXiv version

[Lightning Talk Slides (pptx) (pdf)]

[Poster (pptx) (pdf)]

# **Evaluating Homomorphic Operations on a Real-World Processing-In-Memory System**

Harshita Gupta\* Mayank Kabra\* Juan Gómez-Luna Konstantinos Kanellopoulos Onur Mutlu

ETH Zürich

### PIM Amplifies Covert & Side Channels

# Amplifying Main Memory-Based Timing Covert and Side Channels using Processing-in-Memory Operations

```

Konstantinos Kanellopoulos<sup>†*</sup> F. Nisa Bostancı<sup>†*</sup> Ataberk Olgun<sup>†</sup>

A. Giray Yağlıkçı<sup>†</sup> İsmail Emir Yüksel<sup>†</sup> Nika Mansouri Ghiasi<sup>†</sup>

Zülal Bingöl<sup>†‡</sup> Mohammad Sadrosadati<sup>†</sup> Onur Mutlu<sup>†</sup>

<sup>†</sup>ETH Zürich <sup>‡</sup>Bilkent University

```

https://arxiv.org/pdf/2404.11284

### A Talk on Security of PIM Systems

### Eliminating the Adoption Barriers

# Processing-in-Memory in the Real World

### PIM Tutorial at ISCA 2024

### ISCA 2024 Memory-Centric Computing Systems Tutorial

Saturday, June 29, Buenos Aires, Argentina

Organizers: Geraldo F. Oliveira, Dr. Mohammad Sadrosadati,

Ataberk Olgun, Professor Onur Mutlu

Program: https://events.safari.ethz.ch/isca24-memorycentric-tutorial/

Overview of PIM | PIM taxonomy

PIM in memory & storage

Real-world PNM systems

PUM for bulk bitwise operations

Programming techniques & tools

Infrastructures for PIM Research

Research challenges &

opportunities

https://www.youtube.com/watch?v=KV2MXvcBqb0

https://events.safari.ethz.ch/isca24-memorycentric-tutorial

### PIM Tutorials [micro'23, isca'23, asplos'23, hpca'23, isca'24]

#### Lectures + Hands-on labs + Invited talks

https://www.youtube.com/live/GIb5EqSrWk0

https://events.safari.ethz.ch/isca-pim-tutorial/

### Real PIM Tutorial [ISCA 2023]

#### June 18: Lectures + Hands-on labs + Invited talks

#### **Tutorial Materials**

| Time                | Speaker                                | Title                                                                                                                  | Materials                        |

|---------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 8:55am-<br>9:00am   | Dr. Juan Gómez Luna                    | Welcome & Agenda                                                                                                       | ▶(PDF) P (PPT)                   |

| 9:00am-<br>10:20am  | Prof. Onur Mutlu                       | Memory-Centric Computing                                                                                               | ▶(PDF) P (PPT)                   |

| 10:20am-<br>11:00am | Dr. Juan Gómez Luna                    | Processing-Near-Memory: Real PNM Architectures / Programming General-purpose PIM                                       | ▶(PDF) P (PPT)                   |

| 11:20am-<br>11:50am | Prof. Izzat El Hajj                    | High-throughput Sequence Alignment using Real Processing-in-Memory Systems                                             | ▶(PDF) P (PPT)                   |

| 11:50am-<br>12:30pm | Dr. Christina Giannoula                | SparseP: Towards Efficient Sparse Matrix Vector Multiplication for Real Processing-In-Memory Systems                   | ▶(PDF) P (PPT)                   |

| 2:00pm-<br>2:45pm   | Dr. Sukhan Lee                         | Introducing Real-world HBM-PIM Powered System for Memory-bound Applications                                            | (PDF) (PPT)                      |

| 2:45pm-<br>3:30pm   | Dr. Juan Gómez Luna /<br>Ataberk Olgun | Processing-Using-Memory: Exploiting the Analog Operational<br>Properties of Memory Components / PUM Prototypes: PiDRAM | → (PDF) P (PPT)  → (PDF) P (PPT) |

| 4:00pm-<br>4:40pm   | Dr. Juan Gómez Luna                    | Accelerating Modern Workloads on a General-purpose PIM System                                                          | ▶(PDF) P (PPT)                   |

| 4:40pm-<br>5:20pm   | Dr. Juan Gómez Luna                    | Adoption Issues: How to Enable PIM?                                                                                    | ▶(PDF) P (PPT)                   |

| 5:20pm-<br>5:30pm   | Dr. Juan Gómez Luna                    | Hands-on Lab: Programming and Understanding a Real Processing-in-<br>Memory Architecture                               | → (Handout)  → (PDF) P (PPT)     |

https://www.youtube.com/ live/GIb5EgSrWk0

https://events.safari.ethz.ch/ isca-pim-tutorial/

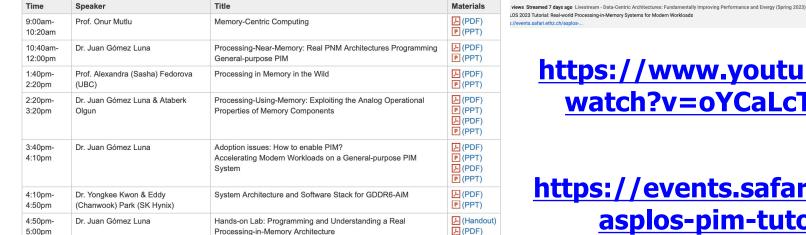

### Real PIM Tutorial [ASPLOS 2023]

#### March 26: Lectures + Hands-on labs + Invited talks

#### ASPLOS 2023 Tutorial: Real-world Processing-in-Memory Systems for Modern Workloads

P (PPT)

Onur Mutlu Lectures 32.1K subscribers

https://www.youtube.com/ watch?v=oYCaLcT0Kmo

https://events.safari.ethz.ch/ asplos-pim-tutorial/

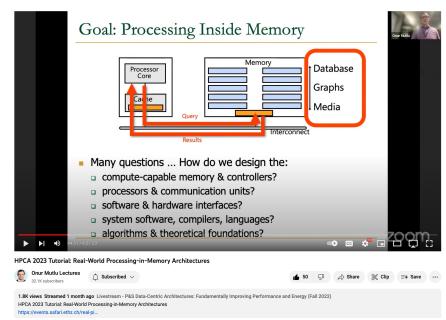

### Real PIM Tutorial [HPCA 2023]

#### February 26: Lectures + Hands-on labs + Invited Talks

| Time                | Speaker                    | Title                                                                                                         | Materials     |  |  |

|---------------------|----------------------------|---------------------------------------------------------------------------------------------------------------|---------------|--|--|

| 8:00am-<br>8:40am   | Prof. Onur Mutlu           | Memory-Centric Computing                                                                                      |               |  |  |

| 8:40am-<br>10:00am  | Dr. Juan Gómez<br>Luna     | Processing-Near-Memory: Real PNM Architectures Programming General-purpose PIM                                | ♪(PDF) P(PPT) |  |  |

| 10:20am-<br>11:00am | Dr. Dimin Niu              | A 3D Logic-to-DRAM Hybrid Bonding Process-Near-Memory Chip for Recommendation                                 | on System     |  |  |

| 11:00am-<br>11:40am | Dr. Christina<br>Giannoula | SparseP: Towards Efficient Sparse Matrix Vector Multiplication on Real Processing-<br>In-Memory Architectures | P (PDF)       |  |  |

| 1:30pm-<br>2:10pm   | Dr. Juan Gómez<br>Luna     | Processing-Using-Memory: Exploiting the Analog Operational Properties of Memory Components                    | P (PDF)       |  |  |

| 2:10pm-<br>2:50pm   | Dr. Manuel Le<br>Gallo     | Deep Learning Inference Using Computational Phase-Change Memory                                               |               |  |  |

| 2:50pm-<br>3:30pm   | Dr. Juan Gómez<br>Luna     | PIM Adoption Issues: How to Enable PIM Adoption?                                                              |               |  |  |

| 3:40pm-<br>5:40pm   | Dr. Juan Gómez<br>Luna     | Hands-on Lab: Programming and Understanding a Real Processing-in-Memory Architecture                          |               |  |  |

https://www.youtube.com/watch?v=f5-nT1tbz5w

https://events.safari.ethz.ch/ real-pim-tutorial/

### Real PIM Tutorial [MICRO 2023]

#### October 29: Lectures + Hands-on labs + Invited talks

https://www.youtube.com/watch ?v=ohUooNSIxOI

https://events.safari.ethz.ch/micro -pim-tutorial

#### Agenda (Tentative, October 29, 2023)

#### Lectures

- 1. Introduction: PIM as a paradigm to overcome the data movement bottleneck.

- 2. PIM taxonomy: PNM (processing near memory) and PUM (processing using memory).

- 3. General-purpose PNM: UPMEM PIM.

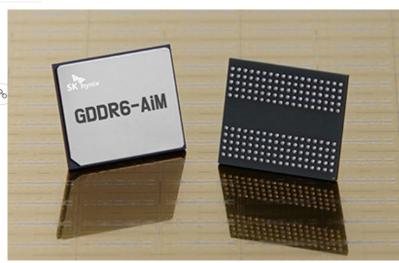

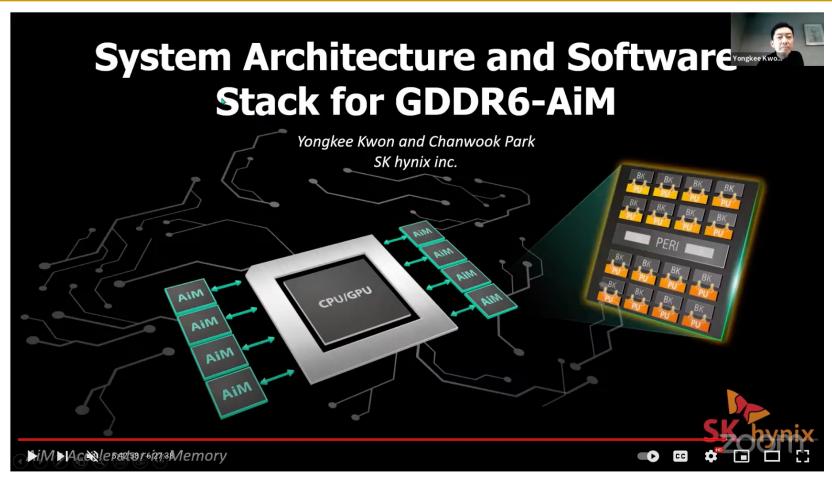

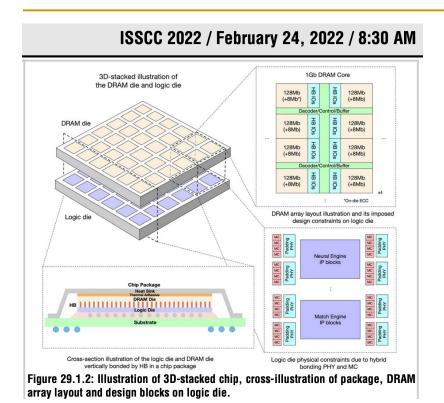

- 4. PNM for neural networks: Samsung HBM-PIM, SK Hynix AiM.

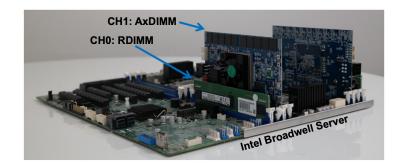

- 5. PNM for recommender systems: Samsung AxDIMM, Alibaba PNM.

- 6. PUM prototypes: PiDRAM, SRAM-based PUM, Flash-based PUM.

- 7. Other approaches: Neuroblade, Mythic.

- 8. Adoption issues: How to enable PIM?

- Hands-on labs: Programming a real PIM system.

### FPGA-based Processing Near Memory

Gagandeep Singh, Mohammed Alser, Damla Senol Cali, Dionysios

Diamantopoulos, Juan Gómez-Luna, Henk Corporaal, and Onur Mutlu,

"FPGA-based Near-Memory Acceleration of Modern Data-Intensive

Applications"

IEEE Micro (IEEE MICRO), 2021.

# FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications

Gagandeep Singh<sup>⋄</sup> Mohammed Alser<sup>⋄</sup> Damla Senol Cali<sup>⋈</sup>

Dionysios Diamantopoulos<sup>▽</sup> Juan Gómez-Luna<sup>⋄</sup>

Henk Corporaal<sup>⋆</sup> Onur Mutlu<sup>⋄⋈</sup>

<sup>⋄</sup>ETH Zürich <sup>⋈</sup> Carnegie Mellon University \*Eindhoven University of Technology <sup>▽</sup>IBM Research Europe

### Near-Memory Acceleration using FPGAs

#### **Near-HBM FPGA-based accelerator**

Two communication technologies: CAPI2 and OCAPI

Two memory technologies: DDR4 and HBM

Two workloads: Weather Modeling and Genome Analysis

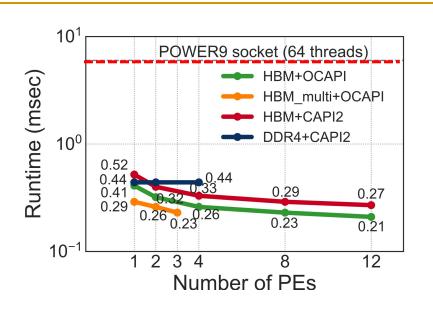

### Performance & Energy Greatly Improve

5-27× performance vs. a 16-core (64-thread) IBM POWER9 CPU

12-133× energy efficiency vs. a 16-core (64-thread) IBM POWER9 CPU

**HBM alleviates memory bandwidth contention vs. DDR4**

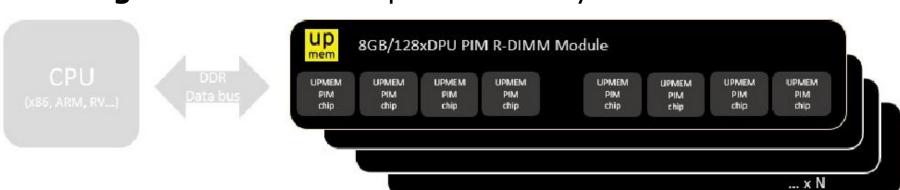

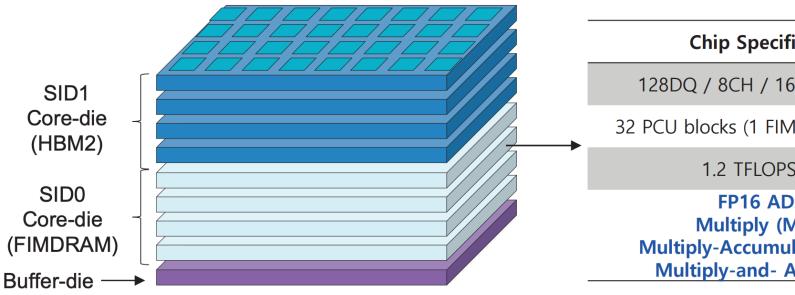

### UPMEM Processing-in-DRAM Engine (2019)

- Processing in DRAM Engine

- Includes standard DIMM modules, with a large number of DPU processors combined with DRAM chips.

- Replaces standard DIMMs

- DDR4 R-DIMM modules

- 8GB+128 DPUs (16 PIM chips)

- Standard 2x-nm DRAM process

- Large amounts of compute & memory bandwidth

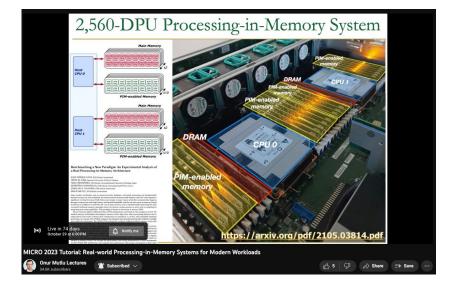

### Experimental Analysis of the UPMEM PIM Engine

### Benchmarking a New Paradigm: An Experimental Analysis of a Real Processing-in-Memory Architecture

JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland IZZAT EL HAJJ, American University of Beirut, Lebanon IVAN FERNANDEZ, ETH Zürich, Switzerland and University of Malaga, Spain CHRISTINA GIANNOULA, ETH Zürich, Switzerland and NTUA, Greece GERALDO F. OLIVEIRA, ETH Zürich, Switzerland ONUR MUTLU, ETH Zürich, Switzerland

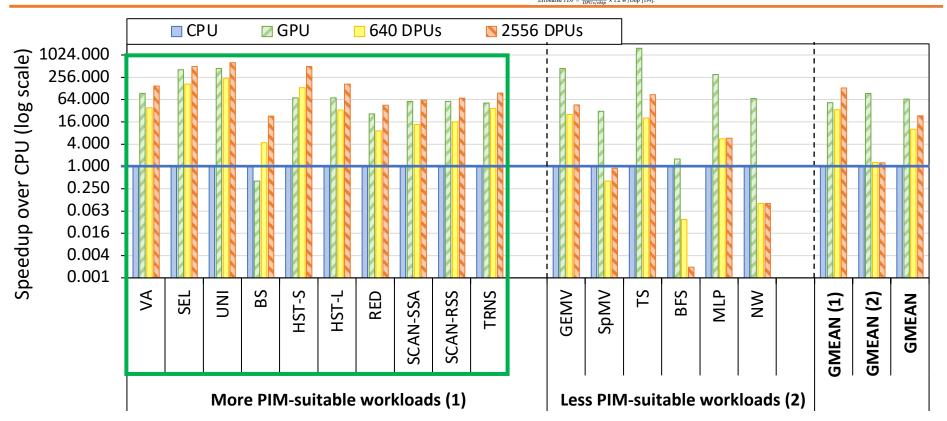

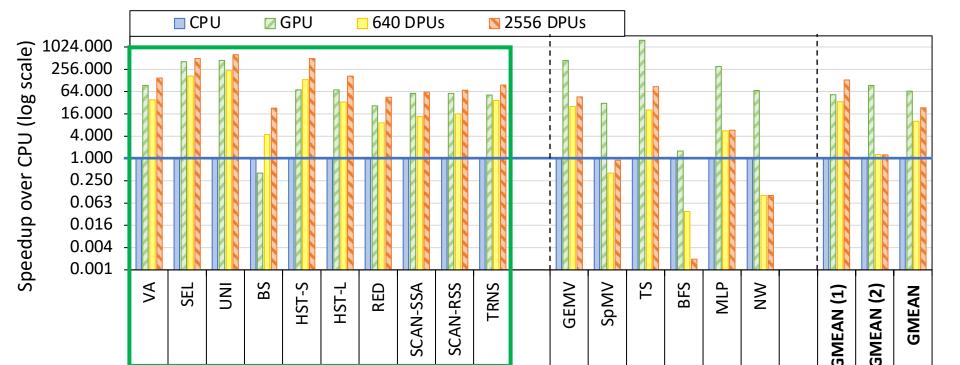

Many modern workloads, such as neural networks, databases, and graph processing, are fundamentally memory-bound. For such workloads, the data movement between main memory and CPU cores imposes a significant overhead in terms of both latency and energy. A major reason is that this communication happens through a narrow bus with high latency and limited bandwidth, and the low data reuse in memory-bound workloads is insufficient to amortize the cost of main memory access. Fundamentally addressing this *data movement bottleneck* requires a paradigm where the memory system assumes an active role in computing by integrating processing capabilities. This paradigm is known as *processing-in-memory (PIM)*.

Recent research explores different forms of PIM architectures, motivated by the emergence of new 3D-stacked memory technologies that integrate memory with a logic layer where processing elements can be easily placed. Past works evaluate these architectures in simulation or, at best, with simplified hardware prototypes. In contrast, the UPMEM company has designed and manufactured the first publicly-available real-world PIM architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called *DRAM Processing Units* (*DPUs*), integrated in the same chip.

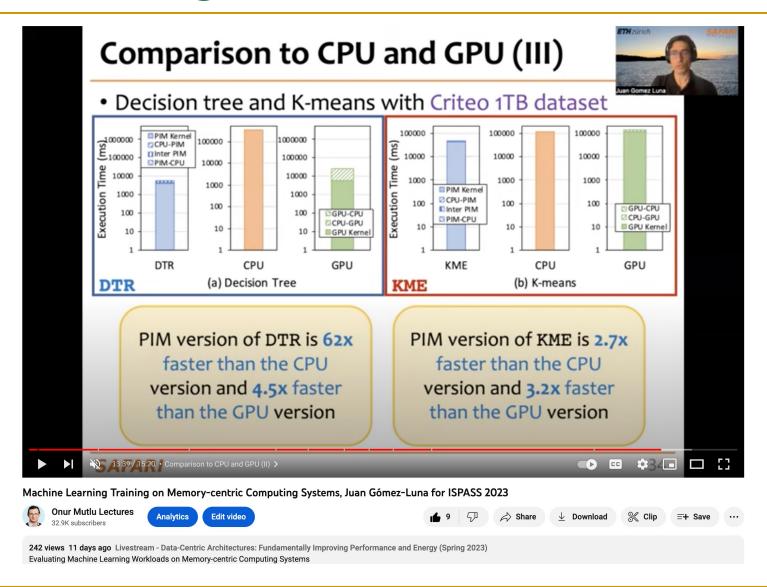

This paper provides the first comprehensive analysis of the first publicly-available real-world PIM architecture. We make two key contributions. First, we conduct an experimental characterization of the UPMEM-based PIM system using microbenchmarks to assess various architecture limits such as compute throughput and memory bandwidth, yielding new insights. Second, we present *PrIM* (*Processing-In-Memory benchmarks*), a benchmark suite of 16 workloads from different application domains (e.g., dense/sparse linear algebra, databases, data analytics, graph processing, neural networks, bioinformatics, image processing), which we identify as memory-bound. We evaluate the performance and scaling characteristics of PrIM benchmarks on the UPMEM PIM architecture, and compare their performance and energy consumption to their state-of-the-art CPU and GPU counterparts. Our extensive evaluation conducted on two real UPMEM-based PIM systems with 640 and 2,556 DPUs provides new insights about suitability of different workloads to the PIM system, programming recommendations for software designers, and suggestions and hints for hardware and architecture designers of future PIM systems.

https://arxiv.org/pdf/2105.03814.pdf

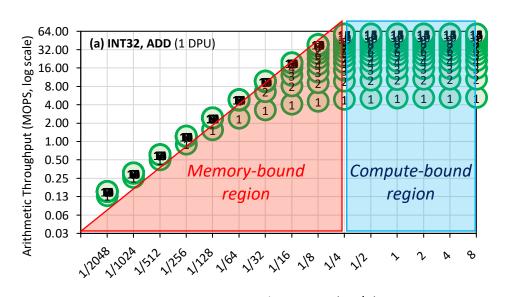

### **Key Takeaway 1**

The throughput saturation point is as low as ¼ OP/B, i.e., 1 integer addition per every 32-bit element fetched

Operational Intensity (OP/B)

#### KEY TAKEAWAY 1

The UPMEM PIM architecture is fundamentally compute bound. As a result, the most suitable workloads are memory-bound.

#### Table 4: Evaluated CPU, GPU, and UPMEM-based PIM Systems.

### Key Takeaway 2

|                                 | _       | _                     |           |                  |           | -               |                    |

|---------------------------------|---------|-----------------------|-----------|------------------|-----------|-----------------|--------------------|

| System                          | Process | Processor Cores       |           |                  | Memory    |                 | TDP                |

| system                          | Node    | Total Cores           | Frequency | Peak Performance | Capacity  | Total Bandwidth | IDF                |

| Intel Xeon E3-1225 v6 CPU [241] | 14 nm   | 4 (8 threads)         | 3.3 GHz   | 26.4 GFLOPS*     | 32 GB     | 37.5 GB/s       | 73 W               |

| NVIDIA Titan V GPU [277]        | 14 nm   | 80 (5,120 SIMD lanes) | 1.2 GHz   | 12,288.0 GFLOPS  | 12 GB     | 652.8 GB/s      | 250 W              |

| 2,556-DPU PIM System            | 2x nm   | 2,5569                | 350 MHz   | 894.6 GOPS       | 159.75 GB | 1.7 TB/s        | 383 W <sup>†</sup> |

| 640-DPU PIM System              | 2x nm   | 640                   | 267 MHz   | 170.9 GOPS       | 40 GB     | 333.75 GB/s     | 96 W <sup>†</sup>  |

<sup>\*</sup>Estimated GFLOPS = 3.3 GHz × 4 cores × 2 instructions per cycle.

†Estimated TDP = Total DPUs

| DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPUs | DPU

#### KEY TAKEAWAY 2

The most well-suited workloads for the UPMEM PIM architecture use no arithmetic operations or use only simple operations (e.g., bitwise operations and integer addition/subtraction).

#### ${\bf Table~4: Evaluated~CPU, GPU, and~UPMEM-based~PIM~Systems.}$

### **Key Takeaway 3**

| System                          | Process | Processor Cores       |           |                  | Memory    |                 | TDP                |

|---------------------------------|---------|-----------------------|-----------|------------------|-----------|-----------------|--------------------|

| system                          | Node    | Total Cores           | Frequency | Peak Performance | Capacity  | Total Bandwidth | IDF                |

| Intel Xeon E3-1225 v6 CPU [241] | 14 nm   | 4 (8 threads)         | 3.3 GHz   | 26.4 GFLOPS*     | 32 GB     | 37.5 GB/s       | 73 W               |

| NVIDIA Titan V GPU [277]        | 14 nm   | 80 (5,120 SIMD lanes) | 1.2 GHz   | 12,288.0 GFLOPS  | 12 GB     | 652.8 GB/s      | 250 W              |

| 2,556-DPU PIM System            | 2x nm   | 2,556 <sup>9</sup>    | 350 MHz   | 894.6 GOPS       | 159.75 GB | 1.7 TB/s        | 383 W <sup>†</sup> |