Memory System Design for AI/ML Accelerators & ML/AI Techniques for Memory System Design

> Onur Mutlu omutlu@gmail.com https://people.inf.ethz.ch/omutlu 30 August 2022 SRC AIHW Annual Review

SAFARI

**ETH** zürich

### Confidentiality

- By reviewing this presentation or participating in a SRC event, you are agreeing not to use the presented information for purposes unrelated to the event until approved by SRC;

- Material may be presented that represents current research, some of which has not been published or protected. This material is not for public disclosure and until potential IP rights have been protected, please treat all of the information presented as <u>confidential information</u> which is the property of the researcher and their university.

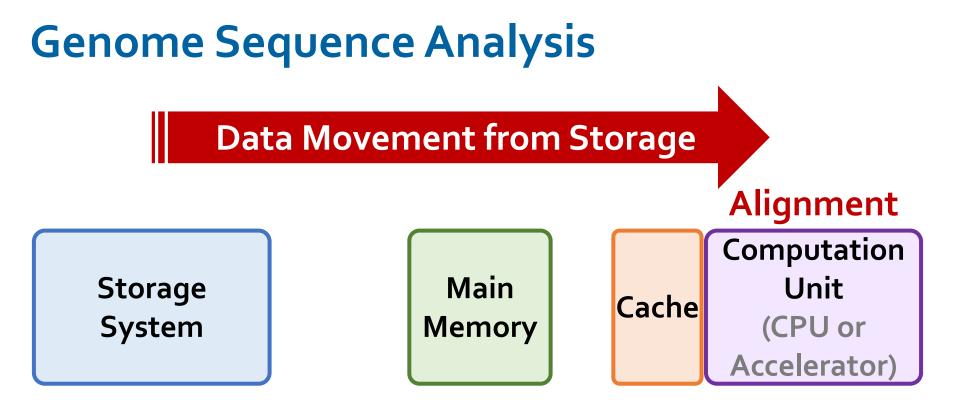

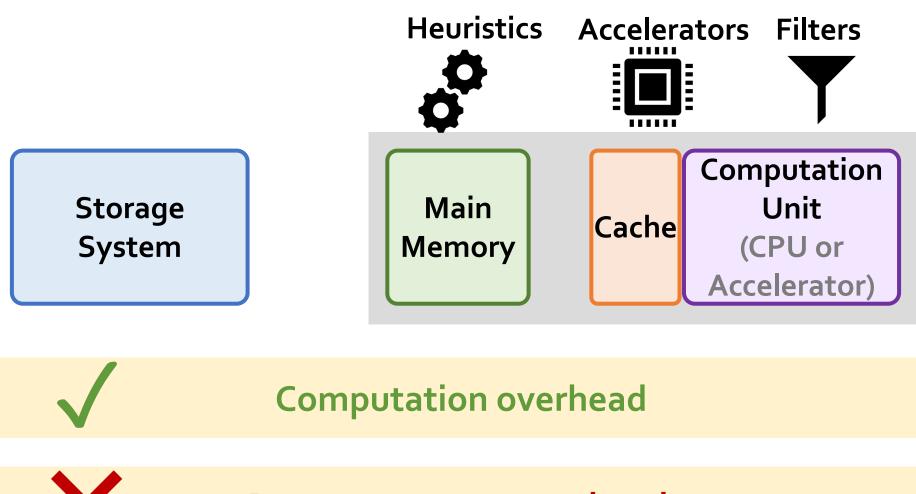

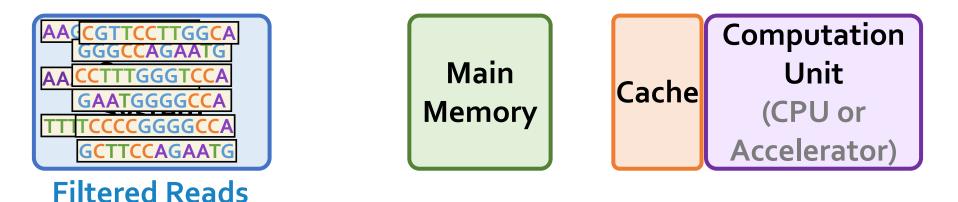

Problem and Background

Task Overview

Technical Challenges, Goals and Ideas

Ideas, Results and Papers from the Past Year

# Computing is Bottlenecked by Data

# Data is Key for AI, ML, Genomics, ...

Important workloads are all data intensive

They require rapid and efficient processing of large amounts of data

- Data is increasing

- □ We can generate more than we can process

# Data is Key for Future Workloads

### **In-memory Databases**

[Mao+, EuroSys'12; Clapp+ (**Intel**), IISWC'15]

### **In-Memory Data Analytics**

[Clapp+ (**Intel**), IISWC'15; Awan+, BDCloud'15]

**Graph/Tree Processing** [Xu+, IISWC'12; Umuroglu+, FPL'15]

**Datacenter Workloads** [Kanev+ (**Google**), ISCA'15]

# Data Overwhelms Modern Machines

### **In-memory Databases**

### **Graph/Tree Processing**

# Data → performance & energy bottleneck

### In-Memory Data Analytics

[Clapp+ (**Intel**), IISWC'15; Awan+, BDCloud'15]

**Datacenter Workloads** [Kanev+ (**Google**), ISCA'I 5]

# Data is Key for Future Workloads

**Google's web browser**

### **TensorFlow Mobile**

Google's machine learning framework

**Google's video codec**

# Data Overwhelms Modern Machines

# Data → performance & energy bottleneck

**Google's video codec**

# Data is Key for Future Workloads

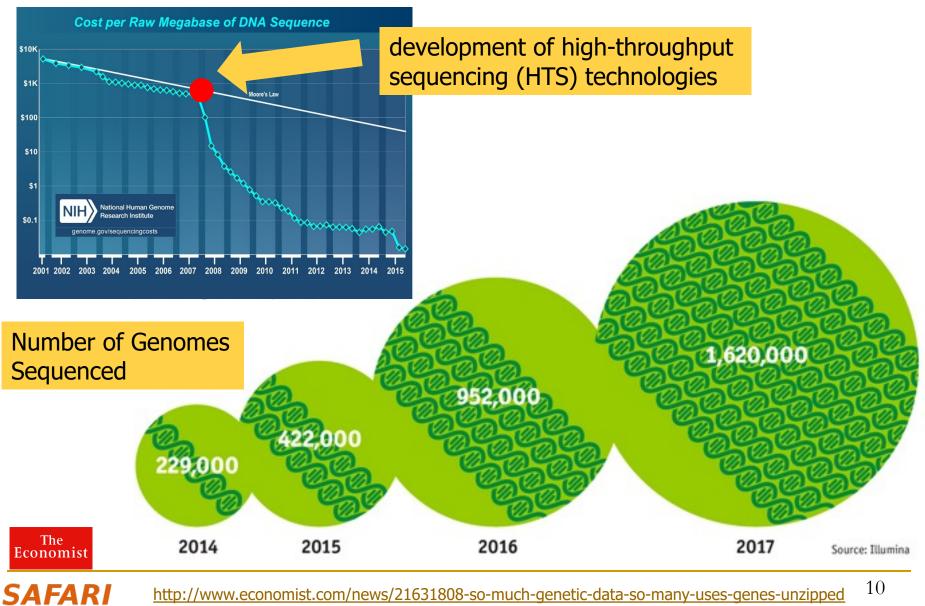

10 http://www.economist.com/news/21631808-so-much-genetic-data-so-many-uses-genes-unzipped

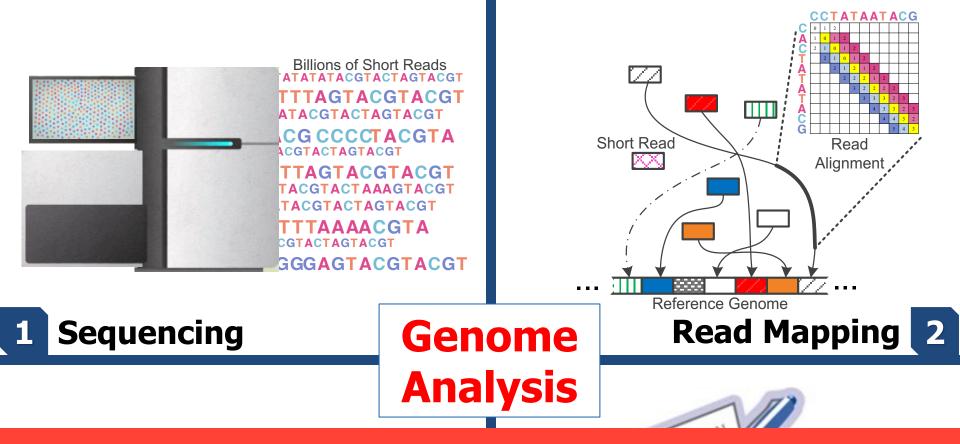

## Data → performance & energy bottleneck

| reau4: | COCITCCAT |

|--------|-----------|

| read5: | CCATGACGC |

| read6: | TTCCATGAC |

### 3 Variant Calling

### **Scientific Discovery 4**

Nanopore sequencing technology and tools for genome assembly: computational analysis of the current state, bottlenecks and future directions

Damla Senol Cali 🖾, Jeremie S Kim, Saugata Ghose, Can Alkan, Onur Mutlu

Briefings in Bioinformatics, bby017, https://doi.org/10.1093/bib/bby017Published:02 April 2018Article history ▼

**Oxford Nanopore MinION**

# Data → performance & energy bottleneck

# Data Overwhelms Modern Machines ...

Storage/memory capability

Communication capability

Computation capability

Greatly impacts robustness, energy, performance, cost

# Data Overwhelms Modern Machines

# Data → performance & energy bottleneck

**Google's video codec**

### Data Movement Overwhelms Modern Machines

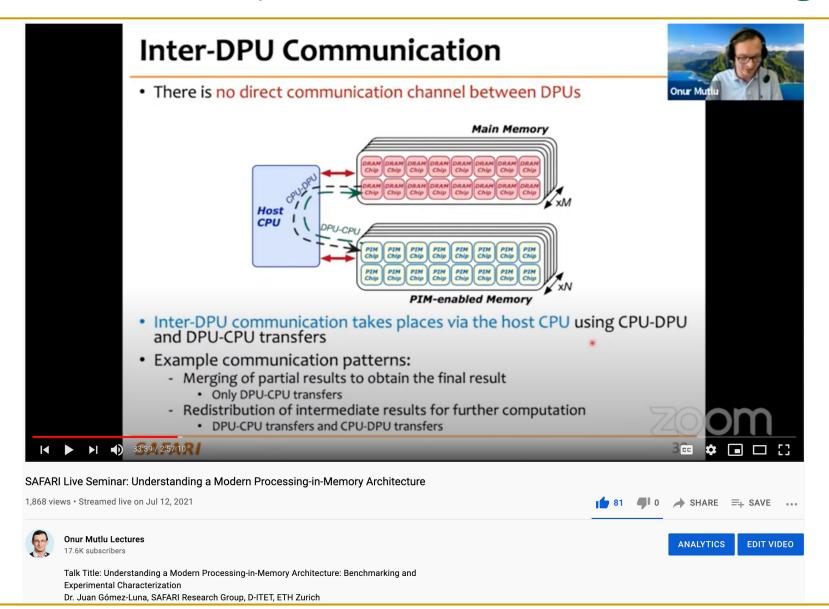

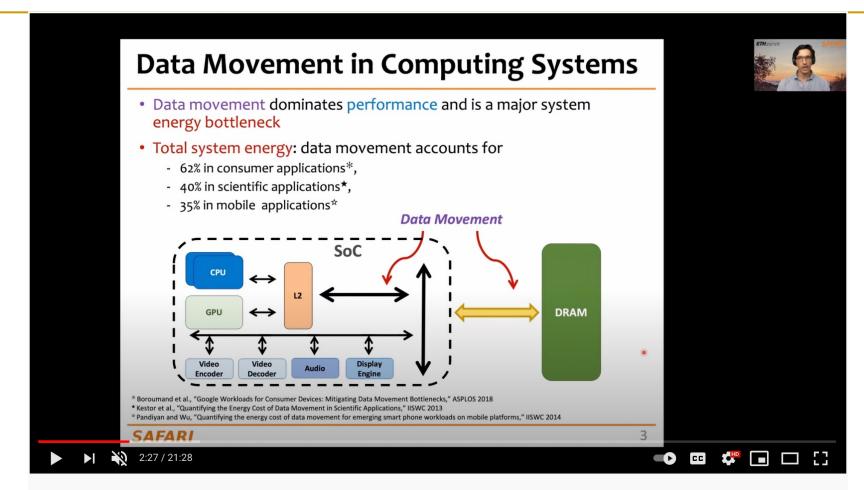

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the <u>23rd International Conference on Architectural Support for Programming</u> <u>Languages and Operating Systems</u> (ASPLOS), Williamsburg, VA, USA, March 2018.

# 62.7% of the total system energy is spent on data movement

## Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup>Saugata Ghose<sup>1</sup>Youngsok Kim<sup>2</sup>Rachata Ausavarungnirun<sup>1</sup>Eric Shiu<sup>3</sup>Rahul Thakur<sup>3</sup>Daehyun Kim<sup>4,3</sup>Aki Kuusela<sup>3</sup>Allan Knies<sup>3</sup>Parthasarathy Ranganathan<sup>3</sup>Onur Mutlu<sup>5,1</sup>15

# An Intelligent Architecture Handles Data Well

### **Ensure data does not overwhelm** the components

- via intelligent algorithms

- via intelligent architectures

- via whole system designs: algorithm-architecture-devices

# Take advantage of vast amounts of data and metadata to improve architectural & system-level decisions

### Understand and exploit properties of (different) data

to improve algorithms & architectures in various metrics

# Corollaries: Computing Systems Today ...

Are processor-centric vs. data-centric

Make designer-dictated decisions vs. data-driven

Make component-based myopic decisions vs. data-aware

# Architectures for Intelligent Machines

# **Data-centric**

# **Data-driven**

# **Data-aware**

### A Blueprint for Fundamentally Better Architectures

# Onur Mutlu, <u>"Intelligent Architectures for Intelligent Computing Systems"</u> Invited Paper in Proceedings of the <u>Design, Automation, and Test in</u> <u>Europe Conference</u> (**DATE**), Virtual, February 2021. [Slides (pptx) (pdf)] [IEDM Tutorial Slides (pptx) (pdf)] [Short DATE Talk Video (11 minutes)] [Longer IEDM Tutorial Video (1 hr 51 minutes)]

### Intelligent Architectures for Intelligent Computing Systems

Onur Mutlu ETH Zurich omutlu@gmail.com

Problem and Background

Task Overview

Technical Challenges, Goals and Ideas

Ideas, Results and Papers from the Past Year

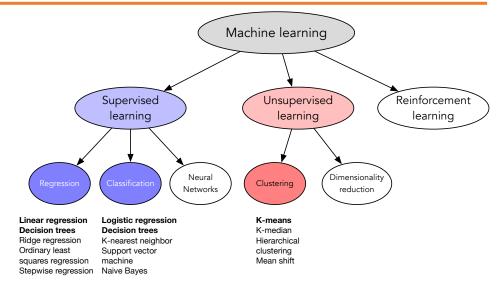

# In This Task... (Task #2946.001)

- We focus on designing memory systems to handle data well

- We aim to solve two different yet related and synergistic problems, both focusing on ML/AI and memory system design

- We explore (and exploit the synergy between)

- Memory system design for AI/ML workloads/accelerators

- AI/ML techniques for improving memory system designs

- Task Name: Memory System Design for AI/ML Accelerators & ML/AI Techniques for Memory System Design

# Our Goals in This Task

Two Major Goals:

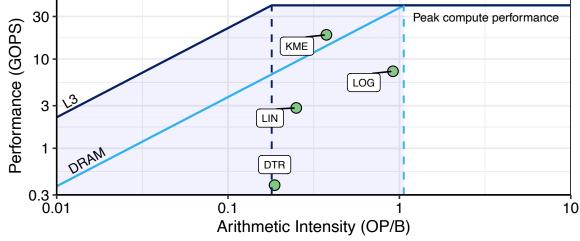

1 Memory system design for AI/ML workloads/accelerators

$\rightarrow$  in-depth exploration of memory system designs for cuttingedge and emerging machine learning accelerators

$\rightarrow$  more efficient on-chip and off-chip memory systems

2. AI/ML techniques for improving memory system designs

$\rightarrow$  take a comprehensive look at memory system design and make it data driven, i.e., based on machine learning

→ more effective cache/memory/prefetch/thread controllers and data/resource management/mapping/scheduling policies

# Anticipated Primary Results

Realistic, practical and effective novel memory system designs for ML/AI accelerators

New ML-based techniques to improve memory system efficiency and performance

Open-source workloads, metrics, methodologies & infrastructures to analyze such designs and techniques.

# Task Description

#### Description

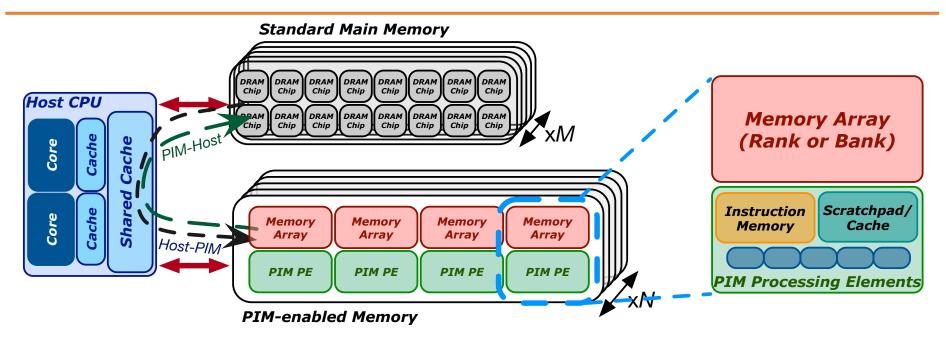

Our major goals in this research are twofold. First, we aim to provide the first in-depth exploration of memory system designs for cutting-edge and emerging machine learning accelerators. To this end, we aim to develop much more efficient on-chip/on-die as well as off-chip memory system designs for such accelerators, along with open source models, metrics, simulators, prototypes & workload suites to evaluate existing and future ML/AI accelerators. Second, we would like to take a comprehensive look at memory system design and make it data driven, i.e., based on machine learning: we aim to design ML/AI techniques for on-chip cache/memory/prefetch/thread controllers and data/resource management/mapping/scheduling policies, to maximize efficiency, performance and QoS beyond levels that can be achievable by human-designed policies.

To this end, we will comprehensively examine a wide variety of key issues and bottlenecks in the entire memory system designs of modern ML/AI accelerators as well as general purpose processors, ranging from issues in SRAM buffers/caches, DRAM main memory, cache and memory controllers, interconnects, non-volatile memory, hybrid memories, prefetching mechanisms, and near-data acceleration mechanisms, with a special focus on cutting-edge data-intensive production ML/AI workloads (for Problem 1) and with a broader focus on key data-intensive workloads (for Problem 2).

To solve Problem 1, based on our analysis of bottlenecks in state-of-the-art ML/AI accelerators and workloads, we aim to develop new on-chip and off-chip memory designs, data organization techniques, data movement reduction mechanisms, request scheduling, caching, prefetching schemes, near-data and in-memory acceleration mechanisms, customized SRAM, DRAM, NVM designs for demands of ML/AI acceleration, and various other innovative techniques across the entire memory hierarchy. To solve Problem 2, based on our analysis of each controller and major policy in the memory hierarchy, we aim to find and design new ML-based policies that are best fit for each controller and its optimization goals.

# Task Deliverables (2020)

#### **Deliverables**

Report on experimental performance and energy analysis & breakdown of ML/AI accelerator execution on key ML/AI workloads using rigorous evaluation metrics and methodologies

Original due date: 30-Jun-2020

Annual review presentation

```

Revised due date: 9-Sep-2020 (Original Due Date: 1-Sep-2020)

```

Report on description and analysis of new customized memory system designs for ML accelerators & complete ML accelerator designs with new data orchestration and memory management mechanisms

Original due date: 31-Dec-2020

# Task Deliverables (2021)

Report on performance and energy analysis of control and management policies in the memory hierarchy & potential of machine learning based techniques to replace them

Original due date: 28-Feb-2021

Report on description and analysis of new ML-based memory system policies and designs & specification and coordination of various on-chip ML-based agents

Original due date: 31-Aug-2021

Annual review presentation

Original due date: 1-Sep-2021

Report on analysis of various different memory types, new on-chip/off-chip near-data processing designs, and shortterm & long-term options for near-data processing designs for ML/AI accelerators

Original due date: 31-Dec-2021

# Task Deliverables (2022)

Report analyzing various new ML-based memory/cache/interconnect/prefetcher control mechanisms along with MLbased data mapping, address mapping, thread scheduling policies across the memory system

Original due date: 30-Jun-2022

Report on open source release of new ML/AI accelerator simulation infrastructures, their evaluation metrics and methodologies, and their analysis

Original due date: 31-Oct-2022

Report on open source release of ML/AI-based memory system evaluation infrastructures their evaluation metrics and methodologies, and their analysis

Original due date: 31-Oct-2022

Final report summarizing research accomplishments and future direction

Original due date: 31-Dec-2022

# Task Information #2946.001 (1)

- Thrust: AI Hardware

- Task Leader: Onur Mutlu

- <u>https://people.inf.ethz.ch/omutlu/</u>

- onur.mutlu@inf.ethz.ch

- Students

- Rahul Bera (ETH)

- Joao Ferreira (ETH)

- Geraldo Francisco de Oliveira Junior (ETH)

- Konstantinos Kanellopoulos (ETH)

- Joel Lindegger (ETH)

- Aditya Manglik (ETH)

- Rakesh Nadig (ETH)

# Task Information #2946.001 (2)

- Senior Researchers

- Juan Gomez Luna (ETH)

- Haiyu Mao (ETH)

- Lois Orosa (ETH)

- Jisung Park (ETH)

- Gagandeep Singh (ETH)

More students/postdocs to be added as the task evolves

# Recent PhD Graduate

Minesh Patel

SAFAR

- October 2021

- Enabling Effective Error Mitigation in Memory Chips That Use On-Die Error-Correcting Codes

- **2022 William C. Carter PhD Dissertation Award in Dependability**

- Best Paper Awards at DSN 2019 & MICRO 2020

- https://www.youtube.com/watch?v=0c9bDr18jZE

- https://arxiv.org/abs/2204.10387

- <u>https://www.mineshp.com/</u>

### **Dissertation Overview**

#### **"Enabling Effective Error Mitigation in Modern Memory Chips that Use On-Die ECC"** Defended Oct. 2021 (ETH Zürich)

Deposited Apr. 2022 (DOI 10.3929/ethz-b-000542542)

#### Advisor:

Onur Mutlu (ETH Zürich) Co-Examiners: Mattan Erez (UT Austin) Moinuddin Qureshi (Georgia Tech) Vilas Sridharan (AMD) Christian Weis (TU Kaiserslautern)

Award Speech - William C. Carter PhD Dissertation Award in Dependability - Minesh Patel

402 views · Premiered Jul 15, 2022

i 21  $\bigcirc$  Dislike → Share  $\downarrow$  Download % CLIP =+ Save ...

ANALYTICS EDIT VIDEO

# Recent PostDoc Alumni

### Dr. Lois Orosa

- March 2022

- Director at the Galician Supercomputing Center

### Dr. Gagandeep Singh

- September 2022

- Joining AMD Research

### Dr. Jisung Park

- September 2022

- Joining POSTECH (South Korea) as Assistant Professor

# Soon to Finish PhD

- Hasan Hassan

- PhD Defense date: September 29, 2022

- Improving DRAM Performance, Reliability, and Security by Rigorously Understanding Intrinsic DRAM Operation

- <u>https://drive.google.com/file/d/1E5mFYI\_SMjCP-</u> <u>7TQ8qt6kRALROGhZs9K/view</u>

# Recent Internships

- Dr. Gagandeep Singh

- February-June 2022

- Visit to AMD Research

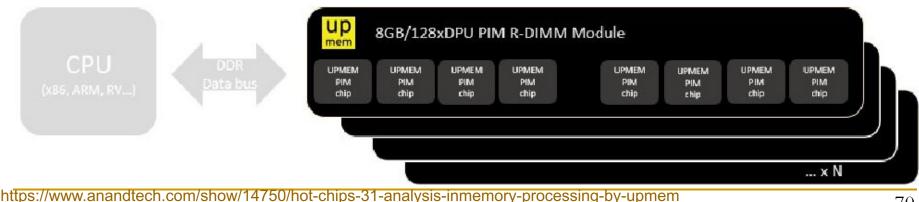

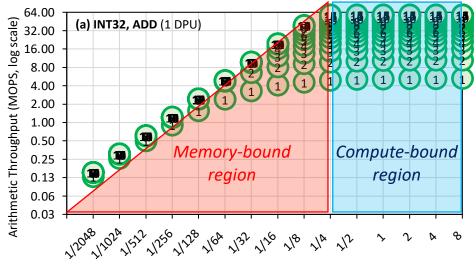

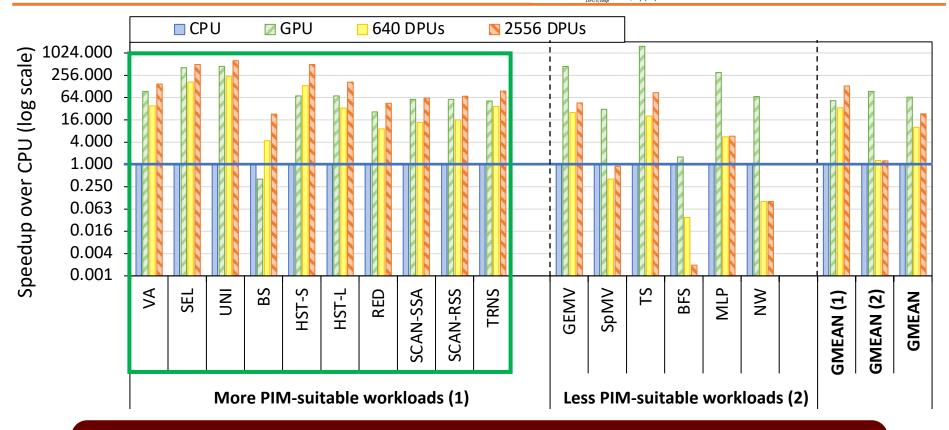

# Upcoming TECHCON Presentation

### Dr. Juan Gomez-Luna

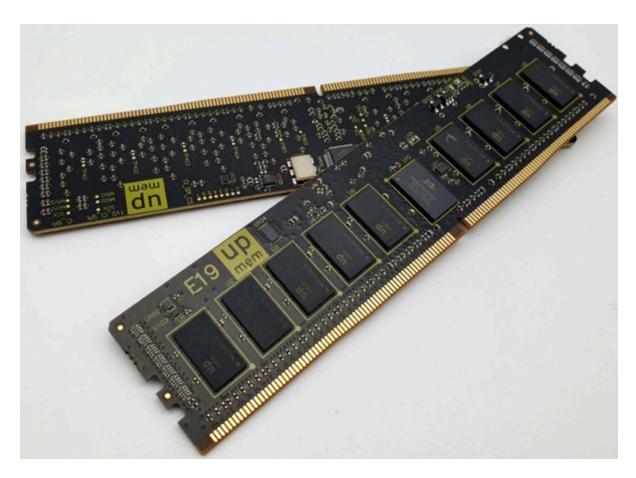

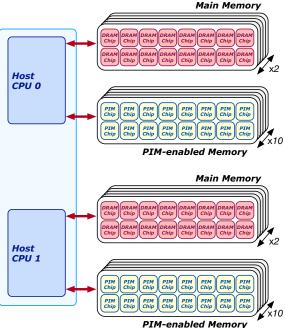

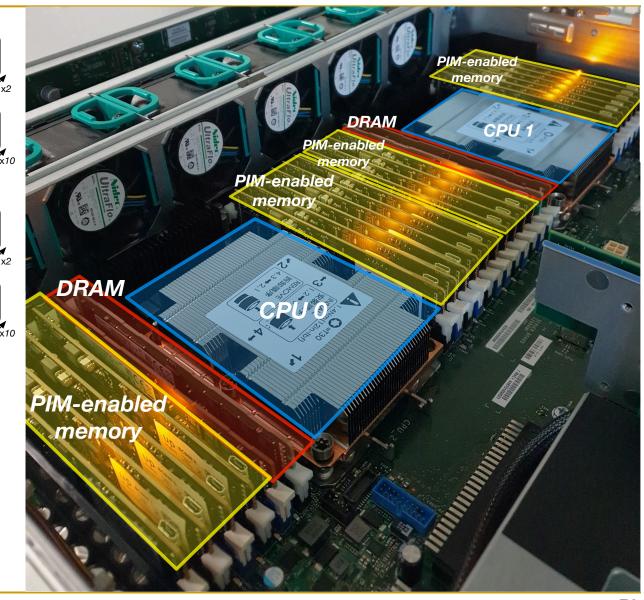

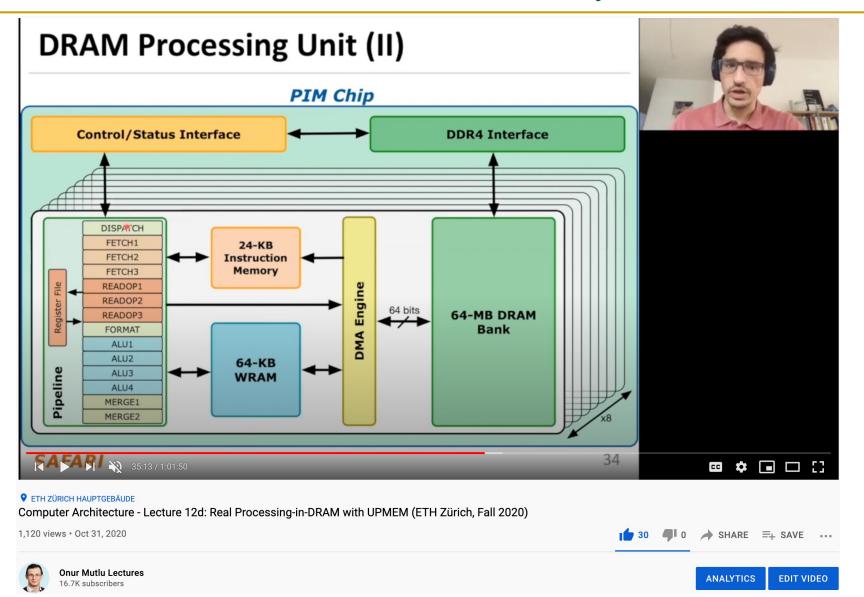

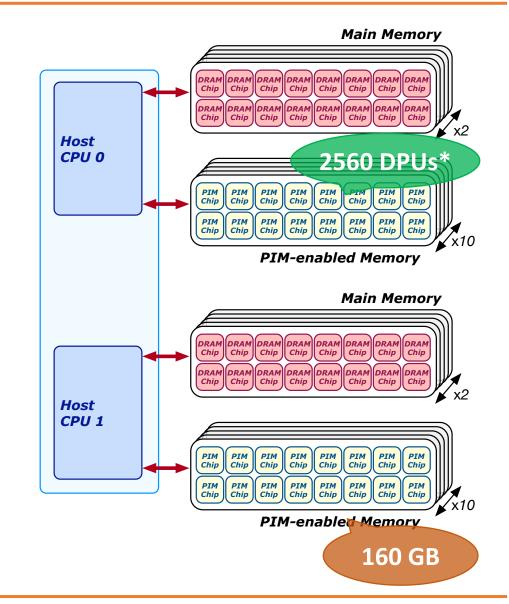

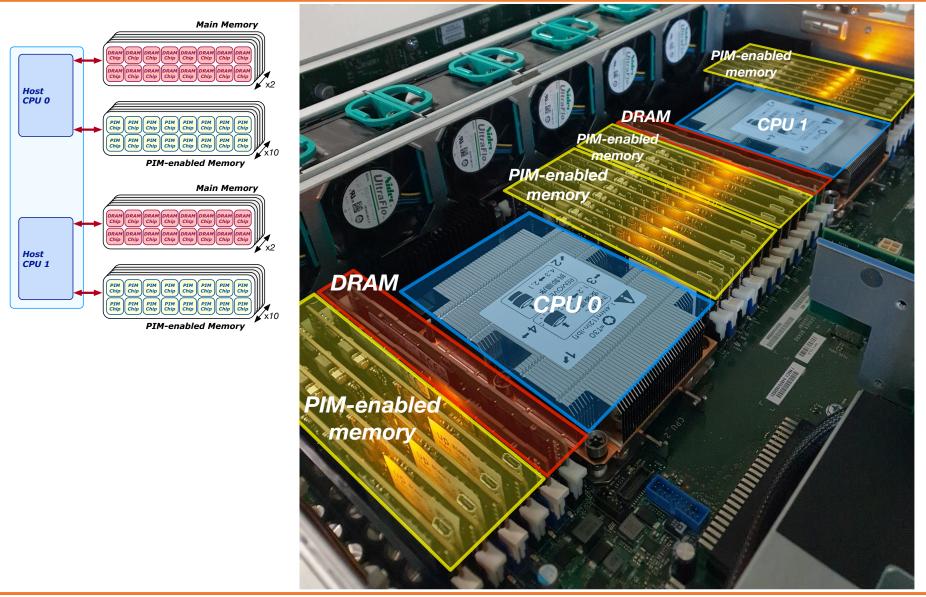

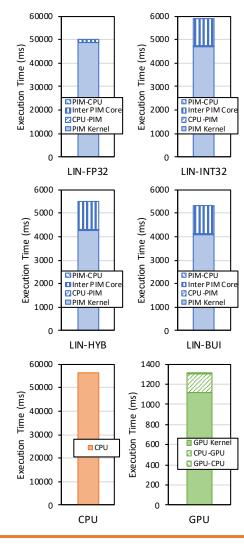

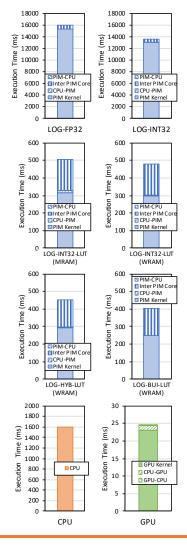

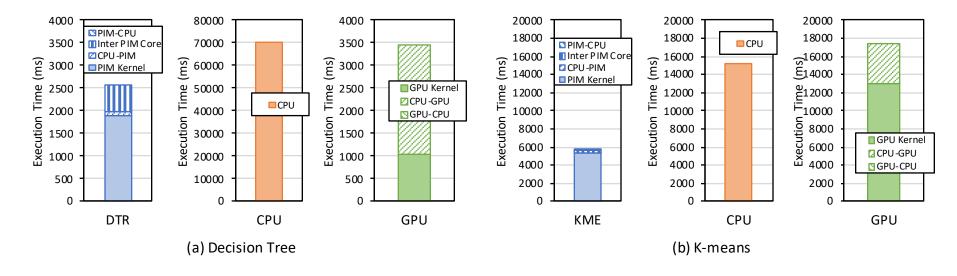

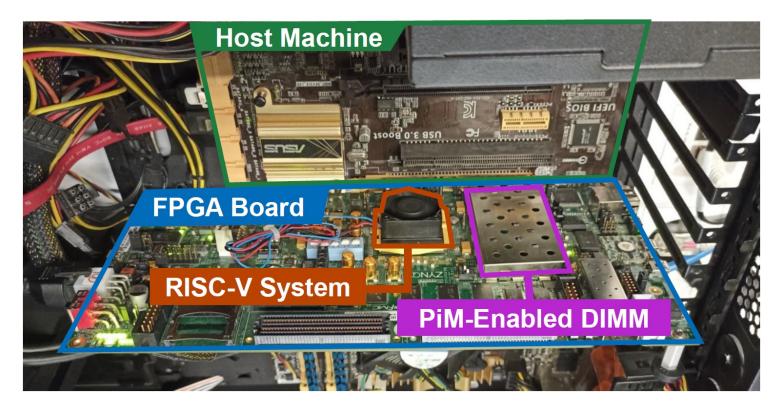

- Benchmarking Memory-Centric Computing Systems: Analysis of Real Processing-in-Memory Hardware

- Based on two major works

- https://arxiv.org/pdf/2105.03814.pdf

- https://arxiv.org/pdf/2207.07886.pdf

### Benchmarking Memory-Centric Computing Systems: Analysis of Real Processing-In-Memory Hardware

Year: 2021, Pages: 1-7 DOI Bookmark: 10.1109/IGSC54211.2021.9651614

#### Authors

SAFARI

Juan Gómez-Luna, ETH Zürich Izzat El Hajj, American University of Beirut Ivan Fernandez, University of Malaga Christina Giannoula, National Technical University of Athens Geraldo F. Oliveira, ETH Zürich Onur Mutlu, ETH Zürich

https://www.youtube.com/watch?v=nphV36SrysA

# Industry Liaisons

- Charles Augustine, Intel

- Pradip Bose, IBM

- Alper Buyuktosunoglu, IBM

- Rosario Cammarota, Intel

- Ramesh Chauhan, Qualcomm

- Prokash Ghosh, NXP

- Jose Joao, ARM

- Arun Joseph, IBM

- Preetham Lobo, IBM

- Nithyakalyani Sampath, TI

- Willem Sanberg, NXP

- Pushkar Sareen, NXP

- Sreenivas Subramoney, Intel

- Xin Zhang, IBM

- We are having and will have regular and irregular meetings with all liaison companies

- Very open to other collaborators, feedback, internships, visits

## Industry Interactions (This Year I)

- Intel: Collaborative papers with as part of this task

- Sreenivas Subramoney, Gurpreet Kalsi, Anant Nori, Kamlesh Pillai, Shankar Balachandran, Bharathwaj Suresh

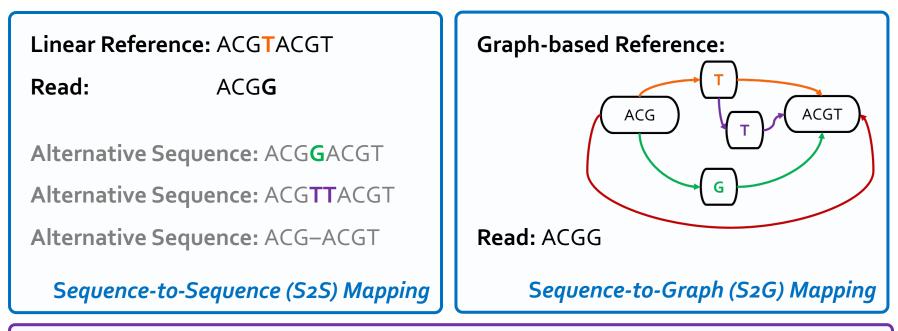

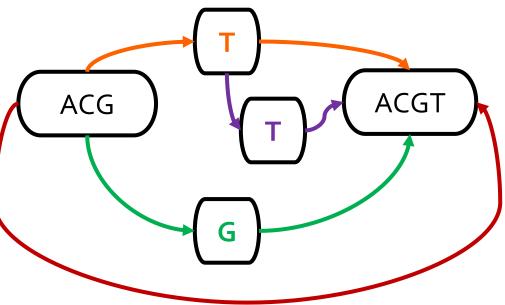

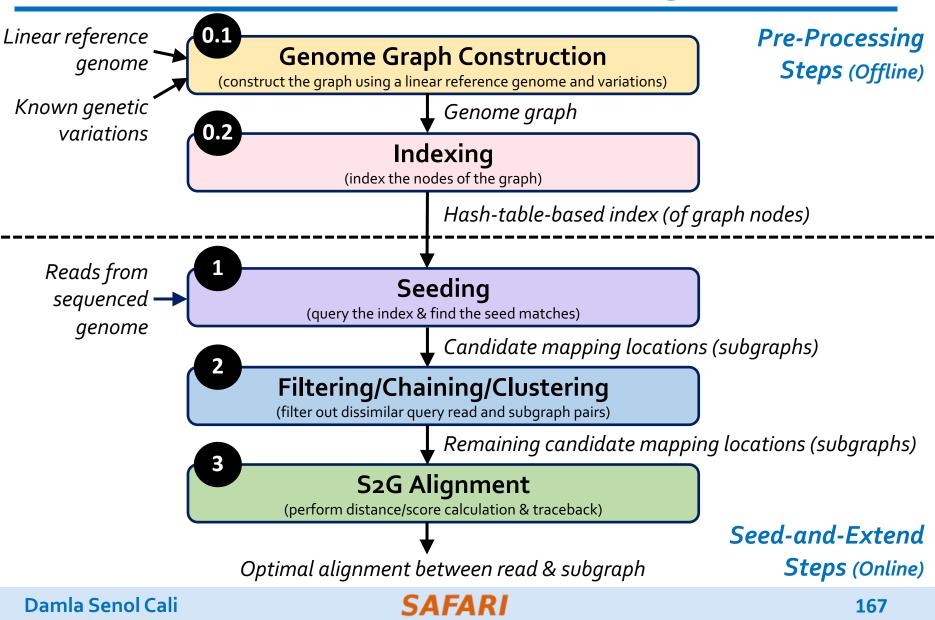

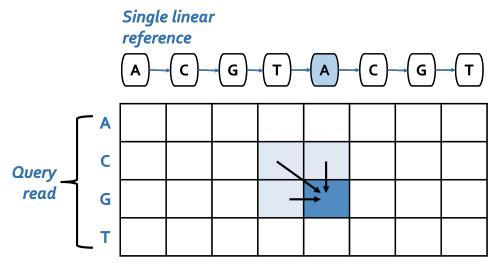

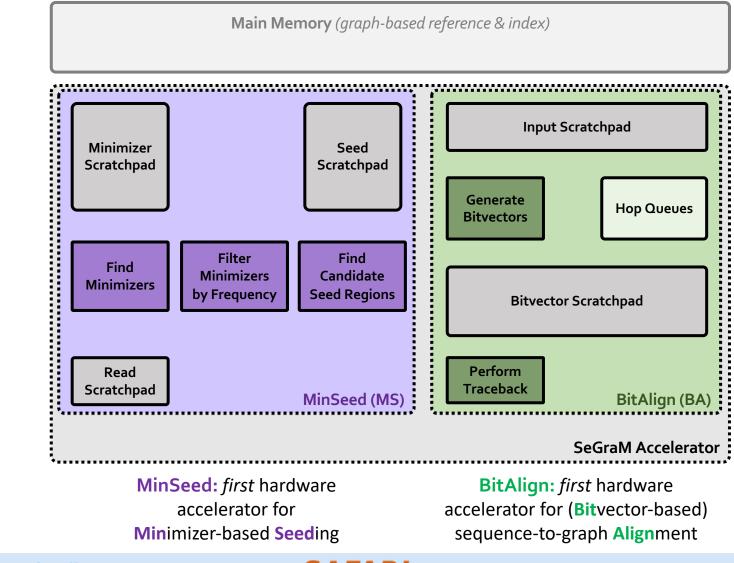

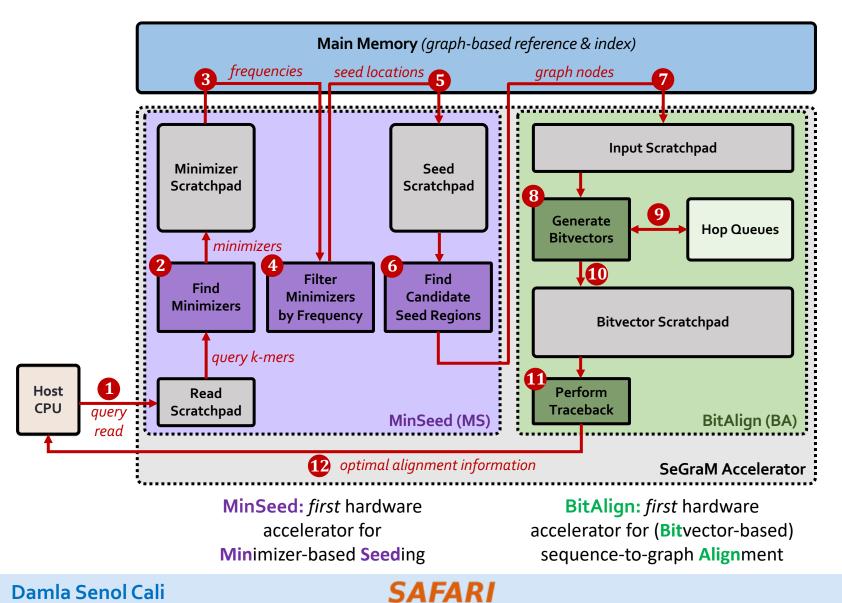

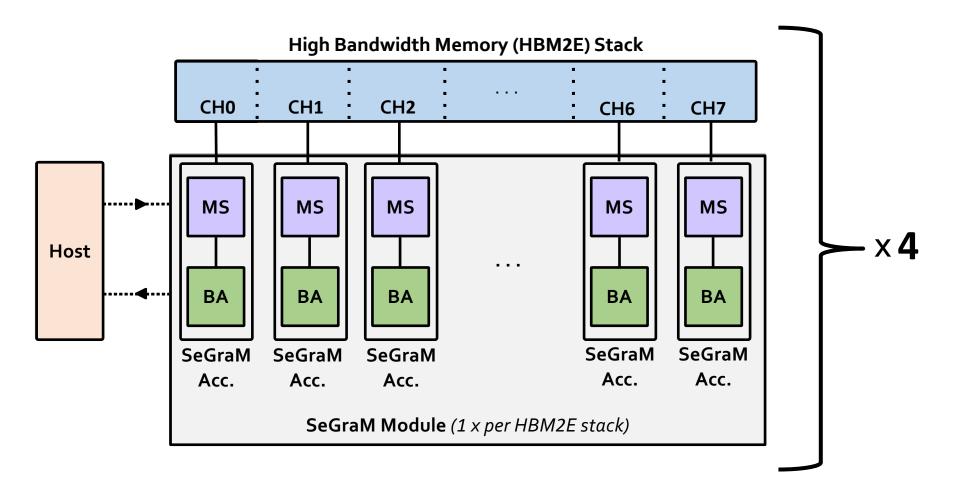

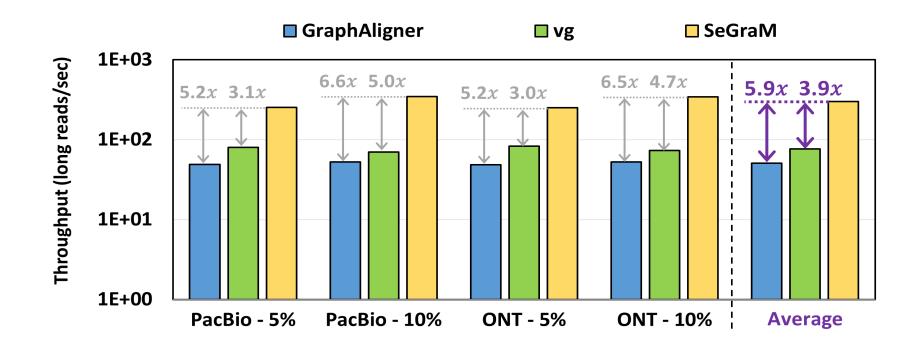

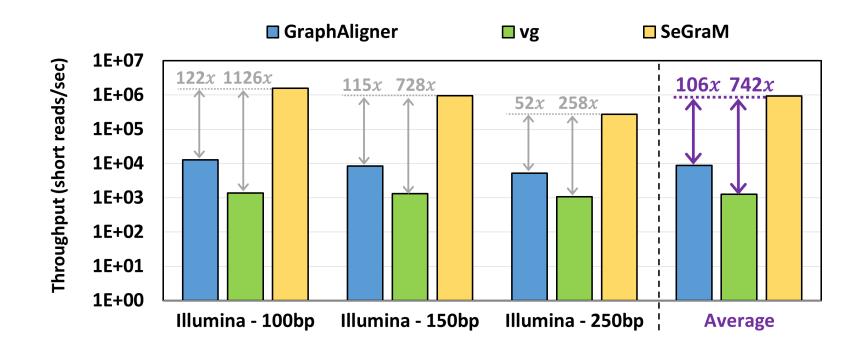

- SeGraM: A Universal Hardware Accelerator for Genomic Sequence-to-Graph and Sequence-to-Sequence Mapping [ISCA 2022]

- pLUTo: Enabling Massively Parallel Computation In DRAM via Lookup Tables [MICRO 2022]

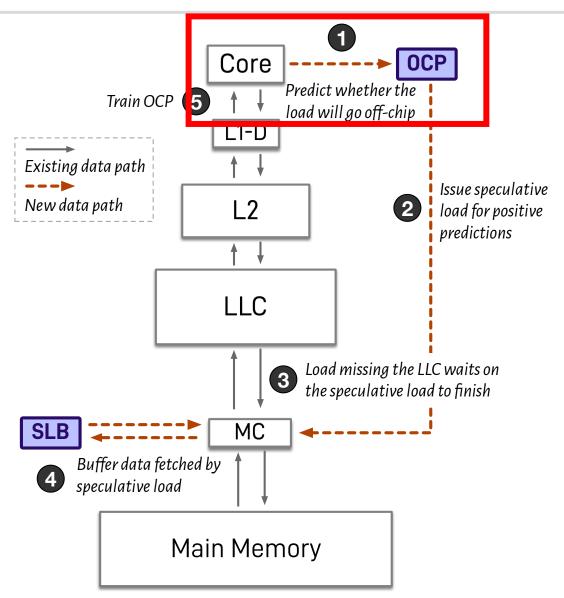

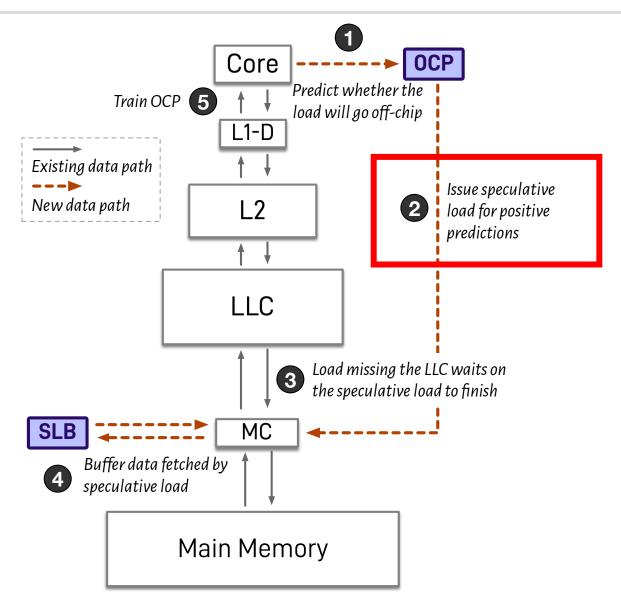

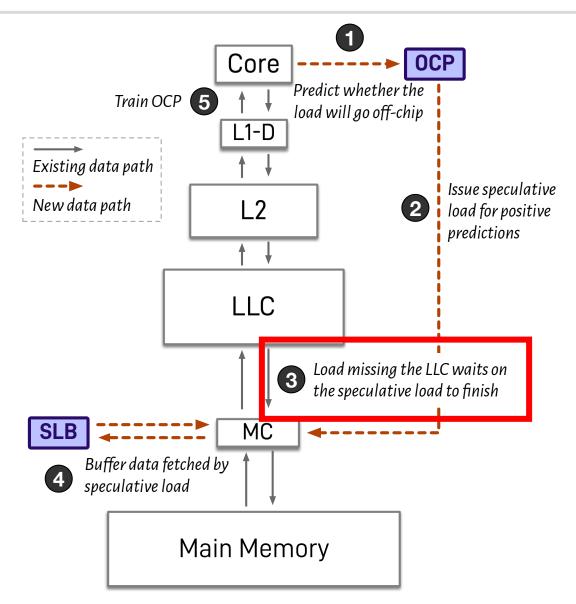

- Hermes: Accelerating Long-Latency Load Requests via Perceptron-Based Off-Chip Load Prediction [MICRO 2022]

- ApHMM: Accelerating Profile Hidden Markov Models for Fast and Energy-Efficient Genome Analysis [arXiv 2022]

- IBM: Collaborative papers

- Dionysios Diamantopoulos, Christoph Hagleitner

- Accelerating Weather Prediction Using Near-Memory Reconfigurable Fabric [TRETS 2022]

## Industry Interactions (This Year II)

- IBM: Collaborative EU Horizon Project BioPIM

- Abu Sebastian, Irem Boybat (IBM Research Zurich)

- <u>http://www.biopim.eu/</u>

- BioPIM project aims to leverage the emerging processing-in-memory (PIM) technologies to enable powerful edge computing.

- Synergistic with this task

- We will focus on co-designing algorithms and data structures commonly used in bioinformatics together with several types of PIM architectures to obtain the highest benefit in cost, energy, and time savings.

- BioPIM will also impact other fields that employ similar algorithms.

- Our designs and algorithms will not be limited to cheap hardware, and they will impact computation efficiency on all forms of computing environments including cloud platforms.

- The targeted breakthrough of **BioPIM** is to invent and leverage in-memory computing architectures to fundamentally improve the performance and energy efficiency of various important bioinformatics algorithms to make mobile genomics a reality

BOPIM

## Industry Interactions (This Year III)

- Qualcomm: In-person Visit & Talk

- Ramesh Chauhan

- May 2022

- IBM Research: In-person Visit & Talk

- Pradip Bose, Karthik Swaminathan, Alper Buyuktosunoglu, Krishnan Kailas

- May 2022

- Intel: Keynote Talk at the Intel Interconnect & Connectivity Summit

- Debendra Das Sharma

- <u>"Memory-Centric Computing"</u>

*Keynote Talk at the Intel Interconnect & Connectivity Summit (IICS)*, Virtual, 9 February 2022. [<u>Slides (pptx) (pdf)</u>]

## Posters for Annual Review 2022

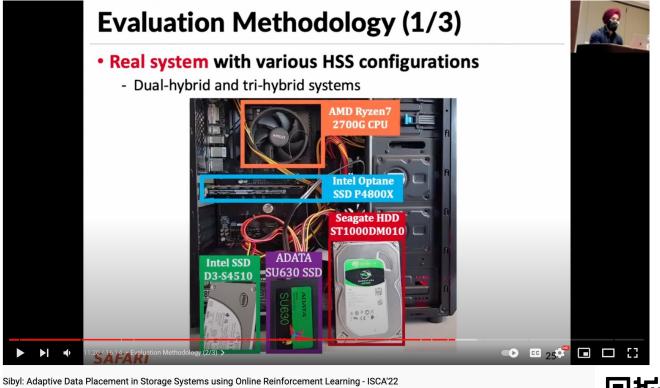

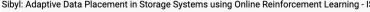

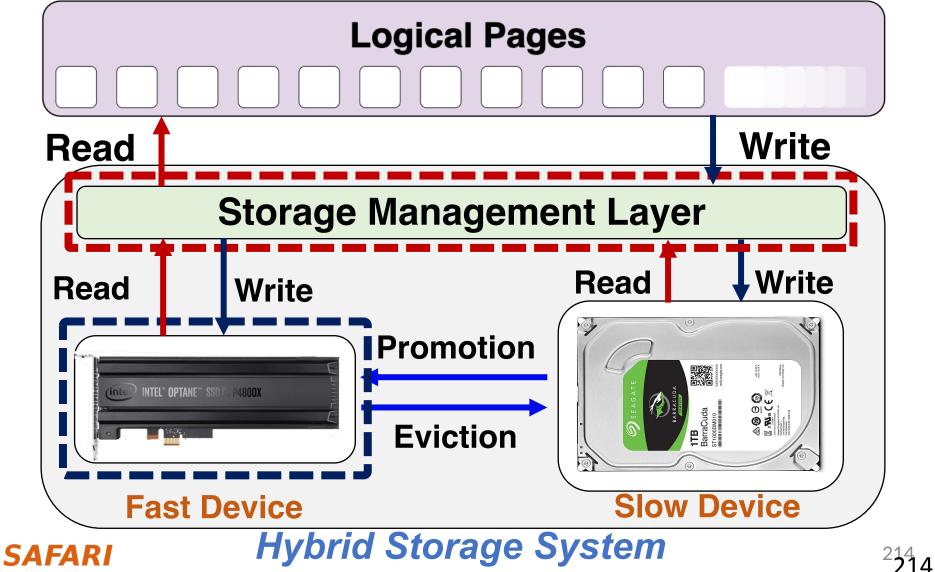

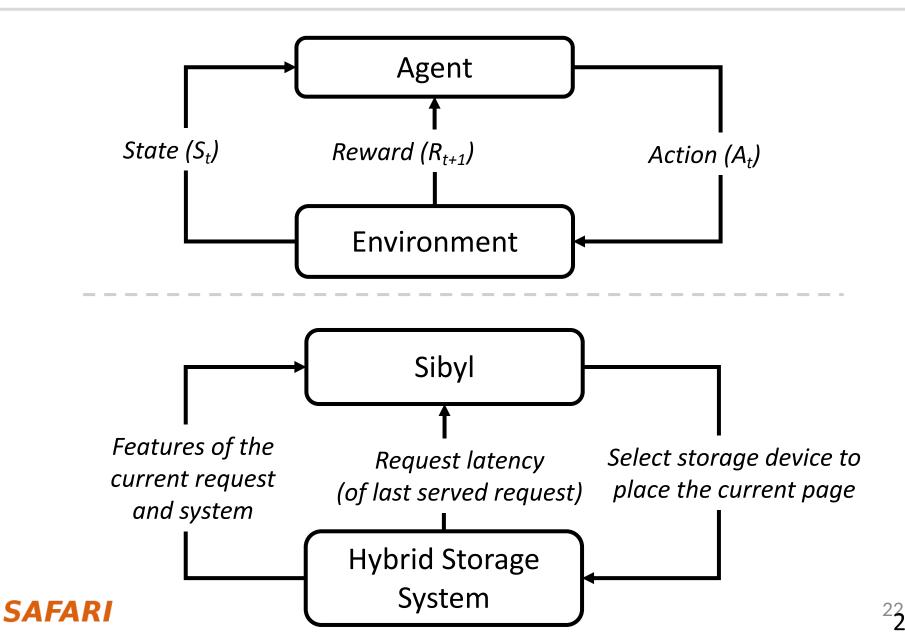

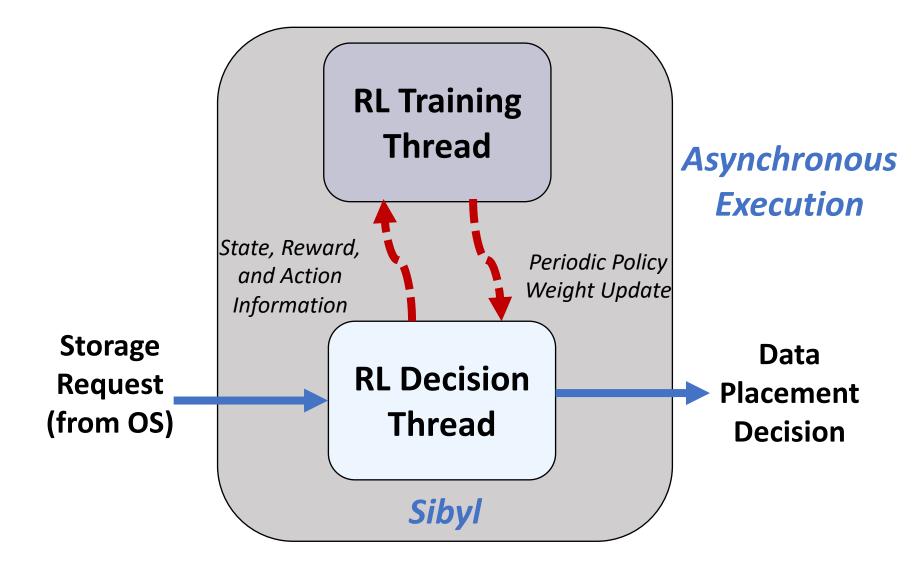

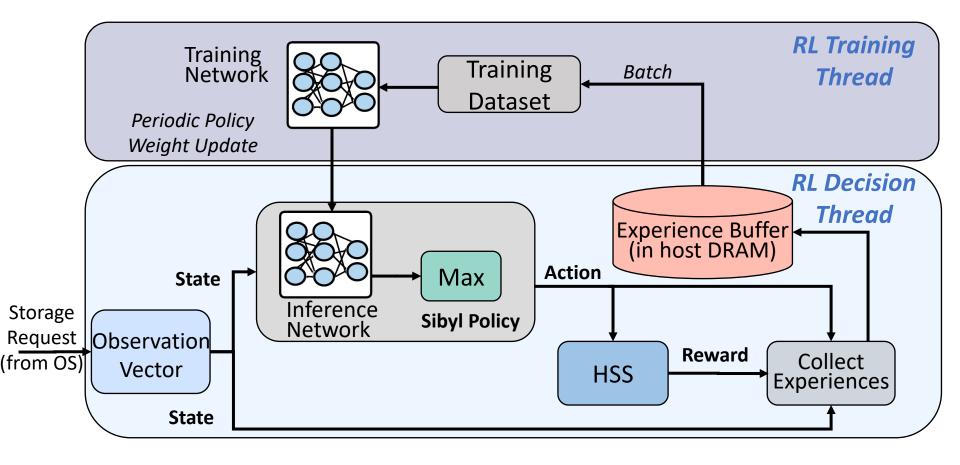

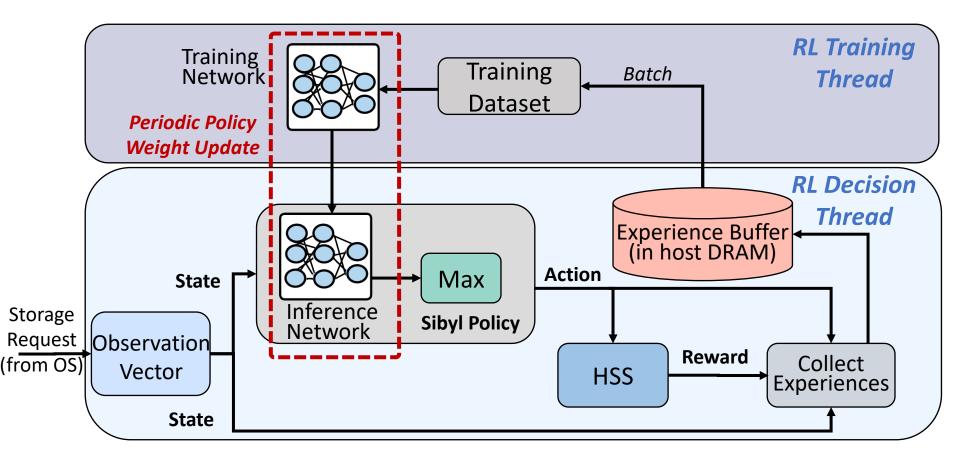

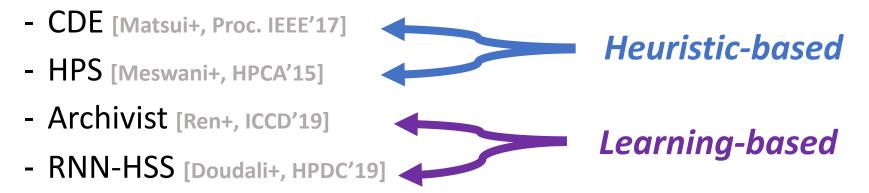

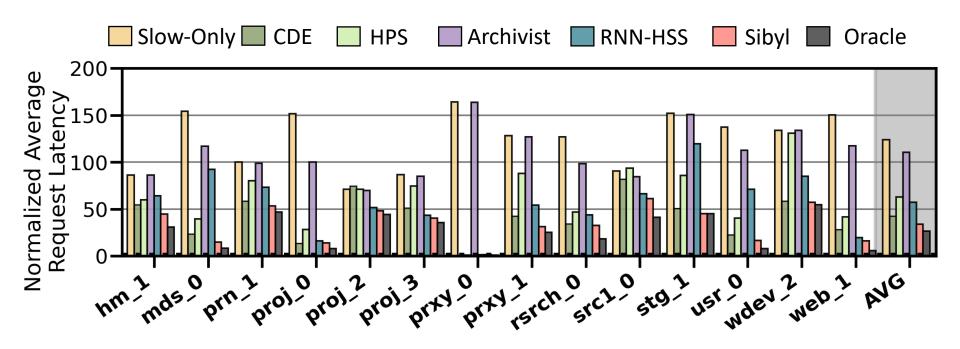

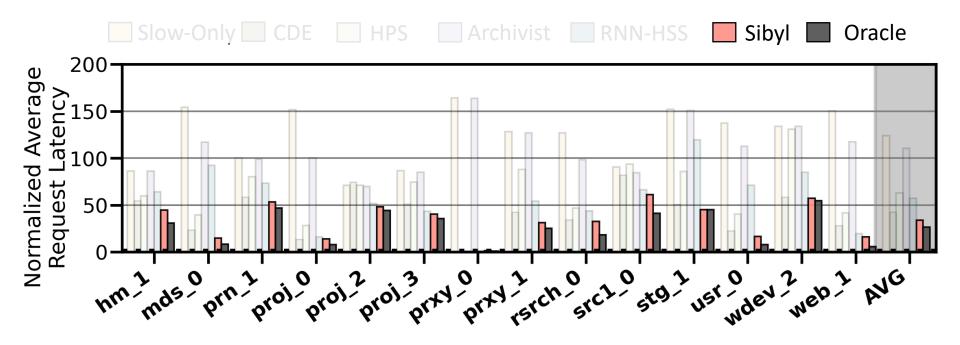

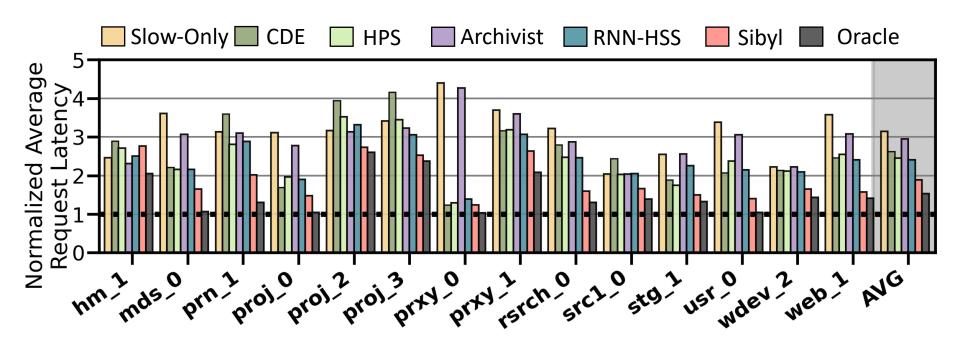

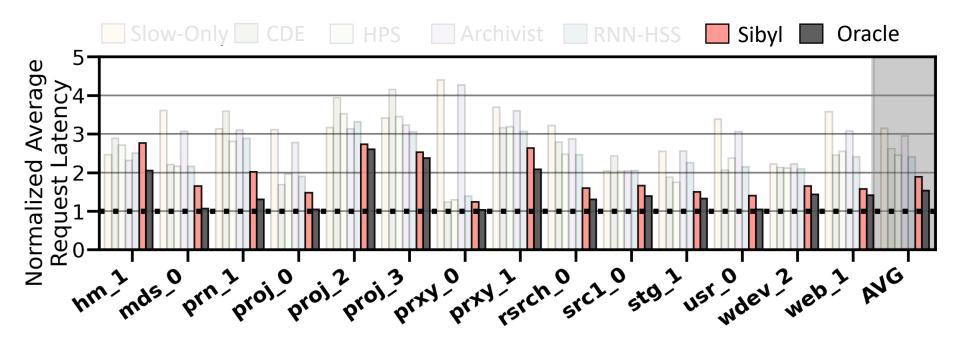

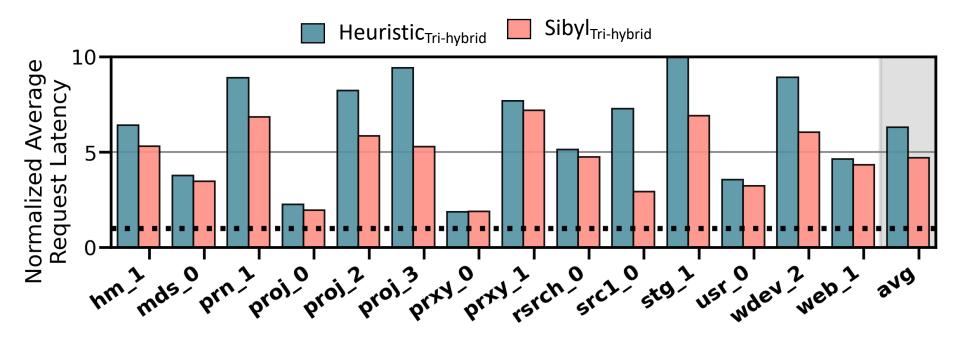

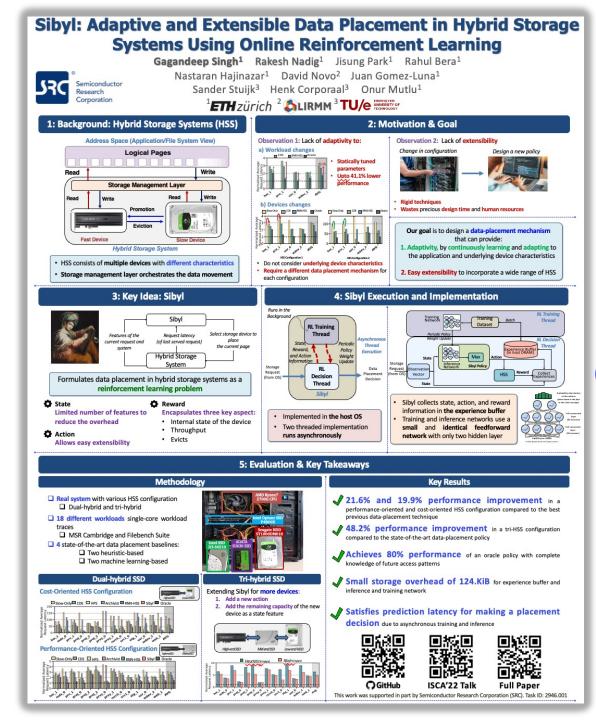

- Sibyl: Adaptive and Extensible Data Placement in Hybrid Storage Systems Using Online Reinforcement Learning [ISCA 2022]

- Gagandeep Singh

- SeGraM: A Universal Hardware Accelerator for Genomic Sequence-to-Graph and Sequence-to-Sequence Mapping [ISCA 2022]

- Damla Senol Cali, Joel Lindegger

- Hermes: Accelerating Long-Latency Load Requests via Perceptron-Based Off-Chip Load Prediction [MICRO 2022]

- Rahul Bera

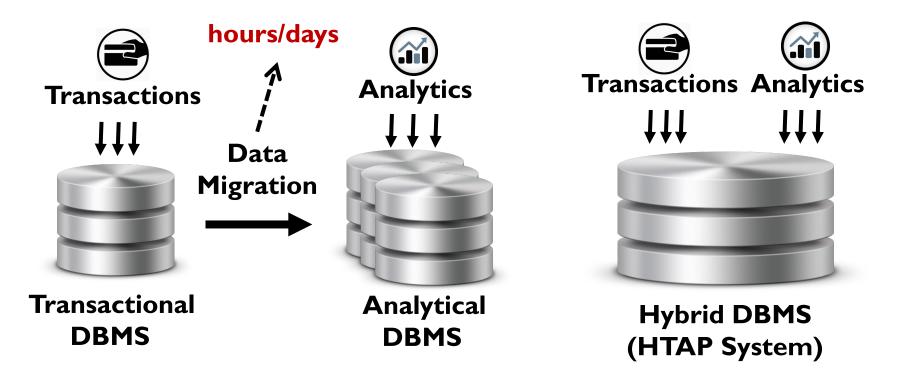

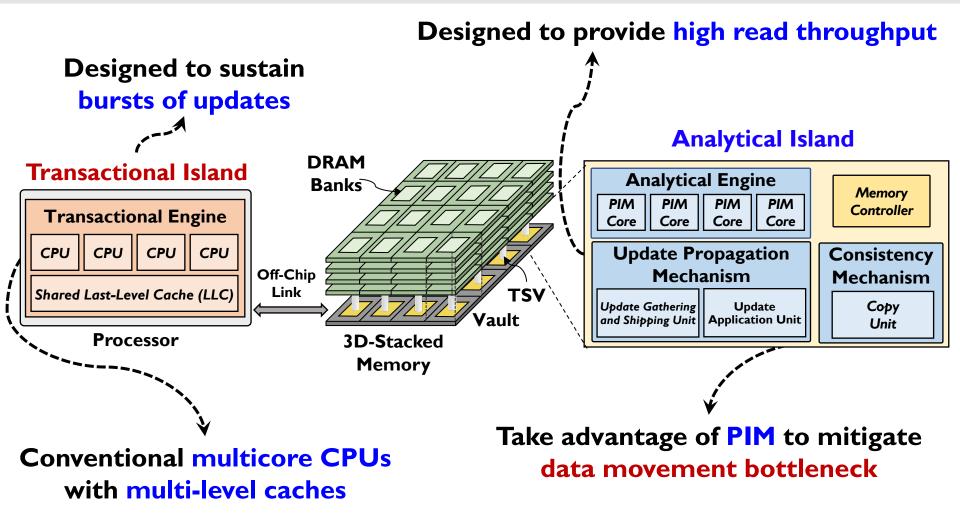

- Polynesia: Enabling High-Performance and Energy-Efficient Hybrid Transactional/Analytical Databases with Hardware/Software Co-Design [ICDE 2022]

- Geraldo Francisco de Oliveira Junior

- Benchmarking Memory-Centric Computing Systems: Analysis of Real Processing-in-Memory Hardware [IEEE Access 2022]

- Juan Gómez-Luna

- Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks [PACT 2021]

- Geraldo Francisco de Oliveira Junior

## Special Research Sessions & Courses

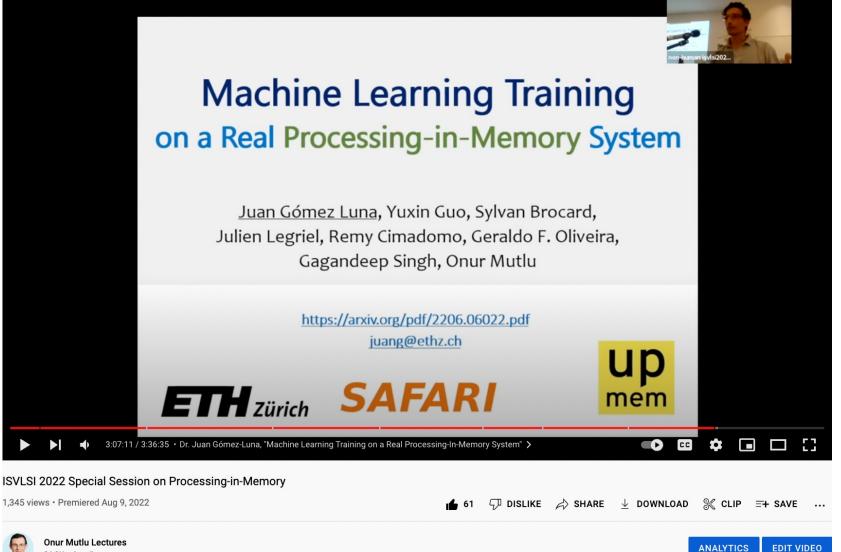

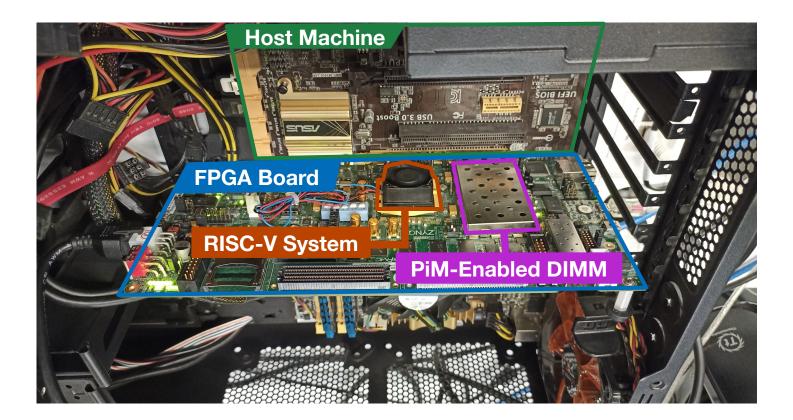

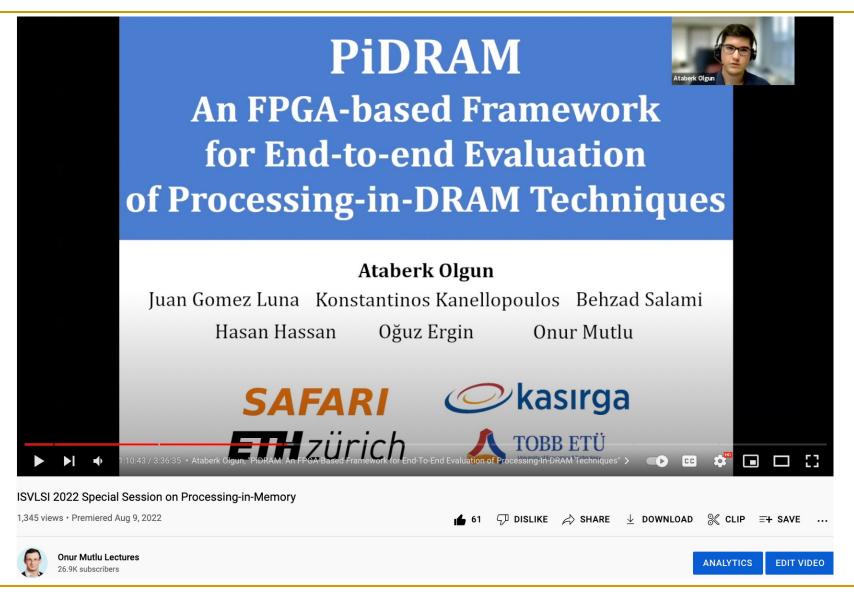

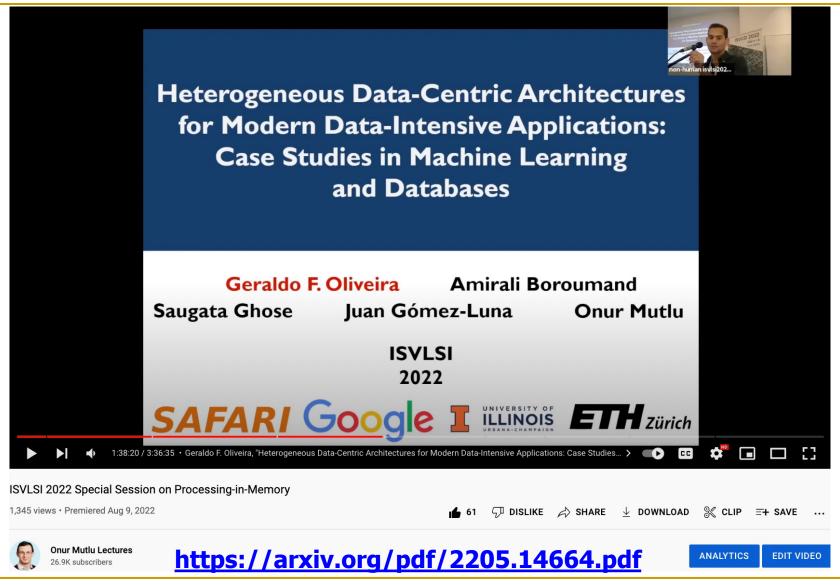

### Special Session at ISVLSI 2022: 9 cutting-edge talks

SAFAR

https://www.youtube.com/watch?v=geukNs5XI3g

41

## Comp Arch (Fall'21)

#### Fall 2021 Edition:

- https://safari.ethz.ch/architecture/fall2021/doku. php?id=schedule

- Fall 2020 Edition:

- https://safari.ethz.ch/architecture/fall2020/doku. php?id=schedule

### Youtube Livestream (2021):

- https://www.youtube.com/watch?v=4yfkM\_5EFg o&list=PL5Q2soXY2Zi-Mnk1PxjEIG32HAGILkTOF

- Youtube Livestream (2020):

- https://www.youtube.com/watch?v=c3mPdZA-Fmc&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN

- Master's level course

- Taken by Bachelor's/Masters/PhD students

- Cutting-edge research topics + fundamentals in Computer Architecture

- 5 Simulator-based Lab Assignments

- Potential research exploration

- Many research readings

### https://www.youtube.com/onurmutlulectures

#### Fall 2021 Lectures & Schedule

Watch on 🕞 YouTub

| Week | Date          | Livestream    | Lecture                                                                   | Readings               | Lab          | HW          |

|------|---------------|---------------|---------------------------------------------------------------------------|------------------------|--------------|-------------|

| W1   | 30.09<br>Thu. | You the Live  | L1: Introduction and Basics                                               | Required<br>Mentioned  | Lab 1<br>Out | HW 0<br>Out |

|      | 01.10<br>Fri. | You Tube Live | L2: Trends, Tradeoffs and Design<br>Fundamentals<br>@(PDF) @(PPT)         | Required<br>Mentioned  |              |             |

| W2   | 07.10<br>Thu. | You Tube Live | L3a: Memory Systems: Challenges and<br>Opportunities<br>ma(PDF) and (PPT) | Described<br>Suggested |              | HW 1<br>Out |

|      |               |               | L3b: Course Info & Logistics                                              |                        |              |             |

|      |               |               | L3c: Memory Performance Attacks                                           | Described<br>Suggested |              |             |

|      | 08.10<br>Fri. | You Tube Live | L4a: Memory Performance Attacks                                           | Described<br>Suggested | Lab 2<br>Out |             |

|      |               |               | L4b: Data Retention and Memory Refresh                                    | Described<br>Suggested |              |             |

|      |               |               | L4c: RowHammer<br>(PDF)  (PPT)                                            | Described<br>Suggested |              |             |

## DDCA (Spring 2022)

### Spring 2022 Edition:

https://safari.ethz.ch/digitaltechnik/spring2022/do ku.php?id=schedule

### Spring 2021 Edition:

https://safari.ethz.ch/digitaltechnik/spring2021/do ku.php?id=schedule

### Youtube Livestream (Spring 2022):

https://www.youtube.com/watch?v=cpXdE3HwvK 0&list=PL5Q2soXY2Zi97Ya5DEUpMpO2bbAoaG7c6

### Youtube Livestream (Spring 2021):

- https://www.youtube.com/watch?v=LbC0EZY8yw 4&list=PL5Q2soXY2Zi uej3aY39YB5pfW4SJ7LIN

- Bachelor's course

- 2<sup>nd</sup> semester at ETH Zurich

- Rigorous introduction into "How Computers Work"

- Digital Design/Logic

- Computer Architecture

- 10 FPGA Lab Assignments

### https://www.youtube.com/onurmutlulectures

Digital Design and Computer Architecture -Spring 2021 Search Recent Changes Media Manager Siten

sched

Trace: • schedule

#### Lecture Video Playlist on YouTube

Subject to Livestream Lecture Playlist

#### Spring 2021 Lectures/Schedule

| Week | Date          | Livestream    | Lecture                                                    | Readings                           | Lab | HW |

|------|---------------|---------------|------------------------------------------------------------|------------------------------------|-----|----|

| W1   | 25.02<br>Thu. | You Tube Live | L1: Introduction and Basics                                | Required<br>Suggested<br>Mentioned |     |    |

|      | 26.02<br>Fri. | You Tube Live | L2a: Tradeoffs, Metrics, Mindset                           | Required                           |     |    |

|      |               |               | L2b: Mysteries in Computer Architecture<br>a (PDF) a (PPT) | Required<br>Mentioned              |     |    |

| W2   | 04.03<br>Thu. | You Tube Live | L3a: Mysteries in Computer Architecture II                 | Required<br>Suggested              |     |    |

Home Announcements Materials <u>Lectures/Schedule</u> Lecture Buzzwords Readings

ReadingsOptional HWsLabs

Extra Assignments

Exams

Technical Docs

Scomputer Architecture (CMU) SS15: Lecture Videos

Computer Architecture (CMU)

S Digitaltechnik SS18: Lecture

S Digitaltechnik SS19: Lecture

Digitaltechnik SS18: Course

Sigitaltechnik SS19: Course

Digitaltechnik SS20: Lecture

Source State Course Signature Signat

SS15: Course Website

Resources

Videos

Website

Videos

Website

Videos

Website

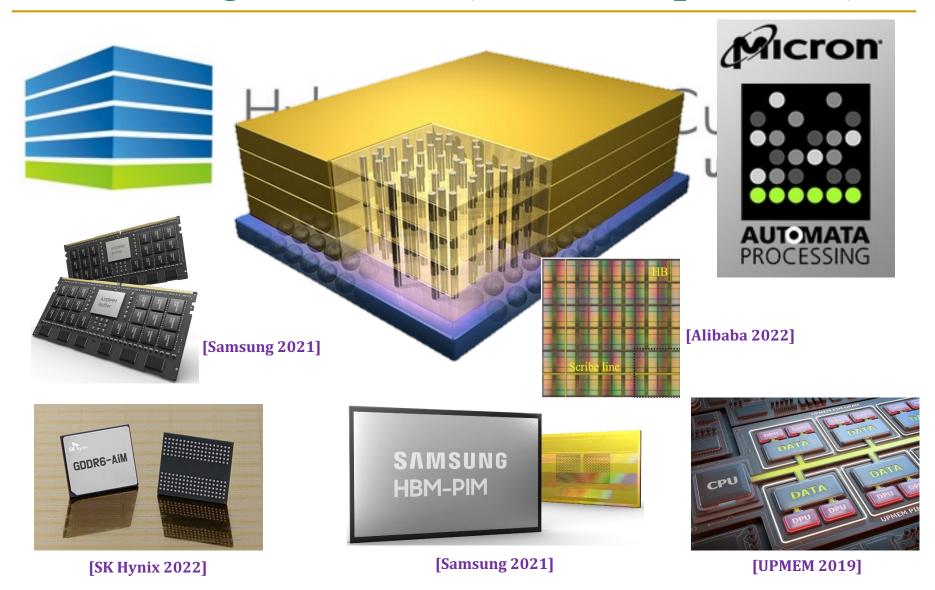

### PIM Course (Spring 2022)

### Spring 2022 Edition:

https://safari.ethz.ch/projects and semi nars/spring2022/doku.php?id=processing in memory

#### Youtube Livestream:

https://www.youtube.com/watch?v=9e4 Chnwdovo&list=PL5Q2soXY2Zi-841fUYYUK9EsXKhQKRPyX

#### Project course

- Taken by Bachelor's/Master's students

- Processing-in-Memory lectures

- Hands-on research exploration

- Many research readings

| P | A Modern Primer on Processing in Memo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Onur Mutlu <sup>a,b</sup> , Saugata Ghose <sup>b,c</sup> , Juan Gómez-Luna <sup>a</sup> , Rachata Ausavarungnirun <sup>d</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | SAFARI Research Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | <sup>b</sup> Carne <sup>(27)</sup> - <sup>b</sup> Carne <sup>(2</sup> |

|   | Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun,<br>"A Modern Primer on Processing in Memory"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | Invited Book Chapter in Emerging Computing: From Devices to Systems -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | Looking Beyond Moore and Von Neumann, Springer, to be published in 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### Spring 2022 Meetings/Schedule

| Week | Date          | Livestream        | Meeting                                                                                 | Learning<br>Materials                          | Assignmen |

|------|---------------|-------------------|-----------------------------------------------------------------------------------------|------------------------------------------------|-----------|

| W1   | 10.03<br>Thu. | You Tube Live     | M1: P&S PIM Course Presentation<br>@ (PDF) @ (PPT)                                      | Required Materials<br>Recommended<br>Materials | HW 0 Out  |

| W2   | 15.03<br>Tue. |                   | Hands-on Project Proposals                                                              |                                                |           |

|      | 17.03<br>Thu. | You Tube Premiere | M2: Real-world PIM: UPMEM PIM                                                           |                                                |           |

| W3   | 24.03<br>Thu. | You The Live      | M3: Real-world PIM:<br>Microbenchmarking of UPMEM<br>PIM<br>@ (PDF) @ (PPT)             |                                                |           |

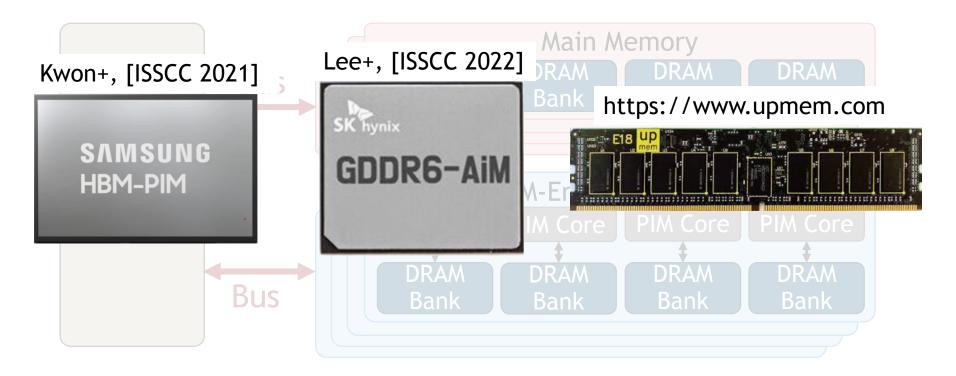

| W4   | 31.03<br>Thu. | You Tube Live     | M4: Real-world PIM: Samsung<br>HBM-PIM<br>(PDF) (PPT)                                   |                                                |           |

| W5   | 07.04<br>Thu. | You Tobe Live     | M5: How to Evaluate Data<br>Movement Bottlenecks<br>(200 (PDF) 222 (PPT)                |                                                |           |

| W6   | 14.04<br>Thu. | You Tube Live     | M6: Real-world PIM: SK Hynix AiM (PDF) (PPT)                                            |                                                |           |

| W7   | 21.04<br>Thu. | You Tobe Premiere | M7: Programming PIM<br>Architectures<br>(PDF) (mathematical (PPT))                      |                                                |           |

| W8   | 28.04<br>Thu. | You Tobe Premiere | M8: Benchmarking and Workload<br>Suitability on PIM<br>(PDF) (mathematical (PPT))       |                                                |           |

| W9   | 05.05<br>Thu. | You Tube Premiere | M9: Real-world PIM: Samsung<br>AxDIMM                                                   |                                                |           |

| W10  | 12.05<br>Thu. | You Tube Premiere | M10: Real-world PIM: Alibaba HB-<br>PNM<br>(PDF) (PPT)                                  |                                                |           |

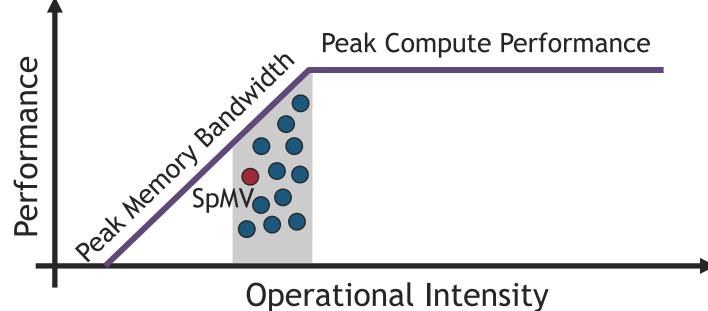

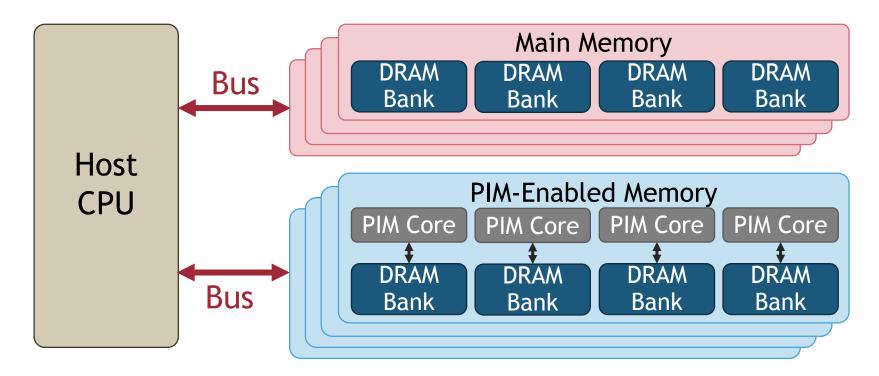

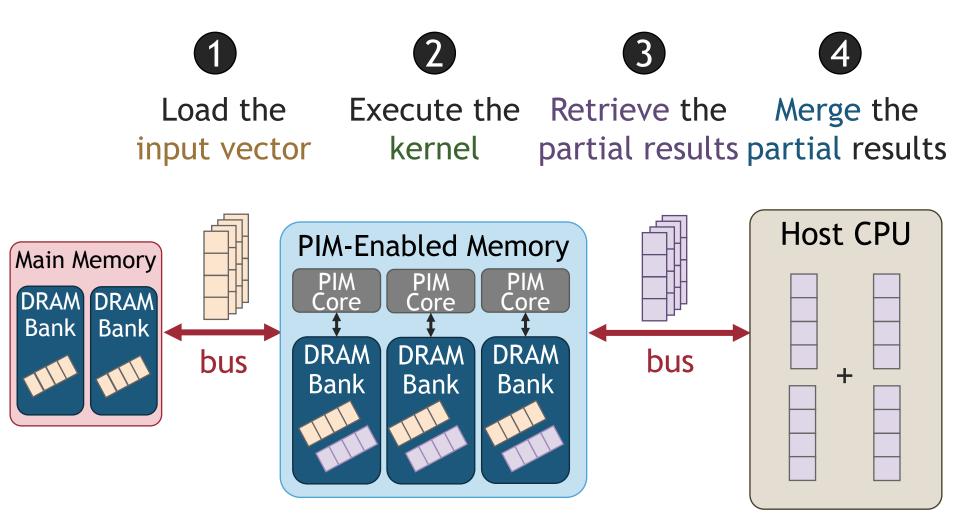

| W11  | 19.05<br>Thu. | You Tube Live     | M11: SpMV on a Real PIM<br>Architecture<br>(PDF) (m) (PPT)                              |                                                |           |

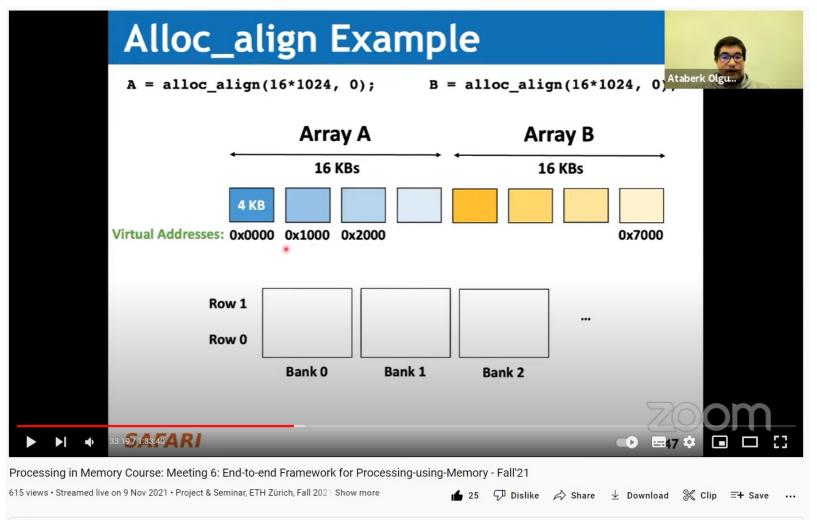

| W12  | 26.05<br>Thu. | You Tube Live     | M12: End-to-End Framework for<br>Processing-using-Memory<br>(PDF) (mathematic (PPT))    |                                                |           |

| W13  | 02.06<br>Thu. | You Tube Live     | M13: Bit-Serial SIMD Processing<br>using DRAM<br>(PDF) (PPT)                            |                                                |           |

| W14  | 09.06<br>Thu. | You Tube Live     | M14: Analyzing and Mitigating ML<br>Inference Bottlenecks<br>(PDF) (mathematical (PPT)) |                                                |           |

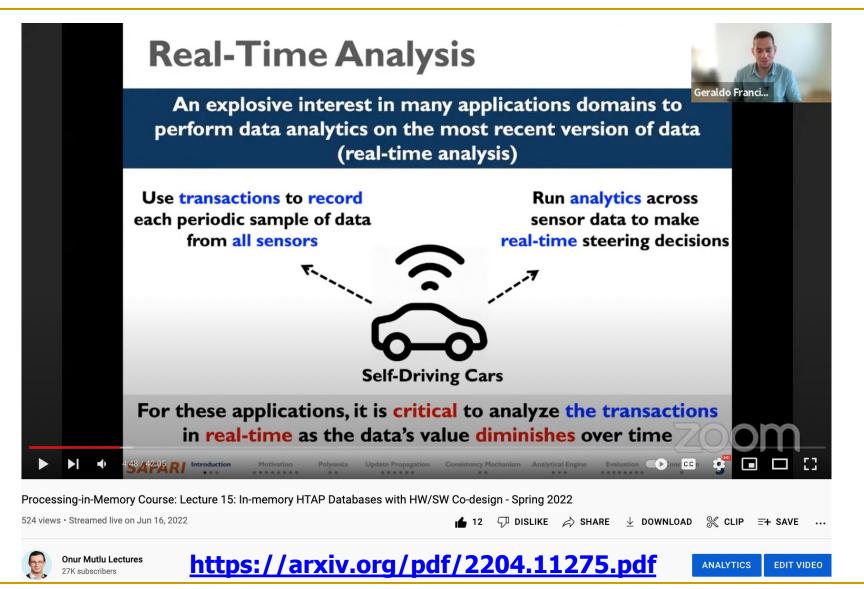

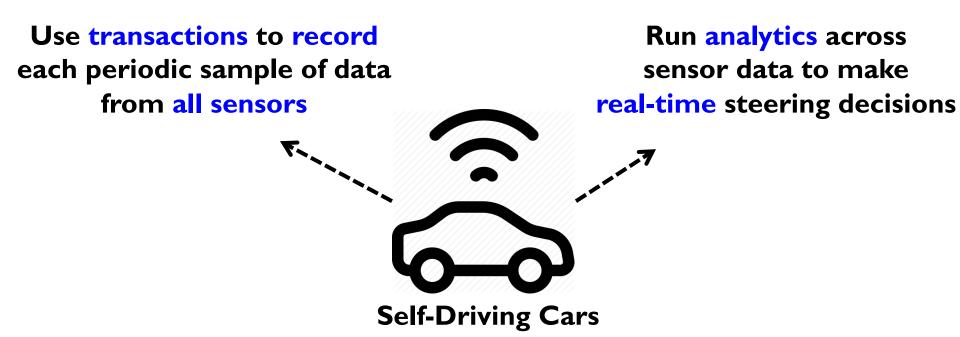

| W15  | 15.06<br>Thu. | You Tube Live     | M15: In-Memory HTAP Databases<br>with HW/SW Co-design<br>(PDF) (2000) (PPT)             |                                                |           |

| W16  | 23.06<br>Thu. | You Tube Live     | M16: In-Storage Processing for<br>Genome Analysis<br>(PDF) ((PPT))                      |                                                |           |

| W17  | 18.07<br>Mon. | You Tube Premiere | M17: How to Enable the Adoption<br>of PIM?<br>(PDF) (PPT)                               |                                                |           |

| W18  | 09.08<br>Tue. | You Tube Premiere | SS1: ISVLSI 2022 Special Session<br>on PIM<br>(PDF & PPT)                               |                                                |           |

## Genomics (Spring 2022)

### Spring 2022 Edition:

https://safari.ethz.ch/projects and semi nars/spring2022/doku.php?id=bioinforma tics

#### Youtube Livestream:

- https://www.youtube.com/watch?v=DEL 5A Y3TI&list=PL5Q2soXY2Zi8NrPDgOR 1yRU Cxxjw-u18

- Project course

- Taken by Bachelor's/Master's students

- Genomics lectures

- Hands-on research exploration

- Many research readings

#### Spring 2022 Meetings/Schedule

| Week | Date          | Livestream        | Meeting                                                                                        | Learning<br>Materials                             | Assignment |

|------|---------------|-------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------|------------|

| W1   | 11.3<br>Fri.  | You Tube Live     | M1: P&S Accelerating Genomics<br>Course Introduction & Project<br>Proposals<br>@ (PDF) @ (PPT) | Required<br>Materials<br>Recommended<br>Materials |            |

| W2   | 18.3<br>Fri.  | You Tube Live     | M2: Introduction to Sequencing                                                                 |                                                   |            |

| W3   | 25.3<br>Fri.  | You Tube Premiere | M3: Read Mapping                                                                               |                                                   |            |

| W4   | 01.04<br>Fri. | You Tube Premiere | M4: GateKeeper                                                                                 |                                                   |            |

| W5   | 08.04<br>Fri. | You Tube Premiere | M5: MAGNET & Shouji                                                                            |                                                   |            |

| W6   | 15.4<br>Fri.  | You Tube Premiere | M6: SneakySnake                                                                                |                                                   |            |

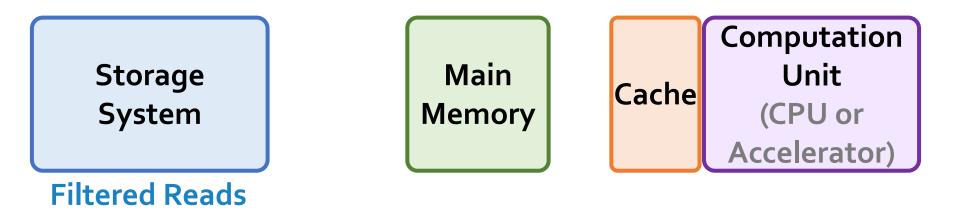

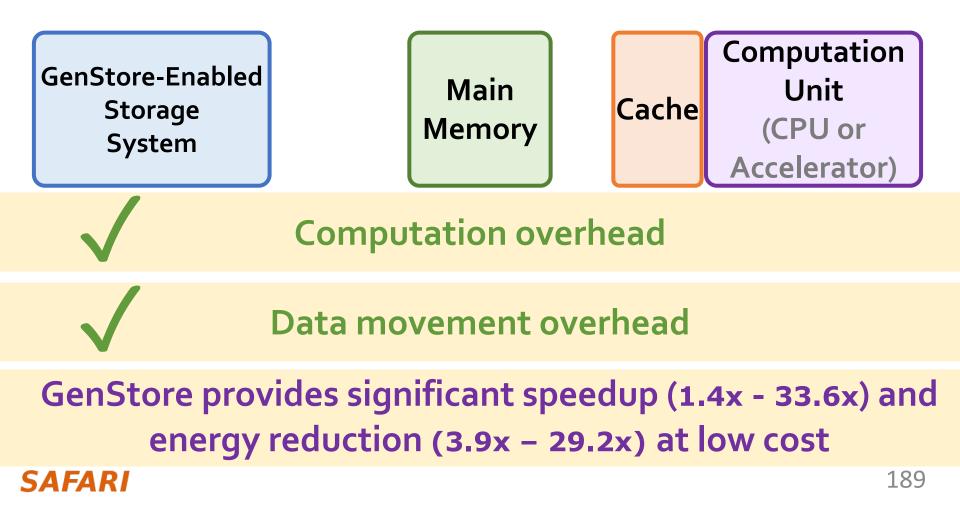

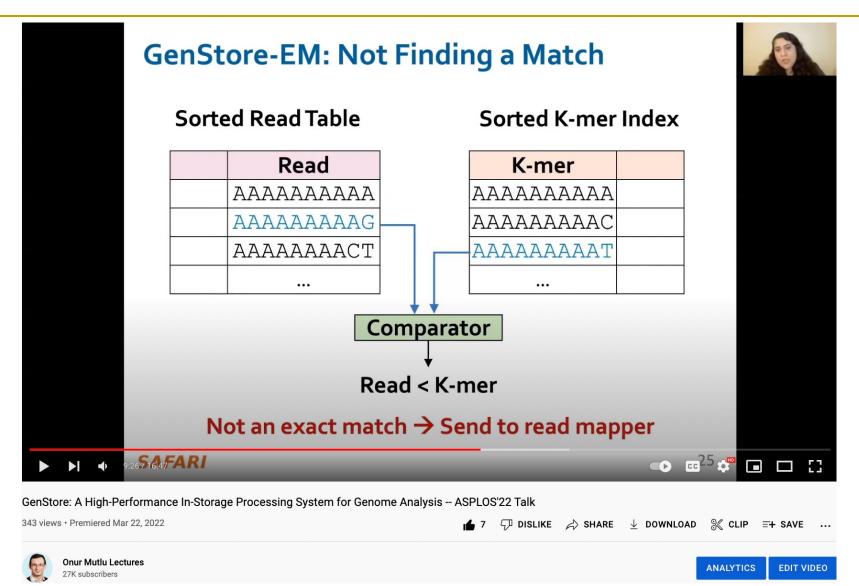

| W7   | 29.4<br>Fri.  | You Tube Premiere | M7: GenStore<br>(PDF)                                                                          |                                                   |            |

| W8   | 06.05<br>Fri. | You Tube Premiere | M8: GRIM-Filter<br>(PDF)    (PPT)                                                              |                                                   |            |

| W9   | 13.05<br>Fri. | You Tube Premiere | M9: Genome Assembly a (PDF) a (PPT)                                                            |                                                   |            |

| W10  | 20.05<br>Fri. | You Tube Live     | M10: Genomic Data Sharing Under<br>Differential Privacy<br>(PDF) (2000) (PPT)                  |                                                   |            |

| W11  | 10.06<br>Fri. | You Tube Premiere | M11: Accelerating Genome<br>Sequence Analysis                                                  |                                                   |            |

### Hetero. Systems (Spring'22)

### Spring 2022 Edition:

https://safari.ethz.ch/projects and semi nars/spring2022/doku.php?id=heterogen eous systems

#### Youtube Livestream:

https://www.youtube.com/watch?v=oFO <u>5fTrgFIY&list=PL5Q2soXY2Zi9XrgXR38IM</u> <u>FTjmY6h7Gzm</u>

#### Project course

- Taken by Bachelor's/Master's students

- GPU and Parallelism lectures

- Hands-on research exploration

- Many research readings

#### Spring 2022 Meetings/Schedule

| Week | Date          | Livestream        | Meeting                                                                 | Learning<br>Materials                          | Assignments |

|------|---------------|-------------------|-------------------------------------------------------------------------|------------------------------------------------|-------------|

| W1   | 15.03<br>Tue. | You Tube Premiere | M1: P&S Course Presentation<br>(PDF) (PPT)                              | Required Materials<br>Recommended<br>Materials | HW 0 Out    |

| W2   | 22.03<br>Tue. | You Tube Premiere | M2: SIMD Processing and GPUs<br>(PDF) m(PPT)                            |                                                |             |

| W3   | 29.03<br>Tue. | You Tube Premiere | M3: GPU Software Hierarchy<br>(PDF) (PPT)                               |                                                |             |

| W4   | 05.04<br>Tue. | You Tube Premiere | M4: GPU Memory Hierarchy<br>(PDF) 200 (PPT)                             |                                                |             |

| W5   | 12.04<br>Tue. | You Tube Premiere | M5: GPU Performance<br>Considerations<br>@ (PDF) @ (PPT)                |                                                |             |

| W6   | 19.04<br>Tue. | You Tube Premiere | M6: Parallel Patterns: Reduction                                        |                                                |             |

| W7   | 26.04<br>Tue. | You Tube Premiere | M7: Parallel Patterns: Histogram                                        |                                                |             |

| W8   | 03.05<br>Tue. | You Tube Premiere | M8: Parallel Patterns: Convolution<br>(PDF)                             |                                                |             |

| W9   | 10.05<br>Tue. | You Tube Premiere | M9: Parallel Patterns: Prefix Sum<br>(Scan)                             |                                                |             |

| W10  | 17.05<br>Tue. | You Tube Premiere | M10: Parallel Patterns: Sparse<br>Matrices<br>(PDF) ((PPT))             |                                                |             |

| W11  | 24.05<br>Tue. | You Tube Premiere | M11: Parallel Patterns: Graph<br>Search<br>@ (PDF) @ (PPT)              |                                                |             |

| W12  | 01.06<br>Wed. | You Tube Premiere | M12: Parallel Patterns: Merge<br>Sort<br>(PDF) (PPT) (PPT)              |                                                |             |

| W13  | 07.06<br>Tue. | You Tube Premiere | M13: Dynamic Parallelism                                                |                                                |             |

| W14  | 15.06<br>Wed. | You Tube Premiere | M14: Collaborative Computing<br>(PDF) m (PPT)                           |                                                |             |

| W15  | 24.06<br>Fri. | You Tube Premiere | M15: GPU Acceleration of<br>Genome Sequence Alignment<br>(PDF) (m(PPT)) |                                                |             |

| W16  | 14.07<br>Thu. | You Tube Premiere | M16: Accelerating Agent-based<br>Simulations<br>(PDF) (a) (ODP)         |                                                |             |

### HW/SW Co-Design (Spring 2022)

#### Spring 2022 Edition:

https://safari.ethz.ch/projects and semi nars/spring2022/doku.php?id=hw sw co design

#### Youtube Livestream:

<u>https://youtube.com/playlist?list=PL5Q2s</u> <u>oXY2Zi8nH7un3ghD2nutKWWDk-NK</u>

#### Project course

- Taken by Bachelor's/Master's students

- HW/SW co-design lectures

- Hands-on research exploration

- Many research readings

#### 2022 Meetings/Schedule (Tentative)

| Week | Date  | Livestream    | Meeting                                 | Materials | Assignments |

|------|-------|---------------|-----------------------------------------|-----------|-------------|

| W0   | 16.03 | You Tube Live | Intro to HW/SW Co-Design                | Required  | HW 0 Out    |

| W1   | 23.03 |               | Project selection                       | Required  |             |

| W2   | 30.03 | You Tube Live | Virtual Memory (I)<br>(PPTX) (PDF)      |           |             |

| W3   | 13.04 | You Tube Live | Virtual Memory (II)<br>a (PPTX) a (PDF) |           |             |

### SSD Course (Spring 2022)

### Spring 2022 Edition:

https://safari.ethz.ch/projects\_and\_semi nars/spring2022/doku.php?id=modern\_s sds

#### Youtube Livestream:

- https://www.youtube.com/watch?v= q4r m71DsY4&list=PL5Q2soXY2Zi8vabcse1kL 22DEcgMl2RAq

- Project course

- Taken by Bachelor's/Master's students

- SSD Basics and Advanced Topics

- Hands-on research exploration

- Many research readings

| _                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Jisung Park    |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                                                                     | P&S Modern SSDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

| _                                                                   | Basics of NAND Flash-Based SSD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9s             |

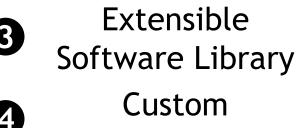

|                                                                     | Dr. Jisung Park                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _              |