# SAFARI EFCL Research Projects: Recent Results and Future Outlook

Onur Mutlu <u>omutlu@gmail.com</u> <u>https://people.inf.ethz.ch/omutlu</u> 23 May 2022 EFCL Mini-Conference

### Current Research Mission

Computer architecture, HW/SW, systems, bioinformatics, security

**Graphics and Vision Processing**

### **Build fundamentally better architectures**

### SAFARI

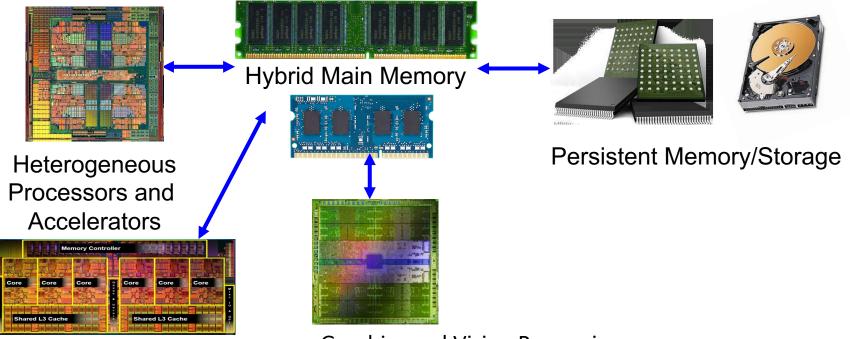

## Four Key Current Directions

Fundamentally Secure/Reliable/Safe Architectures

Fundamentally Energy-Efficient Architectures

Memory-centric (Data-centric) Architectures

Fundamentally Low-Latency and Predictable Architectures

Architectures for AI/ML, Genomics, Medicine, Health, ...

### Fundamentally Better Architectures

# **Data-centric**

# **Data-driven**

# **Data-aware**

## Onur Mutlu's SAFARI Research Group

### Computer architecture, HW/SW, systems, bioinformatics, security, memory

https://safari.ethz.ch/safari-newsletter-january-2021/

### SAFARI Newsletter December 2021 Edition

### <u>https://safari.ethz.ch/safari-newsletter-december-2021/</u>

Think Big, Aim High

f y in 🛛

View in your browser December 2021

# Referenced Papers, Talks, Artifacts

All are available at

https://people.inf.ethz.ch/omutlu/projects.htm

https://www.youtube.com/onurmutlulectures

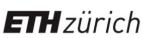

https://github.com/CMU-SAFARI/

# Open-Source Artifacts

https://github.com/CMU-SAFARI

# Open Source Tools: SAFARI GitHub

MQSim is a fast and accurate simulator modeling the performance of modern multi-queue (MQ) SSDs as well as traditional SATA based SSDs. MQSim faithfully models new high-bandwidth protocol implement...

● C++ ☆ 143 😵 90

Source code for testing the Row Hammer error mechanism in DRAM devices. Described in the ISCA 2014 paper by Kim et al. at http://users.ece.cmu.edu/~omutlu/pub/dram-row-hammer\_isca14.pdf.

●C ☆ 188 % 41

### https://github.com/CMU-SAFARI/

### Onur Mutlu's SAFARI Research Group

# SAFARI Research Group safari.ethz.ch

# SAFARI Overview at EFCL Huawei Day

Onur Mutlu, "SAFARI Research Group: Introduction & Research" Invited Talk at the ETH Future Computing Laboratory Huawei Day, Virtual, 19 October 2021. [Slides (pptx) (pdf)] [Talk Video (15 minutes)]

# SAFARI Overview at EFCL Huawei Day

SAFARI Research Group: Introduction & Research - ETH Future Computing

Laboratorv Event Talk - Onur Mutlu

### https://youtu.be/mSr1QQmYuX0

### Fundamentally Better Architectures

# **Data-centric**

# **Data-driven**

# **Data-aware**

### A Blueprint for Fundamentally Better Architectures

### Onur Mutlu, "Intelligent Architectures for Intelligent Computing Systems" Invited Paper in Proceedings of the Design, Automation, and Test in Europe Conference (DATE), Virtual, February 2021. [Slides (pptx) (pdf)] [IEDM Tutorial Slides (pptx) (pdf)] [Short DATE Talk Video (11 minutes)] [Longer IEDM Tutorial Video (1 hr 51 minutes)]

### Intelligent Architectures for Intelligent Computing Systems

Onur Mutlu ETH Zurich omutlu@gmail.com

### SAFARI

# Current EFCL Projects

"A New Methodology and Open-Source Benchmark Suite for Evaluating Data Movement Bottlenecks: A Processing-in-Memory Case Study"

Data-centric

"Machine-Learning-Assisted Intelligent Microarchitectures to Reduce Memory Access Latency"

Data-driven

- "Cross-layer Hardware/Software Techniques to Enable Powerful Computation and Memory Optimizations"

- Data-aware

A New Methodology and Open-Source Benchmark Suite for Evaluating Data Movement Bottlenecks: A Processing-in-Memory Case Study

> Juan Gómez Luna, Geraldo F. Oliveira, Mohammad Sadr, Lois Orosa Onur Mutlu

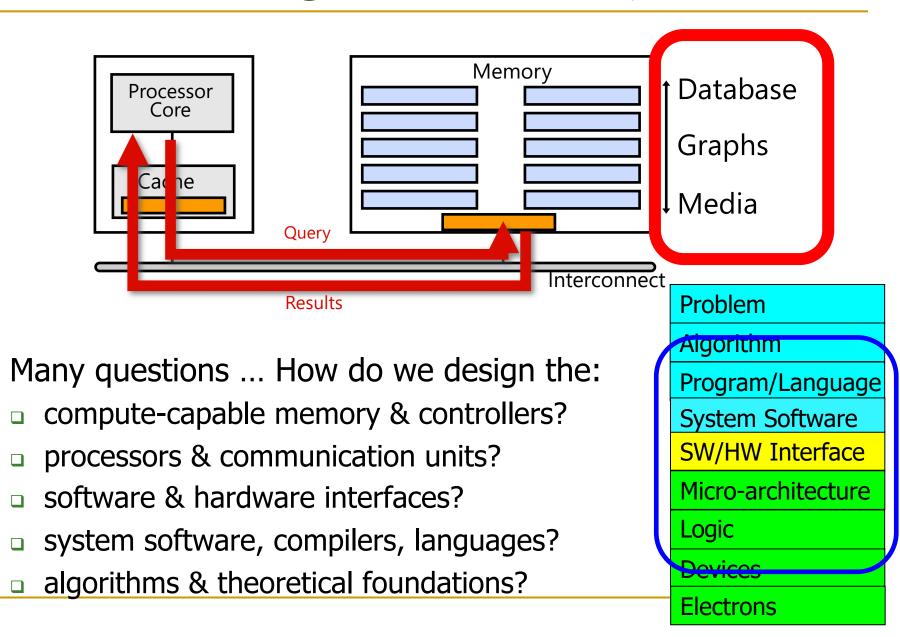

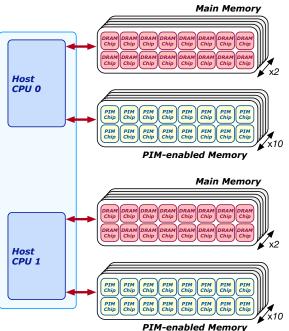

# Goal: Processing Inside Memory

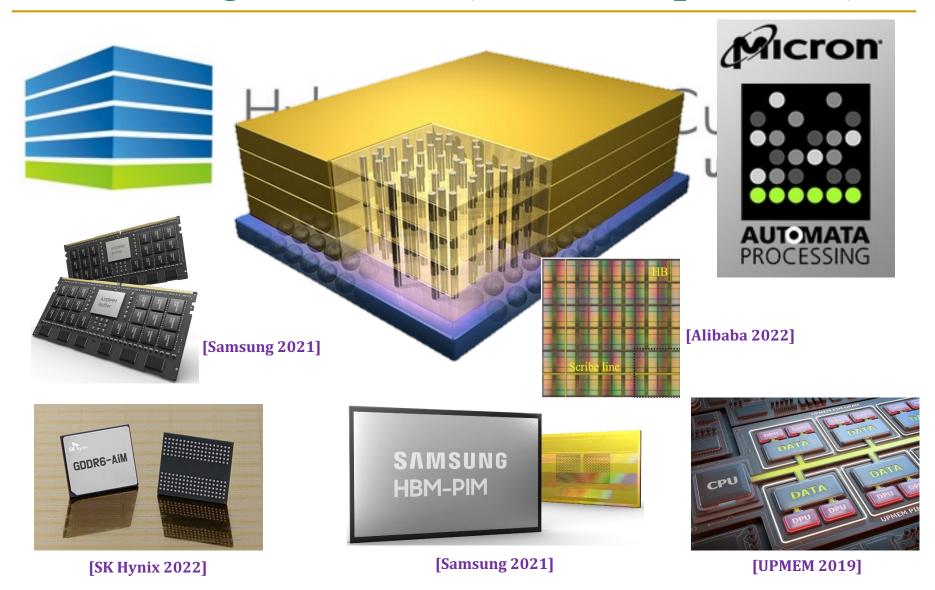

# Processing-in-Memory Landscape Today

This does not include many experimental chips and startups

# PIM Review and Open Problems

# A Modern Primer on Processing in Memory

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b,c</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>d</sup>

SAFARI Research Group

<sup>a</sup>ETH Zürich <sup>b</sup>Carnegie Mellon University <sup>c</sup>University of Illinois at Urbana-Champaign <sup>d</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun, "A Modern Primer on Processing in Memory" *Invited Book Chapter in <u>Emerging Computing: From Devices to Systems -</u> <i>Looking Beyond Moore and Von Neumann*, Springer, to be published in 2021.

### SAFARI

https://arxiv.org/pdf/1903.03988.pdf

# PIM Review and Open Problems (II)

### A Workload and Programming Ease Driven Perspective of Processing-in-Memory

Saugata Ghose†Amirali Boroumand†Jeremie S. Kim†§Juan Gómez-Luna§Onur Mutlu§††Carnegie Mellon University§ETH Zürich

Saugata Ghose, Amirali Boroumand, Jeremie S. Kim, Juan Gomez-Luna, and Onur Mutlu, "Processing-in-Memory: A Workload-Driven Perspective" *Invited Article in IBM Journal of Research & Development, Special Issue on Hardware for Artificial Intelligence*, to appear in November 2019. [Preliminary arXiv version]

### SAFARI

https://arxiv.org/pdf/1907.12947.pdf

### A Modern Primer on Processing in Memory

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b,c</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>d</sup>

SAFARI Research Group

<sup>a</sup>ETH Zürich <sup>b</sup>Carnegie Mellon University <sup>c</sup>University of Illinois at Urbana-Champaign <sup>d</sup>King Mongkut's University of Technology North Bangkok

### Abstract

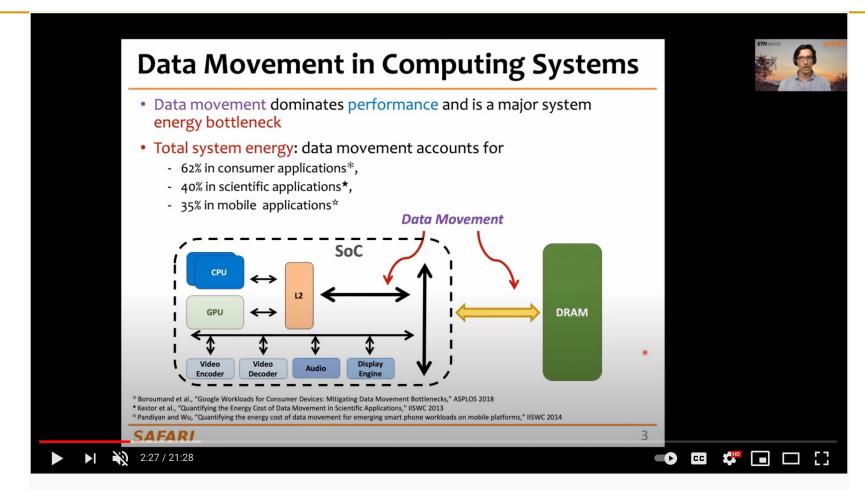

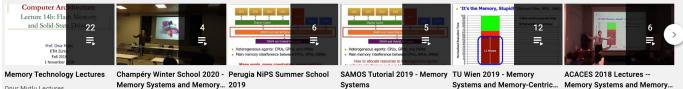

Modern computing systems are overwhelmingly designed to move data to computation. This design choice goes directly against at least three key trends in computing that cause performance, scalability and energy bottlenecks: (1) data access is a key bottleneck as many important applications are increasingly data-intensive, and memory bandwidth and energy do not scale well, (2) energy consumption is a key limiter in almost all computing platforms, especially server and mobile systems, (3) data movement, especially off-chip to on-chip, is very expensive in terms of bandwidth, energy and latency, much more so than computation. These trends are especially severely-felt in the data-intensive server and energy-constrained mobile systems of today.

At the same time, conventional memory technology is facing many technology scaling challenges in terms of reliability, energy, and performance. As a result, memory system architects are open to organizing memory in different ways and making it more intelligent, at the expense of higher cost. The emergence of 3D-stacked memory plus logic, the adoption of error correcting codes inside the latest DRAM chips, proliferation of different main memory standards and chips, specialized for different purposes (e.g., graphics, low-power, high bandwidth, low latency), and the necessity of designing new solutions to serious reliability and security issues, such as the RowHammer phenomenon, are an evidence of this trend.

This chapter discusses recent research that aims to practically enable computation close to data, an approach we call *processing-in-memory* (PIM). PIM places computation mechanisms in or near where the data is stored (i.e., inside the memory chips, in the logic layer of 3D-stacked memory, or in the memory controllers), so that data movement between the computation units and memory is reduced or eliminated. While the general idea of PIM is not new, we discuss motivating trends in applications as well as memory circuits/technology that greatly exacerbate the need for enabling it in modern computing systems. We examine at least two promising new approaches to designing PIM systems to accelerate important data-intensive applications: (1) *processing using memory* by exploiting analog operational properties of DRAM chips to perform massively-parallel operations in memory, with low-cost changes, (2) *processing near memory* by exploiting 3D-stacked memory technology design to provide high memory bandwidth and low memory latency to in-memory logic. In both approaches, we describe and tackle relevant cross-layer research, design, and adoption challenges in devices, architecture, systems, and programming models. Our focus is on the development of in-memory processing designs that can be adopted in real computing platforms at low cost. We conclude by discussing work on solving key challenges to the practical adoption of PIM.

*Keywords:* memory systems, data movement, main memory, processing-in-memory, near-data processing, computation-in-memory, processing using memory, processing near memory, 3D-stacked memory, non-volatile memory, energy efficiency, high-performance computing, computer architecture, computing paradigm, emerging technologies, memory scaling, technology scaling, dependable systems, robust systems, hardware security, system security, latency, low-latency computing

### SAFARI

### Contents

SAFARI

| 1 | Introduction                                | 2  |  |  |  |

|---|---------------------------------------------|----|--|--|--|

| 2 | Major Trends Affecting Main Memory          | 4  |  |  |  |

| 3 | The Need for Intelligent Memory Controllers |    |  |  |  |

| - | to Enhance Memory Scaling                   | 6  |  |  |  |

| _ |                                             |    |  |  |  |

| 4 | Perils of Processor-Centric Design          | 9  |  |  |  |

| 5 | Processing-in-Memory (PIM): Technology      | _  |  |  |  |

| 5 | Enablers and Two Approaches                 | 12 |  |  |  |

| - | 5.1 New Technology Enablers: 3D-Stacked     | _  |  |  |  |

|   | Memory and Non-Volatile Memory              | 12 |  |  |  |

| - | 5.2 Two Approaches: Processing Using        |    |  |  |  |

|   | Memory (PUM) vs. Processing Near            |    |  |  |  |

|   | Memory (PNM)                                | 13 |  |  |  |

|   |                                             |    |  |  |  |

| 6 | Processing Using Memory (PUM)               | 14 |  |  |  |

|   | 6.1 RowClone                                | 14 |  |  |  |

|   | 6.2 Ambit                                   | 15 |  |  |  |

|   | 6.3 Gather-Scatter DRAM                     | 17 |  |  |  |

|   | 6.4 In-DRAM Security Primitives             | 17 |  |  |  |

| 7 | Processing Near Memory (PNM)                | 18 |  |  |  |

| 4 | 7.1 Tesseract: Coarse-Grained Application-  | 10 |  |  |  |

|   | Level PNM Acceleration of Graph Pro-        |    |  |  |  |

|   | cessing                                     | 19 |  |  |  |

| - | 7.2 Function-Level PNM Acceleration of      |    |  |  |  |

|   | Mobile Consumer Workloads                   | 20 |  |  |  |

|   | 7.3 Programmer-Transparent Function-        |    |  |  |  |

|   | Level PNM Acceleration of GPU               |    |  |  |  |

|   | Applications                                | 21 |  |  |  |

| _ | 7.4 Instruction-Level PNM Acceleration      |    |  |  |  |

|   | with PIM-Enabled Instructions (PEI)         | 21 |  |  |  |

| _ | 7.5 Function-Level PNM Acceleration of      | _  |  |  |  |

|   | Genome Analysis Workloads                   | 22 |  |  |  |

| _ | 7.6 Application-Level PNM Acceleration of   | 22 |  |  |  |

|   | Time Series Analysis                        | 23 |  |  |  |

| 8 | Enabling the Adoption of PIM                | 24 |  |  |  |

| • | 8.1 Programming Models and Code Genera-     |    |  |  |  |

|   | tion for PIM                                | 24 |  |  |  |

| _ | 8.2 PIM Runtime: Scheduling and Data        |    |  |  |  |

|   | Mapping                                     | 25 |  |  |  |

| _ | 8.3 Memory Coherence                        | 27 |  |  |  |

|   | 8.4 Virtual Memory Support                  | 27 |  |  |  |

|   | 8.5 Data Structures for PIM                 | 28 |  |  |  |

|   | 8.6 Benchmarks and Simulation Infrastruc-   |    |  |  |  |

|   | tures                                       | 29 |  |  |  |

| _ | 8.7 Real PIM Hardware Systems and Proto-    |    |  |  |  |

|   | types                                       | 30 |  |  |  |

|   | 8.8 Security Considerations                 | 30 |  |  |  |

| 0 | Conclusion and Future Order 1               | 21 |  |  |  |

| 9 | Conclusion and Future Outlook               | 31 |  |  |  |

### 1. Introduction

Main memory, built using the Dynamic Random Access Memory (DRAM) technology, is a major component in nearly all computing systems, including servers, cloud platforms, mobile/embedded devices, and sensor systems. Across all of these systems, the data working set sizes of modern applications are rapidly growing, while the need for fast analysis of such data is increasing. Thus, main memory is becoming an increasingly significant bottleneck across a wide variety of computing systems and applications [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16]. Alleviating the main memory bottleneck requires the memory capacity, energy, cost, and performance to all scale in an efficient manner across technology generations. Unfortunately, it has become increasingly difficult in recent years, especially the past decade, to scale all of these dimensions [1, 2, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 40, 41, 42, 43, 44, 45, 46, 47, 48, 49], and thus the main memory bottleneck has been worsening.

A major reason for the main memory bottleneck is the high energy and latency cost associated with data movement. In modern computers, to perform any operation on data that resides in main memory, the processor must retrieve the data from main memory. This requires the memory controller to issue commands to a DRAM module across a relatively slow and power-hungry off-chip bus (known as the memory channel). The DRAM module sends the requested data across the memory channel, after which the data is placed in the caches and registers. The CPU can perform computation on the data once the data is in its registers. Data movement from the DRAM to the CPU incurs long latency and consumes a significant amount of energy [7, 50, 51, 52, 53, 54]. These costs are often exacerbated by the fact that much of the data brought into the caches is not reused by the CPU [52, 53, 55, 56], providing little benefit in return for the high latency and energy cost.

The cost of data movement is a fundamental issue with the *processor-centric* nature of contemporary computer systems. The CPU is considered to be the master in the system, and computation is performed only in the processor (and accelerators). In contrast, data storage and communication units, including the main memory, are treated as unintelligent workers that are incapable of computation. As a result of this processor-centric design paradigm, data moves a lot in the system between the computation units and communication/ storage units so that computation can be done on it. With the increasingly *data-centric* nature of contemporary and emerging appli-

22

## Eliminating the Adoption Barriers

# How to Enable Adoption of Processing in Memory

# Potential Barriers to Adoption of PIM

1. Applications & software for PIM

2. Ease of **programming** (interfaces and compiler/HW support)

3. **System** and **security** support: coherence, synchronization, virtual memory, isolation, communication interfaces, ...

4. **Runtime** and **compilation** systems for adaptive scheduling, data mapping, access/sharing control, ...

5. Infrastructures to assess benefits and feasibility

### All can be solved with change of mindset

## Our Goal

- To enable adoption of Processing-in-Memory (PIM) systems by solving various key challenges

- Identifying workloads and functions suitable for PIM

- Fundamental (architecture-independent) characterization

- Architecture-specific suitability

- Overcoming the problem of lack of useful tools

- Profiling tools

- Analytical performance and energy models (or ML-based models)

- Simulation tools

- The project is organized in two phases

- Phase 1: Methodology and open-source benchmark suite(s)

- Phase 2: Follow-up project to enable PIM adoption

# Results So Far (2021-2022)

DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks [IEEE Access 2021]

- Benchmarking a New Paradigm: Experimental Analysis and Characterization of a Real Processing-in-Memory System [IEEE Access 2022]

- Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks [PACT 2021]

- Enabling High-Performance and Energy-Efficient Hybrid Transactional/Analytical Databases with Hardware/Software Cooperation [ICDE 2022]

- FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications [IEEE Micro 2021]

### SAFARI

DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

### Geraldo F. Oliveira

Juan Gómez-Luna Lois Orosa Saugata Ghose Nandita Vijaykumar Ivan Fernandez Mohammad Sadrosadati Onur Mutlu

## **Executive Summary**

- <u>Problem</u>: Data movement is a major bottleneck is modern systems. However, it is **unclear** how to identify:

- different sources of data movement bottlenecks

- the most suitable mitigation technique (e.g., caching, prefetching, near-data processing) for a given data movement bottleneck

- <u>Goals</u>:

SAFARI

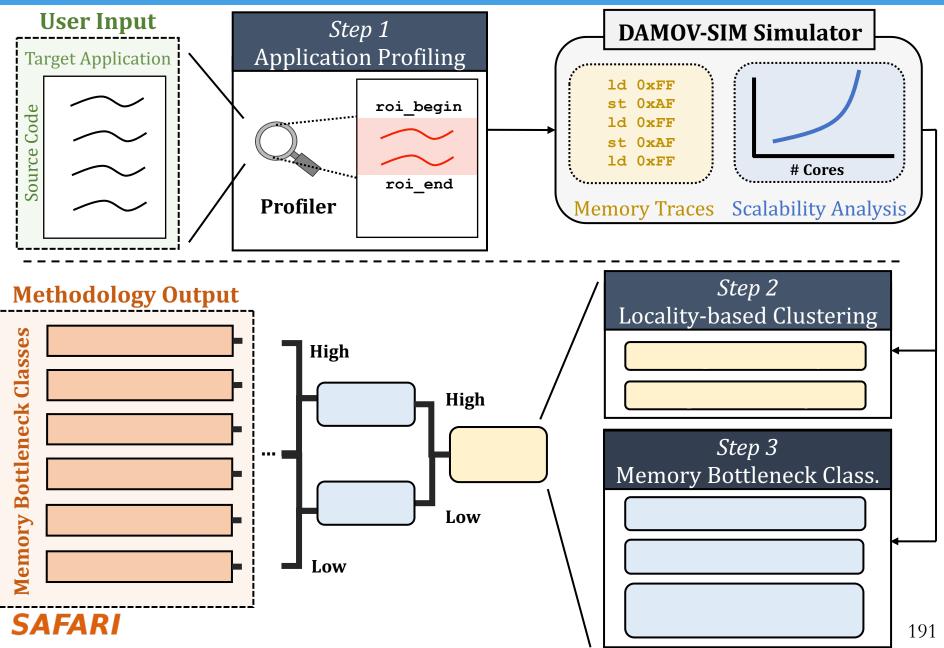

- 1. Design a methodology to **identify** sources of data movement bottlenecks

- 2. **Compare** compute- and memory-centric data movement mitigation techniques

- <u>Key Approach</u>: Perform a large-scale application characterization to identify key metrics that reveal the sources to data movement bottlenecks

- Key Contributions:

- Experimental characterization of 77K functions across 345 applications

- A methodology to characterize applications based on data movement bottlenecks and their relation with different data movement mitigation techniques

- DAMOV: a benchmark suite with 144 functions for data movement studies

- Four case-studies to highlight DAMOV's applicability to open research problems

### **DAMOV:** <u>https://github.com/CMU-SAFARI/DAMOV</u>

### **Near-Data Processing**

### **UPMEM (2019)**

Near-DRAM-banks processing for general-purpose computing

0.9 TOPS compute throughput<sup>1</sup>

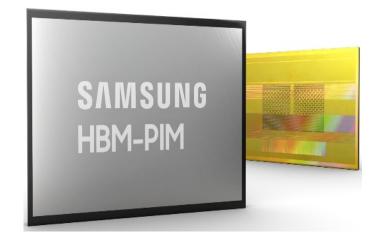

### Samsung FIMDRAM (2021)

### Near-DRAM-banks processing for neural networks

**1.2 TFLOPS compute throughput<sup>2</sup>**

### The goal of Near-Data Processing (NDP) is to mitigate data movement

Devaux, "The True Processing In Memory Accelerator," HCS, 2019

Kwon+, "A 20nm 6GB Function-In-Memory DRAM, Based on HBM2 with a 1.2TFLOPS Programmable Computing Unit Using Bank-Level Parallelism, for Machine Learning Applications," ISSCC, 2021

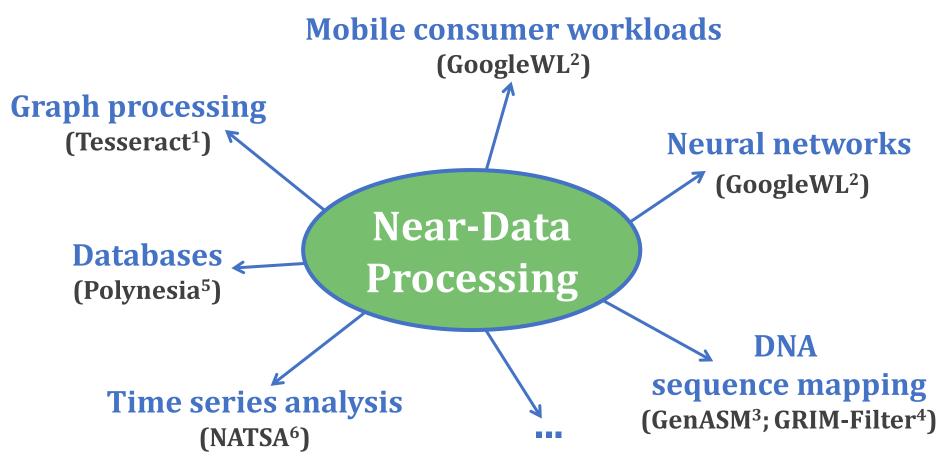

### When to Employ Near-Data Processing?

[1] Ahn+, "A Scalable Processing-in-Memory Accelerator for Parallel Graph Processing," ISCA, 2015

[2] Boroumand+, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks," ASPLOS, 2018

[3] Cali+, "GenASM: A High-Performance, Low-Power Approximate String Matching Acceleration Framework for Genome Sequence Analysis," MICRO, 2020

[4] Kim+, "GRIM-Filter: Fast Seed Location Filtering in DNA Read Mapping Using Processing-in-Memory Technologies," BMC Genomics, 2018

[5] Boroumand+, "Polynesia: Enabling Effective Hybrid Transactional/Analytical Databases with Specialized Hardware/Software Co-Design," arXiv:2103.00798 [cs.AR], 2021

[6] Fernandez+, "NATSA: A Near-Data Processing Accelerator for Time Series Analysis," ICCD, 2020

SAFAR

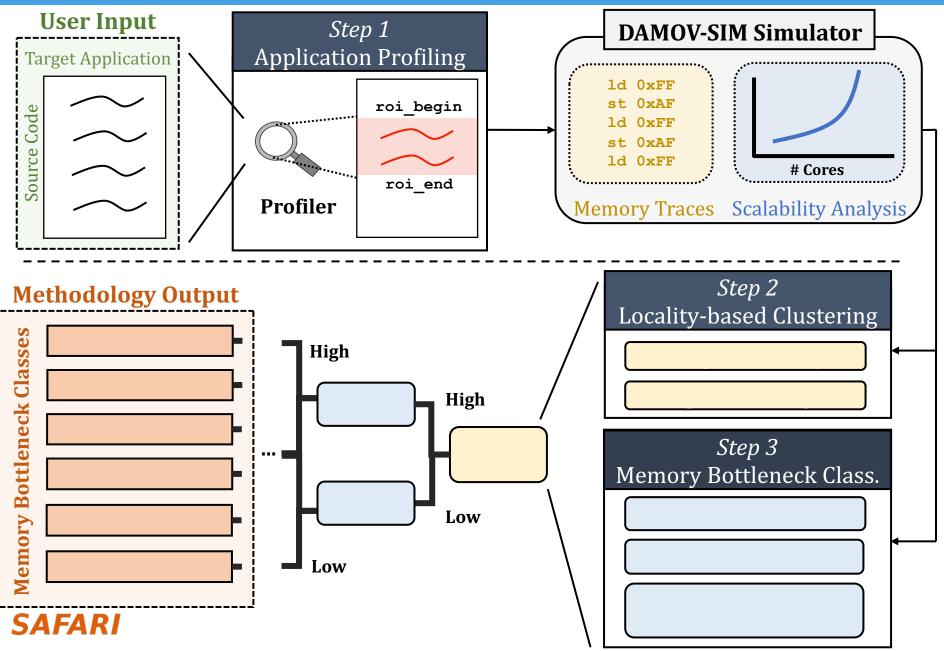

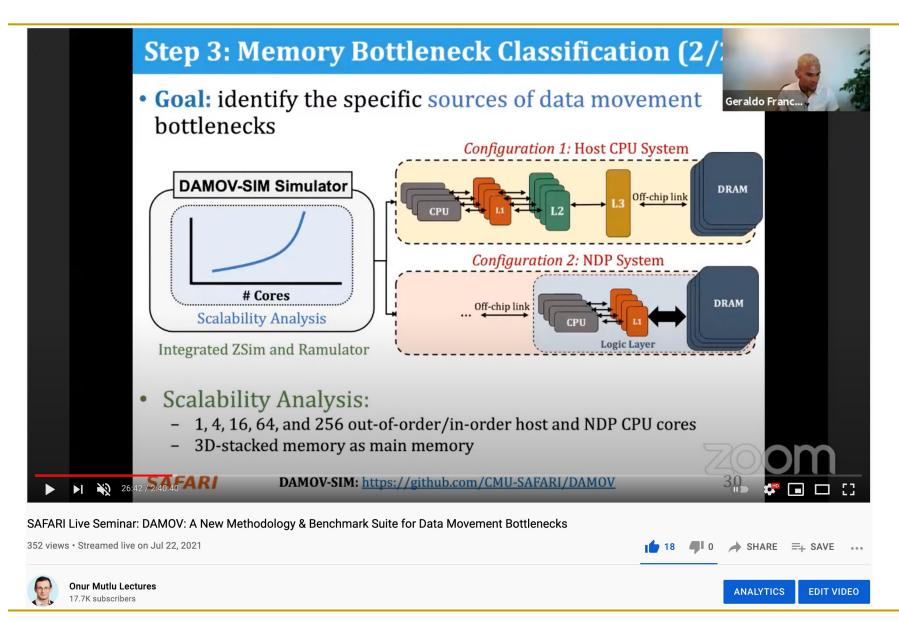

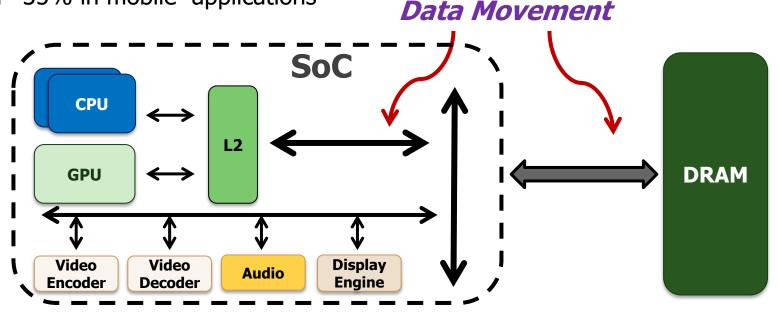

# **Key Approach**

- New workload characterization methodology to analyze:

- data movement bottlenecks

- suitability of different data movement mitigation mechanisms

- Two main profiling strategies:

**Architecture-independent profiling:**

characterizes the memory behavior independently of the underlying hardware

**Architecture-dependent profiling:**

evaluates the impact of the system configuration on the memory behavior

### **Methodology Overview**

# **Step 1: Application Profiling**

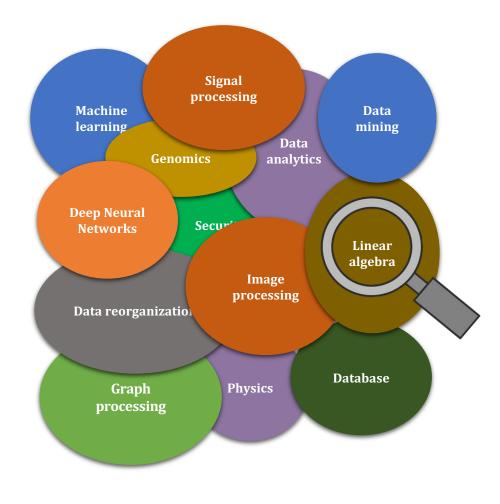

- We analyze 345 applications from distinct domains:

- Graph Processing

- Deep Neural Networks

- Physics

- High-Performance Computing

- Genomics

- Machine Learning

- Databases

- Data Reorganization

- Image Processing

- Map-Reduce

- Benchmarking

- Linear Algebra

SAFARI

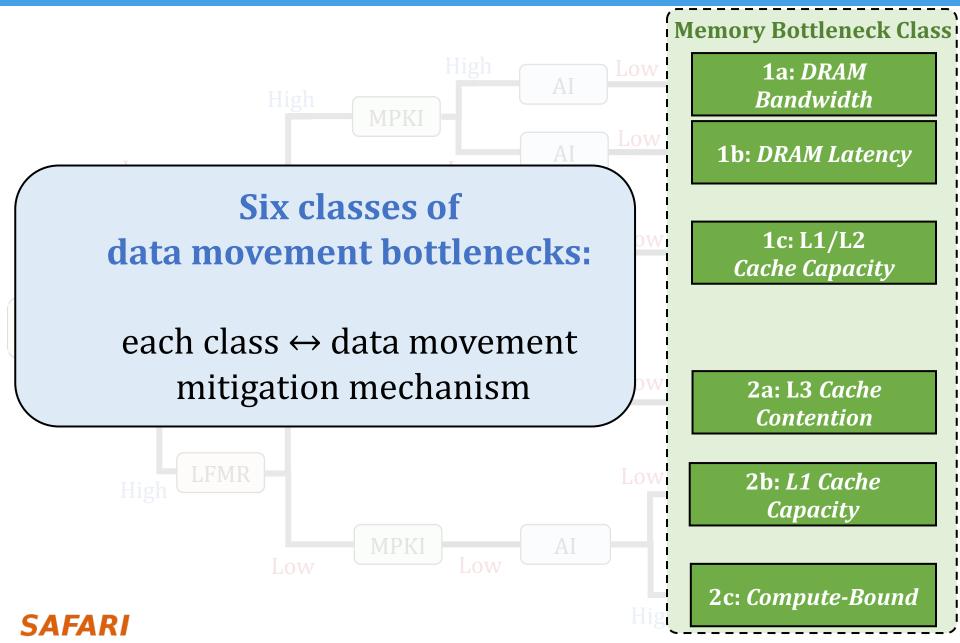

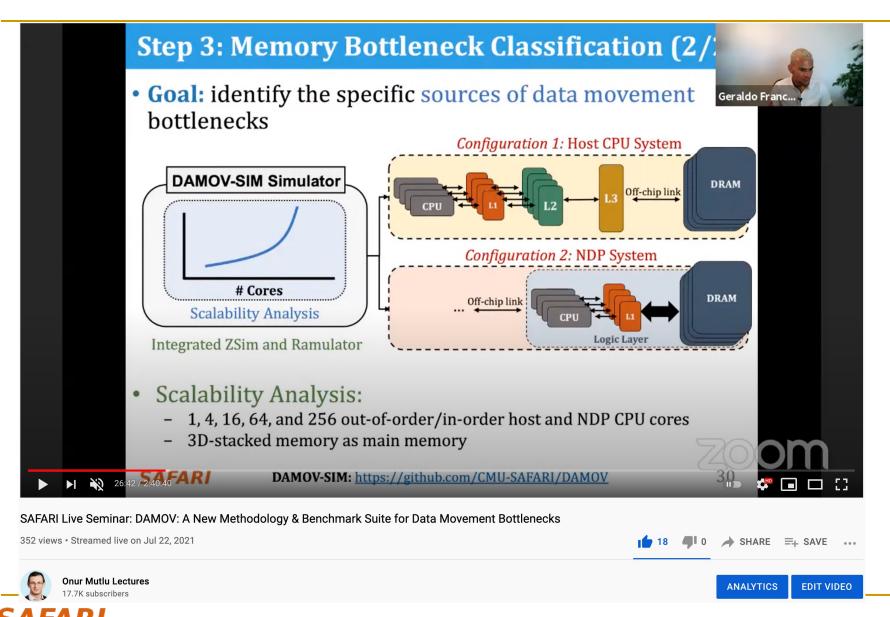

### **Step 3: Memory Bottleneck Analysis**

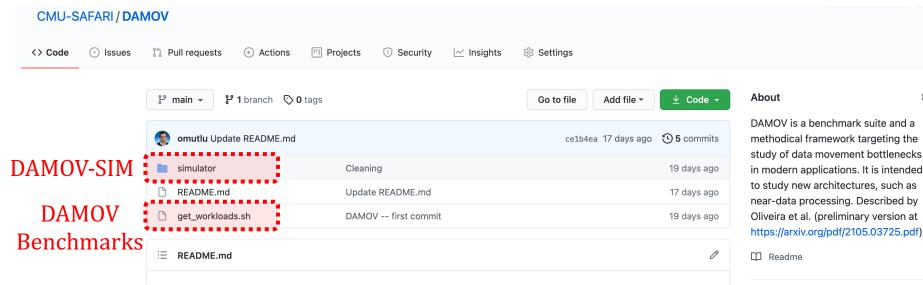

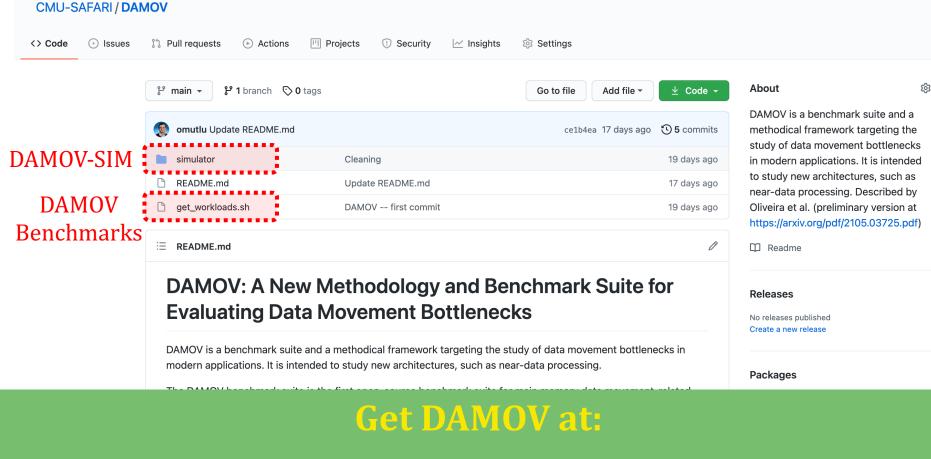

### **DAMOV** is Open Source

• We open-source our benchmark suite and our toolchain

### DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

DAMOV is a benchmark suite and a methodical framework targeting the study of data movement bottlenecks in modern applications. It is intended to study new architectures, such as near-data processing.

The DAMOV benchmark suite is the first open-source benchmark suite for main memory data movement-related studies, based on our systematic characterization methodology. This suite consists of 144 functions representing different sources of data movement bottlenecks and can be used as a baseline benchmark set for future data-movement mitigation research. The applications in the DAMOV benchmark suite belong to popular benchmark suites, including BWA, Chai, Darknet, GASE, Hardware Effects, Hashjoin, HPCC, HPCG, Ligra, PARSEC, Parboil, PolyBench, Phoenix, Rodinia, SPLASH-2, STREAM.

### Releases

No releases published Create a new release කු

### Packages

No packages published Publish your first package

### Languages

### SAFARI

### **DAMOV** is Open Source

• We open-source our benchmark suite and our toolchain

| Code | 1) Pull requests 🕞 Actions 🔟 Projects 🔃 Security 🗠 Insights           | Settings                                                                                                                                                                  |                                                                           |

|------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|      | <sup>৫°</sup> main → <sup>৫°</sup> 1 branch 💿 0 tags                  | Go to file Add file ▼                                                                                                                                                     | About<br>DAMOV is a benchmark suite and                                   |

|      | Get DAM                                                               | OV at:                                                                                                                                                                    |                                                                           |

| ]    | https://github.com/CN                                                 | <b>IU-SAFARI/I</b>                                                                                                                                                        | DAMOV                                                                     |

|      |                                                                       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                     |                                                                           |

|      | i≡ README.md                                                          | Û                                                                                                                                                                         | 🛱 Readme                                                                  |

|      | DAMOV: A New Methodology and Be<br>Evaluating Data Movement Bottlenec | nchmark Suite for<br>ks                                                                                                                                                   | Readme      Releases      No releases published      Create a new release |

|      | DAMOV: A New Methodology and Be                                       | nchmark Suite for<br>ks<br>tudy of data movement bottlenecks in<br>ar-data processing.<br>r main memory data movement-related<br>e consists of 144 functions representing | Releases No releases published                                            |

### More on DAMOV Analysis Methodology & Workloads

https://www.youtube.com/watch?v=GWideVyo0nM&list=PL5Q2soXY2Zi tOTAYm--dYByNPL7JhwR9&index=3

### More on DAMOV Methods & Benchmarks

Geraldo F. Oliveira, Juan Gomez-Luna, Lois Orosa, Saugata Ghose, Nandita Vijaykumar, Ivan fernandez, Mohammad Sadrosadati, and Onur Mutlu, "DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks"

<u>IEEE Access</u>, 8 September 2021. Preprint in <u>arXiv</u>, 8 May 2021.

[arXiv preprint]

[IEEE Access version]

[DAMOV Suite and Simulator Source Code]

[SAFARI Live Seminar Video (2 hrs 40 mins)]

[Short Talk Video (21 minutes)]

#### DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

GERALDO F. OLIVEIRA, ETH Zürich, Switzerland JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland LOIS OROSA, ETH Zürich, Switzerland SAUGATA GHOSE, University of Illinois at Urbana–Champaign, USA NANDITA VIJAYKUMAR, University of Toronto, Canada IVAN FERNANDEZ, University of Malaga, Spain & ETH Zürich, Switzerland MOHAMMAD SADROSADATI, ETH Zürich, Switzerland ONUR MUTLU, ETH Zürich, Switzerland

### DAMOV Analysis Methodology & Workloads

#### DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks

GERALDO F. OLIVEIRA, ETH Zürich, Switzerland JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland LOIS OROSA, ETH Zürich, Switzerland SAUGATA GHOSE, University of Illinois at Urbana–Champaign, USA NANDITA VIJAYKUMAR, University of Toronto, Canada IVAN FERNANDEZ, University of Malaga, Spain & ETH Zürich, Switzerland MOHAMMAD SADROSADATI, Institute for Research in Fundamental Sciences (IPM), Iran & ETH Zürich, Switzerland ONUR MUTLU, ETH Zürich, Switzerland

Data movement between the CPU and main memory is a first-order obstacle against improving performance, scalability, and energy efficiency in modern systems. Computer systems employ a range of techniques to reduce overheads tied to data movement, spanning from traditional mechanisms (e.g., deep multi-level cache hierarchies, aggressive hardware prefetchers) to emerging techniques such as Near-Data Processing (NDP), where some computation is moved close to memory. Prior NDP works investigate the root causes of data movement bottlenecks using different profiling methodologies and tools. However, there is still a lack of understanding about the key metrics that can identify different data movement bottlenecks and their relation to traditional and emerging data movement mitigation mechanisms. Our goal is to methodically identify potential sources of data movement mitigation techniques (e.g., caching and prefetching) to more memory-centric techniques (e.g., NDP), thereby developing a rigorous understanding of the best techniques to mitigate each source of data movement.

With this goal in mind, we perform the first large-scale characterization of a wide variety of applications, across a wide range of application domains, to identify fundamental program properties that lead to data movement to/from main memory. We develop the first systematic methodology to classify applications based on the sources contributing to data movement bottlenecks. From our large-scale characterization of 77K functions across 345 applications, we select 144 functions to form the first open-source benchmark suite (DAMOV) for main memory data movement studies. We select a diverse range of functions that (1) represent different types of data movement bottlenecks, and (2) come from a wide range of application domains. Using NDP as a case study, we identify new insights about the different data movement bottlenecks and use these insights to determine the most suitable data movement mitigation mechanism for a particular application. We open-source DAMOV and the complete source code for our new characterization methodology at https://github.com/CMU-SAFARI/DAMOV.

#### SAFARI

#### https://arxiv.org/pdf/2105.03725.pdf

### Results So Far (2021-2022)

- DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks [IEEE Access 2021]

- Benchmarking a New Paradigm: Experimental Analysis and Characterization of a Real Processing-in-Memory System [IEEE Access 2022]

- Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks [PACT 2021]

- Enabling High-Performance and Energy-Efficient Hybrid Transactional/Analytical Databases with Hardware/Software Cooperation [ICDE 2022]

- FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications [IEEE Micro 2021]

### Eliminating the Adoption Barriers

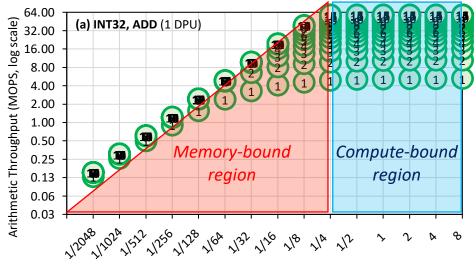

# Processing-in-Memory in the Real World

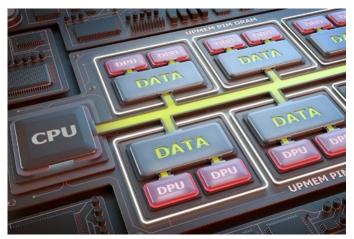

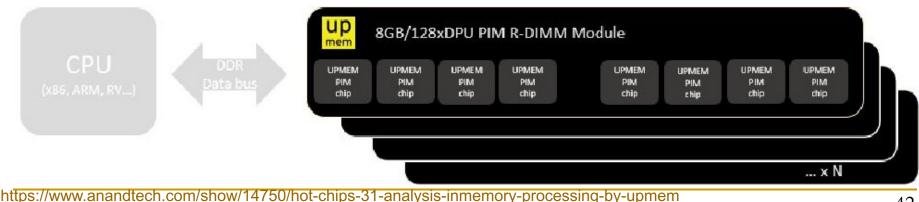

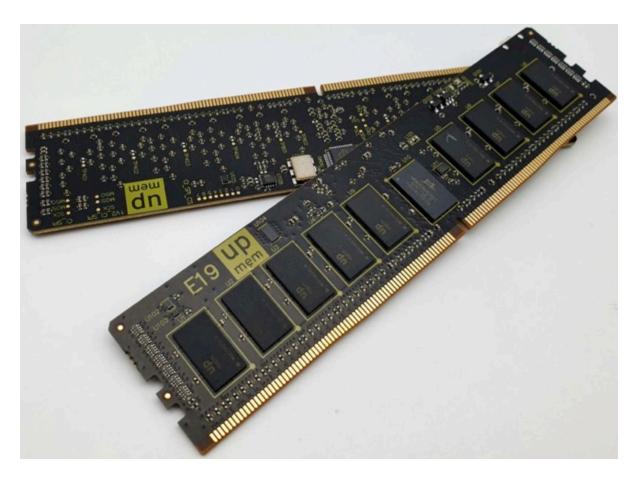

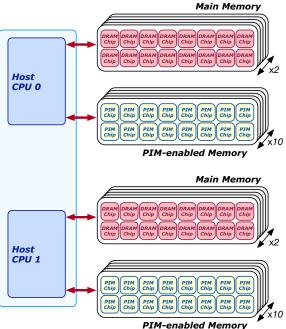

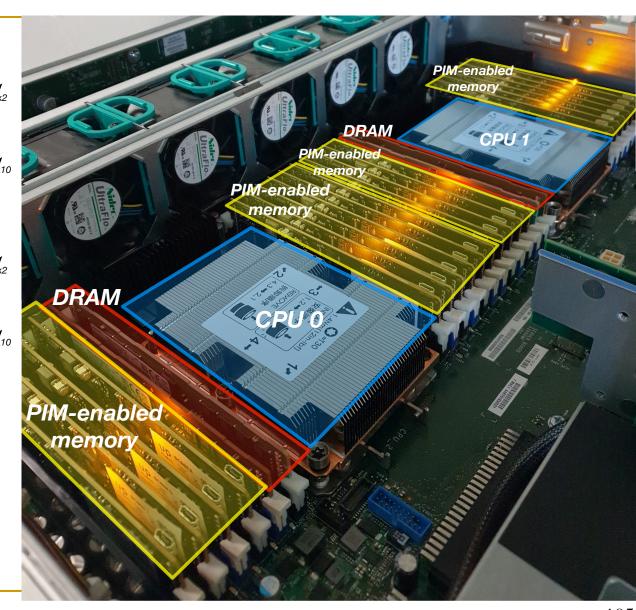

### UPMEM Processing-in-DRAM Engine (2019)

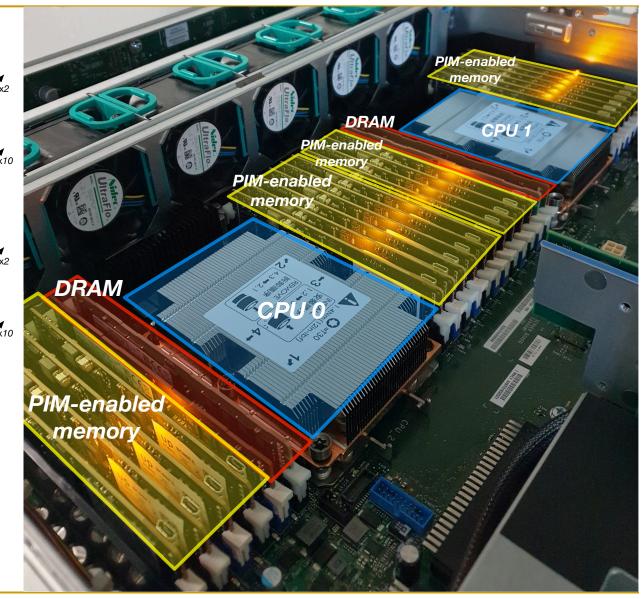

### Processing in DRAM Engine

Includes standard DIMM modules, with a large number of DPU processors combined with DRAM chips.

### Replaces standard DIMMs

- DDR4 R-DIMM modules

- 8GB+128 DPUs (16 PIM chips)

- Standard 2x-nm DRAM process

Large amounts of compute & memory bandwidth

https://www.upmem.com/video-upmem-presenting-its-true-processing-in-memory-solution-hot-chips-2019/

## **UPMEM Memory Modules**

- E19: 8 chips DIMM (1 rank). DPUs @ 267 MHz

- P21: 16 chips DIMM (2 ranks). DPUs @ 350 MHz

## 2,560-DPU Processing-in-Memory System

#### Benchmarking a New Paradigm: An Experimental Analysis of a Real Processing-in-Memory Architecture

JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland IZZAT EL HAJJ, Amerian University of Beruti, Lebanon IVAN FERNANDEZ, ETH Zürich, Switzerland and University of Malaga, Spain CHRISTINA GIANNOULA, ETH Zürich, Switzerland and NTUA, Greece GERALDO F. OLIVEIRA, ETH Zürich, Switzerland ONUR MUTLU, ETH Zürich, Switzerland

Many modern workloads, such as neural networks, databases, and graph processing, are fundamentally memory-bound for such workloads, the data movement between main memory and CPU cores imposes a significant overhead in terms of both latency and energy. A major reason is that this communication happense through a narrow bus with high latency and limited bandwidth, and the low data reuse in memory-bound workloads is insufficient to amorize the cost of main memory ancess. Fundamentally addressing this data movement builteneck requires a paradigm where the memory system assumes an active role in computing by integrating processing capabilities. This paradigm is known as *processing-in-memory* (PdM).

Recent research explores different forms of PIM architectures, motivated by the emergence of new 3Dstacked memory technologies that integrate memory with a logic layer where processing elements can be easily placed. Past works evaluate these architectures in simulation or, at best, with simplified hardware prototypes. In contrast, the UPMEM company has designed and manufactured the first publicly-available real-world PIM architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called DRAM Processing Units (DPUs), integrated in the same chip.

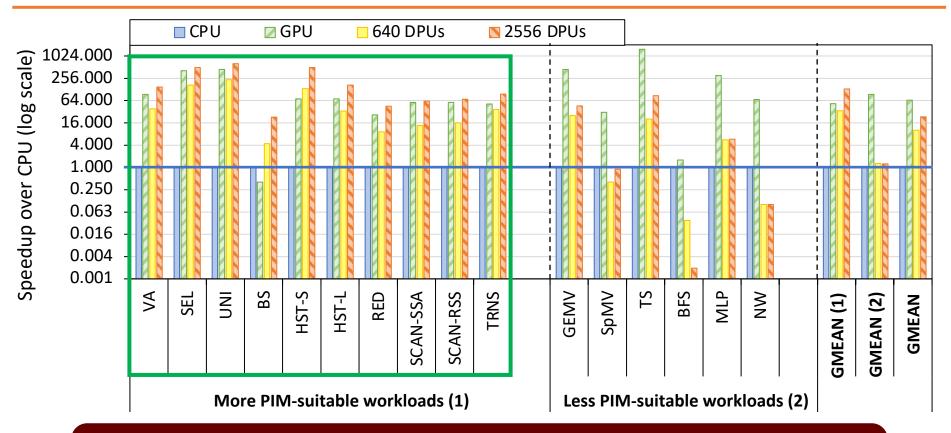

This paper provides the first comprehensive analysis of the first publicly-available real-world PIM architecture. We make two evolution through Strik, we conduct an experimental characterization of the UPMEM-based PIM system using microbenchmarks to assess various architecture limits such as compute throughput and memory bandwisht, yielding new insights. Second, we present PMU (*Decessing in-Memory benchmarks*), a benchmark suite of 16 workloads from different application domains (e.g., denne/sparse linear algebra, dathases, data analytics, graph processing, neural networks, bioinformatics, image processing), which we identify as memory-bound. We evaluate the performance and scaling characteristics of PtM benchmarks on the UPMEM PIM architecture, and compare their performance and energy consumption to their stateof-the-art CPU and CPU counterparts. Our extensive evaluation conducted on two real UPMEM-based PIM systems with 64 and 2550 PUP sproids new insights about satiabality of different workloads to the PIM systems reason of and 2550 PUP sorvides new insights about satiabality of different workloads to the PIM systems reason of Suture PIM systems.

https://arxiv.org/pdf/2105.03814.pdf

### More on the UPMEM PIM System

https://www.youtube.com/watch?v=Sscy1Wrr22A&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN&index=26

### UPMEM PIM System Summary & Analysis

Juan Gomez-Luna, Izzat El Hajj, Ivan Fernandez, Christina Giannoula, Geraldo F. Oliveira, and Onur Mutlu, "Benchmarking Memory-Centric Computing Systems: Analysis of Real **Processing-in-Memory Hardware**" Invited Paper at Workshop on Computing with Unconventional Technologies (CUT), Virtual, October 2021. [arXiv version] [PrIM Benchmarks Source Code] [Slides (pptx) (pdf)] [Talk Video (37 minutes)] [Lightning Talk Video (3 minutes)]

### Benchmarking Memory-Centric Computing Systems: Analysis of Real Processing-in-Memory Hardware

Juan Gómez-Luna ETH Zürich

Izzat El Hajj American University of Beirut

University of Malaga

Ivan Fernandez Christina Giannoula Geraldo F. Oliveira Onur Mutlu National Technical University of Athens

ETH Zürich ETH Zürich

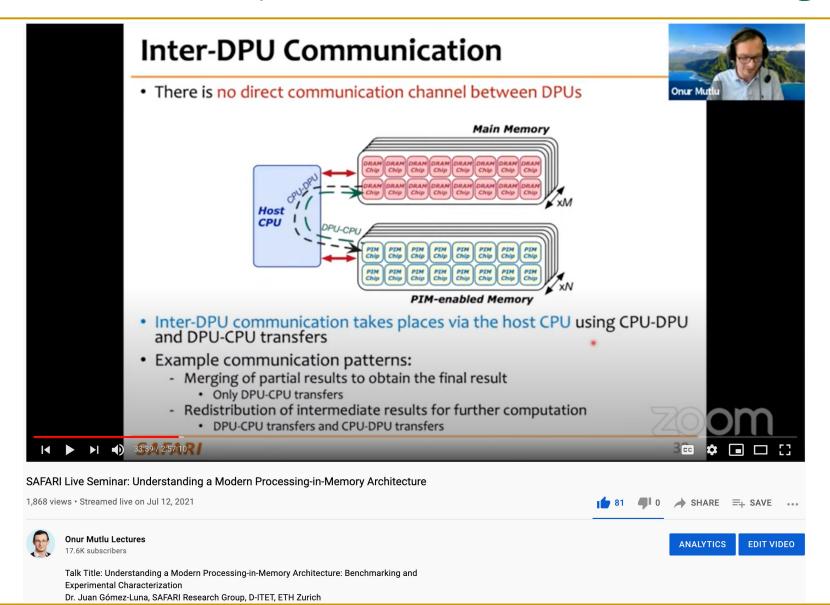

## Understanding a Modern Processing-in-Memory Architecture:

### **Benchmarking and Experimental Characterization**

<u>Juan Gómez Luna</u>, Izzat El Hajj, Ivan Fernandez, Christina Giannoula, Geraldo F. Oliveira, Onur Mutlu

https://arxiv.org/pdf/2105.03814.pdf https://github.com/CMU-SAFARI/prim-benchmarks

## **Executive Summary**

- Data movement between memory/storage units and compute units is a major contributor to execution time and energy consumption

- Processing-in-Memory (PIM) is a paradigm that can tackle the data movement bottleneck

- Though explored for +50 years, technology challenges prevented the successful materialization

- UPMEM has designed and fabricated the first publicly-available real-world PIM architecture

- DDR4 chips embedding in-order multithreaded DRAM Processing Units (DPUs)

- Our work:

- Introduction to UPMEM programming model and PIM architecture

- Microbenchmark-based characterization of the DPU

- Benchmarking and workload suitability study

- Main contributions:

- Comprehensive characterization and analysis of the first commercially-available PIM architecture

- PrIM (Processing-In-Memory) benchmarks:

- 16 workloads that are memory-bound in conventional processor-centric systems

- Strong and weak scaling characteristics

- Comparison to state-of-the-art CPU and GPU

- Takeaways:

- Workload characteristics for PIM suitability

- Programming recommendations

- Suggestions and hints for hardware and architecture designers of future PIM systems

- PrIM: (a) programming samples, (b) evaluation and comparison of current and future PIM systems

## **PrIM Benchmarks: Application Domains**

| Domain                | Benchmark                     | Short name |

|-----------------------|-------------------------------|------------|

| Dense linear algebra  | Vector Addition               | VA         |

|                       | Matrix-Vector Multiply        | GEMV       |

| Sparse linear algebra | Sparse Matrix-Vector Multiply | SpMV       |

| Databases             | Select                        | SEL        |

|                       | Unique                        | UNI        |

| Data analytics        | Binary Search                 | BS         |

|                       | Time Series Analysis          | TS         |

| Graph processing      | Breadth-First Search          | BFS        |

| Neural networks       | Multilayer Perceptron         | MLP        |

| Bioinformatics        | Needleman-Wunsch              | NW         |

| Image processing      | Image histogram (short)       | HST-S      |

|                       | Image histogram (large)       | HST-L      |

| Parallel primitives   | Reduction                     | RED        |

|                       | Prefix sum (scan-scan-add)    | SCAN-SSA   |

|                       | Prefix sum (reduce-scan-scan) | SCAN-RSS   |

|                       | Matrix transposition          | TRNS       |

## **PrIM Benchmarks are Open Source**

- All microbenchmarks, benchmarks, and scripts

- <u>https://github.com/CMU-SAFARI/prim-benchmarks</u>

| % main * prim-benchmarks / README.md     Image: Second Secon | CMU-SAFARI / prim-benchmark         | S     | 💿 Unwato          | th → 2 🖧 Star 2 😵 Fork 1               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|-------------------|----------------------------------------|

| <ul> <li>Juan Gomez Luna PrIM first commit</li> <li>Latest commit 3de4b49 9 days ago  History</li> <li>At 1 contributor</li> <li>168 lines (132 sloc) 5.79 KB</li> <li>Raw Blame  Blame  I &lt; 1</li> </ul> PrIM (Processing-In-Memory Benchmarks) PrIM is the first benchmark suite for a real-world processing-in-memory (PIM) architecture. PrIM is developed to evaluate, analyze, and characterize the first publicly-available real-world processing-in-memory (PIM) architecture, the UPMEM PIM architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called DRAM Processing Units (DPUs), integrated in the same chip. PrIM provides a common set of workloads to evaluate the UPMEM PIM architecture with and can be useful for programming, architecture and system researchers all alike to improve multiple aspects of future PIM hardware and software. The workloads have different characteristics, exhibiting heterogeneity in their memory access patterns, operations and data types, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <> Code 🕑 Issues 👘 Pull requests    |       | 🕮 Wiki 🕕 Security | 🖂 Insights 🛛 🕸 Settings                |

| Ra 1 contributor         Image: Interpret to the state of the sta           | ه main → prim-benchmarks / READ     | ME.md |                   | Go to file                             |

| Id8 lines (132 sloc) 5.79 KB Raw Blame C & C PrIM (Processing-In-Memory Benchmarks) PrIM is the first benchmark suite for a real-world processing-in-memory (PIM) architecture. PrIM is developed to evaluate, analyze, and characterize the first publicly-available real-world processing-in-memory (PIM) architecture, the UPMEM PIM architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called DRAM Processing Units (DPUs), integrated in the same chip. PrIM provides a common set of workloads to evaluate the UPMEM PIM architecture with and can be useful for programming, architecture and system researchers all alike to improve multiple aspects of future PIM hardware and software. The workloads have different characteristics, exhibiting heterogeneity in their memory access patterns, operations and data types, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 💿 Juan Gomez Luna PrIM first commit |       | Late              | st commit 3de4b49 9 days ago 🕤 History |

| PrIM (Processing-In-Memory Benchmarks)         PrIM is the first benchmark suite for a real-world processing-in-memory (PIM) architecture. PrIM is developed to evaluate, analyze, and characterize the first publicly-available real-world processing-in-memory (PIM) architecture, the UPMEM PIM architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called DRAM Processing Units (DPUs), integrated in the same chip.         PrIM provides a common set of workloads to evaluate the UPMEM PIM architecture with and can be useful for programming, architecture and system researchers all alike to improve multiple aspects of future PIM hardware and software. The workloads have different characteristics, exhibiting heterogeneity in their memory access patterns, operations and data types, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | २२ 1 contributor                    |       |                   |                                        |

| PrIM is the first benchmark suite for a real-world processing-in-memory (PIM) architecture. PrIM is developed to evaluate,<br>analyze, and characterize the first publicly-available real-world processing-in-memory (PIM) architecture, the UPMEM PIM<br>architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called<br>DRAM Processing Units (DPUs), integrated in the same chip.<br>PrIM provides a common set of workloads to evaluate the UPMEM PIM architecture with and can be useful for programming,<br>architecture and system researchers all alike to improve multiple aspects of future PIM hardware and software. The workloads<br>have different characteristics, exhibiting heterogeneity in their memory access patterns, operations and data types, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | i≘ 168 lines (132 sloc) 5.79 KB     |       |                   | Raw Blame 🖵 🖉 🗓                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |       |                   |                                        |

### Benchmarking a New Paradigm: Experimental Analysis and Characterization of a Real Processing-in-Memory System

JUAN GÓMEZ-LUNA<sup>1</sup>, IZZAT EL HAJJ<sup>2</sup>, IVAN FERNANDEZ<sup>1,3</sup>, CHRISTINA GIANNOULA<sup>1,4</sup>, GERALDO F. OLIVEIRA<sup>1</sup>, AND ONUR MUTLU<sup>1</sup>

<sup>1</sup>ETH Zürich

<sup>2</sup>American University of Beirut

<sup>3</sup>University of Malaga

<sup>4</sup>National Technical University of Athens

Corresponding author: Juan Gómez-Luna (e-mail: juang@ethz.ch).

https://doi.org/10.1109/ACCESS.2022.3174101 https://github.com/CMU-SAFARI/prim-benchmarks

### **Observations, Recommendations, Takeaways**

#### **GENERAL PROGRAMMING RECOMMENDATIONS**

- 1. Execute on the *DRAM Processing Units* (*DPUs*) **portions of parallel code** that are as long as possible.

- 2. Split the workload into **independent data blocks**, which the DPUs operate on independently.

- 3. Use **as many working DPUs** in the system as possible.

- 4. Launch at least **11** *tasklets* (i.e., software threads) per DPU.

#### **PROGRAMMING RECOMMENDATION 1**

For data movement between the DPU's MRAM bank and the WRAM, **use large DMA transfer sizes when all the accessed data is going to be used**.

#### **KEY OBSERVATION 7**

Larger CPU-DPU and DPU-CPU transfers between the host main memory and the DRAM Processing Unit's Main memory (MRAM) banks result in higher sustained bandwidth.

#### **KEY TAKEAWAY 1**

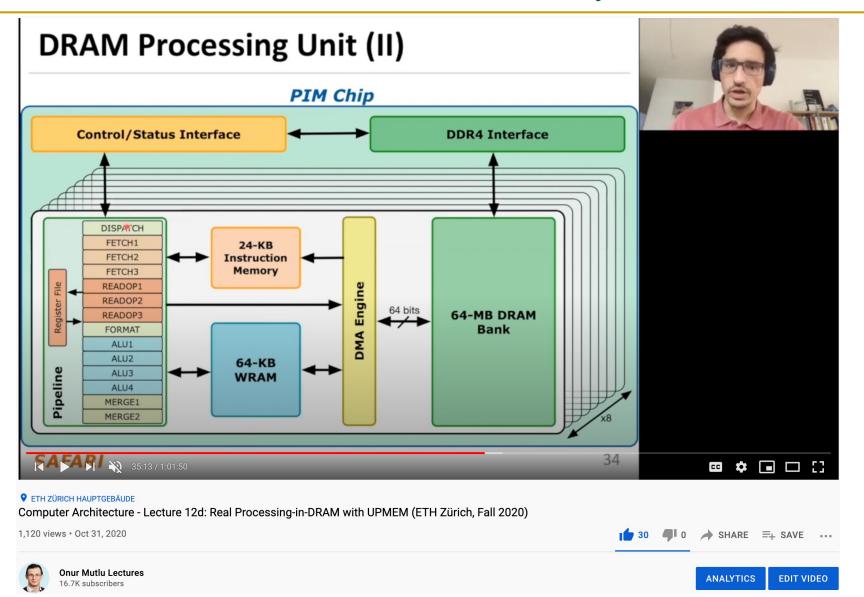

The UPMEM PIM architecture is fundamentally compute bound. As a result, the most suitable work- loads are memory-bound.

## Outline

- Introduction

- Accelerator Model

- UPMEM-based PIM System Overview

- UPMEM PIM Programming

- Vector Addition

- CPU-DPU Data Transfers

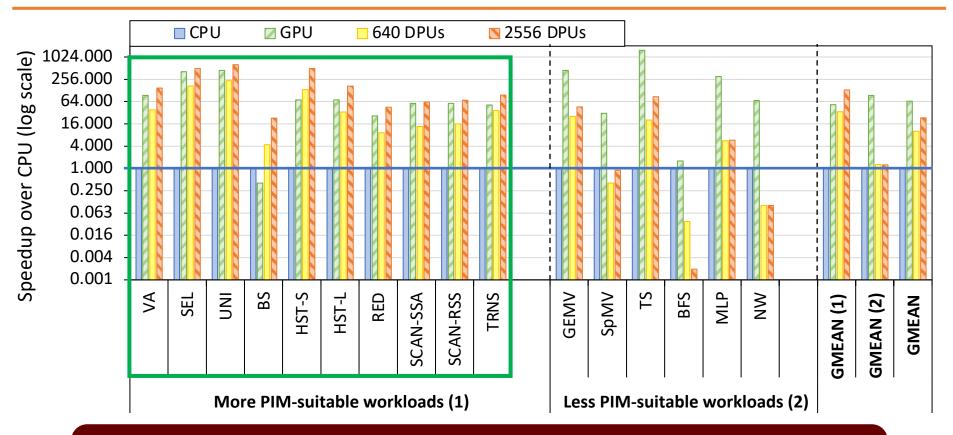

- Inter-DPU Communication

- CPU-DPU/DPU-CPU Transfer Bandwidth

- DRAM Processing Unit

- Arithmetic Throughput

- WRAM and MRAM Bandwidth

- PrIM Benchmarks

- Roofline Model

- Benchmark Diversity

- Evaluation

- Strong and Weak Scaling

- Comparison to CPU and GPU

Key Takeaways

## Key Takeaway 1

Operational Intensity (OP/B)

The throughput saturation point is as low as ¼ OP/B, i.e., 1 integer addition per every 32-bit element fetched

#### **KEY TAKEAWAY 1**

**The UPMEM PIM architecture is fundamentally compute bound.** As a result, **the most suitable workloads are memory-bound.**

## Key Takeaway 2

#### **KEY TAKEAWAY 2**

The most well-suited workloads for the UPMEM PIM architecture use no arithmetic operations or use only simple operations (e.g., bitwise operations and integer addition/subtraction).

## Key Takeaway 3

#### **KEY TAKEAWAY 3**

The most well-suited workloads for the UPMEM PIM architecture require little or no communication across DPUs (inter-DPU communication).

#### **KEY TAKEAWAY 4**

• UPMEM-based PIM systems **outperform state-of-the-art CPUs in terms of performance and energy efficiency on most of PrIM benchmarks.**

• UPMEM-based PIM systems **outperform state-of-the-art GPUs on a majority of PrIM benchmarks**, and the outlook is even more positive for future PIM systems.

• UPMEM-based PIM systems are **more energy-efficient than state**of-the-art CPUs and GPUs on workloads that they provide performance improvements over the CPUs and the GPUs.

### Benchmarking a New Paradigm: Experimental Analysis and Characterization of a Real Processing-in-Memory System

JUAN GÓMEZ-LUNA<sup>1</sup>, IZZAT EL HAJJ<sup>2</sup>, IVAN FERNANDEZ<sup>1,3</sup>, CHRISTINA GIANNOULA<sup>1,4</sup>, GERALDO F. OLIVEIRA<sup>1</sup>, AND ONUR MUTLU<sup>1</sup>

<sup>1</sup>ETH Zürich

<sup>2</sup>American University of Beirut

<sup>3</sup>University of Malaga

<sup>4</sup>National Technical University of Athens

Corresponding author: Juan Gómez-Luna (e-mail: juang@ethz.ch).

https://doi.org/10.1109/ACCESS.2022.3174101 https://github.com/CMU-SAFARI/prim-benchmarks

## Understanding a Modern Processing-in-Memory Architecture:

### **Benchmarking and Experimental Characterization**

<u>Juan Gómez Luna</u>, Izzat El Hajj, Ivan Fernandez, Christina Giannoula, Geraldo F. Oliveira, Onur Mutlu

el1goluj@gmail.com

<u>https://arxiv.org/pdf/2105.03814.pdf</u> <u>https://github.com/CMU-SAFARI/prim-benchmarks</u>

### Experimental Analysis of the UPMEM PIM Engine

### Benchmarking a New Paradigm: An Experimental Analysis of a Real Processing-in-Memory Architecture

JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland IZZAT EL HAJJ, American University of Beirut, Lebanon IVAN FERNANDEZ, ETH Zürich, Switzerland and University of Malaga, Spain CHRISTINA GIANNOULA, ETH Zürich, Switzerland and NTUA, Greece GERALDO F. OLIVEIRA, ETH Zürich, Switzerland ONUR MUTLU, ETH Zürich, Switzerland

Many modern workloads, such as neural networks, databases, and graph processing, are fundamentally memory-bound. For such workloads, the data movement between main memory and CPU cores imposes a significant overhead in terms of both latency and energy. A major reason is that this communication happens through a narrow bus with high latency and limited bandwidth, and the low data reuse in memory-bound workloads is insufficient to amortize the cost of main memory access. Fundamentally addressing this *data movement bottleneck* requires a paradigm where the memory system assumes an active role in computing by integrating processing capabilities. This paradigm is known as *processing-in-memory (PIM*).

Recent research explores different forms of PIM architectures, motivated by the emergence of new 3Dstacked memory technologies that integrate memory with a logic layer where processing elements can be easily placed. Past works evaluate these architectures in simulation or, at best, with simplified hardware prototypes. In contrast, the UPMEM company has designed and manufactured the first publicly-available real-world PIM architecture. The UPMEM PIM architecture combines traditional DRAM memory arrays with general-purpose in-order cores, called *DRAM Processing Units* (*DPUs*), integrated in the same chip.

This paper provides the first comprehensive analysis of the first publicly-available real-world PIM architecture. We make two key contributions. First, we conduct an experimental characterization of the UPMEM-based PIM system using microbenchmarks to assess various architecture limits such as compute throughput and memory bandwidth, yielding new insights. Second, we present *PrIM* (*Processing-In-Memory benchmarks*), a benchmark suite of 16 workloads from different application domains (e.g., dense/sparse linear algebra, databases, data analytics, graph processing, neural networks, bioinformatics, image processing), which we identify as memory-bound. We evaluate the performance and scaling characteristics of PrIM benchmarks on the UPMEM PIM architecture, and compare their performance and energy consumption to their stateof-the-art CPU and GPU counterparts. Our extensive evaluation conducted on two real UPMEM-based PIM systems with 640 and 2,556 DPUs provides new insights about suitability of different workloads to the PIM system, programming recommendations for software designers, and suggestions and hints for hardware and architecture designers of future PIM systems.

#### https://arxiv.org/pdf/2105.03814.pdf

### More on Analysis of the UPMEM PIM Engine

#### https://www.youtube.com/watch?v=D8Hjy2iU9I4&list=PL5Q2soXY2Zi\_tOTAYm--dYByNPL7JhwR9

### More on Analysis of the UPMEM PIM Engine

#### Understanding a Modern Processing-in-Memory Arch: Benchmarking & Experimental Characterization; 21m

#### https://www.youtube.com/watch?v=Pp9jSU2b9oM&list=PL5Q2soXY2Zi8\_VVChACnON4sfh2bJ5IrD&index=159

### More on PRIM Benchmarks

Juan Gomez-Luna, Izzat El Hajj, Ivan Fernandez, Christina Giannoula, Geraldo F. Oliveira, and Onur Mutlu, **"Benchmarking a New Paradigm: An Experimental Analysis of a Real Processing-in-Memory** Architecture" Preprint in arXiv, 9 May 2021. [arXiv preprint] PrIM Benchmarks Source Code Slides (pptx) (pdf) [Long Talk Slides (pptx) (pdf)] [Short Talk Slides (pptx) (pdf)] [SAFARI Live Seminar Slides (pptx) (pdf)] [SAFARI Live Seminar Video (2 hrs 57 mins)] [Lightning Talk Video (3 minutes)]

### UPMEM PIM System Summary & Analysis

Juan Gomez-Luna, Izzat El Hajj, Ivan Fernandez, Christina Giannoula, Geraldo F. Oliveira, and Onur Mutlu, "Benchmarking Memory-Centric Computing Systems: Analysis of Real **Processing-in-Memory Hardware**" Invited Paper at Workshop on Computing with Unconventional Technologies (CUT), Virtual, October 2021. [arXiv version] [PrIM Benchmarks Source Code] [Slides (pptx) (pdf)] [Talk Video (37 minutes)] [Lightning Talk Video (3 minutes)]

### Benchmarking Memory-Centric Computing Systems: Analysis of Real Processing-in-Memory Hardware

Juan Gómez-Luna ETH Zürich

Izzat El Hajj American University of Beirut

University of Malaga

Ivan Fernandez Christina Giannoula Geraldo F. Oliveira Onur Mutlu National Technical University of Athens

ETH Zürich ETH Zürich

### Results So Far (2021-2022)

- DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks [IEEE Access 2021]

- Benchmarking a New Paradigm: Experimental Analysis and Characterization of a Real Processing-in-Memory System [IEEE Access 2022]

- Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks [PACT 2021]

- Enabling High-Performance and Energy-Efficient Hybrid Transactional/Analytical Databases with Hardware/Software Cooperation [ICDE 2022]

- FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications [IEEE Micro 2021]

### Data-Centric Neural Network Inference

Amirali Boroumand, Saugata Ghose, Berkin Akin, Ravi Narayanaswami, Geraldo F. Oliveira, Xiaoyu Ma, Eric Shiu, and Onur Mutlu,

"Google Neural Network Models for Edge Devices: Analyzing and

<u>Mitigating Machine Learning Inference Bottlenecks"</u>

Proceedings of the <u>30th International Conference on Parallel Architectures and</u>

<u>Compilation Techniques</u> (PACT), Virtual, September 2021.

[Slides (pptx) (pdf)]

[Talk Video (14 minutes)]

#### **Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks**

Amirali Boroumand\*\*Saugata Ghose\*Berkin Akin\*Ravi Narayanaswami\*Geraldo F. Oliveira\*Xiaoyu Ma\*Eric Shiu\*Onur Mutlu\*\*\* Carnegie Mellon Univ.\* Stanford Univ.\* Univ. of Illinois Urbana-Champaign\* Google\* ETH Zürich

### Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks

Amirali BoroumandSaugata GhoseBerkin AkinRavi NarayanaswamiGeraldo F. OliveiraXiaoyu MaEric ShiuOnur Mutlu

**PACT 2021**

## **Executive Summary**

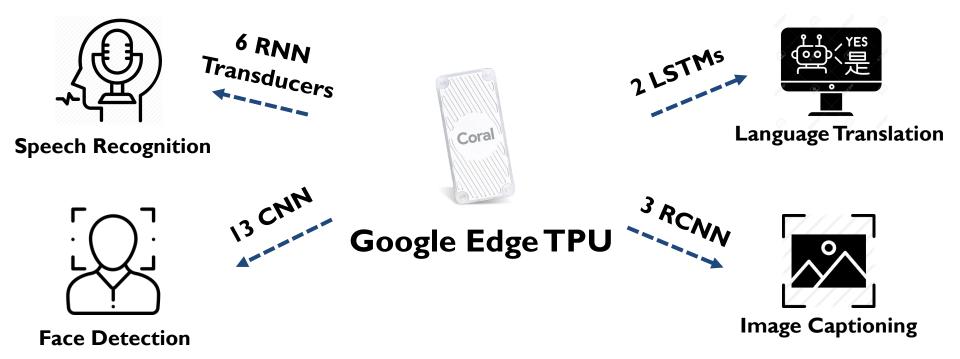

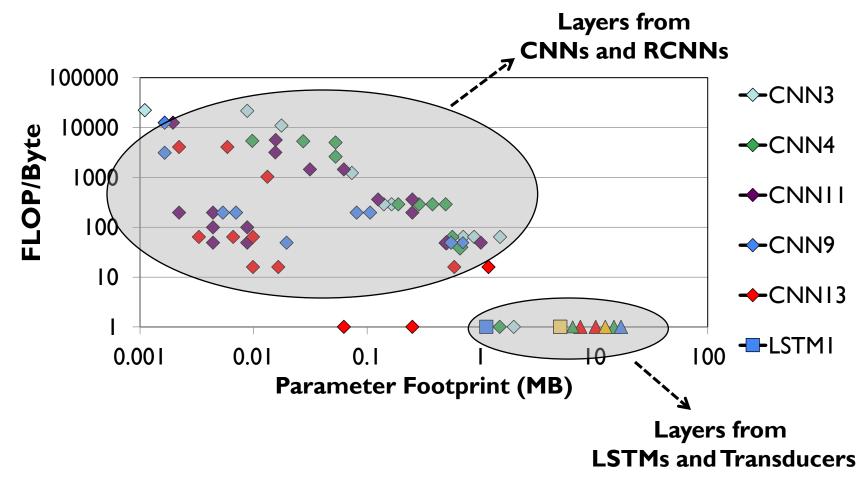

#### <u>Context</u>: We extensively analyze a state-of-the-art edge ML accelerator (Google Edge TPU) using 24 Google edge models

- Wide range of models (CNNs, LSTMs, Transducers, RCNNs)

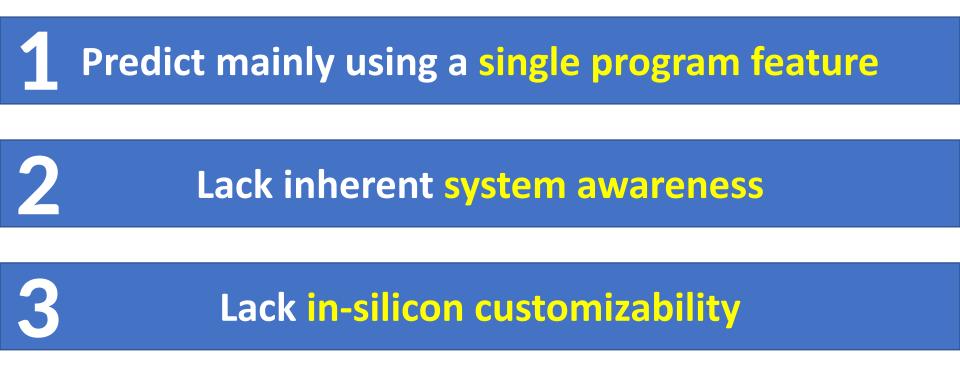

#### **Problem:** The Edge TPU accelerator suffers from three challenges:

- It operates significantly below its peak throughput

- It operates significantly below its theoretical energy efficiency

- It inefficiently handles memory accesses

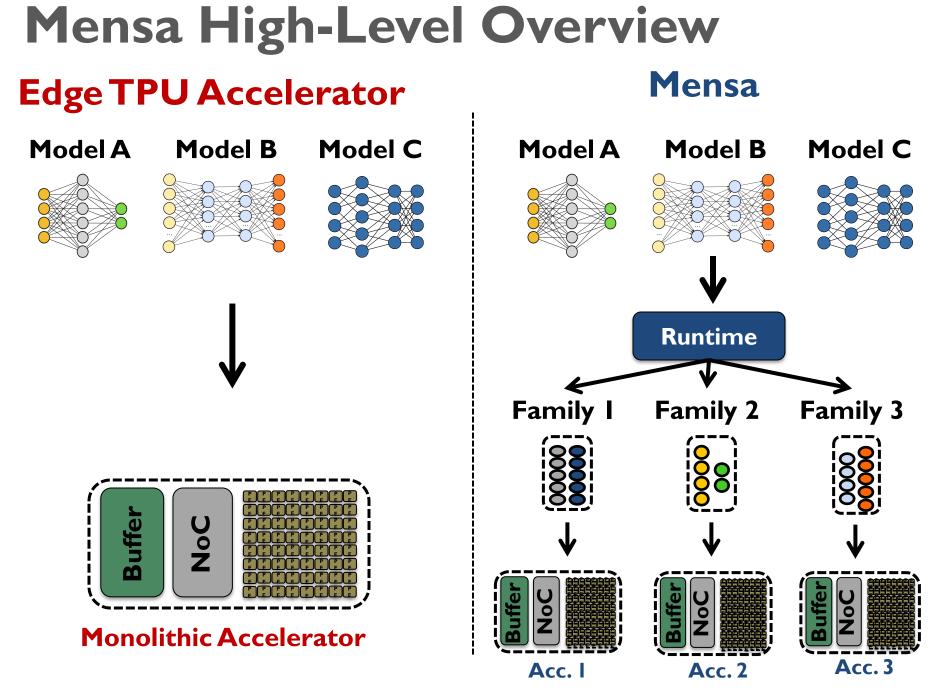

## <u>Key Insight</u>: These shortcomings arise from the monolithic design of the Edge TPU accelerator

- The Edge TPU accelerator design does not account for layer heterogeneity

#### Key Mechanism: A new framework called Mensa

Mensa consists of heterogeneous accelerators whose dataflow and hardware are specialized for specific families of layers

#### Key Results: We design a version of Mensa for Google edge ML models

- Mensa improves performance and energy by 3.0X and 3.1X

- Mensa reduces cost and improves area efficiency

## **Google Edge NN Models**

### We analyze inference execution using 24 edge NN models

## **Diversity Across the Models**

### Insight I: there is significant variation in terms of layer characteristics across the models

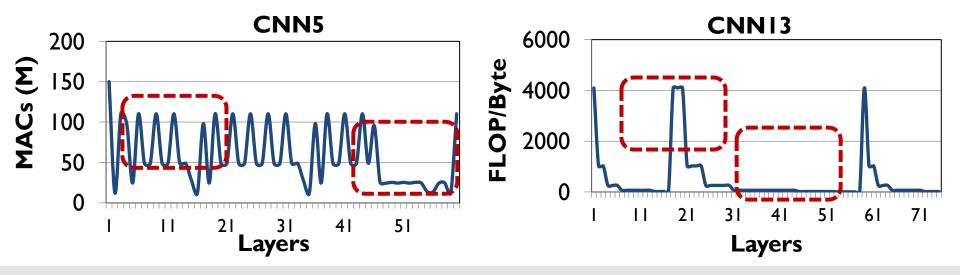

## **Diversity Within the Models**

Insight 2: even within each model, layers exhibit significant variation in terms of layer characteristics

For example, our analysis of edge CNN models shows:

Variation in MAC intensity: up to 200x across layers

Variation in FLOP/Byte: up to 244x across layers

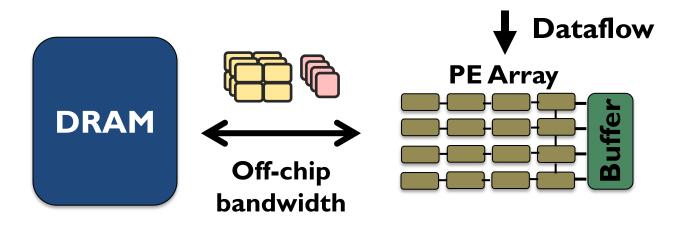

### **Root Cause of Accelerator Challenges**

The key components of Google Edge TPU are completely oblivious to layer heterogeneity

Edge accelerators typically take a monolithic approach: equip the accelerator with an over-provisioned <u>PE array</u> and <u>on-chip buffer</u>, a rigid <u>dataflow</u>, and fixed <u>off-chip bandwidth</u>

While this approach might work for a specific group of layers, it fails to efficiently execute inference across a wide variety of edge models

# Mensa Framework

**Goal:** design an edge accelerator that can efficiently run inference across a wide range of different models and layers

### Instead of running the entire NN model on a monolithic accelerator:

Mensa: a new acceleration framework for edge NN inference

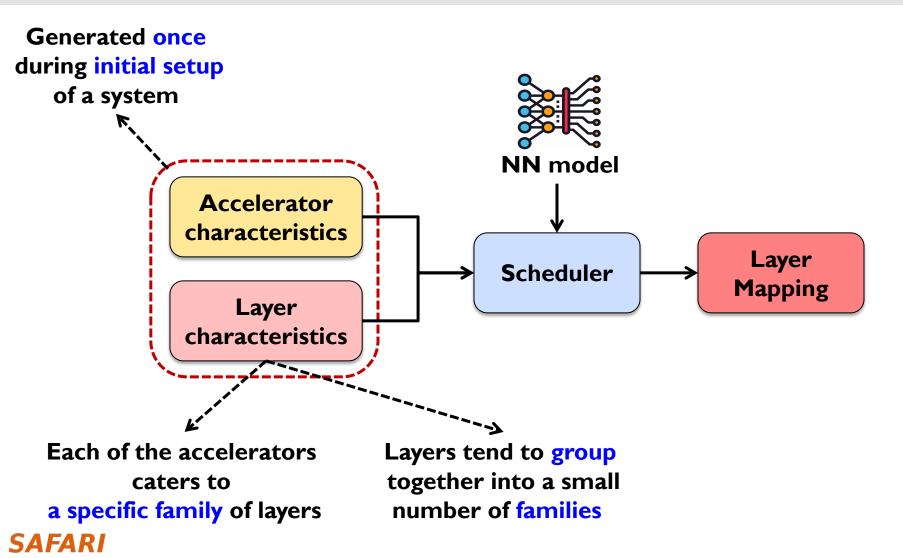

# Mensa Runtime Scheduler

The goal of Mensa's software runtime scheduler is to identify which accelerator each layer in an NN model should run on

# Mensa Runtime Scheduler

The goal of Mensa's software runtime scheduler is to identify which accelerator each layer in an NN model should run on

Generated once during initial setup

# Mensa: Highly-Efficient ML Inference

Amirali Boroumand, Saugata Ghose, Berkin Akin, Ravi Narayanaswami, Geraldo F. Oliveira, Xiaoyu Ma, Eric Shiu, and Onur Mutlu,

"Google Neural Network Models for Edge Devices: Analyzing and

Mitigating Machine Learning Inference Bottlenecks"

Proceedings of the 30th International Conference on Parallel Architectures and

Compilation Techniques (PACT), Virtual, September 2021.

[Slides (pptx) (pdf)]

[Talk Video (14 minutes)]

### **Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks**

Amirali Boroumand\*\*Saugata Ghose\*Berkin Akin\*Ravi Narayanaswami\*Geraldo F. Oliveira\*Xiaoyu Ma\*Eric Shiu\*Onur Mutlu\*\*\* Carnegie Mellon Univ.\* Stanford Univ.\* Univ. of Illinois Urbana-Champaign\* Google\* ETH Zürich

# Results So Far (2021-2022)

- DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks [IEEE Access 2021]

- Benchmarking a New Paradigm: Experimental Analysis and Characterization of a Real Processing-in-Memory System [IEEE Access 2022]

- Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks [PACT 2021]

- Enabling High-Performance and Energy-Efficient Hybrid

Transactional/Analytical Databases with Hardware/Software

Cooperation [ICDE 2022]

- FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications [IEEE Micro 2021]

# Accelerating HTAP Database Systems

Appears in ICDE 2022

### **Polynesia: Enabling High-Performance and Energy-Efficient Hybrid Transactional/Analytical Databases** with Hardware/Software Co-Design

Amirali Boroumand<sup>†</sup>

Saugata Ghose<sup> $\diamond$ </sup> Geraldo F. Oliveira<sup>‡</sup> Onur Mutlu<sup>‡</sup> <sup>†</sup>Google <sup>•</sup>Univ. of Illinois Urbana-Champaign <sup>‡</sup>ETH Zürich

https://arxiv.org/pdf/2204.11275.pdf

# Results So Far (2021-2022)

- DAMOV: A New Methodology and Benchmark Suite for Evaluating Data Movement Bottlenecks [IEEE Access 2021]

- Benchmarking a New Paradigm: Experimental Analysis and Characterization of a Real Processing-in-Memory System [IEEE Access 2022]

- Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks [PACT 2021]

- Enabling High-Performance and Energy-Efficient Hybrid Transactional/Analytical Databases with Hardware/Software Cooperation [ICDE 2022]

FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications [IEEE Micro 2021]

# FPGA-based Processing Near Memory

Gagandeep Singh, Mohammed Alser, Damla Senol Cali, Dionysios Diamantopoulos, Juan Gómez-Luna, Henk Corporaal, and Onur Mutlu, "FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications" IEEE Micro (IEEE MICRO), 2021.

# FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications

Gagandeep Singh<sup>◊</sup> Mohammed Alser<sup>◊</sup> Damla Senol Cali<sup>⋈</sup>

**Dionysios Diamantopoulos**<sup>∇</sup> **Juan Gómez-Luna**<sup>◊</sup>

Henk Corporaal<sup>★</sup> Onur Mutlu<sup>◊ ⋈</sup>

◇ETH Zürich <sup>™</sup>Carnegie Mellon University

\*Eindhoven University of Technology <sup>▽</sup>IBM Research Europe

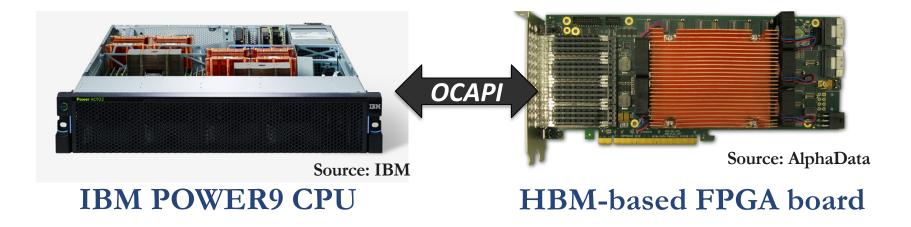

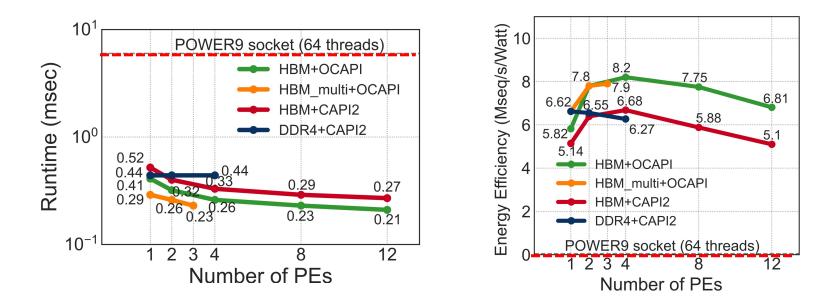

# Near-Memory Acceleration Using FPGAs

### **Near-HBM FPGA-based accelerator**

Two communication technologies: CAPI2 and OCAPI Two memory technologies: DDR4 and HBM Two workloads: Weather Modeling and Genome Analysis

# Performance & Energy Greatly Improve

5-27× performance vs. a 16-core (64-thread) IBM POWER9 CPU

12-133× energy efficiency vs. a 16-core (64-thread) IBM POWER9 CPU

### **HBM alleviates memory bandwidth contention vs. DDR4**

### We Need to Revisit the Entire Stack

| Problem            | , |

|--------------------|---|

| Aigorithm          |   |

| Program/Language   |   |

| System Software    |   |

| SW/HW Interface    |   |

| Micro-architecture |   |

| Logic              |   |

| Devices            |   |

| Electrons          |   |

### We can get there step by step

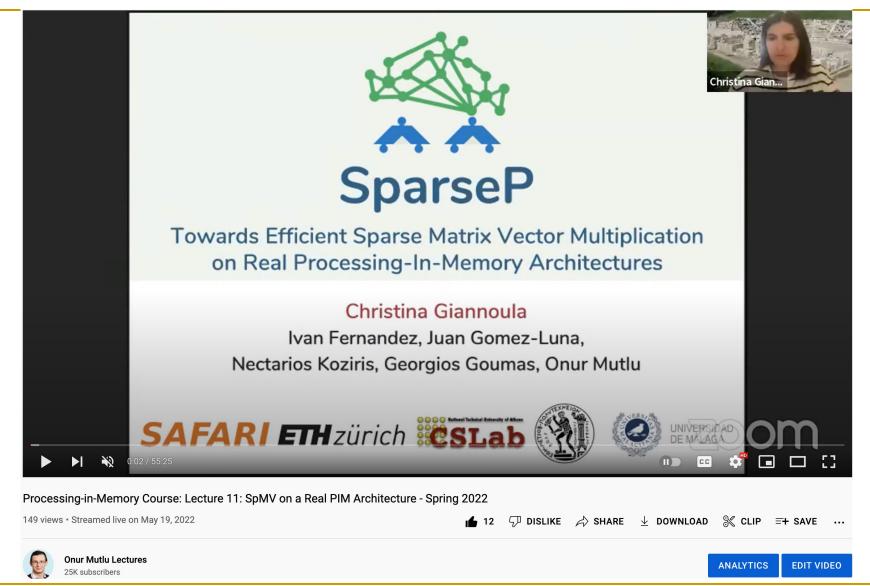

# Coming Up: SpMV on Real PIM Systems

### • To appear in SIGMETRICS 2022

### **SparseP:** Towards Efficient Sparse Matrix Vector Multiplication on Real Processing-In-Memory Systems

CHRISTINA GIANNOULA, ETH Zürich, Switzerland and National Technical University of Athens, Greece

IVAN FERNANDEZ, ETH Zürich, Switzerland and University of Malaga, Spain JUAN GÓMEZ-LUNA, ETH Zürich, Switzerland NECTARIOS KOZIRIS, National Technical University of Athens, Greece GEORGIOS GOUMAS, National Technical University of Athens, Greece ONUR MUTLU, ETH Zürich, Switzerland

> https://arxiv.org/pdf/2201.05072.pdf https://github.com/CMU-SAFARI/SparseP

# Coming Up: SpMV on Real PIM Systems

#### https://www.youtube.com/watch?v=5kaOsJKlGrE

# Coming Up: FPGA Framework for PuM

### PiDRAM: A Holistic End-to-end FPGA-based Framework for Processing-in-DRAM

Ataberk Olgun§†

Juan Gómez Luna<sup>§</sup> Konstantinos Kanellopoulos<sup>§</sup> Hasan Hassan<sup>§</sup> Oğuz Ergin<sup>†</sup> Onur Mutlu<sup>§</sup> <sup>§</sup>ETH Zürich <sup>†</sup>TOBB ETÜ <sup>\*</sup>BSC

Behzad Salami<sup>§\*</sup>

https://arxiv.org/pdf/2111.00082.pdf https://github.com/cmu-safari/pidram

# Comp Arch (Fall'21)

#### Fall 2021 Edition:

- https://safari.ethz.ch/architecture/fall2021/doku. php?id=schedule

- Fall 2020 Edition:

- https://safari.ethz.ch/architecture/fall2020/doku. php?id=schedule

#### Youtube Livestream (2021):

- https://www.youtube.com/watch?v=4yfkM\_5EFg o&list=PL5Q2soXY2Zi-Mnk1PxjEIG32HAGILkTOF

- Youtube Livestream (2020):

- https://www.youtube.com/watch?v=c3mPdZA-Fmc&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN

- Master's level course

- Taken by Bachelor's/Masters/PhD students

- Cutting-edge research topics + fundamentals in Computer Architecture

- 5 Simulator-based Lab Assignments

- Potential research exploration

- Many research readings

### https://www.youtube.com/onurmutlulectures

#### Fall 2021 Lectures & Schedule

Watch on 🕞 YouTub

| Week | Date          | Livestream    | Lecture                                                                   | Readings               | Lab          | HW          |

|------|---------------|---------------|---------------------------------------------------------------------------|------------------------|--------------|-------------|

| W1   | 30.09<br>Thu. | You the Live  | L1: Introduction and Basics                                               | Required<br>Mentioned  | Lab 1<br>Out | HW 0<br>Out |

|      | 01.10<br>Fri. | You Tube Live | L2: Trends, Tradeoffs and Design<br>Fundamentals<br>@(PDF) @(PPT)         | Required<br>Mentioned  |              |             |

| W2   | 07.10<br>Thu. | You Tibe Live | L3a: Memory Systems: Challenges and<br>Opportunities<br>ma(PDF) izm (PPT) | Described<br>Suggested |              | HW 1<br>Out |

|      |               |               | L3b: Course Info & Logistics                                              |                        |              |             |

|      |               |               | L3c: Memory Performance Attacks                                           | Described<br>Suggested |              |             |

|      | 08.10<br>Fri. |               | L4a: Memory Performance Attacks                                           | Described<br>Suggested | Lab 2<br>Out |             |

|      |               |               | L4b: Data Retention and Memory Refresh                                    | Described<br>Suggested |              |             |

|      |               |               | L4c: RowHammer<br>(PDF)   (PPT)                                           | Described<br>Suggested |              |             |

### PIM Course (Fall'21)

#### Fall 2021 Edition:

https://safari.ethz.ch/projects and semi nars/fall2021/doku.php?id=processing in memory

#### Youtube Livestream:

https://www.youtube.com/watch?v=9e4 Chnwdovo&list=PL5Q2soXY2Zi-841fUYYUK9EsXKhQKRPyX

#### Project course

- Taken by Bachelor's/Master's students

- Processing-in-Memory lectures

- Hands-on research exploration

- Many research readings

Lecture Video Playlist on YouTube

Secture Playlist

#### Fall 2021 Meetings/Schedule

| Week | Date          | Livestream    | Meeting                                                                       | Learning Materials                             | Assignments |

|------|---------------|---------------|-------------------------------------------------------------------------------|------------------------------------------------|-------------|

| W1   | 05.10<br>Tue. | You Tube Live | M1: P&S PIM Course Presentation<br>(PDF) (PPT)                                | Required Materials<br>Recommended<br>Materials | HW 0 Out    |

| W2   | 12.10<br>Tue. | You Tube Live | M2: Real-World PIM Architectures                                              |                                                |             |

| W3   | 19.10<br>Tue. | You Tube Live | M3: Real-World PIM Architectures II (PDF) (PDF)                               |                                                |             |

| W4   | 26.10<br>Tue. | You Tube Live | M4: Real-World PIM Architectures III a (PDF) a (PPT)                          |                                                |             |

| W5   | 02.11<br>Tue. | You Tube Live | M5: Real-World PIM Architectures IV                                           |                                                |             |

| W6   | 09.11<br>Tue. | You Tube Live | M6: End-to-End Framework for<br>Processing-using-Memory<br>(PDF) (2000) (PPT) |                                                |             |

| W7   | 16.11<br>Tue. | You Tube Live | M7: How to Evaluate Data Movement<br>Bottlenecks<br>@ (PDF) # (PPT)           |                                                |             |

| W8   | 23.11<br>Tue. | You Tube Live | M8: Programming PIM Architectures                                             |                                                |             |

| W9   | 30.11<br>Tue. | You Tube Live | M9: Benchmarking and Workload<br>Suitability on PIM<br>@ (PDF) # (PPT)        |                                                |             |

| W10  | 07.12<br>Tue. | You Tube Live | M10: Bit-Serial SIMD Processing<br>using DRAM<br>@ (PDF) @ (PPT)              |                                                |             |

### **PIM Course (Current)**

#### Spring 2022 Edition:

https://safari.ethz.ch/projects\_and\_semi nars/spring2022/doku.php?id=processing in\_memory

#### Youtube Livestream:

https://www.youtube.com/watch?v=9e4 Chnwdovo&list=PL5Q2soXY2Zi-841fUYYUK9EsXKhQKRPyX

#### Project course

- Taken by Bachelor's/Master's students

- Processing-in-Memory lectures

- Hands-on research exploration

- Many research readings

#### Recorded Lecture Playlist

#### Spring 2022 Meetings/Schedule

| Week | Date          | Livestream      | Meeting                                                                      | Learning<br>Materials                          | Assignments |

|------|---------------|-----------------|------------------------------------------------------------------------------|------------------------------------------------|-------------|

| W1   | 10.03<br>Thu. | Weine Live      | M1: P&S PIM Course<br>Presentation<br>(PDF) ((PPT))                          | Required Materials<br>Recommended<br>Materials | HW 0 Out    |

| W2   | 15.03<br>Tue. |                 | Hands-on Project Proposals                                                   |                                                |             |

|      | 17.03<br>Thu. | Nemiere         | M2: Real-world PIM: UPMEM PIM<br>(PDF) (PPT)                                 |                                                |             |

| W3   | 24.03<br>Thu. | Metro Live      | M3: Real-world PIM:<br>Microbenchmarking of UPMEM<br>PIM<br>am(PDF) am (PPT) |                                                |             |

| W4   | 31.03<br>Thu. | Maine Live      | M4: Real-world PIM: Samsung<br>HBM-PIM<br>(PDF) ((PPT))                      |                                                |             |

| W5   | 07.04<br>Thu. | W Tive          | M5: How to Evaluate Data<br>Movement Bottlenecks<br>(m(PDF) (m (PPT)         |                                                |             |

| W6   | 14.04<br>Thu. | Millio Live     | M6: Real-world PIM: SK Hynix<br>AM<br>(m) (PDF) (m) (PPT)                    |                                                |             |

| W7   | 21.04<br>Thu. | Metere Premiere | M7: Programming PIM<br>Architectures<br>(PDF) (m (PPT)                       |                                                |             |

| W8   | 28.04<br>Thu. | Millio Premiere | M8: Benchmarking and Workload<br>Suitability on PIM<br>im (PDF) im (PPT)     |                                                |             |

| W9   | 05.05<br>Thu. | Main Premiere   | M9: Real-world PIM: Samsung<br>AxDIMM<br>(PDF) ((PPT))                       |                                                |             |

| W10  | 12.05<br>Thu. |                 | M10: Real-world PIM: Alibaba HB-<br>PNM                                      |                                                |             |

## Current EFCL Projects

- A New Methodology and Open-Source Benchmark Suite for Evaluating Data Movement Bottlenecks: A Processing-in-Memory Case Study"

- Data-centric

"Machine-Learning-Assisted Intelligent Microarchitectures to Reduce Memory Access Latency"

Data-driven

"Cross-layer Hardware/Software Techniques to Enable Powerful Computation and Memory Optimizations"

Data-aware

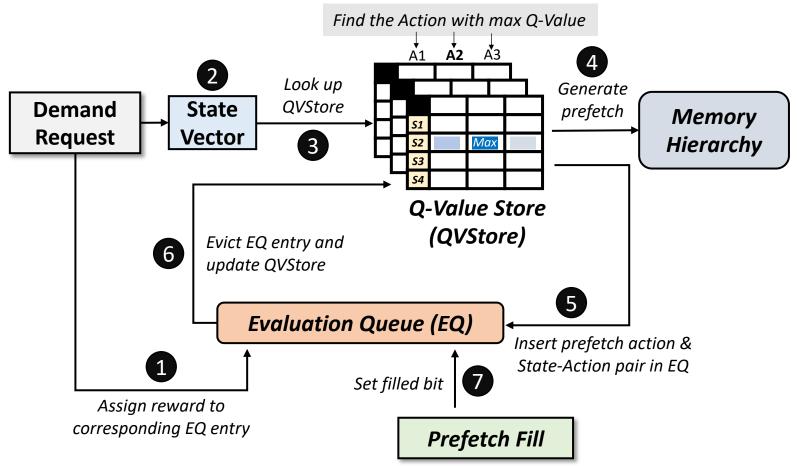

Machine-Learning-Assisted Intelligent Microarchitectures to Reduce Memory Access Latency

Rahul Bera, Gagandeep Singh, Rakesh Nadig, Konstantinos Kanellopoulos, Onur Mutlu

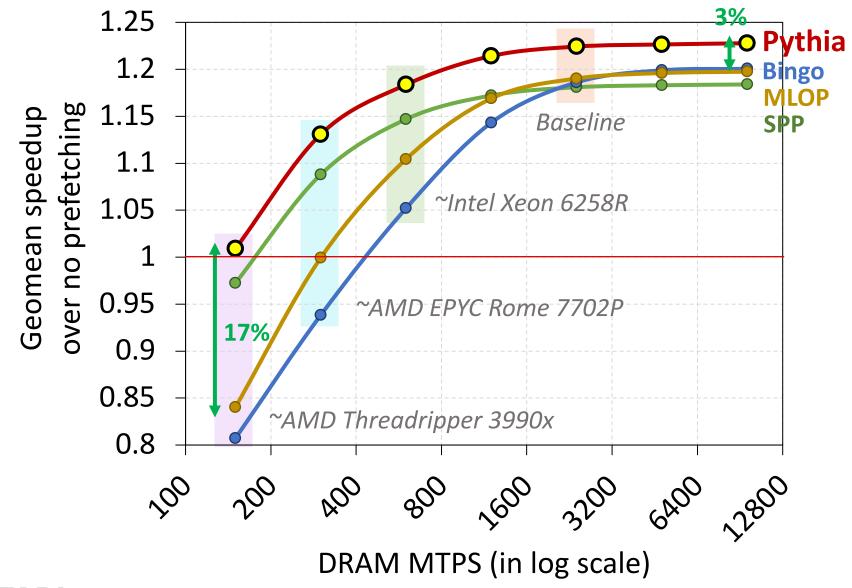

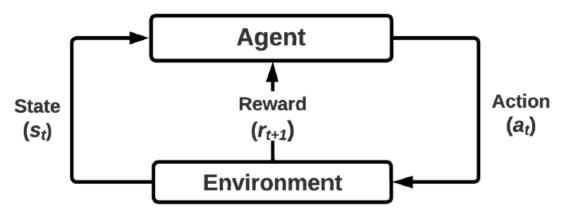

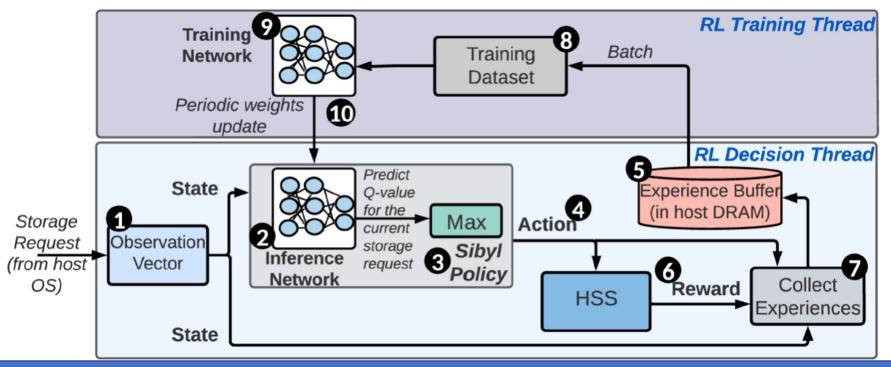

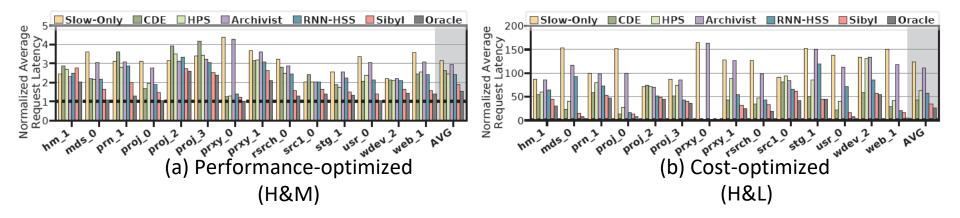

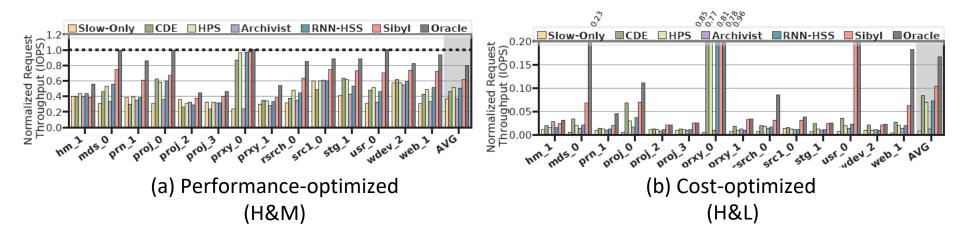

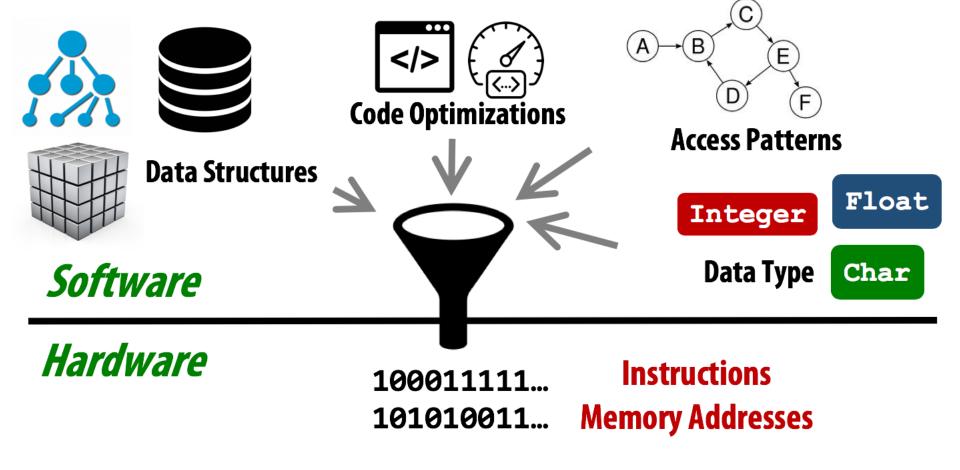

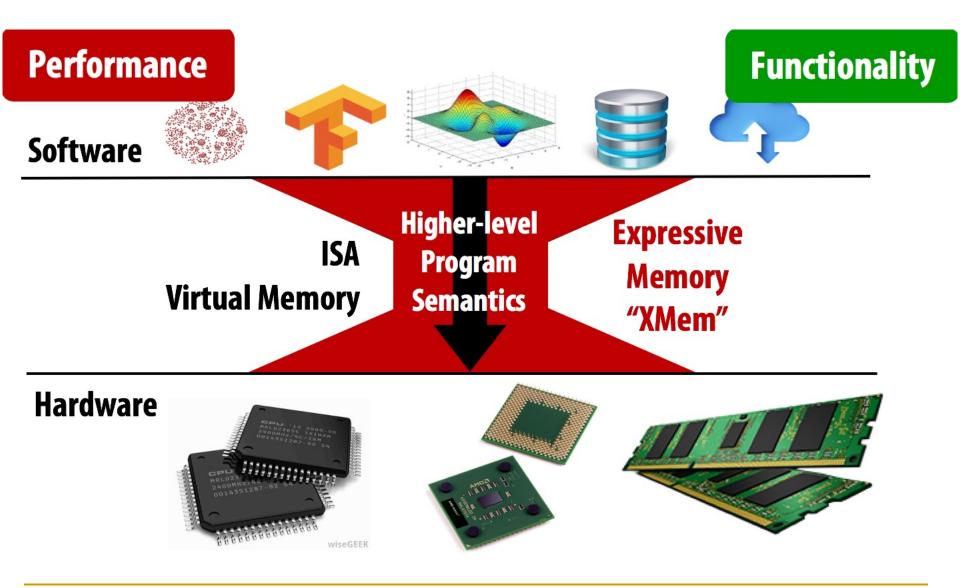

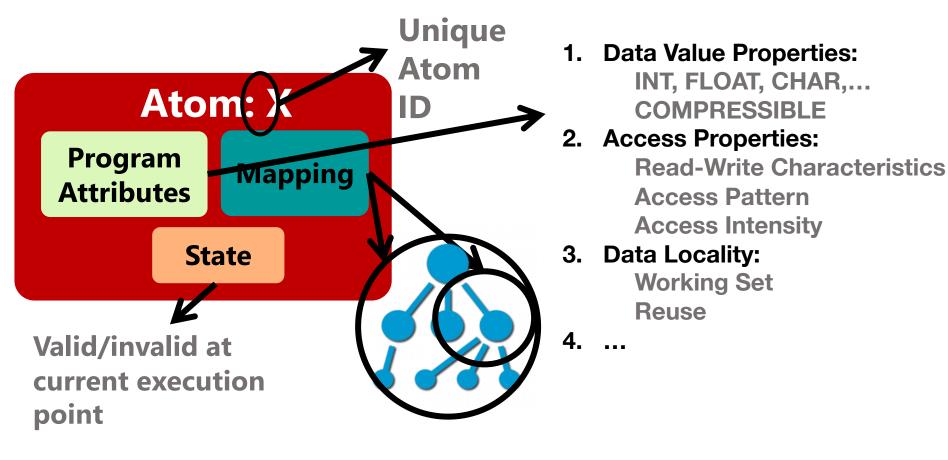

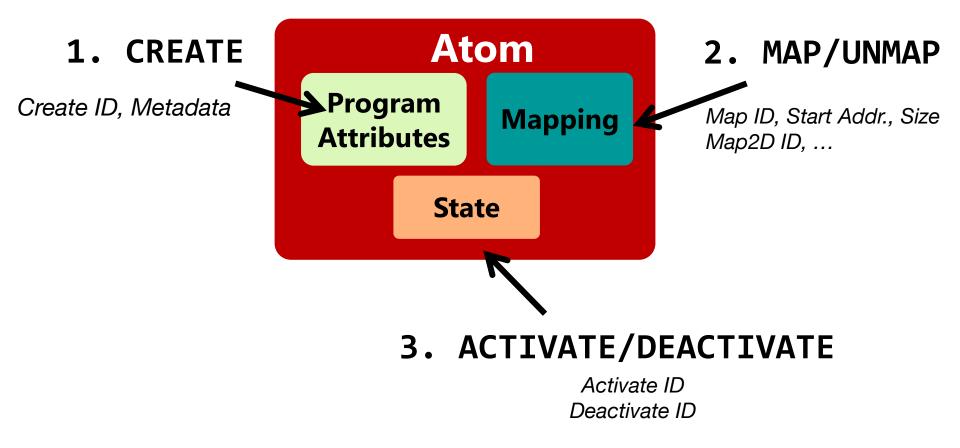

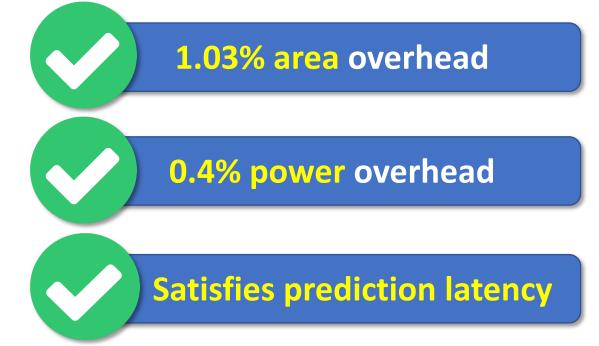

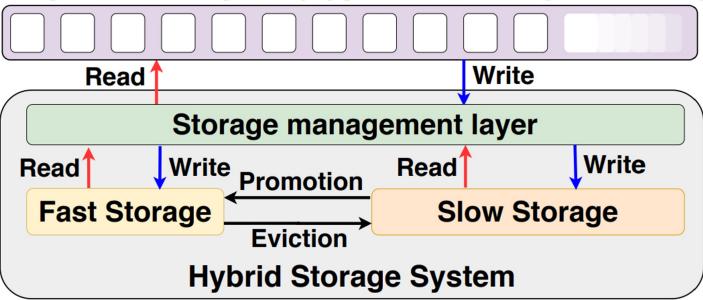

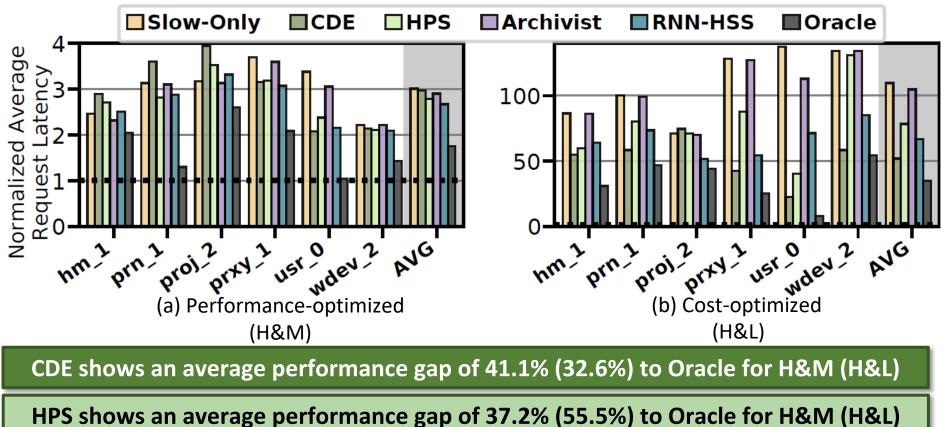

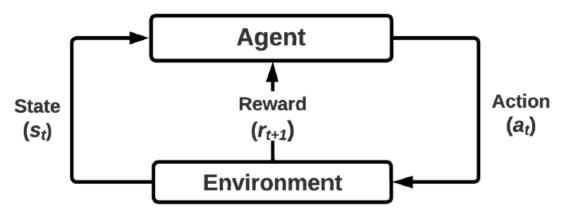

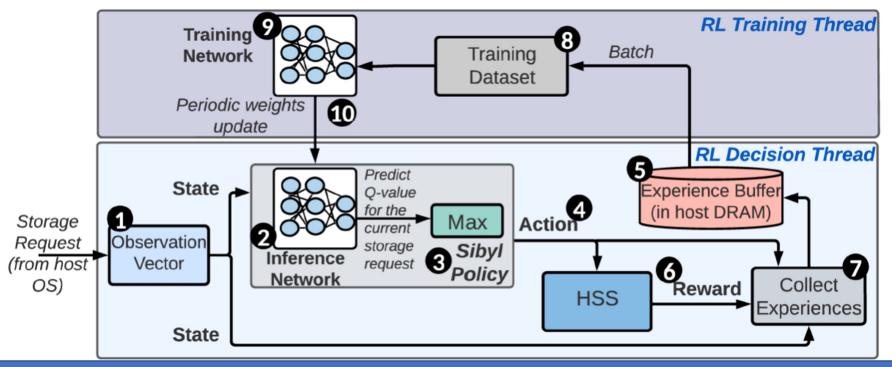

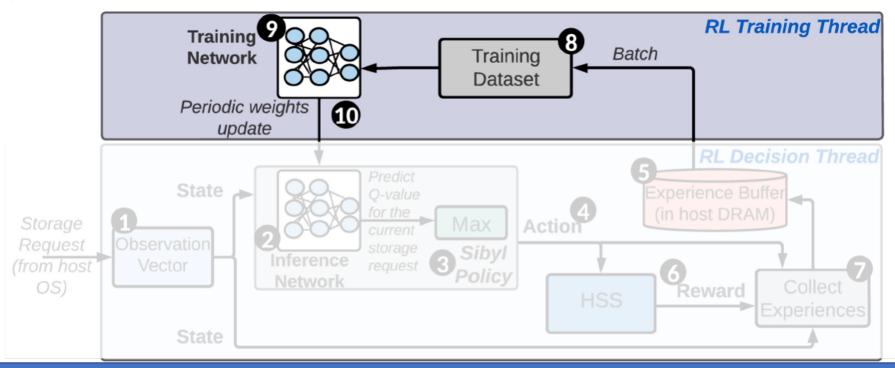

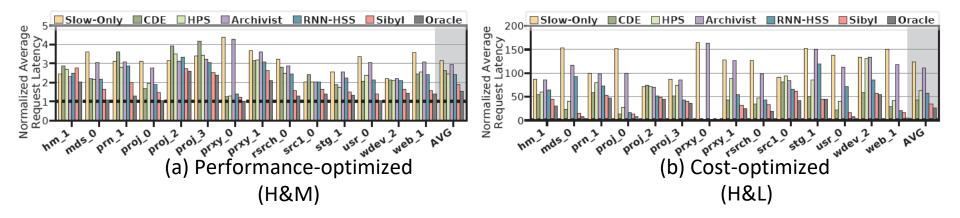

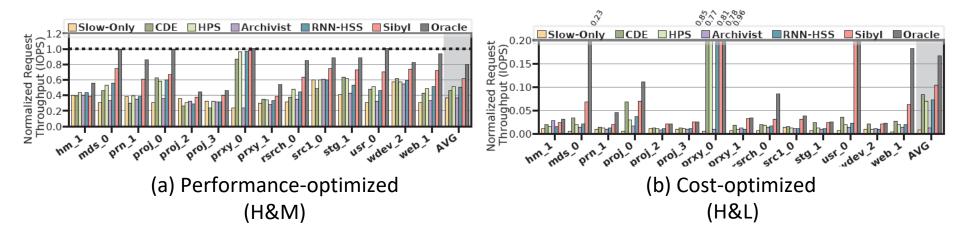

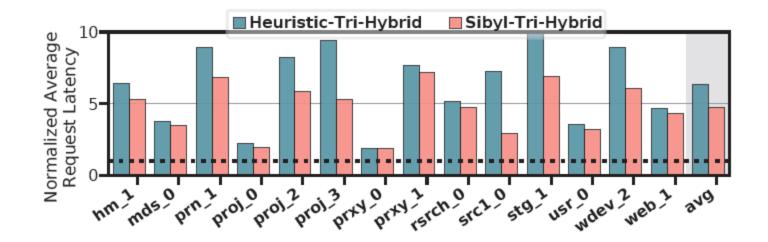

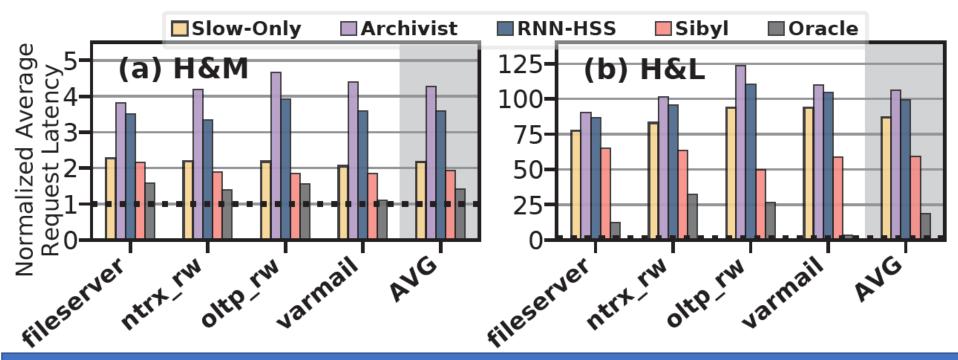

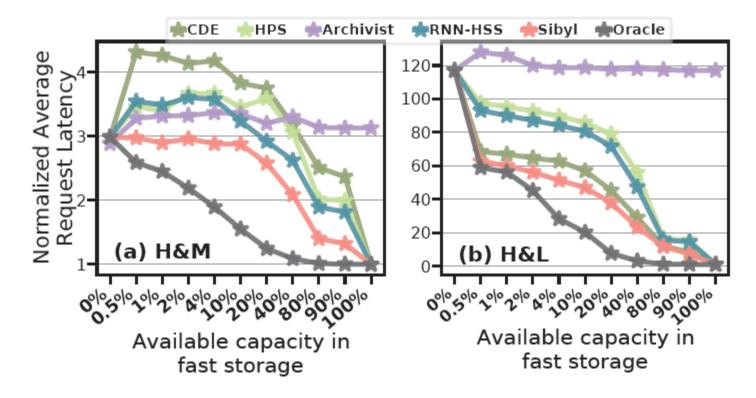

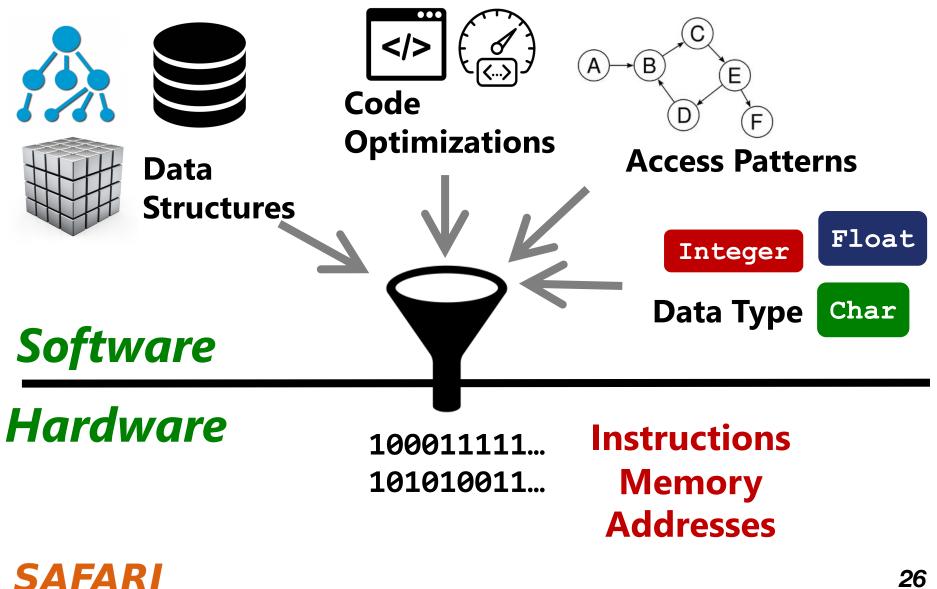

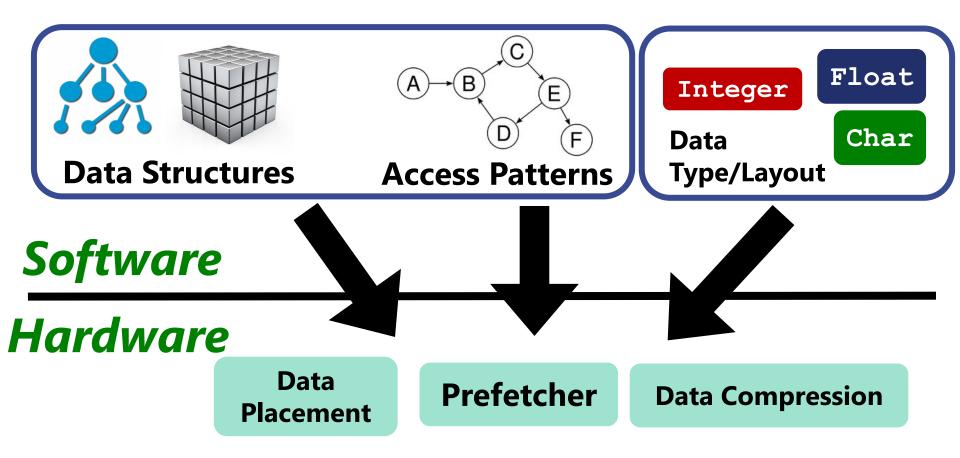

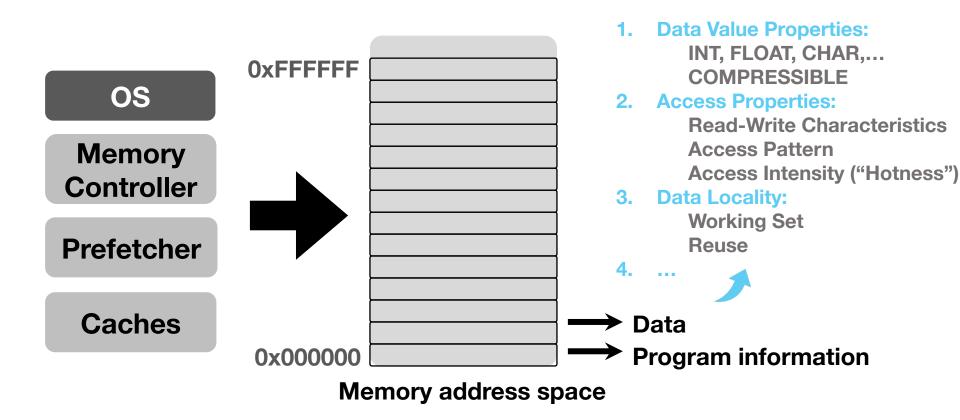

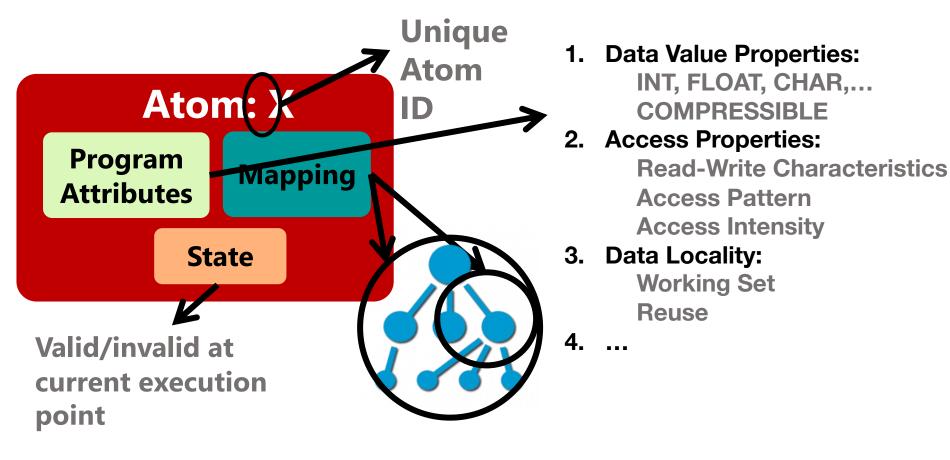

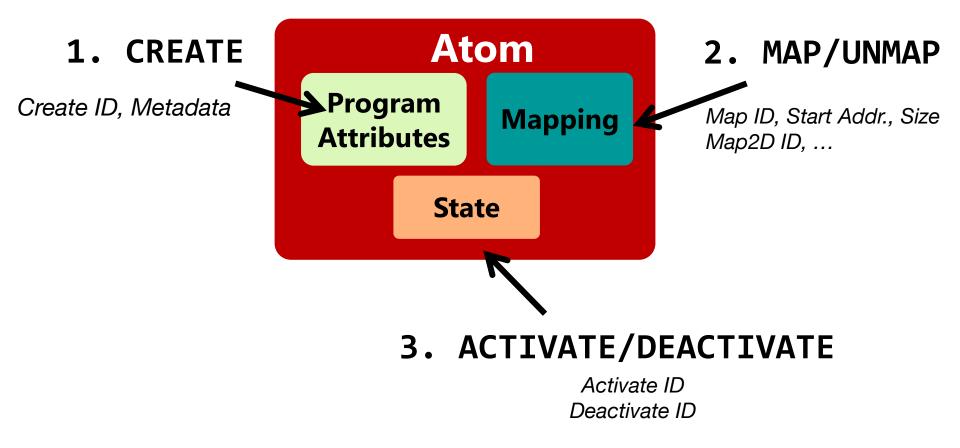

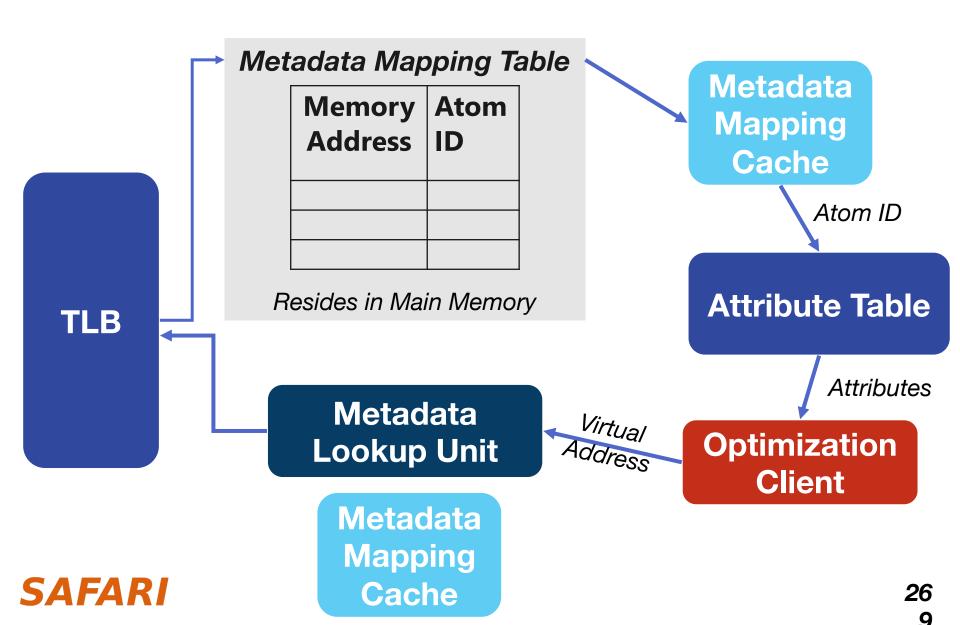

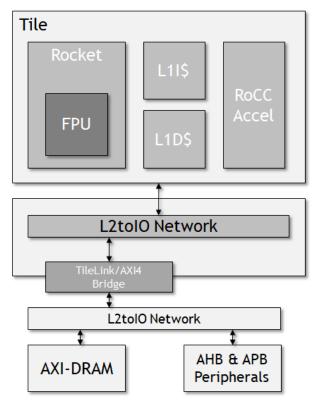

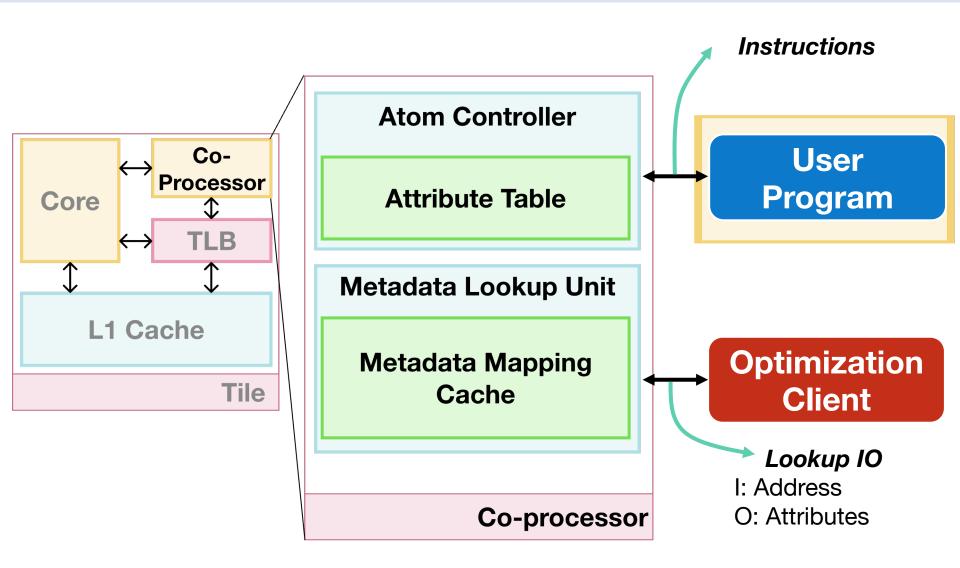

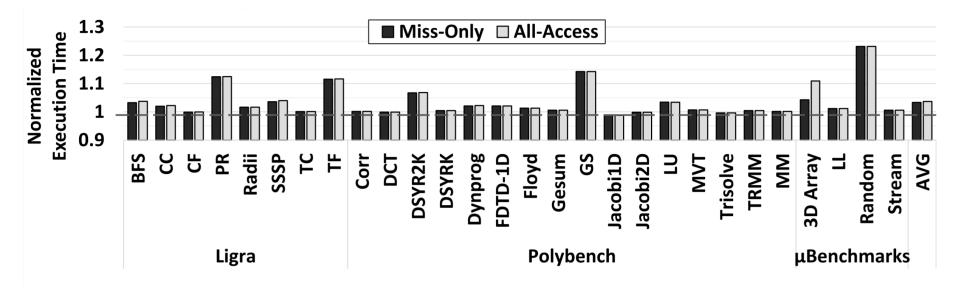

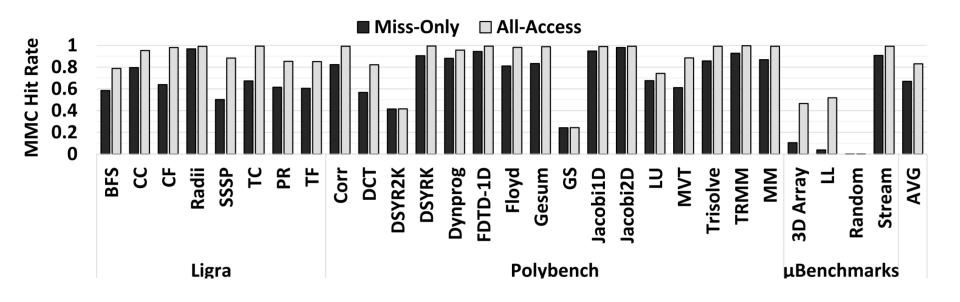

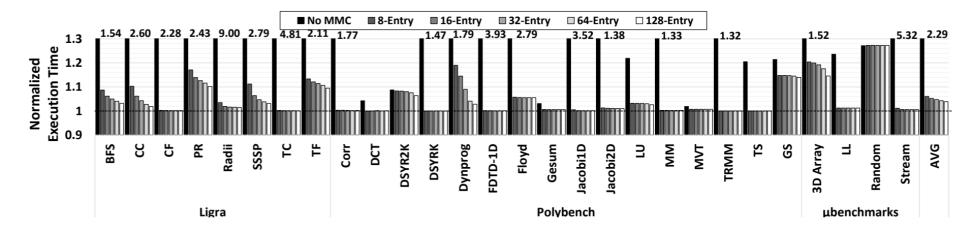

# System Architecture Design Today