#### RowHammer, RowPress & Beyond

Can We Be Free of Bitflips (Soon)?

Onur Mutlu

omutlu@gmail.com

https://people.inf.ethz.ch/omutlu

31 May 2024

Qualcomm Innovation Fellowship Finals Keynote Talk

Carnegie Mellon

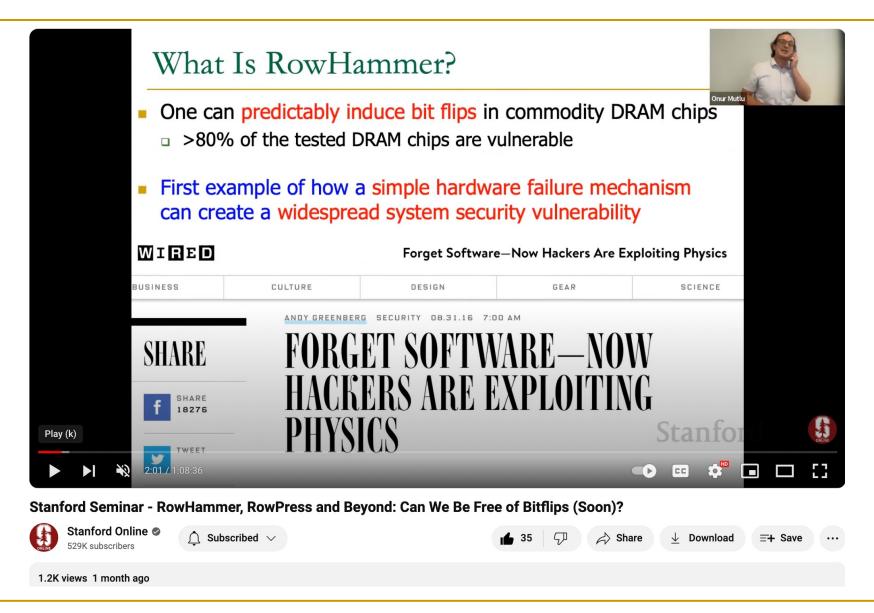

#### What Is RowHammer?

- One can predictably induce bit flips in commodity DRAM chips

- All recent DRAM chips are fundamentally vulnerable

- First example of how a simple hardware failure mechanism can create a widespread system security vulnerability

Forget Software—Now Hackers Are Exploiting Physics

BUSINESS CULTURE DESIGN GEAR SCIENCE

NDY GREENBERG SECURITY 08.31.16 7:00 AM

# FORGET SOFTWARE—NOW HACKERS ARE EXPLOITING PHYSICS

#### An "Early" Position Paper [IMW'13]

Onur Mutlu,

"Memory Scaling: A Systems Architecture Perspective"

Proceedings of the 5th International Memory

Workshop (IMW), Monterey, CA, May 2013. Slides

(pptx) (pdf)

EETimes Reprint

#### Memory Scaling: A Systems Architecture Perspective

Onur Mutlu

Carnegie Mellon University

onur@cmu.edu

http://users.ece.cmu.edu/~omutlu/

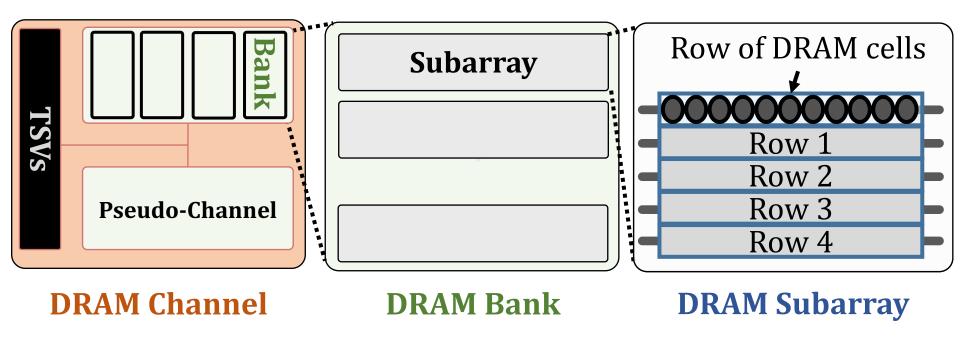

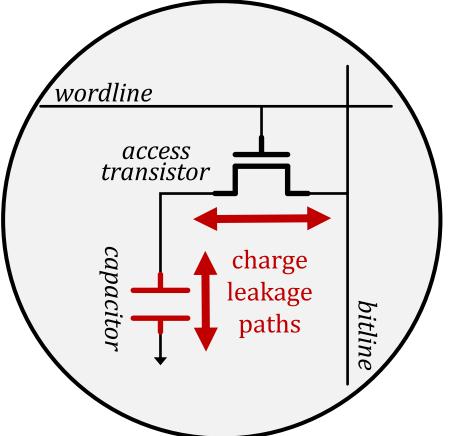

#### The DRAM Scaling Problem

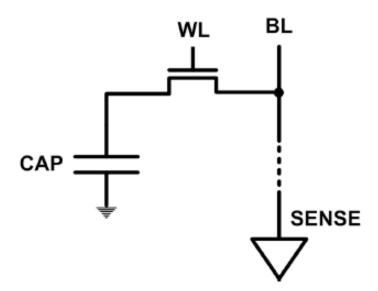

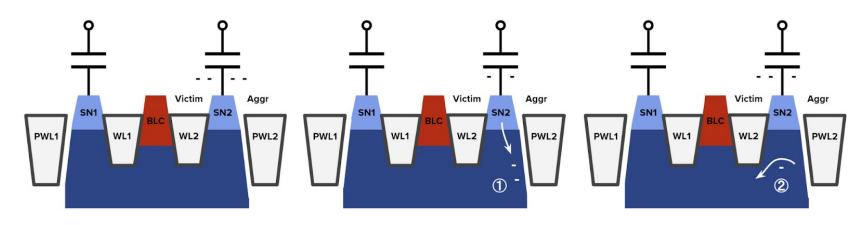

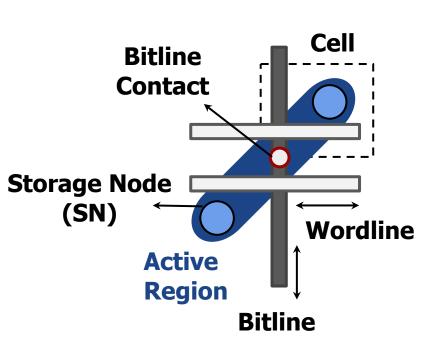

- DRAM stores charge in a capacitor (charge-based memory)

- Capacitor must be large enough for reliable sensing

- Access transistor should be large enough for low leakage and high retention time

- Scaling beyond 40-35nm (2013) is challenging [ITRS, 2009]

DRAM capacity, cost, and energy/power hard to scale

#### The DRAM Scaling Problem

- DRAM stores charge in a capacitor (charge-based memory)

- Capacitor must be large enough for reliable sensing

- Access transistor should be large enough for low leakage and high retention time

- Scaling beyond 40-35nm (2013) is challenging [ITRS, 2009]

DRAM capacity, cost, and energy/power hard to scale

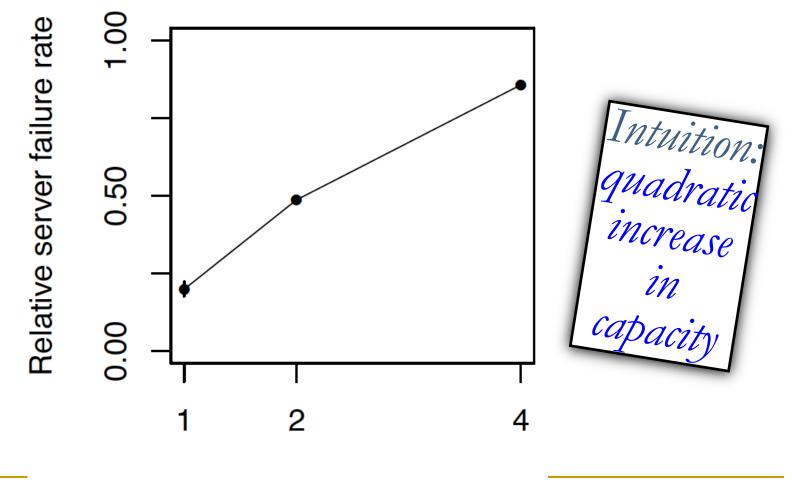

#### As Memory Scales, It Becomes Unreliable

- Data from all of Facebook's servers worldwide

- Meza+, "Revisiting Memory Errors in Large-Scale Production Data Centers," DSN'15.

#### Large-Scale Failure Analysis of DRAM Chips

- Analysis and modeling of memory errors found in all of Facebook's server fleet

- Justin Meza, Qiang Wu, Sanjeev Kumar, and Onur Mutlu, "Revisiting Memory Errors in Large-Scale Production Data Centers: Analysis and Modeling of New Trends from the Field" Proceedings of the 45th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Rio de Janeiro, Brazil, June 2015.

[Slides (pptx) (pdf)] [DRAM Error Model]

#### Revisiting Memory Errors in Large-Scale Production Data Centers: Analysis and Modeling of New Trends from the Field

Justin Meza Qiang Wu\* Sanjeev Kumar\* Onur Mutlu Carnegie Mellon University \* Facebook, Inc.

#### Infrastructures to Understand Such Issues

Flipping Bits in Memory Without Accessing

Them: An Experimental Study of DRAM

Disturbance Errors (Kim et al., ISCA 2014)

Adaptive-Latency DRAM: Optimizing DRAM

Timing for the Common-Case (Lee et al.,

HPCA 2015)

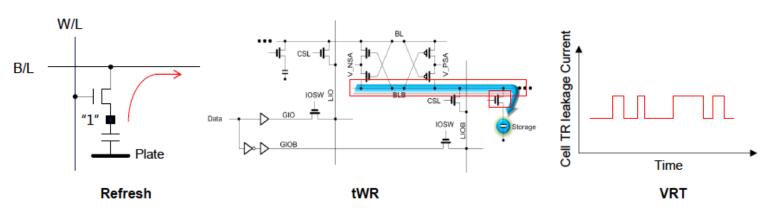

<u>AVATAR: A Variable-Retention-Time (VRT)</u> <u>Aware Refresh for DRAM Systems</u> (Qureshi et al., DSN 2015) An Experimental Study of Data Retention

Behavior in Modern DRAM Devices:

Implications for Retention Time Profiling

Mechanisms (Liu et al., ISCA 2013)

The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study (Khan et al., SIGMETRICS 2014)

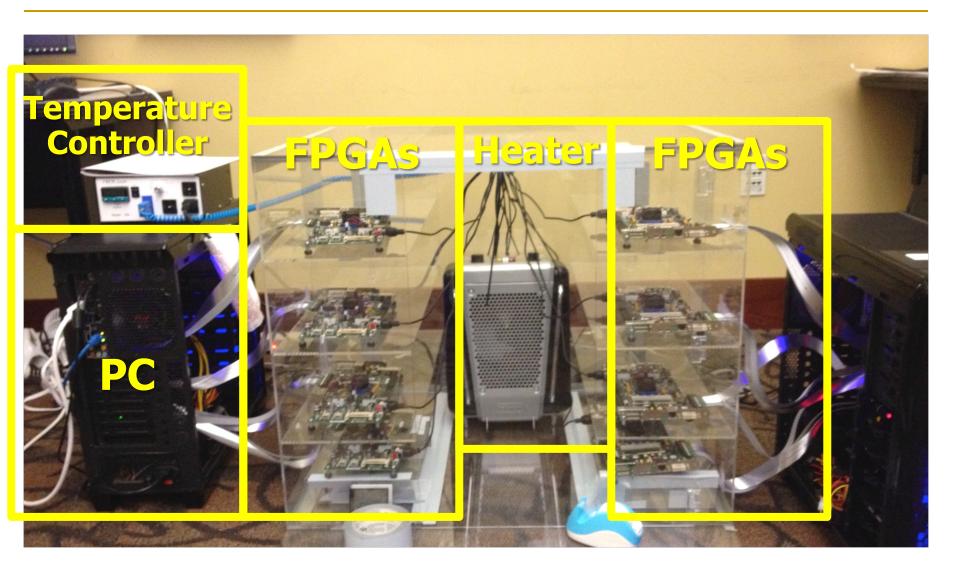

#### Infrastructures to Understand Such Issues

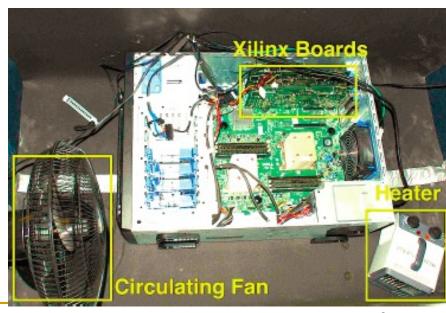

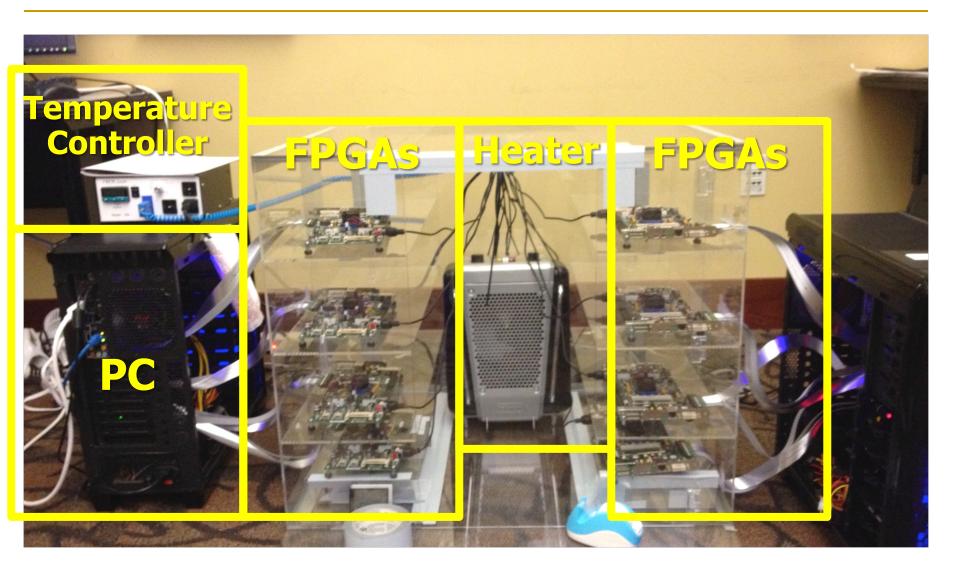

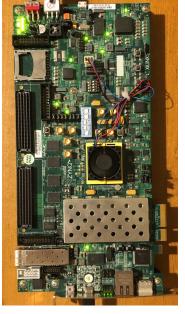

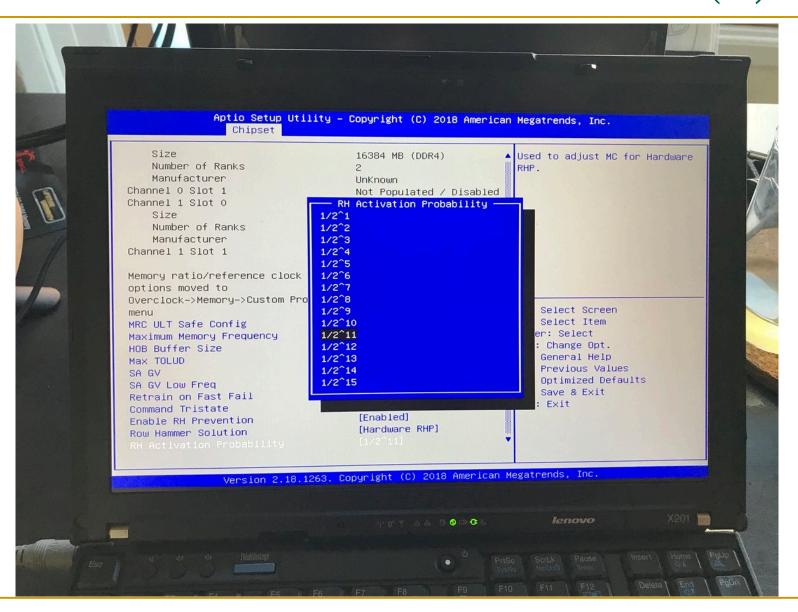

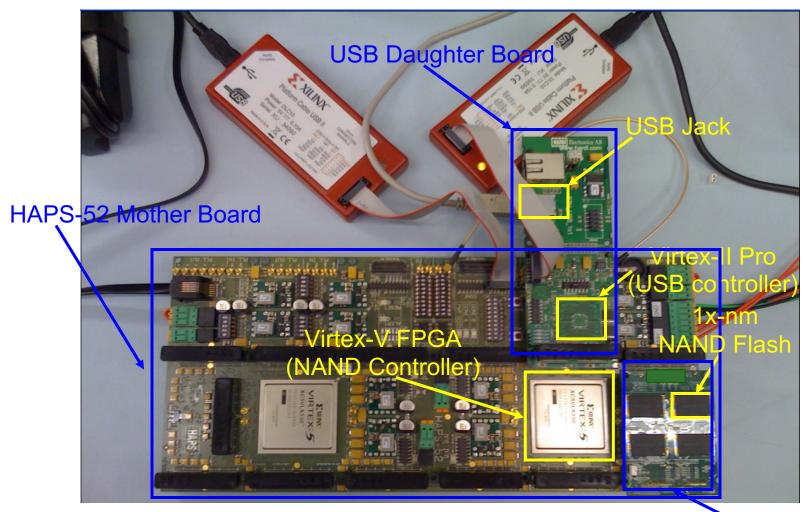

#### SoftMC: Open Source DRAM Infrastructure

Hasan Hassan et al., "SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies," HPCA 2017.

- Easy to Use (C++ API)

- Open-source github.com/CMU-SAFARI/SoftMC

#### SoftMC: Open Source DRAM Infrastructure

Hasan Hassan, Nandita Vijaykumar, Samira Khan, Saugata Ghose, Kevin Chang, Gennady Pekhimenko, Donghyuk Lee, Oguz Ergin, and Onur Mutlu, "SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies"

Proceedings of the 23rd International Symposium on High-Performance Computer Architecture (HPCA), Austin, TX, USA, February 2017.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

[Full Talk Lecture (39 minutes)]

### SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

Hasan Hassan Nandita Vijaykumar Samira Khan Saugata Ghose Kevin Chang Gennady Pekhimenko Donghyuk Lee $^{6,3}$  Oguz Ergin Onur Mutlu Onur Mutlu

<sup>1</sup>ETH Zürich <sup>2</sup>TOBB University of Economics & Technology <sup>3</sup>Carnegie Mellon University <sup>4</sup>University of Virginia <sup>5</sup>Microsoft Research <sup>6</sup>NVIDIA Research

Source Code

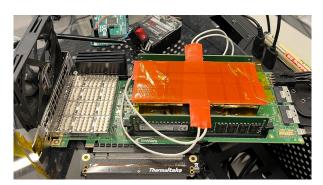

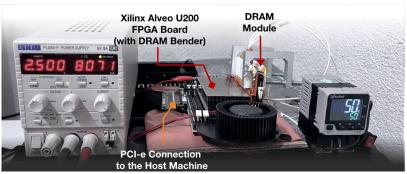

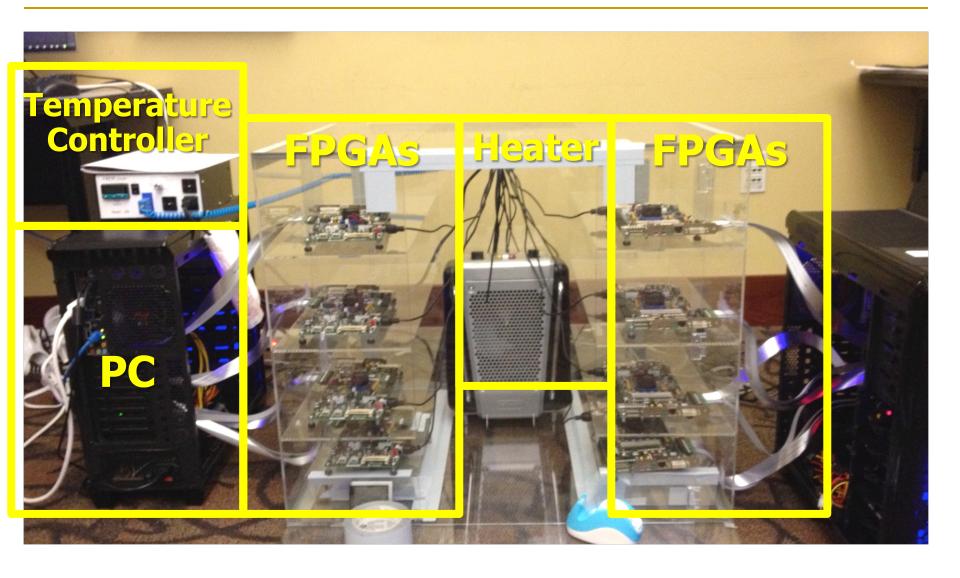

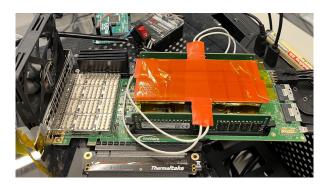

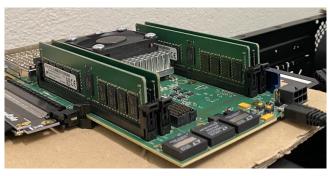

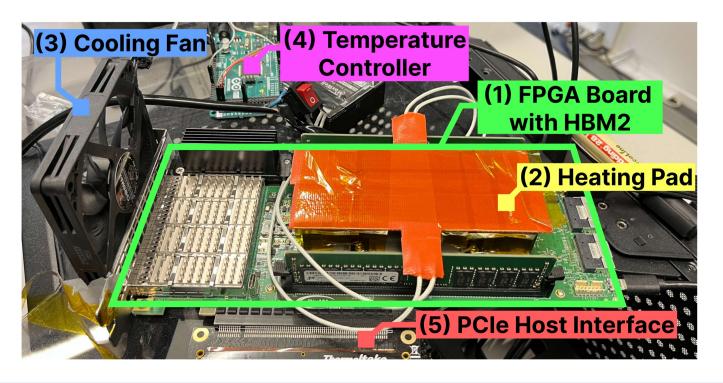

#### DRAM Bender

Ataberk Olgun, Hasan Hassan, A Giray Yağlıkçı, Yahya Can Tuğrul, Lois Orosa,

Haocong Luo, Minesh Patel, Oğuz Ergin, and Onur Mutlu,

"DRAM Bender: An Extensible and Versatile FPGA-based Infrastructure

to Easily Test State-of-the-art DRAM Chips"

<u>IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems</u> (**TCAD**), 2023.

[Extended arXiv version]

[DRAM Bender Source Code]

[DRAM Bender Tutorial Video (43 minutes)]

### DRAM Bender: An Extensible and Versatile FPGA-based Infrastructure to Easily Test State-of-the-art DRAM Chips

Ataberk Olgun<sup>§</sup> Hasan Hassan<sup>§</sup> A. Giray Yağlıkçı<sup>§</sup> Yahya Can Tuğrul<sup>§†</sup> Lois Orosa<sup>§⊙</sup> Haocong Luo<sup>§</sup> Minesh Patel<sup>§</sup> Oğuz Ergin<sup>†</sup> Onur Mutlu<sup>§</sup> <sup>§</sup>ETH Zürich <sup>†</sup>TOBB ETÜ <sup>⊙</sup>Galician Supercomputing Center

#### **DRAM Bender: Prototypes**

| Testing Infrastructure            | Protocol Support | FPGA Support    |

|-----------------------------------|------------------|-----------------|

| SoftMC [134]                      | DDR3             | One Prototype   |

| LiteX RowHammer Tester (LRT) [17] | DDR3/4, LPDDR4   | Two Prototypes  |

| DRAM Bender (this work)           | DDR3/DDR4        | Five Prototypes |

#### Five out of the box FPGA-based prototypes

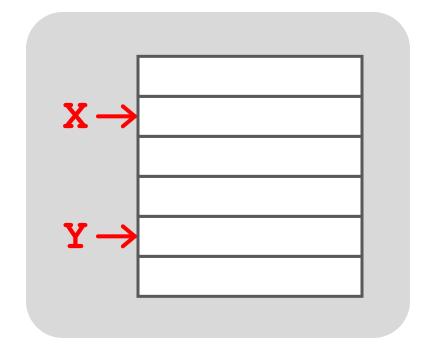

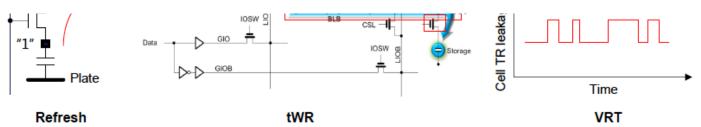

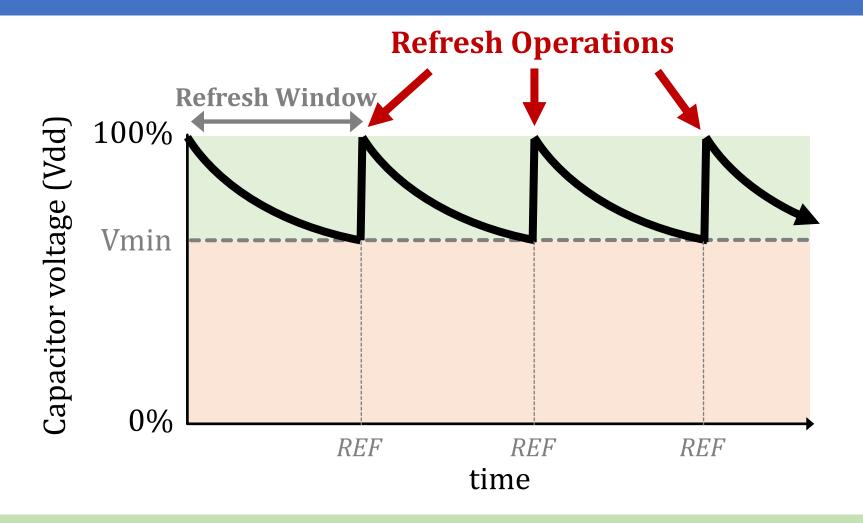

#### Data Retention in Memory [Liu et al., ISCA 2013]

Retention Time Profile of DRAM looks like this:

64-128ms

>256ms

128-256ms

Location dependent

Stored value pattern dependent

Time dependent

#### RAIDR: Heterogeneous Refresh [ISCA'12]

■ Jamie Liu, Ben Jaiyen, Richard Veras, and Onur Mutlu,

"RAIDR: Retention-Aware Intelligent DRAM Refresh"

Proceedings of the 39th International Symposium on Computer

Architecture (ISCA), Portland, OR, June 2012. Slides (pdf)

[Invited Retrospective at 50 Years of ISCA, 2023 (pdf)]

Selected to the ISCA-50 25-Year Retrospective Issue covering

1996-2020 in 2023 (Retrospective (pdf) Full Issue).

#### RAIDR: Retention-Aware Intelligent DRAM Refresh

Jamie Liu Ben Jaiyen Richard Veras Onur Mutlu Carnegie Mellon University

#### Analysis of Data Retention Failures [ISCA'13]

Jamie Liu, Ben Jaiyen, Yoongu Kim, Chris Wilkerson, and Onur Mutlu,

"An Experimental Study of Data Retention Behavior in Modern DRAM Devices:

Implications for Retention Time Profiling Mechanisms"

Proceedings of the <u>40th International Symposium on Computer Architecture</u> (**ISCA**), Tel-Aviv, Israel, June 2013. <u>Slides (ppt)</u> <u>Slides (pdf)</u>

[Invited Retrospective at 50 Years of ISCA, 2023 (pdf)]

Selected to the ISCA-50 25-Year Retrospective Issue covering 1996-2020 in 2023 (Retrospective (pdf) Full Issue).

# An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms

Jamie Liu\*

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

jamiel@alumni.cmu.edu

Ben Jaiyen Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

bjaiyen@alumni.cmu.edu

Yoongu Kim

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

yoonguk@ece.cmu.edu

Chris Wilkerson

Intel Corporation

2200 Mission College Blvd.

Santa Clara, CA 95054

chris.wilkerson@intel.com

Onur Mutlu

Carnegie Mellon University

5000 Forbes Ave.

Pittsburgh, PA 15213

onur@cmu.edu

#### A Curious Phenomenon

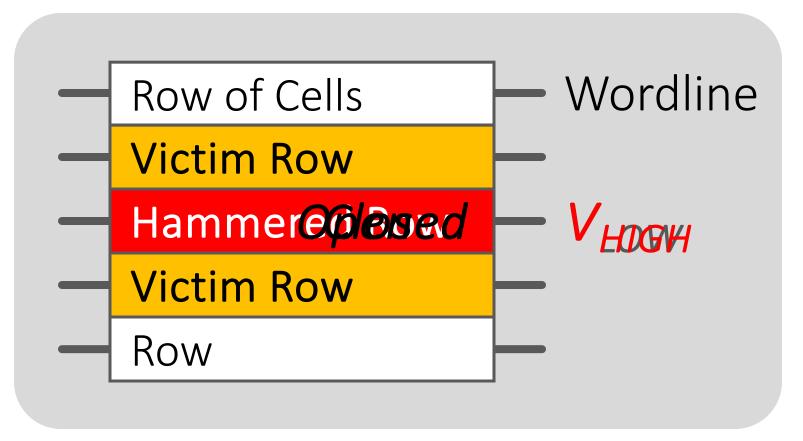

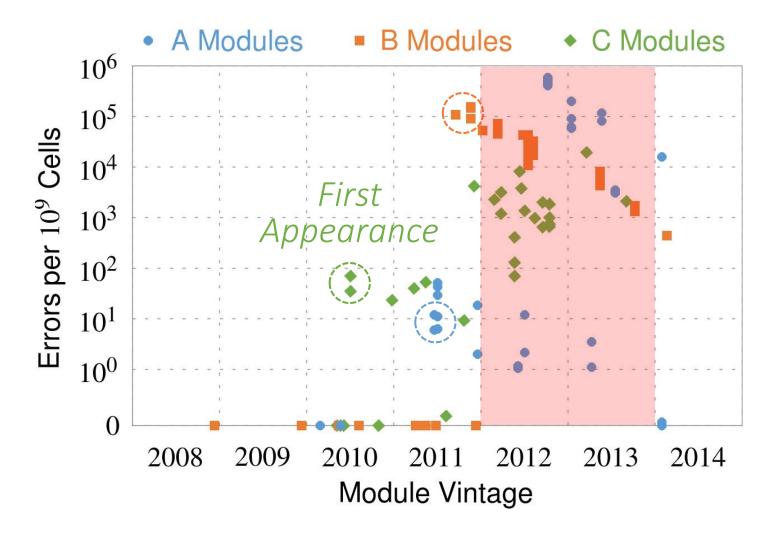

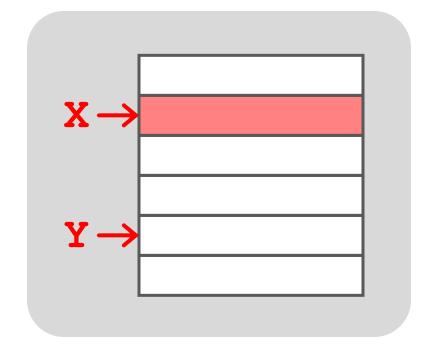

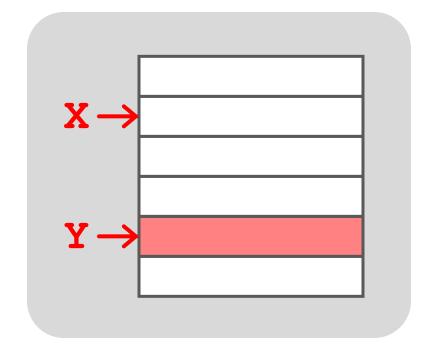

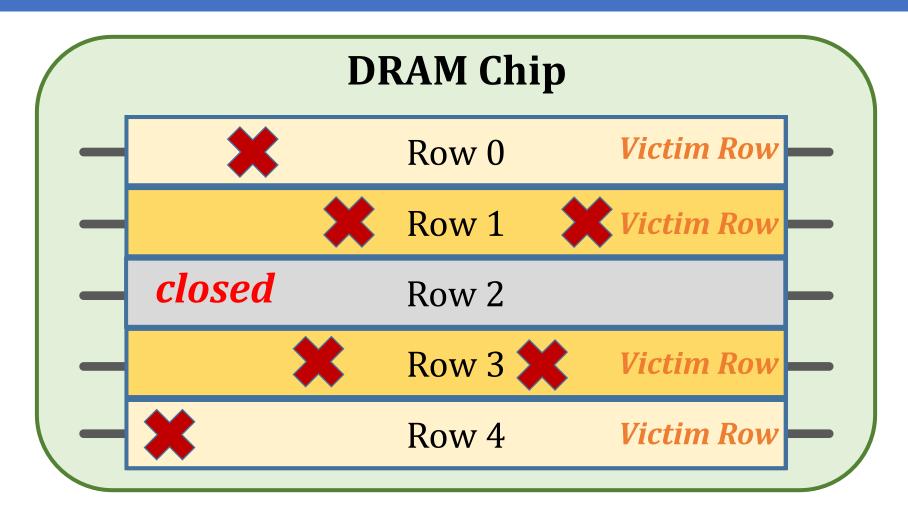

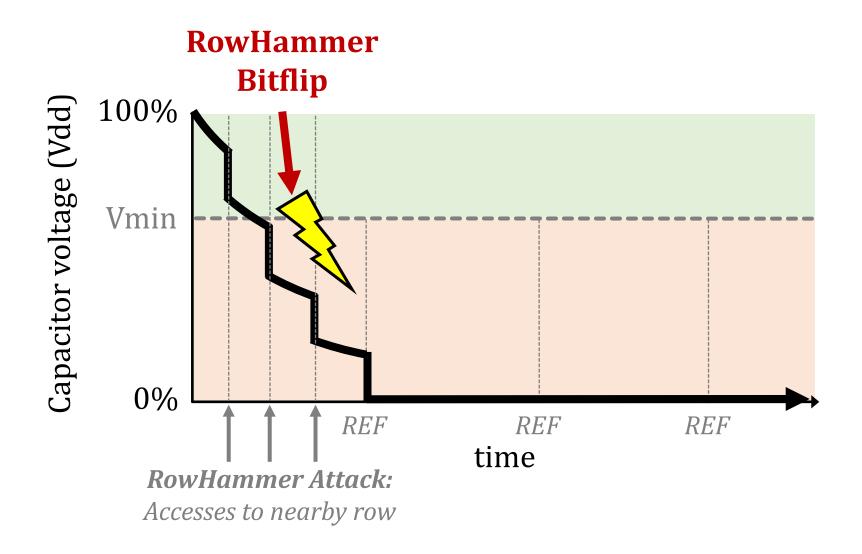

#### Modern DRAM is Prone to Disturbance Errors

Repeatedly reading a row enough times (before memory gets refreshed) induces disturbance errors in adjacent rows in most real DRAM chips you can buy today

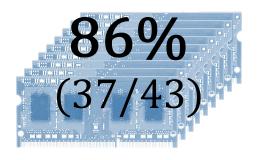

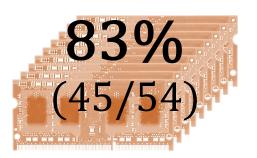

#### Most DRAM Modules Are Vulnerable

A company

**B** company

**C** company

Up to  $1.0 \times 10^7$  errors

Up to 2.7×10<sup>6</sup> errors

Up to  $3.3 \times 10^5$  errors

#### Recent DRAM Is More Vulnerable

All modules from 2012–2013 are vulnerable

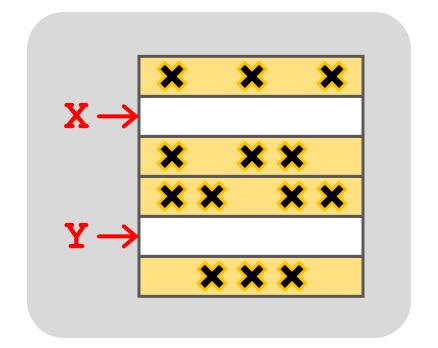

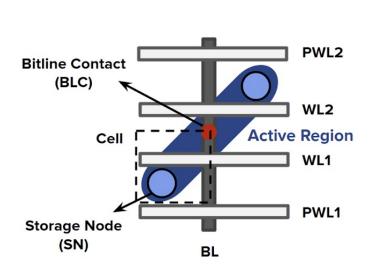

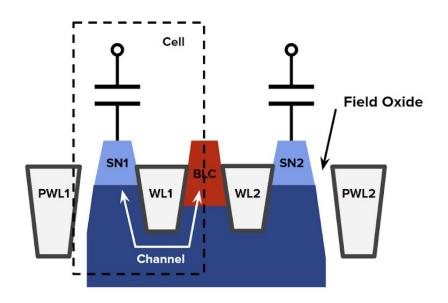

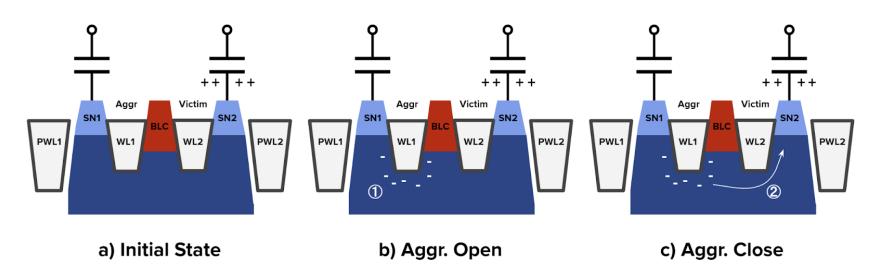

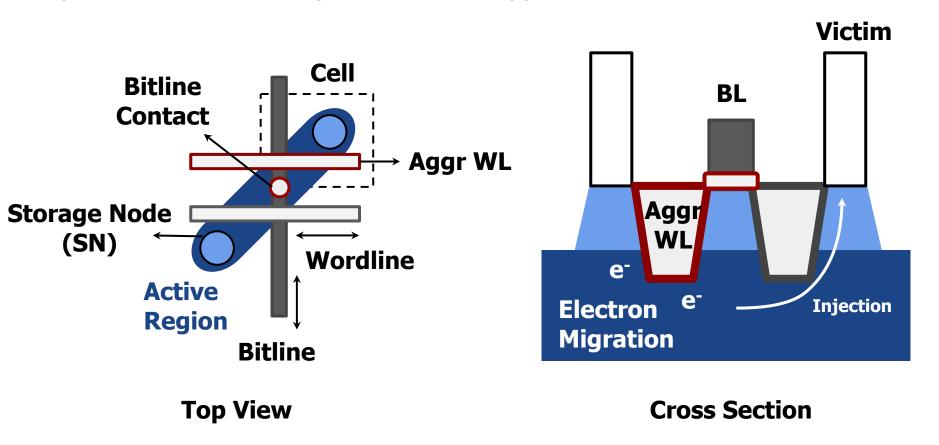

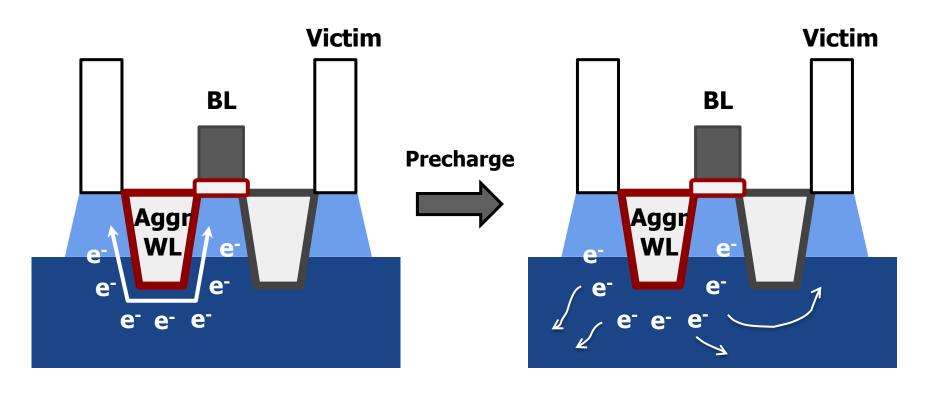

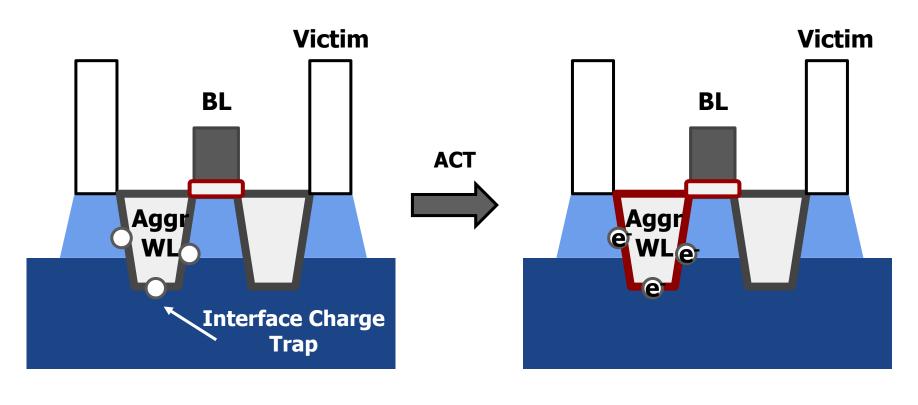

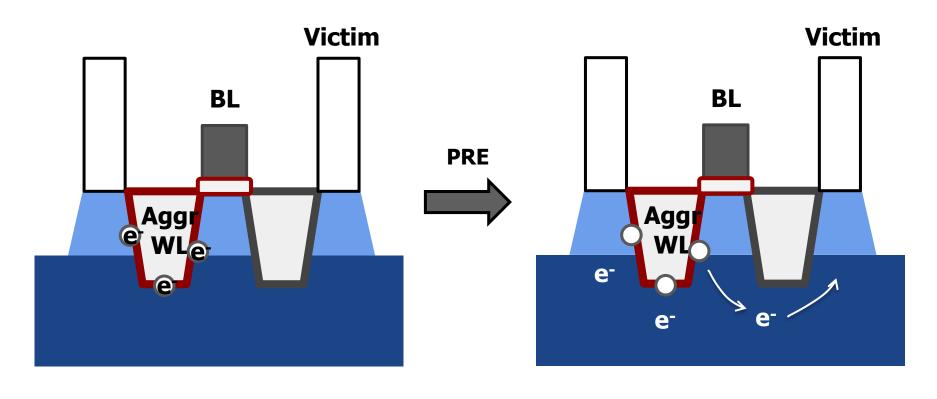

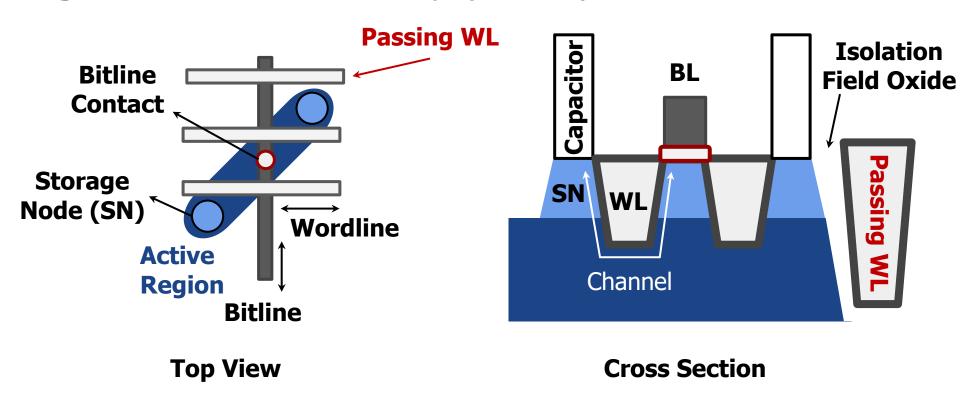

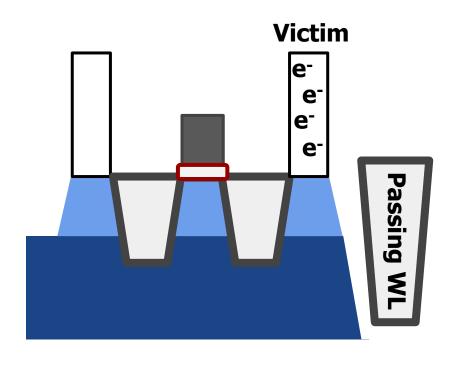

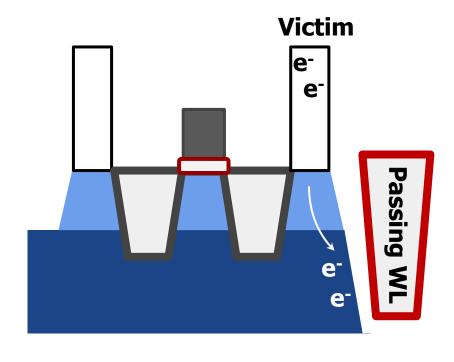

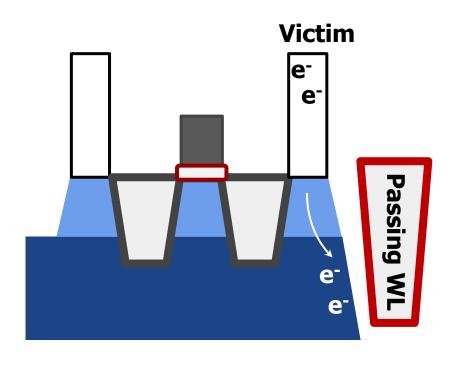

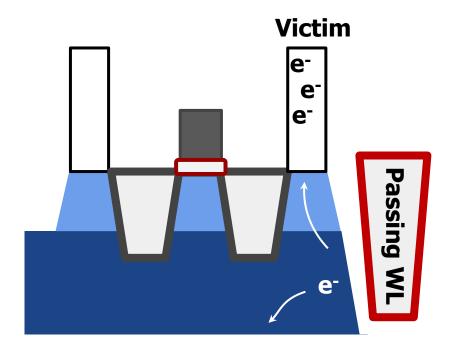

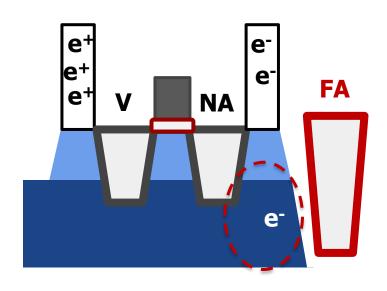

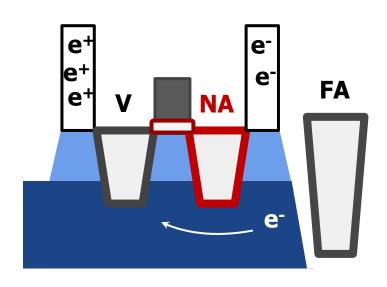

#### Why Is This Happening?

- DRAM cells are too close to each other!

- They are not electrically isolated from each other

- Access to one cell affects the value in nearby cells

- due to electrical interference between

- the cells

- wires used for accessing the cells

- Also called cell-to-cell coupling/interference

- Example: When we activate (apply high voltage) to a row, an adjacent row gets slightly activated as well

- Vulnerable cells in that slightly-activated row lose a little bit of charge

- If RowHammer happens enough times, charge in such cells gets drained

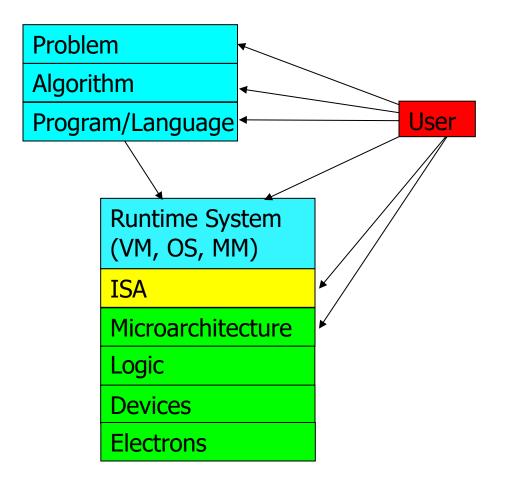

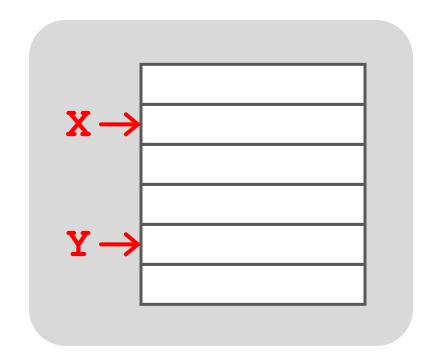

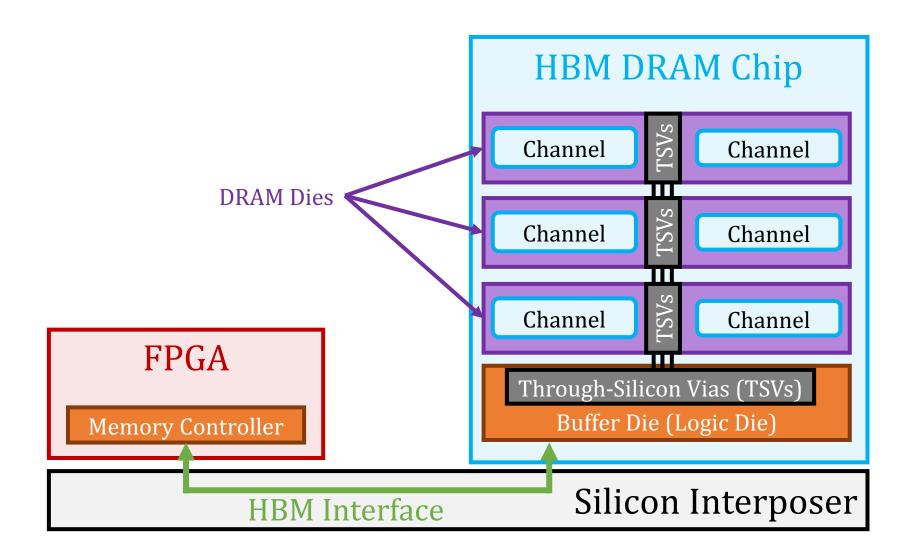

#### Higher-Level Implications

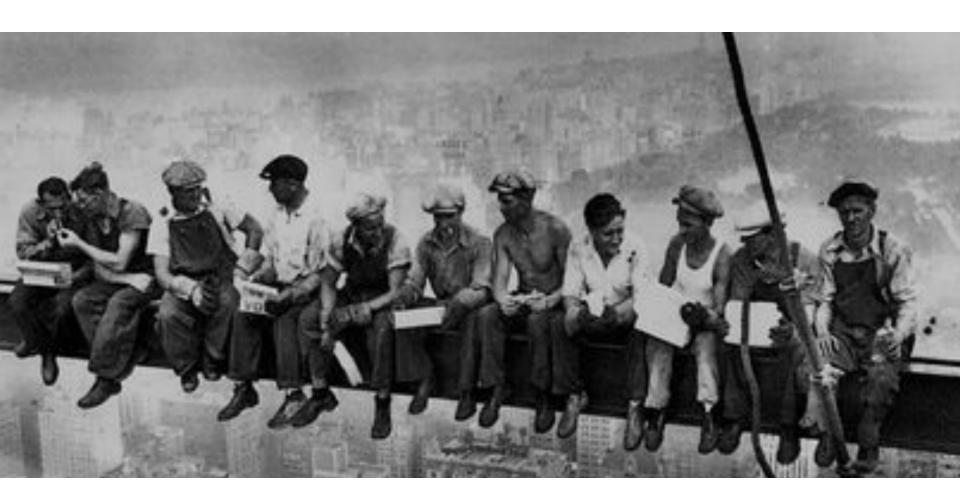

This simple circuit level failure mechanism has enormous implications on upper layers of the transformation hierarchy

**Problem** Algorithm Program/Language **Runtime System** (VM, OS, MM) ISA (Architecture) Microarchitecture Logic Devices Electrons

```

loop:

mov (X), %eax

mov (Y), %ebx

clflush (X)

clflush (Y)

mfence

jmp loop

```

- 1. Avoid cache hits

- Flush X from cache

- 2. Avoid *row hits* to X

- Read Y in another row

```

loop:

mov (X), %eax

mov (Y), %ebx

clflush (X)

clflush (Y)

mfence

jmp loop

```

```

loop:

mov (X), %eax

mov (Y), %ebx

clflush (X)

clflush (Y)

mfence

jmp loop

```

```

loop:

mov (X), %eax

mov (Y), %ebx

clflush (X)

clflush (Y)

mfence

jmp loop

```

#### Observed Errors in Real Systems

| CPU Architecture          | Errors | Access-Rate |

|---------------------------|--------|-------------|

| Intel Haswell (2013)      | 22.9K  | 12.3M/sec   |

| Intel Ivy Bridge (2012)   | 20.7K  | 11.7M/sec   |

| Intel Sandy Bridge (2011) | 16.1K  | 11.6M/sec   |

| AMD Piledriver (2012)     | 59     | 6.1M/sec    |

#### A real reliability, security, safety issue

#### One Can Take Over an Otherwise-Secure System

#### Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Abstract. Memory isolation is a key property of a reliable and secure computing system — an access to one memory address should not have unintended side effects on data stored in other addresses. However, as DRAM process technology

### Project Zero

Flipping Bits in Memory Without Accessing Them:

An Experimental Study of DRAM Disturbance Errors

(Kim et al., ISCA 2014)

News and updates from the Project Zero team at Google

Exploiting the DRAM rowhammer bug to gain kernel privileges (Seaborn, 2015)

Monday, March 9, 2015

Exploiting the DRAM rowhammer bug to gain kernel privileges

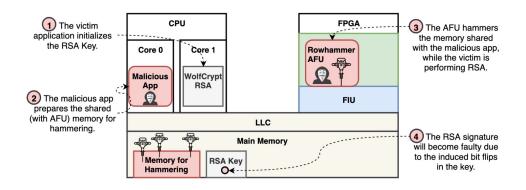

#### RowHammer Security Attack Example

- "Rowhammer" is a problem with some recent DRAM devices in which repeatedly accessing a row of memory can cause bit flips in adjacent rows (Kim et al., ISCA 2014).

- Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors (Kim et al., ISCA 2014)

- We tested a selection of laptops and found that a subset of them exhibited the problem.

- We built two working privilege escalation exploits that use this effect.

- Exploiting the DRAM rowhammer bug to gain kernel privileges (Seaborn+, 2015)

- One exploit uses rowhammer-induced bit flips to gain kernel privileges on x86-64 Linux when run as an unprivileged userland process.

- When run on a machine vulnerable to the rowhammer problem, the process was able to induce bit flips in page table entries (PTEs).

- It was able to use this to gain write access to its own page table, and hence gain read-write access to all of physical memory.

#### Security Implications

#### Security Implications

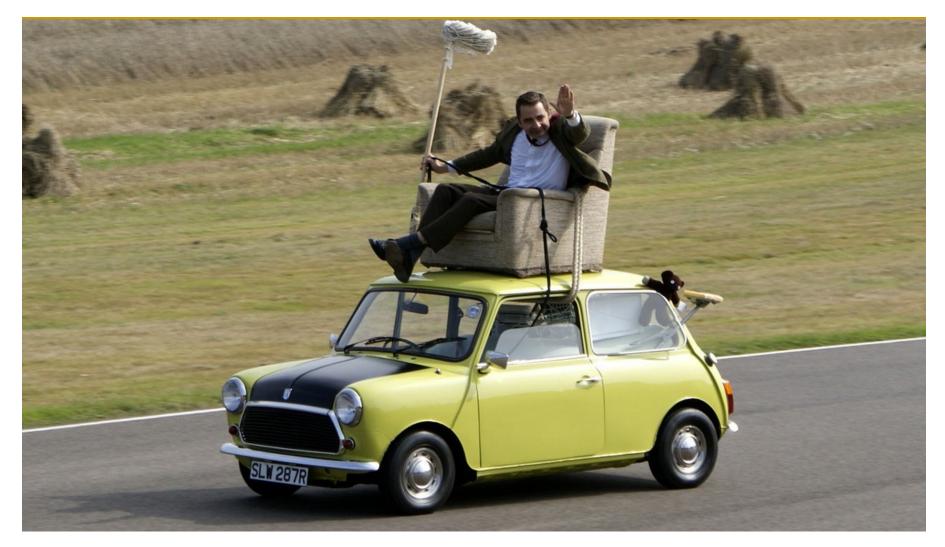

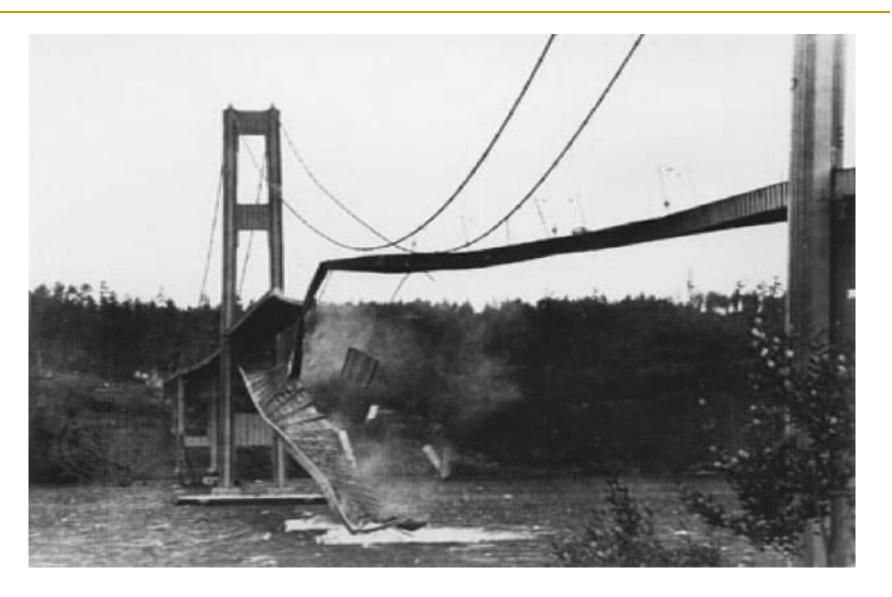

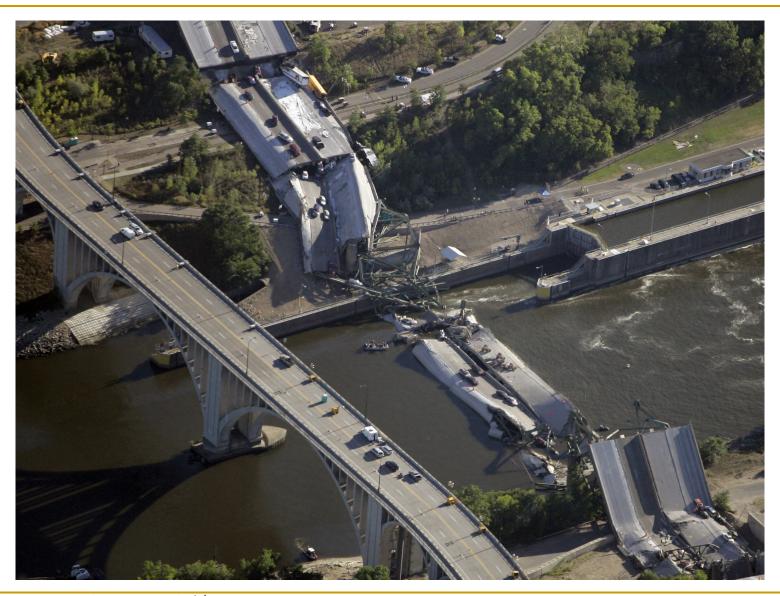

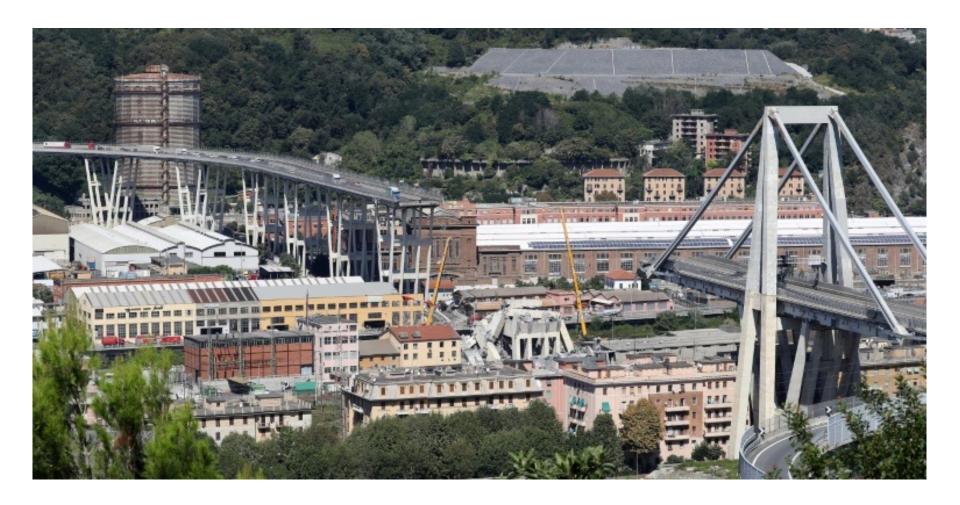

It's like breaking into an apartment by repeatedly slamming a neighbor's door until the vibrations open the door you were after

#### More Security Implications (I)

"We can gain unrestricted access to systems of website visitors."

www.iaik.tugraz.at

Not there yet, but ...

ROOT privileges for web apps!

Daniel Gruss (@lavados), Clémentine Maurice (@BloodyTangerine), December 28, 2015 — 32c3, Hamburg, Germany

Rowhammer.js: A Remote Software-Induced Fault Attack in JavaScript (DIMVA'16)

33

#### More Security Implications (II)

"Can gain control of a smart phone deterministically" Hammer And Root Millions of Androids

Drammer: Deterministic Rowhammer Attacks on Mobile Platforms, CCS'16 34

#### More Security Implications (III)

Using an integrated GPU in a mobile system to remotely escalate privilege via the WebGL interface. IEEE S&P 2018

"GRAND PWNING UNIT" —

# Drive-by Rowhammer attack uses GPU to compromise an Android phone

JavaScript based GLitch pwns browsers by flipping bits inside memory chips.

**DAN GOODIN - 5/3/2018, 12:00 PM**

## Grand Pwning Unit: Accelerating Microarchitectural Attacks with the GPU

Pietro Frigo Vrije Universiteit Amsterdam p.frigo@vu.nl Cristiano Giuffrida Vrije Universiteit Amsterdam giuffrida@cs.vu.nl Herbert Bos

Vrije Universiteit

Amsterdam

herbertb@cs.vu.nl

Kaveh Razavi Vrije Universiteit Amsterdam kaveh@cs.vu.nl

#### More Security Implications (IV)

Rowhammer over RDMA (I) USENIX ATC 2018

BIZ & IT

TECH

SCIENCE

**POLIC**

CARS

AMING & CULTUR

THROWHAMMER —

# Packets over a LAN are all it takes to trigger serious Rowhammer bit flips

The bar for exploiting potentially serious DDR weakness keeps getting lower.

**DAN GOODIN - 5/10/2018, 5:26 PM**

#### Throwhammer: Rowhammer Attacks over the Network and Defenses

Andrei Tatar

VU Amsterdam

Radhesh Krishnan

VU Amsterdam

Herbert Bos

Herbert Bos VU Amsterdam Elias Athanasopoulos University of Cyprus

> Kaveh Razavi VU Amsterdam

Cristiano Giuffrida VU Amsterdam

### More Security Implications (V)

Rowhammer over RDMA (II)

Nethammer—Exploiting DRAM Rowhammer Bug Through Network Requests

## Nethammer: Inducing Rowhammer Faults through Network Requests

Moritz Lipp Graz University of Technology

Daniel Gruss

Graz University of Technology

Misiker Tadesse Aga University of Michigan

Clémentine Maurice Univ Rennes, CNRS, IRISA

Lukas Lamster Graz University of Technology Michael Schwarz Graz University of Technology

Lukas Raab Graz University of Technology

#### More Security Implications (VI)

**IEEE S&P 2020**

#### RAMBleed

#### RAMBleed: Reading Bits in Memory Without Accessing Them

Andrew Kwong University of Michigan ankwong@umich.edu

Daniel Genkin University of Michigan genkin@umich.edu

Daniel Gruss Graz University of Technology daniel.gruss@iaik.tugraz.at

Yuval Yarom University of Adelaide and Data61 yval@cs.adelaide.edu.au

### More Security Implications (VII)

USENIX Security 2019

# Terminal Brain Damage: Exposing the Graceless Degradation in Deep Neural Networks Under Hardware Fault Attacks

Sanghyun Hong, Pietro Frigo<sup>†</sup>, Yiğitcan Kaya, Cristiano Giuffrida<sup>†</sup>, Tudor Dumitraș

University of Maryland, College Park

†Vrije Universiteit Amsterdam

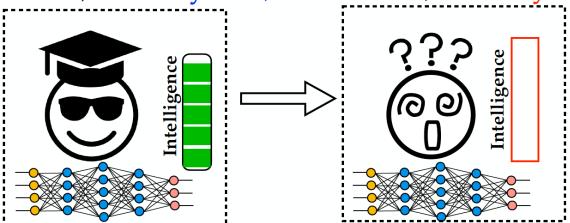

#### A Single Bit-flip Can Cause Terminal Brain Damage to DNNs

One specific bit-flip in a DNN's representation leads to accuracy drop over 90%

Our research found that a specific bit-flip in a DNN's bitwise representation can cause the accuracy loss up to 90%, and the DNN has 40-50% parameters, on average, that can lead to the accuracy drop over 10% when individually subjected to such single bitwise corruptions...

**Read More**

### More Security Implications (VIII)

#### USENIX Security 2020

## DeepHammer: Depleting the Intelligence of Deep Neural Networks through Targeted Chain of Bit Flips

Fan Yao

University of Central Florida

fan.yao@ucf.edu

Adnan Siraj Rakin Deliang Fan Arizona State University asrakin@asu.edu dfan@asu.edu

#### Degrade the inference accuracy to the level of Random Guess

Example: ResNet-20 for CIFAR-10, 10 output classes

Before attack, Accuracy: 90.2% After attack, Accuracy: ~10% (1/10)

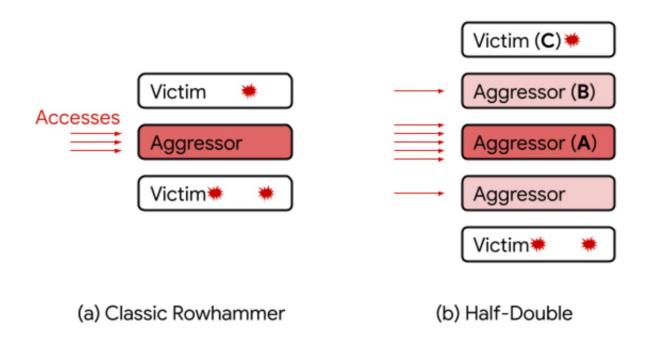

#### Google's Half-Double RowHammer Attack (May 2021)

#### Google Security Blog

The latest news and insights from Google on security and safety on the Internet

#### Introducing Half-Double: New hammering technique for DRAM Rowhammer bug

May 25, 2021

Research Team: Salman Qazi, Yoongu Kim, Nicolas Boichat, Eric Shiu & Mattias Nissler

Today, we are sharing details around our discovery of Half-Double, a new Rowhammer technique that capitalizes on the worsening physics of some of the newer DRAM chips to alter the contents of memory.

Rowhammer is a DRAM vulnerability whereby repeated accesses to one address can tamper with the data stored at other addresses. Much like speculative execution vulnerabilities in CPUs, Rowhammer is a breach of the security guarantees made by the underlying hardware. As an electrical coupling phenomenon within the silicon itself, Rowhammer allows the potential bypass of hardware and software memory protection policies. This can allow untrusted code to break out of its sandbox and take full control of the system.

### More Security Implications (VIII)

USENIX Security 2022

Google's Half-Double RowHammer Attack

The latest news and insights from Google on security and safety on the Internet

Introducing Half-Double: New hammering technique for DRAM Rowhammer bug

May 25, 2021

Research Team: Salman Qazi, Yoongu Kim, Nicolas Boichat, Eric Shiu & Mattias Nissle

Today, we are sharing details around our discovery of Half-Double, a new Rowhammer technique that capitalizes on the worsening physics of some of the newer DRAM chips to alter the contents of memory.

Rowhammer is a DRAM vulnerability whereby repeated accesses to one address can tamper with the data stored at other addresses. Much like speculative execution vulnerabilities in CPUs, Rowhammer is a breach of the security guarantees made by the underlying hardware. As an electrical coupling phenomenon within the silicon itself, Rowhammer allows the potential bypass of hardware and software memory protection policies. This can allow untrusted code to break out of its sandbox and take full control of the system.

#### **Half-Double: Hammering From the Next Row Over**

Andreas Kogler<sup>1</sup> Jonas Juffinger<sup>1,2</sup> Salman Qazi<sup>3</sup> Yoongu Kim<sup>3</sup> Moritz Lipp<sup>4\*</sup>

Nicolas Boichat<sup>3</sup> Eric Shiu<sup>5</sup> Mattias Nissler<sup>3</sup> Daniel Gruss<sup>1</sup>

<sup>1</sup>Graz University of Technology <sup>2</sup>Lamarr Security Research <sup>3</sup>Google <sup>4</sup>Amazon Web Services <sup>5</sup>Rivos

## More Security Implications?

#### A RowHammer Survey Across the Stack

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

<u>IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems</u> (**TCAD**) Special Issue on Top Picks in Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

[Slides from COSADE 2019 (pptx)]

[Slides from VLSI-SOC 2020 (pptx) (pdf)]

[Talk Video (1 hr 15 minutes, with Q&A)]

## RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> §ETH Zürich <sup>‡</sup>Carnegie Mellon University

SAFARI

### A RowHammer Survey: Recent Update

Onur Mutlu, Ataberk Olgun, and A. Giray Yaglikci,

"Fundamentally Understanding and Solving RowHammer"

Invited Special Session Paper at the <u>28th Asia and South Pacific Design Automation Conference (ASP-DAC)</u>, Tokyo, Japan, January 2023.

[arXiv version]

[Slides (pptx) (pdf)]

[Talk Video (26 minutes)]

#### Fundamentally Understanding and Solving RowHammer

Onur Mutlu

onur.mutlu@safari.ethz.ch

ETH Zürich

Zürich, Switzerland

Ataberk Olgun ataberk.olgun@safari.ethz.ch ETH Zürich Zürich, Switzerland A. Giray Yağlıkcı giray.yaglikci@safari.ethz.ch ETH Zürich Zürich, Switzerland

https://arxiv.org/pdf/2211.07613.pdf

45

## Understanding RowHammer

#### First RowHammer Analysis [ISCA 2014]

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

<u>"Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors"</u>

Proceedings of the <u>41st International Symposium on Computer Architecture</u> (**ISCA**), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data] [Lecture Video (1 hr 49 mins), 25 September 2020]

One of the 7 papers of 2012-2017 selected as Top Picks in Hardware and Embedded Security for IEEE TCAD (<u>link</u>).

Selected to the ISCA-50 25-Year Retrospective Issue covering 1996-2020 in 2023 (Retrospective (pdf) Full Issue).

#### Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly\* Jeremie Kim<sup>1</sup> Chris Fallin\* Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup>

<sup>1</sup>Carnegie Mellon University <sup>2</sup>Intel Labs

SAFARI

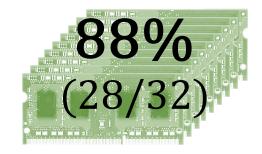

#### RowHammer Infrastructure (2012-2014)

Tested

DRAM

Modules

from

2008-2014

(129 total)

| Manufacturer                | Module                                   | Date* (yy-ww)  | $Timing^{\dagger}$ |                      | Organization |       | Chip                   |          |                             | Victims-per-Module                         |                                         |                                            | RI <sub>th</sub> (ms) |

|-----------------------------|------------------------------------------|----------------|--------------------|----------------------|--------------|-------|------------------------|----------|-----------------------------|--------------------------------------------|-----------------------------------------|--------------------------------------------|-----------------------|

|                             |                                          |                | Freq (MT/s)        | t <sub>RC</sub> (ns) | Size (GB)    | Chips | Size (Gb) <sup>‡</sup> | Pins     | Die Version <sup>§</sup>    | Average                                    | Minimum                                 | Maximum                                    | Min                   |

| A<br>Total of<br>43 Modules | $A_1$                                    | 10-08          | 1066               | 50.625               | 0.5          | 4     | 1                      | ×16      | $\mathcal{B}$               | 0                                          | 0                                       | 0                                          | -                     |

|                             | A <sub>2</sub>                           | 10-20          | 1066               | 50.625               | 1            | 8     | 1                      | ×8       | F                           | 0                                          | 0                                       | 0                                          | -                     |

|                             | A <sub>3-5</sub>                         | 10-20          | 1066               | 50.625               | 0.5          | 4     | 1                      | ×16      | В                           | 0                                          | 0                                       | 0                                          | -                     |

|                             | A <sub>6-7</sub>                         | 11-24          | 1066               | 49.125               | 1            | 4     | 2                      | ×16      | $\mathcal{D}$               | $7.8 \times 10^{1}$                        | $5.2 \times 10^{1}$                     | $1.0 \times 10^{2}$                        | 21.3                  |

|                             | A <sub>8-12</sub>                        | 11-26          | 1066               | 49.125               | 1            | 4     | 2                      | ×16      | D                           | $2.4 \times 10^{2}$                        | $5.4 \times 10^{1}$                     | $4.4 \times 10^{2}$                        | 16.4                  |

|                             | A <sub>13-14</sub>                       | 11-50          | 1066               | 49.125               | 1            | 4     | 2                      | ×16      | $\mathcal{D}$               | $8.8 \times 10^{1}$                        | $1.7 \times 10^{1}$                     | $1.6 \times 10^{2}$                        | 26.2                  |

|                             | A <sub>15-16</sub>                       | 12-22          | 1600               | 50.625               | 1            | 4     | 2                      | ×16      |                             | 9.5                                        | 9                                       | $1.0 \times 10^{1}$                        | 34.4                  |

|                             | A <sub>17-18</sub>                       | 12-26          | 1600               | 49.125               | 2            | 8     | 2                      | ×8       | M                           | $1.2 \times 10^2$                          | $3.7 \times 10^{1}$                     | $2.0 \times 10^{2}$                        | 21.3                  |

|                             | A <sub>19-30</sub>                       | 12-40          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | $\kappa$                    |                                            | $7.0 \times 10^6$                       |                                            | 8.2                   |

|                             | A <sub>31-34</sub>                       | 13-02          | 1600               | 48.125               | 2 2          | 8     | 2 2                    | ×8<br>×8 | _                           | $1.8 \times 10^{6}$                        | $1.0 \times 10^6$<br>$1.9 \times 10^1$  | $3.5 \times 10^{6}$                        | 11.5                  |

|                             | A <sub>35-36</sub>                       | 13-14          | 1600               | 48.125               |              |       |                        |          |                             | $4.0 \times 10^{1}$<br>$1.7 \times 10^{6}$ | $1.9 \times 10^{6}$ $1.4 \times 10^{6}$ | $6.1 \times 10^{1}$<br>$2.0 \times 10^{6}$ | 21.3                  |

|                             | A <sub>37-38</sub>                       | 13-20          | 1600               | 48.125               | 2            | 8     | 2 2                    | ×8       | K                           | $5.7 \times 10^{4}$                        |                                         | $6.0 \times 10^4$                          | 9.8                   |

|                             | A <sub>39-40</sub>                       | 13-28          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | ~                           |                                            | $2.7 \times 10^5$                       |                                            | 16.4                  |

|                             | A <sub>41</sub>                          | 14-04<br>14-04 | 1600<br>1600       | 49.125<br>48.125     | 2            | 8     | 2                      | ×8<br>×8 | ĸ                           | 0.5                                        | 0                                       | $2.7 \times 10^{5}$                        | 18.0<br>62.3          |

|                             | A <sub>42-43</sub>                       |                |                    |                      |              |       |                        |          |                             |                                            |                                         |                                            | 02.3                  |

| В                           | Bı                                       | 08-49          | 1066               | 50.625               | 1            | 8     | 1                      | ×8       | $\mathcal{D}$               | 0                                          | 0                                       | 0                                          | -                     |

|                             | B <sub>2</sub>                           | 09-49          | 1066               | 50.625               | 1            | 8     | 1                      | ×8       | $\frac{\mathcal{E}}{T}$     | 0                                          | 0                                       | 0                                          | -                     |

|                             | B <sub>3</sub>                           | 10-19          | 1066               | 50.625               | 1            | 8     | 1                      | ×8       | F                           | 0                                          | 0                                       | 0                                          | -                     |

|                             | B <sub>4</sub>                           | 10-31          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | C                           | 0                                          | 0                                       | 0                                          | -                     |

|                             | B <sub>5</sub>                           | 11-13          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | C<br>F                      | 0                                          | 0                                       | 0                                          | -                     |

|                             | B <sub>6</sub>                           | 11-16          | 1066               | 50.625               |              | 8     | 1                      | ×8       | F                           | 0                                          | 0                                       | 0                                          | -                     |

|                             | B <sub>7</sub><br>B <sub>8</sub>         | 11-19<br>11-25 | 1066<br>1333       | 50.625<br>49.125     | 2            | 8     | 2                      | ×8<br>×8 | C                           | 0                                          | 0                                       | 0                                          |                       |

|                             | B <sub>9</sub>                           | 11-23          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | $\mathcal{D}$               | $1.9 \times 10^{6}$                        | $1.9 \times 10^{6}$                     | $1.9 \times 10^{6}$                        | 11.5                  |

| Ь                           | D <sub>9</sub>                           | 11-46          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | $\mathcal{D}$               | $2.2 \times 10^6$                          |                                         | $2.7 \times 10^6$                          | 11.5                  |

| Total of<br>54 Modules      | B <sub>10-12</sub>                       | 11-40          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | c                           | 0                                          | 0                                       | 0                                          | 11.3                  |

|                             | B <sub>13</sub><br>B <sub>14</sub>       | 12-01          | 1866               | 47.125               | 2            | 8     | 2                      | ×8       | $\mathcal{D}$               | $9.1 \times 10^{5}$                        | $9.1 \times 10^{5}$                     |                                            | 9.8                   |

|                             | D <sub>14</sub>                          | 12-10          | 1866               | 47.125               | 2            | 8     | 2                      | ×8       | $\mathcal{D}$               | $9.8 \times 10^{5}$                        | $7.8 \times 10^{5}$                     | $1.2 \times 10^{6}$                        | 11.5                  |

|                             | B <sub>15-31</sub>                       | 12-10          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | ε                           |                                            | $7.4 \times 10^5$                       |                                            | 11.5                  |

|                             | B <sub>32</sub>                          | 12-23          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | ε                           |                                            | $1.9 \times 10^{5}$                     |                                            | 11.5                  |

|                             | B <sub>33-42</sub><br>B <sub>43-47</sub> | 12-28          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | ε                           |                                            | $2.9 \times 10^{5}$                     | $5.5 \times 10^5$                          | 13.1                  |

|                             |                                          | 13-19          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | ε                           |                                            | $7.4 \times 10^4$                       |                                            | 14.7                  |

|                             | B <sub>48-51</sub>                       | 13-40          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | $\mathcal{D}$               |                                            | $2.3 \times 10^4$                       |                                            | 21.3                  |

|                             | B <sub>52-53</sub><br>B <sub>54</sub>    | 14-07          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | $\mathcal{D}$               |                                            | $7.5 \times 10^3$                       |                                            | 26.2                  |

|                             |                                          |                |                    |                      |              |       |                        |          |                             |                                            |                                         |                                            |                       |

| C                           | C <sub>1</sub>                           | 10-18          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | $\mathcal{A}$               | 0                                          | 0                                       | 0                                          | -                     |

|                             | C <sub>2</sub>                           | 10-20          | 1066               | 50.625               | 2            | 8     | 2                      | ×8       | A                           | 0                                          | 0                                       | 0                                          | -                     |

|                             | C <sub>3</sub>                           | 10-22          | 1066               | 50.625               | 2            | 8     | 2                      | ×8       | A                           | 0                                          | 0                                       | 0                                          | -                     |

|                             | C <sub>4-5</sub>                         | 10-26          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | B                           | $8.9 \times 10^{2}$                        | $6.0 \times 10^{2}$                     | $1.2 \times 10^{3}$                        | 29.5                  |

|                             | U <sub>6</sub>                           | 10-43          | 1333               | 49.125               | 1 2          | 8     | 1 2                    | ×8       | $\mathcal{T}$ $\mathcal{B}$ | 0                                          | $0 \\ 4.0 \times 10^{2}$                | $0 \\ 4.0 \times 10^{2}$                   | - 20.5                |

|                             | C <sub>7</sub>                           | 10-51          | 1333<br>1333       | 49.125               | 2            | 8     | 2                      | ×8<br>×8 | В                           | $4.0 \times 10^2$<br>$6.9 \times 10^2$     | $6.9 \times 10^{2}$                     | $6.9 \times 10^{2}$                        | 29.5<br>21.3          |

|                             | C <sub>8</sub>                           | 11-12          |                    | 46.25                |              | 8     |                        |          |                             |                                            | $9.2 \times 10^{-2}$                    |                                            |                       |

|                             | C <sub>9</sub><br>C <sub>10</sub>        | 11-19<br>11-31 | 1333<br>1333       | 46.25<br>49.125      | 2 2          | 8     | 2 2                    | ×8<br>×8 | B<br>B                      | $9.2 \times 10^{2}$                        | 3.2 × 10-                               | 3.2 × 10-                                  | 27.9<br>39.3          |

|                             |                                          | 11-31          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | В                           | $1.6 \times 10^{2}$                        | $1.6 \times 10^{2}$                     | $1.6 \times 10^{2}$                        | 39.3                  |

|                             | C <sub>11</sub>                          | 11-42          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | C                           | $7.1 \times 10^{4}$                        | $7.1 \times 10^4$                       |                                            | 19.7                  |

|                             | C <sub>12</sub>                          | 12-08          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | c                           | $3.9 \times 10^4$                          | $3.9 \times 10^4$                       |                                            | 21.3                  |

| Total of                    | C <sub>13</sub>                          | 12-08          | 1333               | 49.125               | 2            | 8     | 2                      | ×8       | c                           | 3.7 × 10 <sup>4</sup>                      | $2.1 \times 10^4$                       |                                            | 21.3                  |

| 32 Modules                  | C <sub>14-15</sub>                       | 12-12          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | c                           | $3.7 \times 10^{3}$<br>$3.5 \times 10^{3}$ | $1.2 \times 10^3$                       | $7.0 \times 10^3$                          | 27.9                  |

|                             | C <sub>16-18</sub><br>C <sub>19</sub>    | 12-23          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | ε                           | $1.4 \times 10^5$                          | $1.4 \times 10^{5}$                     | $1.4 \times 10^{5}$                        | 18.0                  |

|                             | C <sub>20</sub>                          | 12-23          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | c                           | $6.5 \times 10^4$                          | $6.5 \times 10^4$                       |                                            | 21.3                  |

|                             | C <sub>21</sub>                          | 12-24          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | c                           | $2.3 \times 10^4$                          |                                         |                                            | 24.6                  |

|                             | C <sub>22</sub>                          | 12-20          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | c                           |                                            | $1.7 \times 10^4$                       |                                            | 22.9                  |

|                             | G <sub>22</sub>                          | 12-32          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | c                           |                                            | $1.1 \times 10^4$                       |                                            | 18.0                  |

|                             | C <sub>23-24</sub><br>C <sub>25-30</sub> | 12-37          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | c                           |                                            | $1.1 \times 10^4$                       |                                            | 19.7                  |

|                             | C <sub>31</sub>                          | 13-11          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | c                           |                                            | $3.3 \times 10^{5}$                     |                                            | 14.7                  |

|                             | C <sub>32</sub>                          | 13-35          | 1600               | 48.125               | 2            | 8     | 2                      | ×8       | c                           | $3.7 \times 10^4$                          | $3.7 \times 10^4$                       |                                            | 21.3                  |

|                             |                                          |                |                    |                      |              |       |                        |          |                             |                                            |                                         |                                            |                       |

<sup>\*</sup> We report the manufacture date marked on the chip packages, which is more accurate than other dates that can be gleaned from a module.

† We report timing constraints stored in the module's on-board ROM [33], which is read by the system BIOS to calibrate the memory controller.

‡ The maximum DRAM chip size supported by our testing platform is 2Gb.

<sup>§</sup> We report DRAM die versions marked on the chip packages, which typically progress in the following manner:  $\mathcal{M} \to \mathcal{A} \to \mathcal{B} \to \mathcal{C} \to \cdots$ .

Table 3. Sample population of 129 DDR3 DRAM modules, categorized by manufacturer and sorted by manufacture date

#### RowHammer Characterization Results

- 1. Most Modules Are at Risk

- 2. Errors vs. Vintage

- 3. Error = Charge Loss

- 4. Adjacency: Aggressor & Victim

- 5. Sensitivity Studies

- 6. Other Results in Paper

- 7. Solution Space

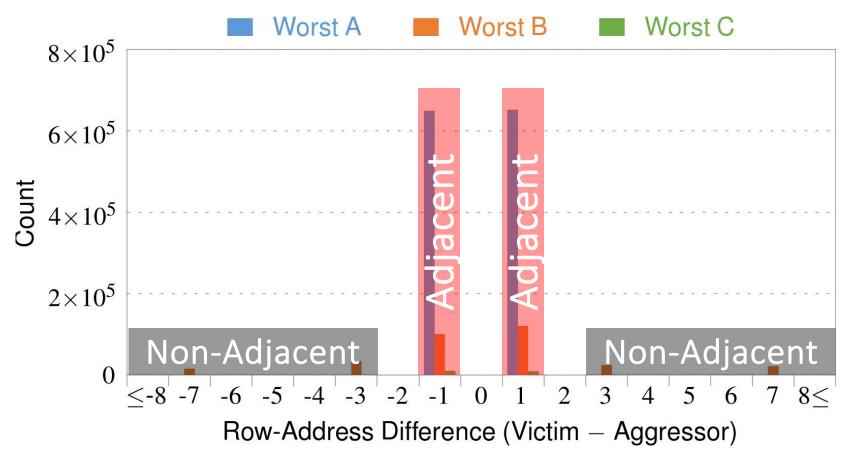

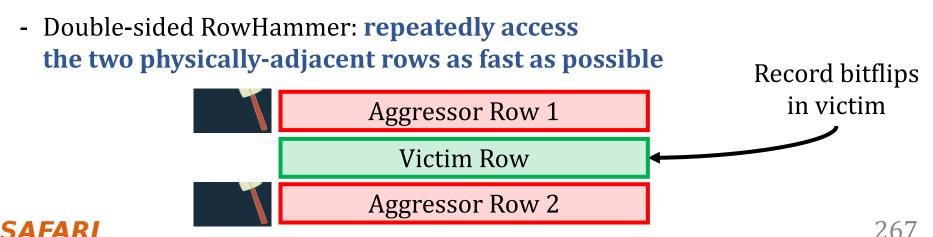

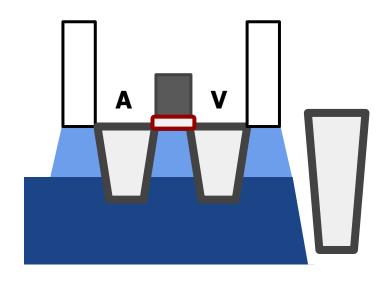

## 4. Adjacency: Aggressor & Victim

Note: For three modules with the most errors (only first bank)

Most aggressors & victims are adjacent

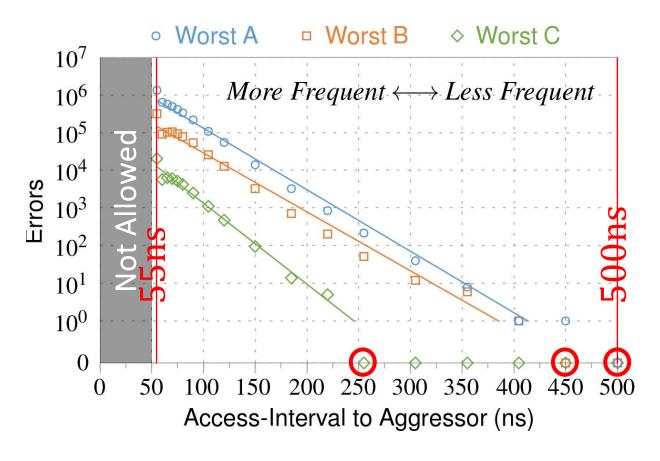

## Access Interval (Aggressor)

Note: For three modules with the most errors (only first bank)

Less frequent accesses → Fewer errors

## 2 Refresh Interval

Note: Using three modules with the most errors (only first bank)

*More frequent refreshes*  $\rightarrow$  *Fewer errors*

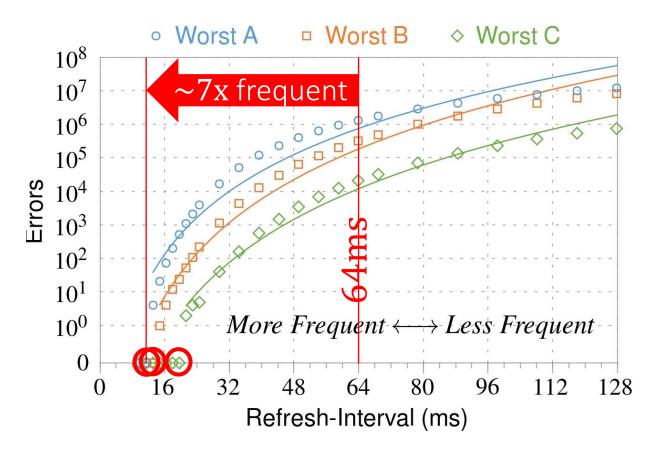

## B Data Pattern

# Solid ~Solid 00000 00000 00000 00000

Errors affected by data stored in other cells

## 6. Other Key Observations [ISCA'14]

- Victim Cells ≠ Retention-Weak Cells

- Almost no overlap between them

- Errors are repeatable

- Across ten iterations of testing, >70% of victim cells had errors in every iteration

- As many as 4 errors per cache-line

- Simple ECC (e.g., SECDED) cannot prevent all errors

- Cells affected by two aggressors on either side

- Double sided hammering

### Major RowHammer Characteristics (2014)

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

"Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors"

Proceedings of the <u>41st International Symposium on Computer Architecture</u> (**ISCA**), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data] [Lecture Video (1 hr 49 mins), 25 September 2020]

One of the 7 papers of 2012-2017 selected as Top Picks in Hardware and Embedded Security for IEEE TCAD (<u>link</u>).

Selected to the ISCA-50 25-Year Retrospective Issue covering 1996-2020 in 2023 (Retrospective (pdf) Full Issue).

#### Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly\* Jeremie Kim<sup>1</sup> Chris Fallin\* Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup>

<sup>1</sup>Carnegie Mellon University <sup>2</sup>Intel Labs

SAFARI

### RowHammer is Getting Much Worse (2020)

Jeremie S. Kim, Minesh Patel, A. Giray Yaglikci, Hasan Hassan, Roknoddin Azizi, Lois Orosa, and Onur Mutlu,

"Revisiting RowHammer: An Experimental Analysis of Modern Devices and Mitigation Techniques"

Proceedings of the <u>47th International Symposium on Computer</u> <u>Architecture</u> (**ISCA**), Valencia, Spain, June 2020.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Talk Video (20 minutes)]

[Lightning Talk Video (3 minutes)]

# Revisiting RowHammer: An Experimental Analysis of Modern DRAM Devices and Mitigation Techniques

Jeremie S. Kim<sup>§†</sup> Minesh Patel<sup>§</sup> A. Giray Yağlıkçı<sup>§</sup> Hasan Hassan<sup>§</sup> Roknoddin Azizi<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§†</sup>

§ETH Zürich †Carnegie Mellon University

### RowHammer Has Many Dimensions (2021)

Lois Orosa, Abdullah Giray Yaglikci, Haocong Luo, Ataberk Olgun, Jisung Park, Hasan Hassan, Minesh Patel, Jeremie S. Kim, and Onur Mutlu,

"A Deeper Look into RowHammer's Sensitivities: Experimental Analysis of Real DRAM Chips and Implications on Future Attacks and Defenses"

Proceedings of the <u>54th International Symposium on Microarchitecture</u> (**MICRO**), Virtual, October 2021.

[Slides (pptx) (pdf)]

[Short Talk Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Talk Video (21 minutes)]

[Lightning Talk Video (1.5 minutes)]

[arXiv version]

#### A Deeper Look into RowHammer's Sensitivities: Experimental Analysis of Real DRAM Chips and Implications on Future Attacks and Defenses

Lois Orosa\* ETH Zürich A. Giray Yağlıkçı\*

ETH Zürich

Haocong Luo ETH Zürich Ataberk Olgun ETH Zürich, TOBB ETÜ Jisung Park

ETH Zürich

Hasan Hassan ETH Zürich Minesh Patel ETH Zürich

Jeremie S. Kim ETH Zürich Onur Mutlu ETH Zürich

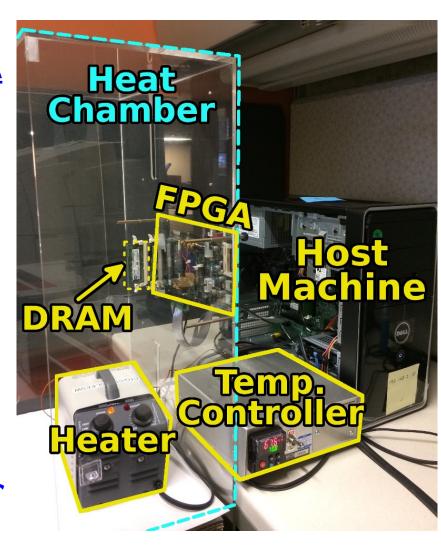

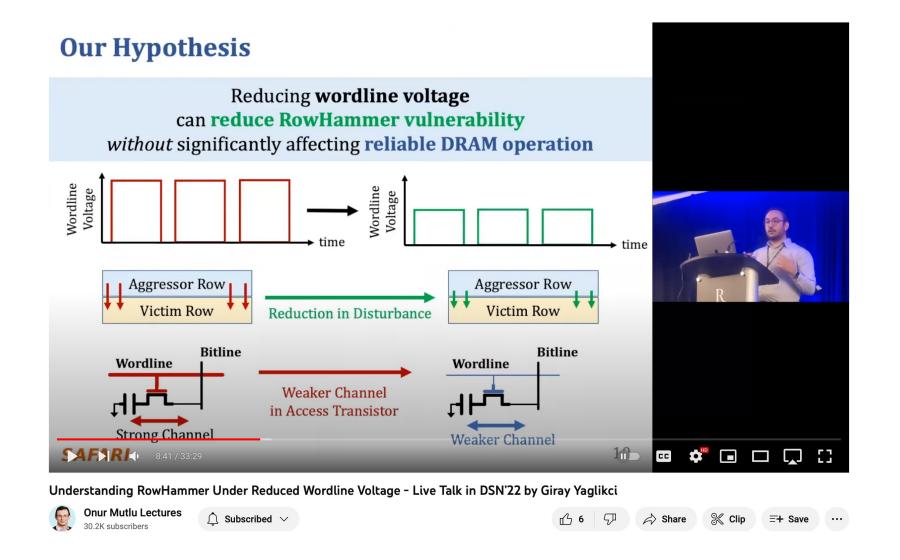

### RowHammer vs. Wordline Voltage (2022)

A. Giray Yağlıkçı, Haocong Luo, Geraldo F. de Oliviera, Ataberk Olgun, Minesh Patel, Jisung Park, Hasan Hassan, Jeremie S. Kim, Lois Orosa, and Onur Mutlu, "Understanding RowHammer Under Reduced Wordline Voltage: An Experimental Study Using Real DRAM Devices"

Proceedings of the <u>52nd Annual IEEE/IFIP International Conference on</u>

<u>Dependable Systems and Networks</u> (**DSN**), Baltimore, MD, USA, June 2022.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[arXiv version]

[Talk Video (34 minutes, including Q&A)]

[<u>Lightning Talk Video</u> (2 minutes)]

#### Understanding RowHammer Under Reduced Wordline Voltage: An Experimental Study Using Real DRAM Devices

A. Giray Yağlıkçı<sup>1</sup> Haocong Luo<sup>1</sup> Geraldo F. de Oliviera<sup>1</sup> Ataberk Olgun<sup>1</sup> Minesh Patel<sup>1</sup> Jisung Park<sup>1</sup> Hasan Hassan<sup>1</sup> Jeremie S. Kim<sup>1</sup> Lois Orosa<sup>1,2</sup> Onur Mutlu<sup>1</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>Galicia Supercomputing Center (CESGA)

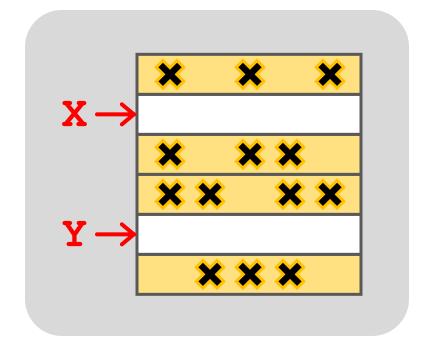

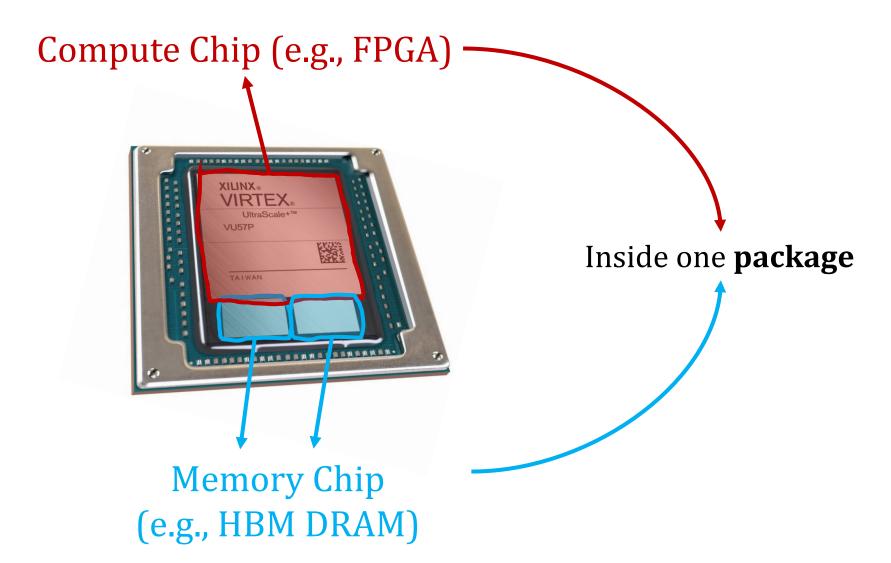

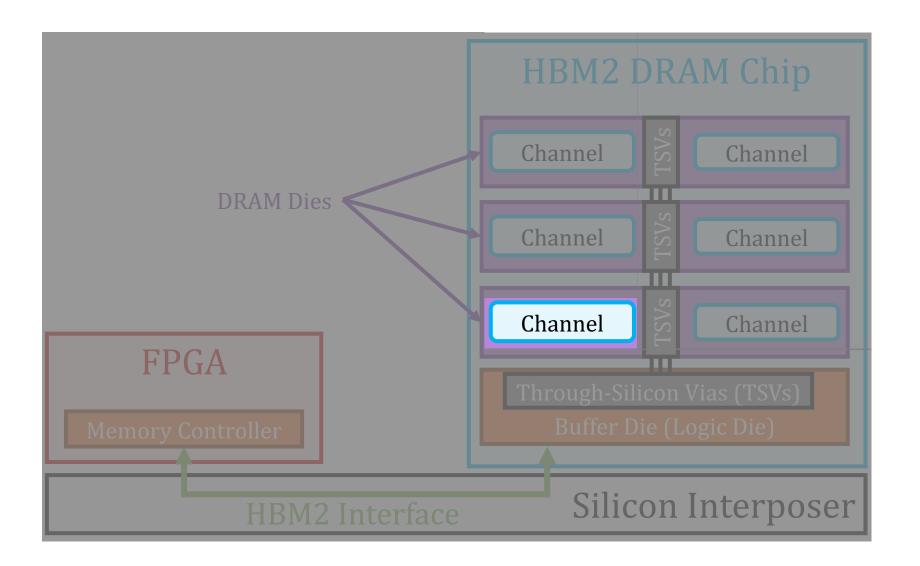

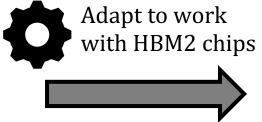

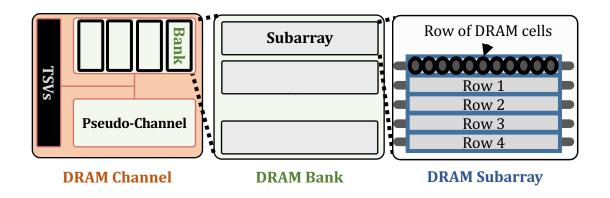

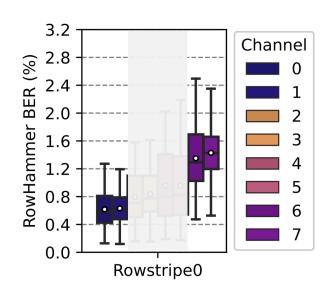

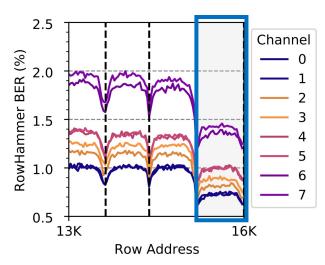

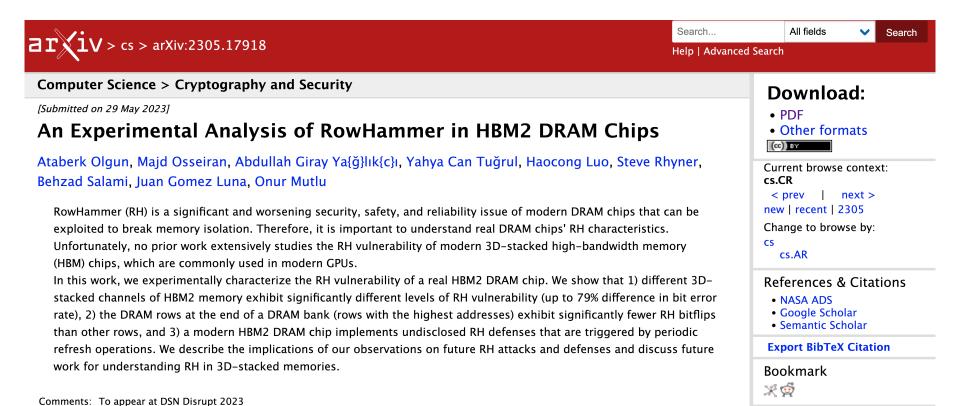

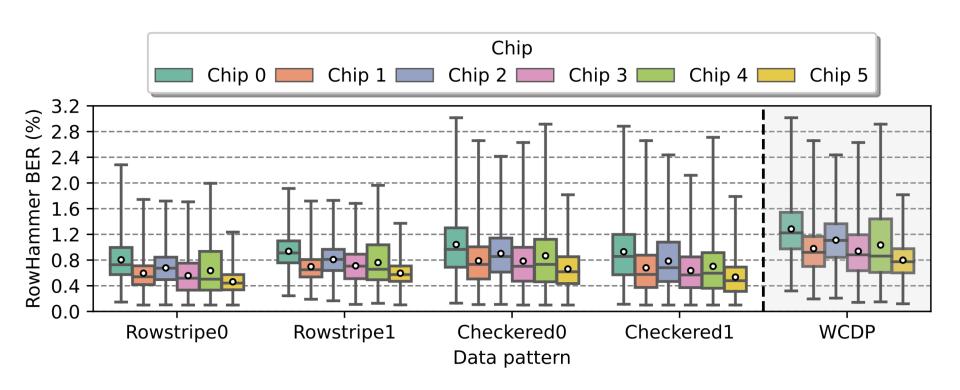

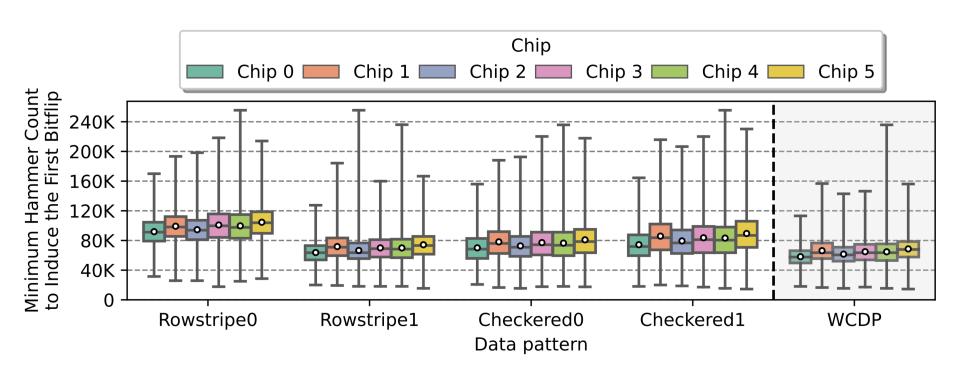

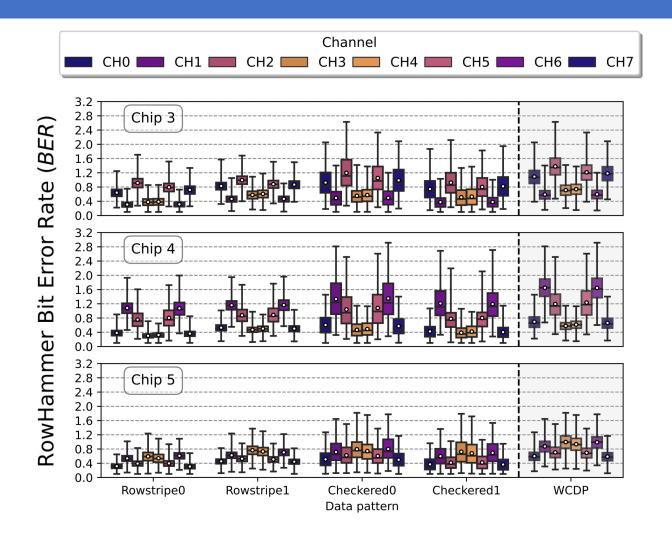

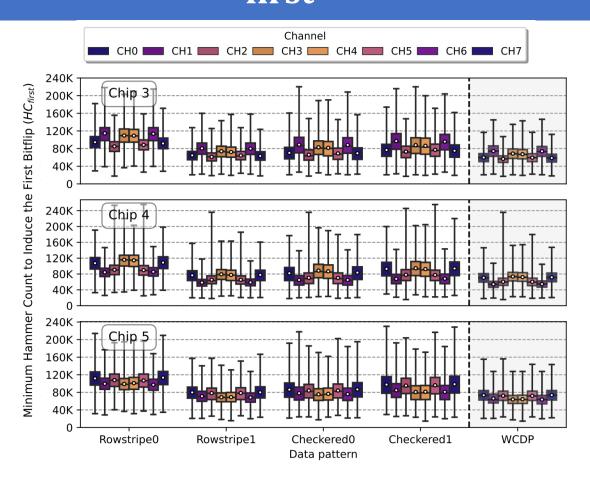

### RowHammer in HBM Chips (2023)

Ataberk Olgun, Majd Osserian, A. Giray Yağlıkçı, Yahya Can Tugrul, Haocong Luo, Steve Rhyner, Behzad Salami, Juan Gomez-Luna, and Onur Mutlu, "An Experimental Analysis of RowHammer in HBM2 DRAM Chips" Proceedings of the <u>53nd Annual IEEE/IFIP International Conference on Dependable Systems and Networks</u> Disrupt Track (DSN Disrupt), Porto, Portugal, June 2023.

[arXiv version]

[Slides (pptx) (pdf)]

[Talk Video (24 minutes, including Q&A)]

#### An Experimental Analysis of RowHammer in HBM2 DRAM Chips

Ataberk Olgun<sup>1</sup> Majd Osseiran<sup>1,2</sup> A. Giray Yağlıkçı<sup>1</sup> Yahya Can Tuğrul<sup>1</sup> Haocong Luo<sup>1</sup> Steve Rhyner<sup>1</sup> Behzad Salami<sup>1</sup> Juan Gomez Luna<sup>1</sup> Onur Mutlu<sup>1</sup>

\*\*ISAFARI Research Group, ETH Zürich\*\*

\*\*Parameter Variation\*\*

\*\*Parameter Variation\*\*

\*\*Parameter Variation\*\*

\*\*Index of Beirut\*\*

\*\*Parameter Variation\*\*

\*\*Index of Beirut\*\*

\*\*Parameter Variation\*\*

\*\*Pa

60

### RowHammer in HBM Chips (2024)

Appears at DSN 2024

# Read Disturbance in High Bandwidth Memory: A Detailed Experimental Study on HBM2 DRAM Chips

```

Ataberk Olgun<sup>1</sup> Majd Osseiran<sup>1</sup> A. Giray Yağlıkçı<sup>1</sup> Yahya Can Tuğrul<sup>1</sup> Haocong Luo<sup>1</sup> Steve Rhyner<sup>1</sup> Behzad Salami<sup>2</sup> Juan Gomez Luna<sup>1</sup> Onur Mutlu<sup>1</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>BSC

```

https://arxiv.org/pdf/2310.14665

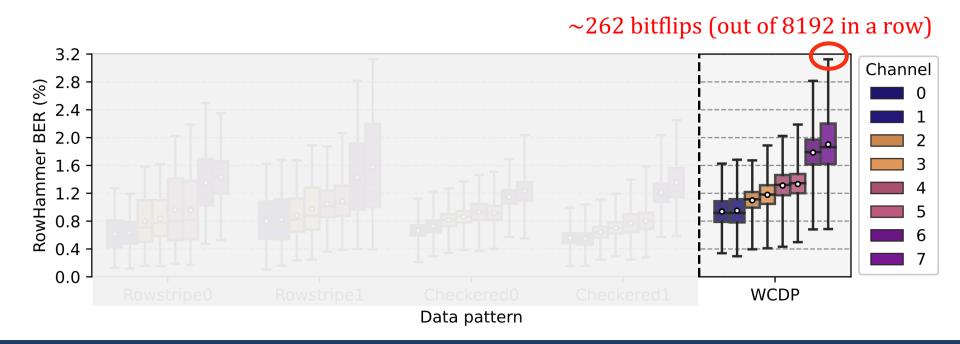

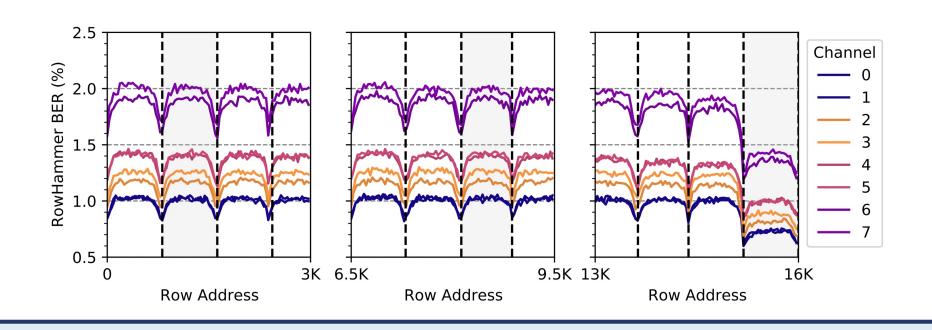

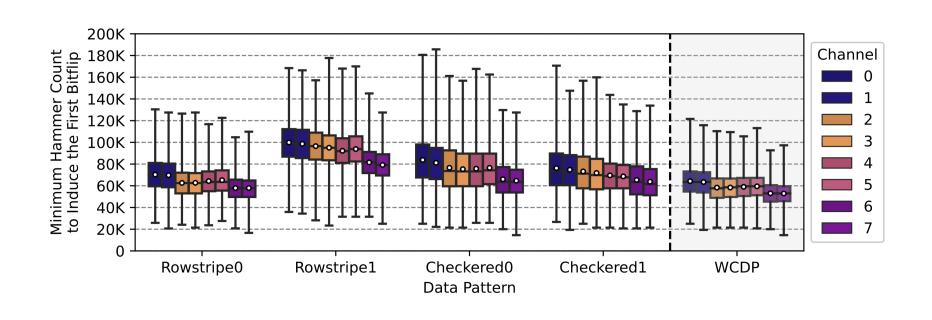

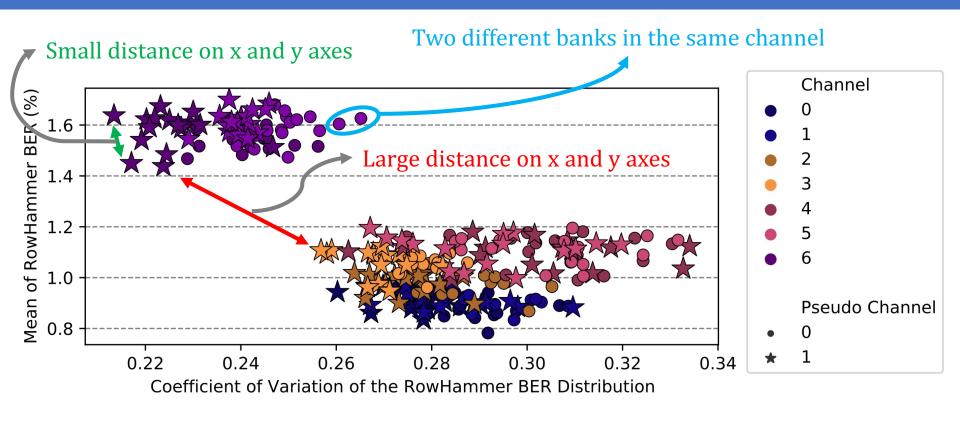

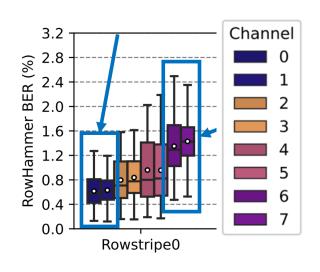

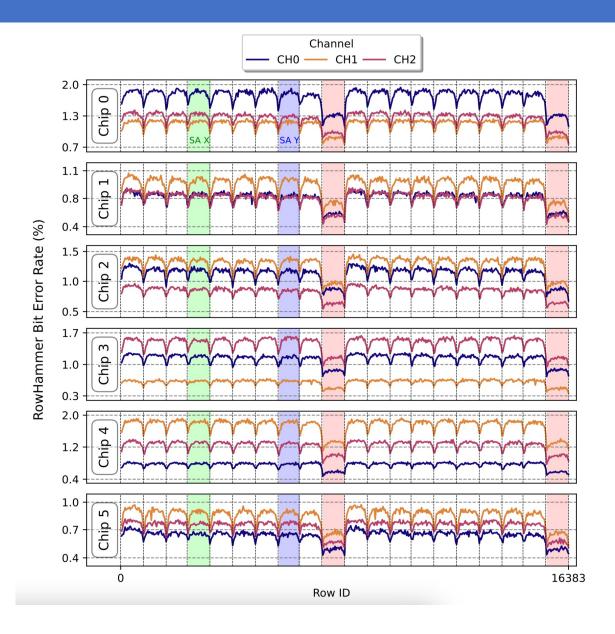

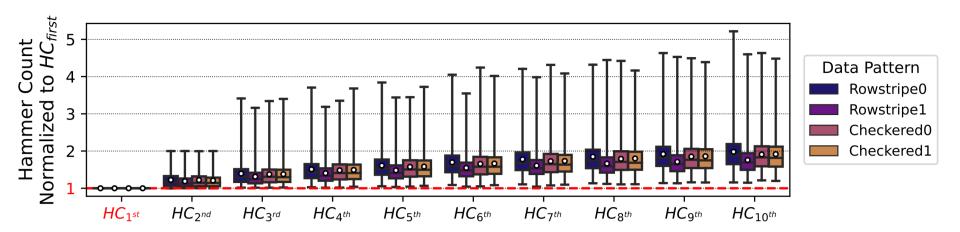

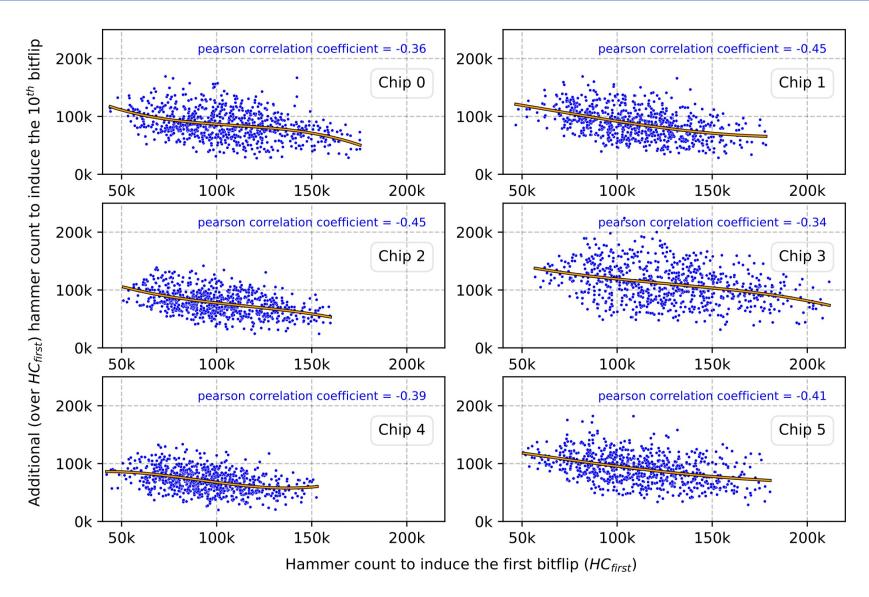

#### RowHammer Spatial Variation Analysis (2024)

Appears at HPCA 2024

#### Spatial Variation-Aware Read Disturbance Defenses: Experimental Analysis of Real DRAM Chips and Implications on Future Solutions

Abdullah Giray Yağlıkçı Yahya Can Tuğrul Geraldo F. Oliveira İsmail Emir Yüksel Ataberk Olgun Haocong Luo Onur Mutlu ETH Zürich

https://arxiv.org/pdf/2402.18652

## RowHammer Solutions

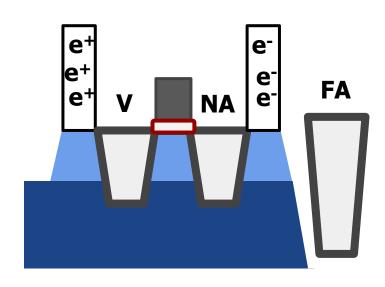

#### Two Types of RowHammer Solutions

#### Immediate

- To protect the vulnerable DRAM chips in the field

- Limited possibilities

- Longer-term

- To protect future DRAM chips

- Wider range of protection mechanisms

- Our ISCA 2014 paper proposes both types of solutions

- Seven solutions in total

- □ PARA proposed as best solution → already employed in the field

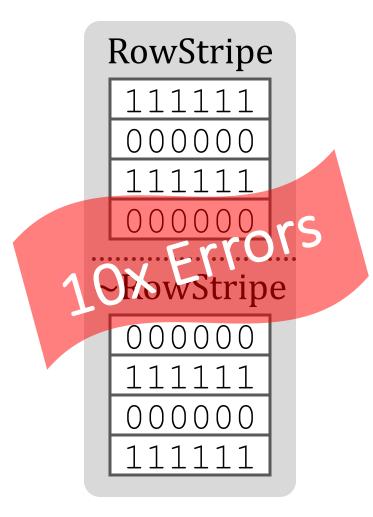

#### **RowHammer Solution Approaches**

- More robust DRAM chips and/or error-correcting codes

- Increased refresh rate

65

### Apple's Security Patch for RowHammer

https://support.apple.com/en-gb/HT204934

Available for: OS X Mountain Lion v10.8.5, OS X Mavericks v10.9.5

Impact: A malicious application may induce memory corruption to escalate privileges

Description: A disturbance error, also known as Rowhammer, exists with some DDR3 RAM that could have led to memory corruption. This issue was mitigated by increasing memory refresh rates.

CVE-ID

CVE-2015-3693 : Mark Seaborn and Thomas Dullien of Google, working from original research by Yoongu Kim et al (2014)

HP, Lenovo, and many other vendors released similar patches

#### Our First Solution to RowHammer

PARA: <u>Probabilistic Adjacent Row Activation</u>

#### Key Idea

- After closing a row, activate (i.e., refresh) its neighbors with a low probability: p = 0.005

#### Reliability Guarantee

- When p=0.005, errors in one year:  $9.4 \times 10^{-14}$

- By adjusting the value of p, we can vary the strength of protection against errors

### Advantages of PARA

- PARA refreshes rows infrequently

- Low power

- Low performance-overhead

- Average slowdown: 0.20% (for 29 benchmarks)

- Maximum slowdown: 0.75%

- PARA is stateless

- Low cost

- Low complexity

- PARA is an effective and low-overhead solution to prevent disturbance errors

## Requirements for PARA

- If implemented in DRAM chip (done today)

- Enough slack in timing and refresh parameters

- Plenty of slack today:

- Lee et al., "Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common Case," HPCA 2015.

- Chang et al., "Understanding Latency Variation in Modern DRAM Chips," SIGMETRICS 2016.

- Lee et al., "Design-Induced Latency Variation in Modern DRAM Chips," SIGMETRICS 2017.

- Chang et al., "Understanding Reduced-Voltage Operation in Modern DRAM Devices," SIGMETRICS 2017.

- Ghose et al., "What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study," SIGMETRICS 2018.

- Kim et al., "Solar-DRAM: Reducing DRAM Access Latency by Exploiting the Variation in Local Bitlines," ICCD 2018.

- If implemented in memory controller

- Need coordination between controller and DRAM

- Memory controller should know which rows are physically adjacent

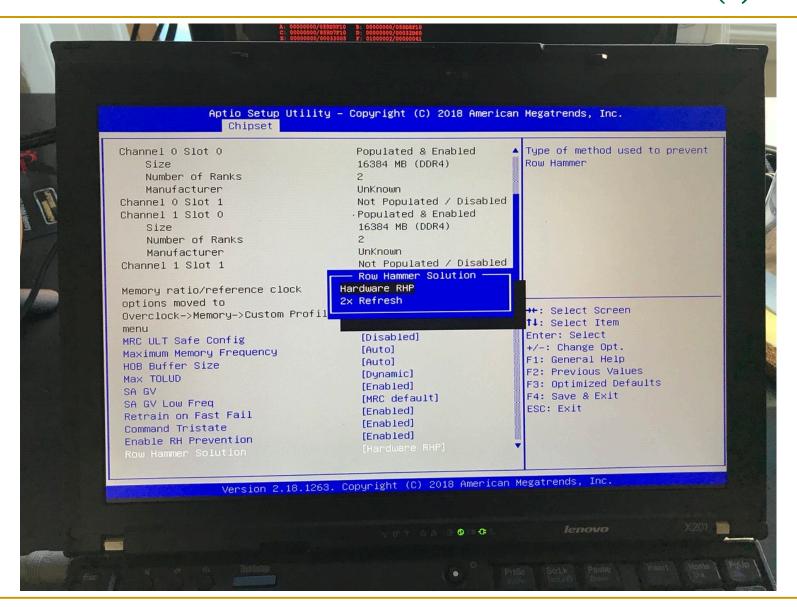

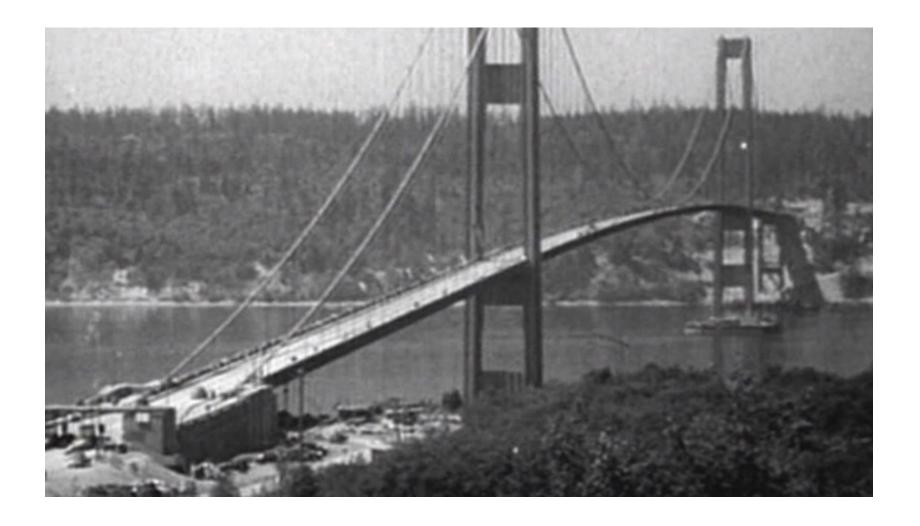

#### Probabilistic Activation in Real Life (I)

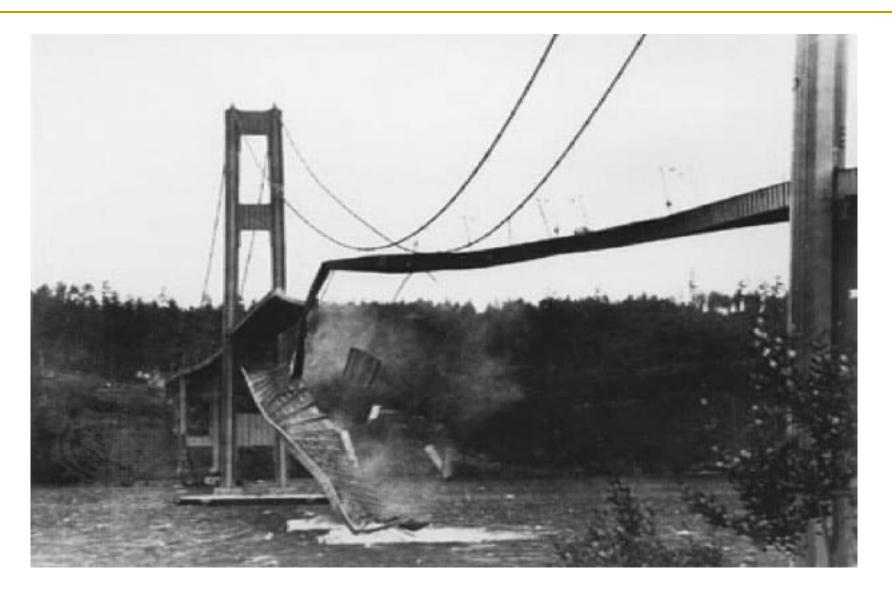

#### Probabilistic Activation in Real Life (II)

#### Seven RowHammer Solutions Proposed

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

"Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors"

Proceedings of the <u>41st International Symposium on Computer Architecture</u> (**ISCA**), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data] [Lecture Video (1 hr 49 mins), 25 September 2020]

One of the 7 papers of 2012-2017 selected as Top Picks in Hardware and Embedded Security for IEEE TCAD (<u>link</u>).

Selected to the ISCA-50 25-Year Retrospective Issue covering 1996-2020 in 2023 (Retrospective (pdf) Full Issue).

#### Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly\* Jeremie Kim<sup>1</sup> Chris Fallin\* Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup>

<sup>1</sup>Carnegie Mellon University <sup>2</sup>Intel Labs

SAFARI

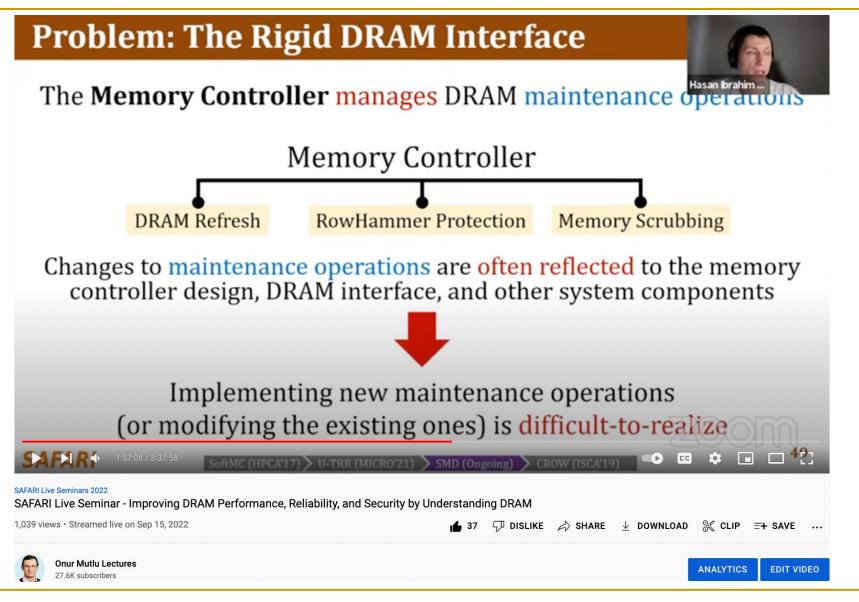

# Main Memory Needs Intelligent Controllers for Security, Safety, Reliability, Scaling

## Aside: Intelligent Controller for NAND Flash

[DATE 2012, ICCD 2012, DATE 2013, ITJ 2013, ICCD 2013, SIGMETRICS 2014, HPCA 2015, DSN 2015, MSST 2015, JSAC 2016, HPCA 2017, DFRWS 2017, PIEEE 2017, HPCA 2018, SIGMETRICS 2018]

NAND Daughter Board

## Intelligent Flash Controllers [PIEEE'17]

Proceedings of the IEEE, Sept. 2017

# Error Characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives

This paper reviews the most recent advances in solid-state drive (SSD) error characterization, mitigation, and data recovery techniques to improve both SSD's reliability and lifetime.

By Yu Cai, Saugata Ghose, Erich F. Haratsch, Yixin Luo, and Onur Mutlu

https://arxiv.org/pdf/1706.08642

## Two Major RowHammer Directions

#### Understanding RowHammer

- Many effects still need to be rigorously examined

- Aging of DRAM Chips

- Environmental Conditions (e.g., Process, Voltage, Temperature)

- Memory Access Patterns

- Memory Controller & System Design Decisions

#### Solving RowHammer

- Flexible and efficient solutions are necessary

- In-field patchable / reconfigurable / programmable solutions

- Co-architecting System and Memory is important

- To avoid performance and denial-of-service problems

# RowHammer in 2020-2024

# Revisiting RowHammer

# RowHammer is Getting Much Worse

Jeremie S. Kim, Minesh Patel, A. Giray Yaglikci, Hasan Hassan, Roknoddin Azizi, Lois Orosa, and Onur Mutlu,

"Revisiting RowHammer: An Experimental Analysis of Modern Devices and Mitigation Techniques"

Proceedings of the <u>47th International Symposium on Computer</u> <u>Architecture</u> (**ISCA**), Valencia, Spain, June 2020.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Talk Video (20 minutes)]

[Lightning Talk Video (3 minutes)]

# Revisiting RowHammer: An Experimental Analysis of Modern DRAM Devices and Mitigation Techniques

Jeremie S. Kim $^{\S \dagger}$  Minesh Patel $^{\S}$  A. Giray Yağlıkçı $^{\S}$  Hasan Hassan $^{\S}$  Roknoddin Azizi $^{\S}$  Lois Orosa $^{\S}$  Onur Mutlu $^{\S \dagger}$   $^{\S}$  ETH Zürich  $^{\dagger}$  Carnegie Mellon University

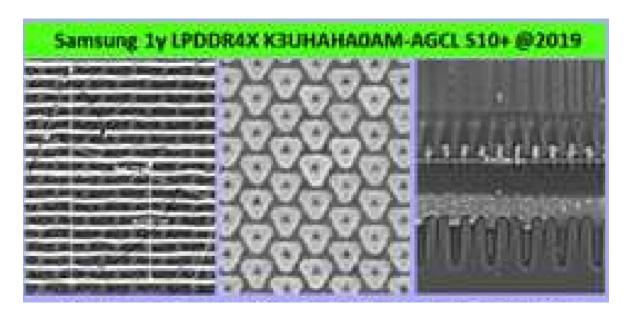

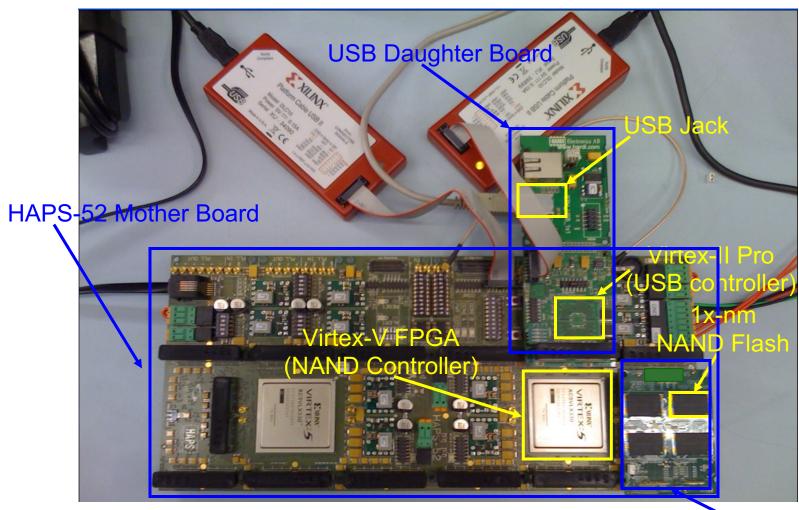

# Key Takeaways from 1580 Chips

Newer DRAM chips are much more vulnerable to RowHammer (more bit flips, happening earlier)

There are new chips whose weakest cells fail after only

4800 hammers

• Chips of newer DRAM technology nodes can exhibit RowHammer bit flips 1) in **more rows** and 2) **farther away** from the victim row.

Existing mitigation mechanisms are NOT effective at future technology nodes

SAFARI

# 1580 DRAM Chips Tested

| DRAM      | Numbe    | Number of Chips (Modules) |          |          |  |  |  |

|-----------|----------|---------------------------|----------|----------|--|--|--|

| type-node | Mfr. A   | Mfr. B                    | Mfr. C   | Total    |  |  |  |

| DDR3-old  | 56 (10)  | 88 (11)                   | 28 (7)   | 172 (28) |  |  |  |

| DDR3-new  | 80 (10)  | 52 (9)                    | 104 (13) | 236 (32) |  |  |  |

| DDR4-old  | 112 (16) | 24 (3)                    | 128 (18) | 264 (37) |  |  |  |

| DDR4-new  | 264 (43) | 16 (2)                    | 108 (28) | 388 (73) |  |  |  |

| LPDDR4-1x | 12 (3)   | 180 (45)                  | N/A      | 192 (48) |  |  |  |

| LPDDR4-1y | 184 (46) | N/A                       | 144 (36) | 328 (82) |  |  |  |

#### **1580** total DRAM chips tested from **300** DRAM modules

- **Three** major DRAM manufacturers {A, B, C}

- **Three** DRAM *types* or *standards* {DDR3, DDR4, LPDDR4}

- LPDDR4 chips we test implement on-die ECC

- Two technology nodes per DRAM type {old/new, 1x/1y}

- Categorized based on manufacturing date, datasheet publication date, purchase date, and characterization results

**Type-node:** configuration describing a chip's type and technology node generation: **DDR3-old/new, DDR4-old/new, LPDDR4-1x/1y**

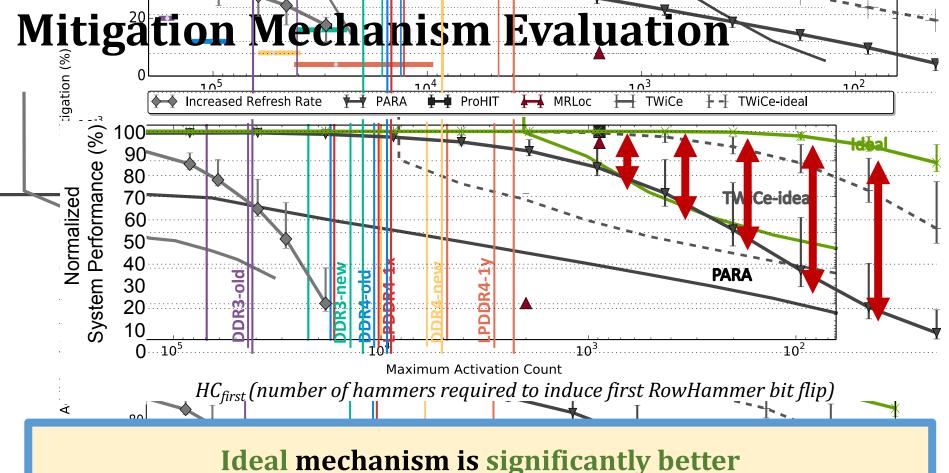

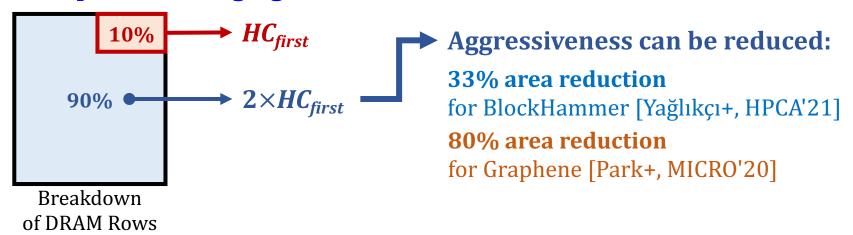

# 3. Hammer Count (HC) Effects

RowHammer bit flip rates **increase** when going **from old to new** DDR4 technology node generations

RowHammer bit flip rates (i.e., RowHammer vulnerability) increase with technology node generation

Ideal mechanism is significantly better than any existing mechanism for HC<sub>first</sub> < 1024

Significant opportunity for developing a RowHammer solution with low performance overhead that supports low  $HC_{first}$

# New RowHammer Characteristics

## RowHammer Has Many Dimensions

Lois Orosa, Abdullah Giray Yaglikci, Haocong Luo, Ataberk Olgun, Jisung Park, Hasan Hassan,

Minesh Patel, Jeremie S. Kim, and Onur Mutlu,

"A Deeper Look into RowHammer's Sensitivities: Experimental Analysis of Real DRAM Chips and Implications on Future Attacks and Defenses"

Proceedings of the <u>54th International Symposium on Microarchitecture</u> (**MICRO**), Virtual, October 2021.

[Slides (pptx) (pdf)]

[Short Talk Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Talk Video (21 minutes)]

[Lightning Talk Video (1.5 minutes)]

[arXiv version]

#### A Deeper Look into RowHammer's Sensitivities: Experimental Analysis of Real DRAM Chips and Implications on Future Attacks and Defenses

Lois Orosa\* ETH Zürich A. Giray Yağlıkçı\*

ETH Zürich

Haocong Luo ETH Zürich Ataberk Olgun ETH Zürich, TOBB ETÜ Jisung Park

ETH Zürich

Hasan Hassan ETH Zürich Minesh Patel ETH Zürich

Jeremie S. Kim ETH Zürich Onur Mutlu ETH Zürich

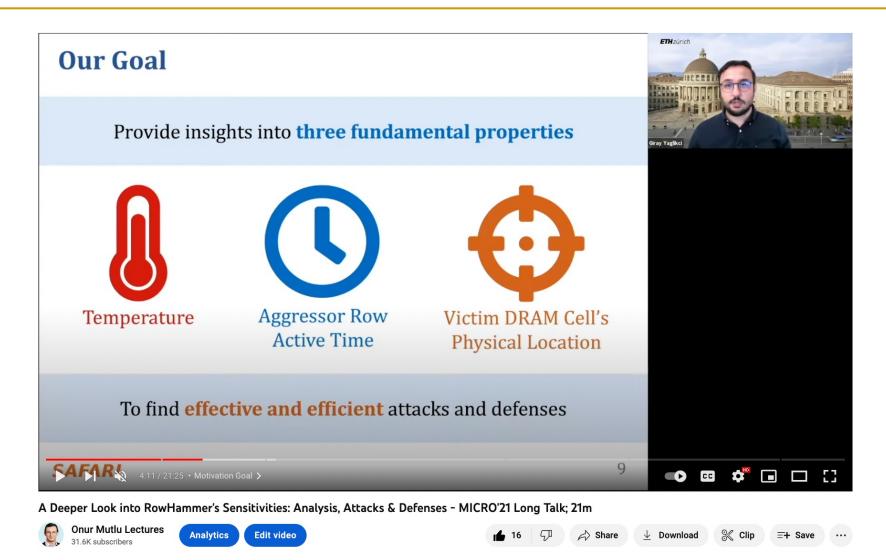

#### **Our Goal**

#### Provide insights into three fundamental properties

To find effective and efficient attacks and defenses

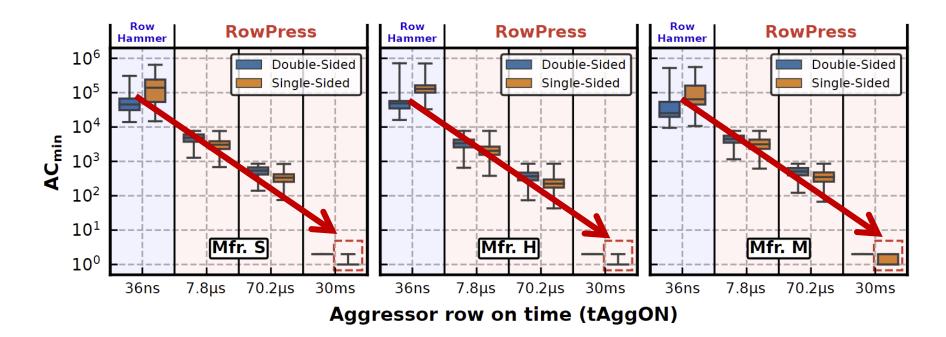

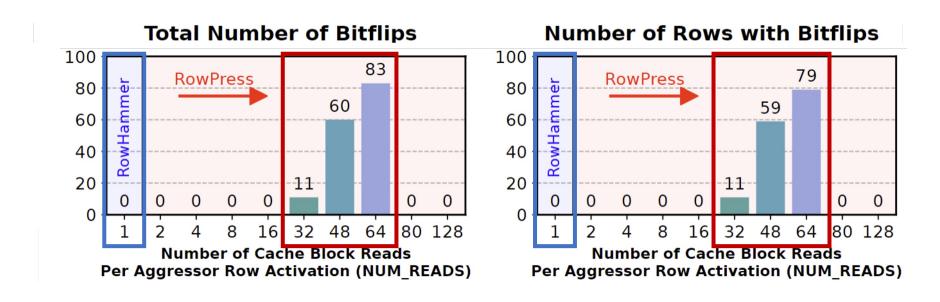

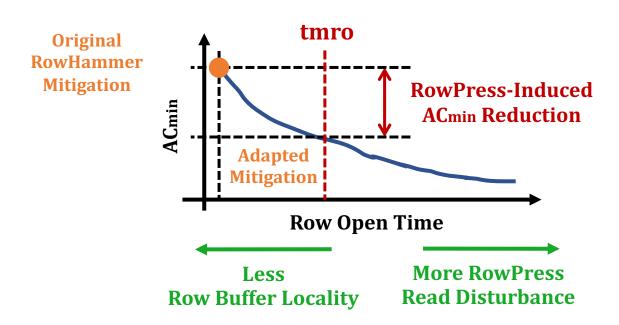

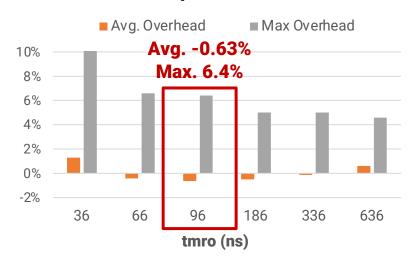

#### **Summary of The Study & Key Results**

• 272 DRAM chips from four major manufacturers

- 6 major takeaways from 16 novel observations

- A RowHammer bit flip is more likely to occur

- 1) in a bounded range of temperature

- 2) if the aggressor row is active for longer time

- 3) in certain physical regions of the DRAM module under attack

- Our novel observations can inspire and aid future work

- Craft more effective attacks

- Design more effective and efficient defenses

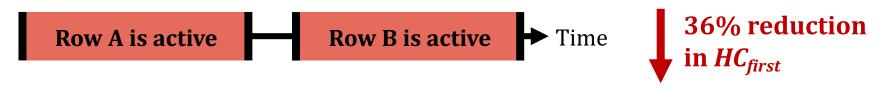

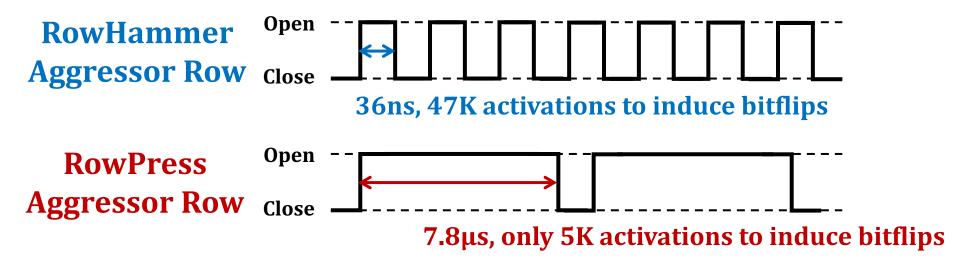

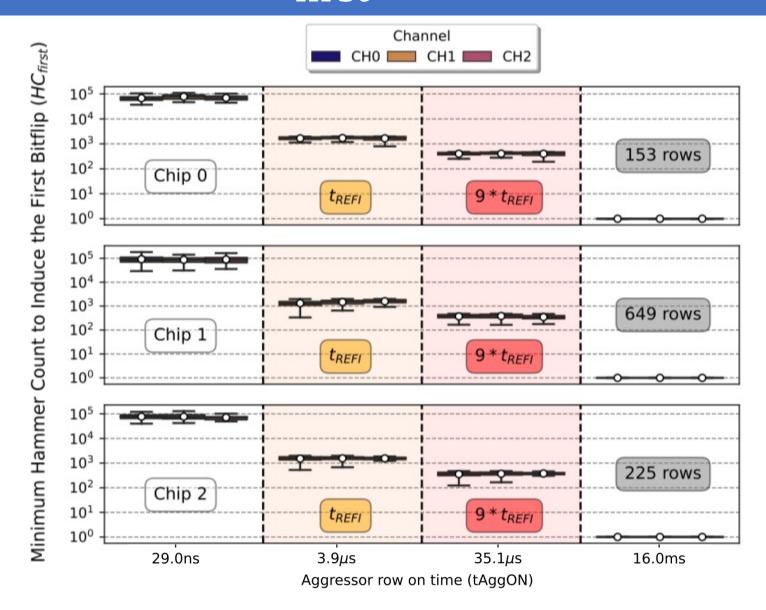

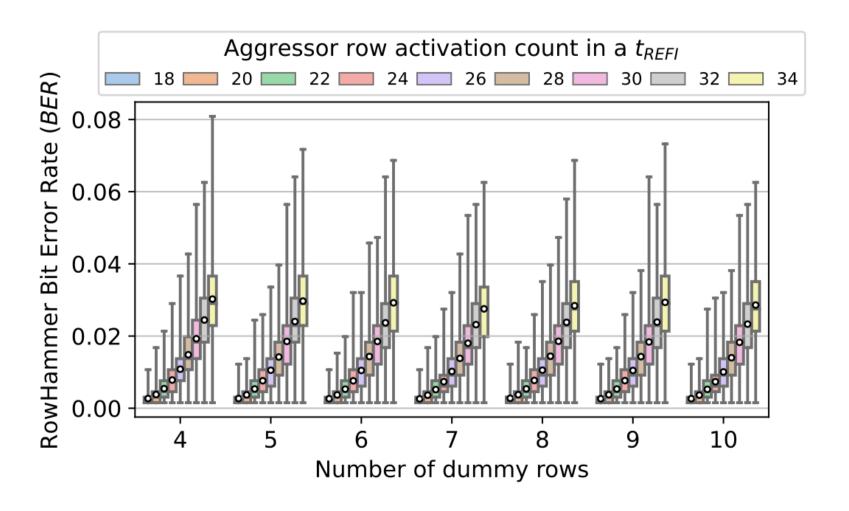

# **Example Attack Improvement 3: Bypassing Defenses with Aggressor Row Active Time**

Activating aggressor rows as frequently as possible:

Keeping aggressor rows active for a longer time:

Reduces the minimum activation count to induce a bit flip by 36%

Bypasses defenses that do not account for this reduction

SAFARI

#### **Example Defense Improvements**

Example 1: Leveraging variation across DRAM rows

- Example 2: Leveraging variation with temperature

- A DRAM cell experiences bit flips within a bounded temperature range

• A row can be **disabled** within the row's **vulnerable temperature range**

# Deeper Look into RowHammer: Talk Video

# More RowHammer Analysis

# RowHammer vs. Wordline Voltage (2022)

A. Giray Yağlıkçı, Haocong Luo, Geraldo F. de Oliviera, Ataberk Olgun, Minesh Patel, Jisung Park, Hasan Hassan, Jeremie S. Kim, Lois Orosa, and Onur Mutlu, "Understanding RowHammer Under Reduced Wordline Voltage: An Experimental Study Using Real DRAM Devices"

Proceedings of the <u>52nd Annual IEEE/IFIP International Conference on</u>

<u>Dependable Systems and Networks</u> (**DSN**), Baltimore, MD, USA, June 2022.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[arXiv version]

[Talk Video (34 minutes, including Q&A)]

[<u>Lightning Talk Video</u> (2 minutes)]

#### Understanding RowHammer Under Reduced Wordline Voltage: An Experimental Study Using Real DRAM Devices

A. Giray Yağlıkçı<sup>1</sup> Haocong Luo<sup>1</sup> Geraldo F. de Oliviera<sup>1</sup> Ataberk Olgun<sup>1</sup> Minesh Patel<sup>1</sup> Jisung Park<sup>1</sup> Hasan Hassan<sup>1</sup> Jeremie S. Kim<sup>1</sup> Lois Orosa<sup>1,2</sup> Onur Mutlu<sup>1</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>Galicia Supercomputing Center (CESGA)

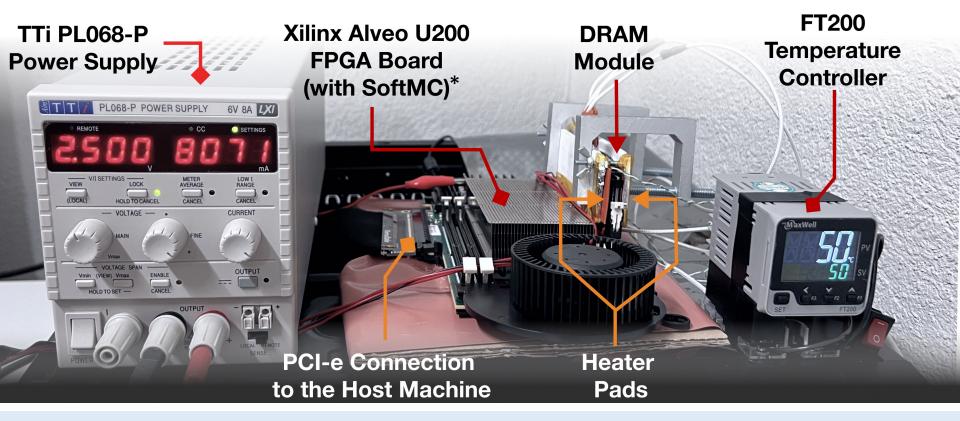

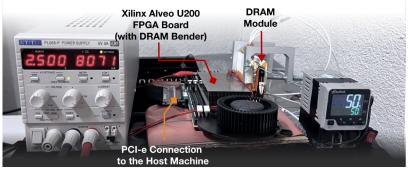

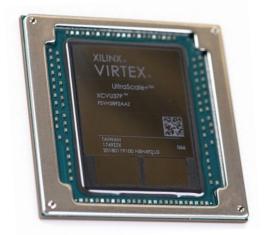

#### **Updated DRAM Testing Infrastructure**

FPGA-based SoftMC (Xilinx Virtex UltraScale+ XCU200)

Fine-grained control over **DRAM commands**, **timing parameters (±1.5ns)**, **temperature (±0.1°C)**, and **wordline voltage (±1mV)**

#### **Summary**

We provide the first RowHammer characterization under reduced wordline voltage

Experimental results with 272 real DRAM chips show that reducing wordline voltage:

#### 1. Reduces RowHammer vulnerability

- Bit error rate caused by a RowHammer attack reduces by 15.2% (66.9% max)

- A row needs to be activated **7.4% more times (85.8% max)** to induce *the first* bit flip

#### 2. Increases row activation latency

- More than **76%** of the tested DRAM chips **reliably operate** using **nominal** timing parameters

- Remaining 24% reliably operate with increased (up to 24ns) row activation latency

#### 3. Reduces data retention time

- 80% of the tested DRAM chips reliably operate using nominal refresh rate

- Remaining 20% reliably operate by

- Using single error correcting codes

- Doubling the refresh rate for a small fraction (16.4%) of DRAM rows

Reducing wordline voltage can **reduce RowHammer vulnerability** without significantly affecting **reliable DRAM operation**

## RowHammer vs. Wordline Voltage: Talk Video

# RowHammer in HBM Chips (2023)

Ataberk Olgun, Majd Osserian, A. Giray Yağlıkçı, Yahya Can Tugrul, Haocong Luo, Steve Rhyner, Behzad Salami, Juan Gomez-Luna, and Onur Mutlu, "An Experimental Analysis of RowHammer in HBM2 DRAM Chips" Proceedings of the <u>53nd Annual IEEE/IFIP International Conference on Dependable Systems and Networks</u> Disrupt Track (DSN Disrupt), Porto, Portugal, June 2023.

[arXiv version]

[Slides (pptx) (pdf)]

[Talk Video (24 minutes, including Q&A)]

#### An Experimental Analysis of RowHammer in HBM2 DRAM Chips

Ataberk Olgun<sup>1</sup> Majd Osseiran<sup>1,2</sup> A. Giray Yağlıkçı<sup>1</sup> Yahya Can Tuğrul<sup>1</sup> Haocong Luo<sup>1</sup> Steve Rhyner<sup>1</sup> Behzad Salami<sup>1</sup> Juan Gomez Luna<sup>1</sup> Onur Mutlu<sup>1</sup>

\*\*ISAFARI Research Group, ETH Zürich\*\*

\*\*Parameter Variation\*\*

\*\*Parameter Variation\*\*

\*\*Parameter Variation\*\*

\*\*Index of Beirut\*\*

\*\*Parameter Variation\*\*

\*\*Index of Beirut\*\*

\*\*Parameter Variation\*\*

\*\*Pa

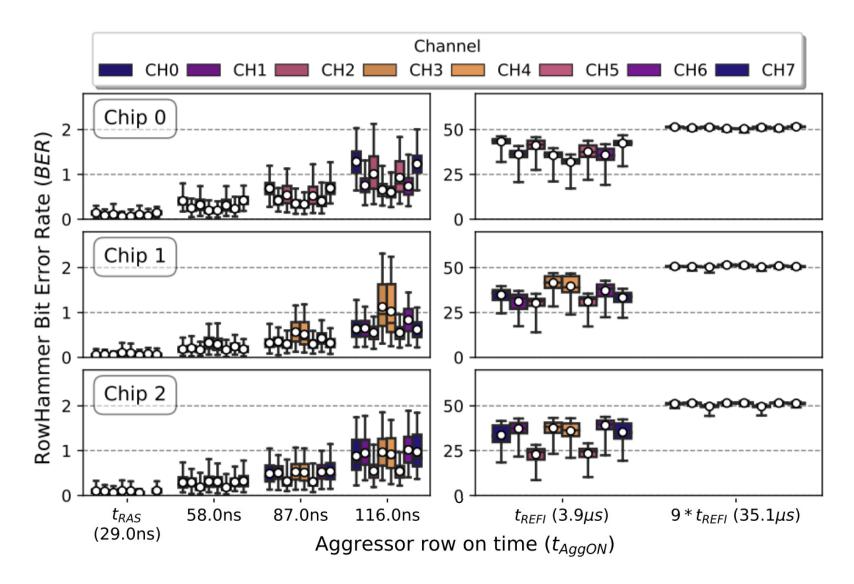

# RowHammer in HBM Chips (2024)

Appears at DSN 2024

### Read Disturbance in High Bandwidth Memory: A Detailed Experimental Study on HBM2 DRAM Chips

```

Ataberk Olgun<sup>1</sup> Majd Osseiran<sup>1</sup> A. Giray Yağlıkçı<sup>1</sup> Yahya Can Tuğrul<sup>1</sup> Haocong Luo<sup>1</sup> Steve Rhyner<sup>1</sup> Behzad Salami<sup>2</sup> Juan Gomez Luna<sup>1</sup> Onur Mutlu<sup>1</sup>

<sup>1</sup>ETH Zürich <sup>2</sup>BSC

```

https://arxiv.org/pdf/2310.14665

## RowHammer Spatial Variation Analysis (2024)

Appears at HPCA 2024

# Spatial Variation-Aware Read Disturbance Defenses: Experimental Analysis of Real DRAM Chips and Implications on Future Solutions

Abdullah Giray Yağlıkçı Yahya Can Tuğrul Geraldo F. Oliveira İsmail Emir Yüksel Ataberk Olgun Haocong Luo Onur Mutlu ETH Zürich

https://arxiv.org/pdf/2402.18652

# New RowHammer Solutions

# TRRespass

# Industry-Adopted Solutions Do Not Work

Pietro Frigo, Emanuele Vannacci, Hasan Hassan, Victor van der Veen, Onur Mutlu, Cristiano Giuffrida, Herbert Bos, and Kaveh Razavi,

"TRRespass: Exploiting the Many Sides of Target Row Refresh"

Proceedings of the <u>41st IEEE Symposium on Security and Privacy</u> (**S&P**), San Francisco, CA, USA, May 2020.

[Slides (pptx) (pdf)]

[Lecture Slides (pptx) (pdf)]

[Talk Video (17 minutes)]

[Lecture Video (59 minutes)]

[Source Code]

[Web Article]

Best Paper Award. IEEE Micro Top Pick Honorable Mention.

Pwnie Award 2020 for Most Innovative Research. Pwnie Awards 2020

# TRRespass: Exploiting the Many Sides of Target Row Refresh

Pietro Frigo\*† Emanuele Vannacci\*† Hasan Hassan§ Victor van der Veen¶ Onur Mutlu§ Cristiano Giuffrida\* Herbert Bos\* Kaveh Razavi\*

\*Vrije Universiteit Amsterdam

§ETH Zürich

¶Qualcomm Technologies Inc.

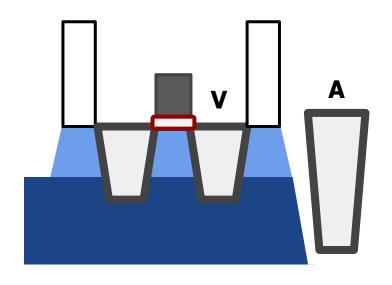

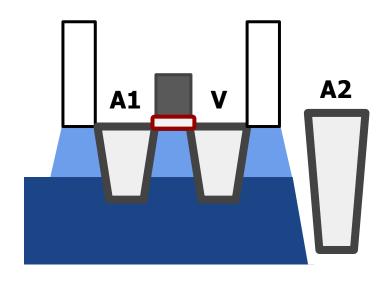

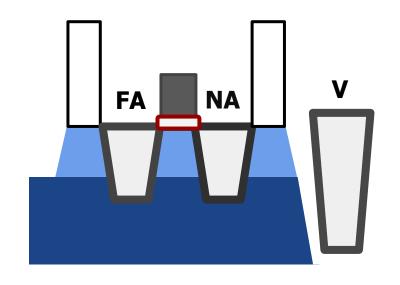

### A Poor RowHammer Solution

## TRRespass

- First work to show that TRR-protected DRAM chips are vulnerable to RowHammer in the field

- Mitigations advertised as secure are not secure

- Introduces the Many-sided RowHammer attack

- Idea: Hammer many rows to bypass TRR mitigations (e.g., by overflowing proprietary TRR tables that detect aggressor rows)

- (Partially) reverse-engineers the TRR and pTRR mitigation mechanisms implemented in DRAM chips and memory controllers

- Provides an automatic tool that can effectively create manysided RowHammer attacks in DDR4 and LPDDR4(X) chips

103

# Example Many-Sided Hammering Patterns

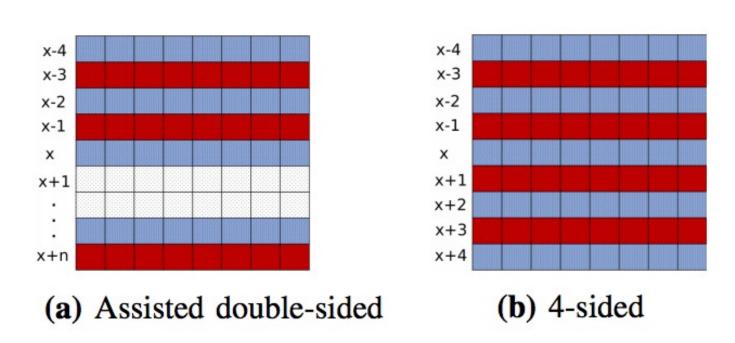

**Fig. 12:** Hammering patterns discovered by *TRRespass*. Aggressor rows are in red (■) and victim rows are in blue (■).

# BitFlips vs. Number of Aggressor Rows

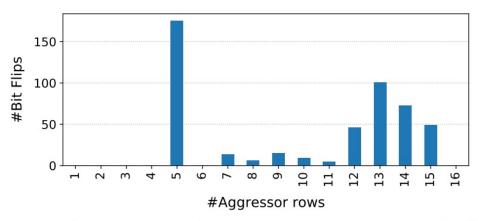

Fig. 10: Bit flips vs. number of aggressor rows. Module  $\mathcal{C}_{12}$ : Number of bit flips in bank 0 as we vary the number of aggressor rows. Using SoftMC, we refresh DRAM with standard tREFI and run the tests until each aggressor rows is hammered 500K times.

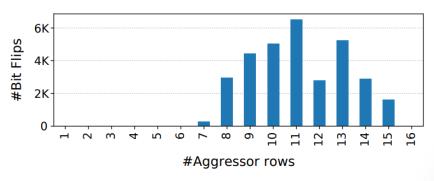

Fig. 11: Bit flips vs. number of aggressor rows. Module  $\mathcal{A}_{15}$ : Number of bit flips in bank 0 as we vary the number of aggressor rows. Using SoftMC, we refresh DRAM with standard treef and run the tests until each aggressor rows is hammered 500K times.

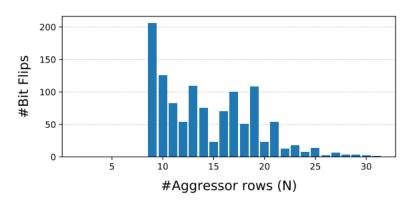

Fig. 13: Bit flips vs. number of aggressor rows. Module  $A_{10}$ : Number of bit flips triggered with *N-sided* RowHammer for varying number of *N* on Intel Core i7-7700K. Each aggressor row is one row away from the closest aggressor row (i.e., VAVAVA... configuration) and aggressor rows are hammered in a round-robin fashion.

# TRRespass Vulnerable DRAM Modules

TABLE II: TRRespass results. We report the number of patterns found and bit flips detected for the 42 DRAM modules in our set.

| Date                            | Freq.              | Size  | Organization |       |       | Found      | 15005000 | Corruptions    |                  |              | Double            |                   |                 |

|---------------------------------|--------------------|-------|--------------|-------|-------|------------|----------|----------------|------------------|--------------|-------------------|-------------------|-----------------|

| Module                          | (yy-ww)            | (MHz) | (GB)         | Ranks | Banks | Pins       | MAC      | Patterns       | Best Pattern     | Total        | $1 \rightarrow 0$ | $0 \rightarrow 1$ | Refresh         |

| $A_{0,1,2,3}$                   | 16-37              | 2132  | 4            | 1     | 16    | ×8         | UL       | 1              | _                | _            |                   | _                 |                 |

| $\mathcal{A}_4$                 | 16-51              | 2132  | 4            | 1     | 16    | $\times 8$ | UL       | 4              | 9-sided          | 7956         | 4008              | 3948              | -               |

| $A_5$                           | 18-51              | 2400  | 4            | 1     | 8     | ×16        | UL       | _              | _                | _            | _                 | _                 | _               |

| $A_{6,7}$                       | 18-15              | 2666  | 4            | 1     | 8     | ×16        | UL       | -              |                  |              | —,                | <del></del>       | _               |

| $\mathcal{A}_8$                 | 17-09              | 2400  | 8            | 1     | 16    | $\times 8$ | UL       | 33             | 19-sided         | 20808        | 10289             | 10519             | _               |

| $\mathcal{A}_9$                 | 17-31              | 2400  | 8            | 1     | 16    | $\times 8$ | UL       | 33             | 19-sided         | 24854        | 12580             | 12274             | _               |

| $\mathcal{A}_{10}$              | 19-02              | 2400  | 16           | 2     | 16    | $\times 8$ | UL       | 488            | 10-sided         | 11342        | 1809              | 11533             | <b>√</b>        |

| $\mathcal{A}_{11}$              | 19-02              | 2400  | 16           | 2     | 16    | $\times 8$ | UL       | 523            | 10-sided         | 12830        | 1682              | 11148             | <b>√</b>        |

| $\mathcal{A}_{12,13}$           | 18-50              | 2666  | 8            | 1     | 16    | $\times 8$ | UL       | _              | _                | _            | _                 | _                 | _               |

| $\mathcal{A}_{14}$              | 19-08 <sup>†</sup> | 3200  | 16           | 2     | 16    | $\times 8$ | UL       | 120            | 14-sided         | 32723        | 16490             | 16233             | _               |

| ${\mathcal{A}_{15}}^{\ddagger}$ | 17-08              | 2132  | 4            | 1     | 16    | $\times 8$ | UL       | 2              | 9-sided          | 22397        | 12351             | 10046             | _               |

| $\mathcal{B}_0$                 | 18-11              | 2666  | 16           | 2     | 16    | ×8         | UL       | 2              | 3-sided          | 17           | 10                | 7                 | -               |

| $\mathcal{B}_1$                 | 18-11              | 2666  | 16           | 2     | 16    | $\times 8$ | UL       | 2              | 3-sided          | 22           | 16                | 6                 | 1 <del></del> 1 |

| $\mathcal{B}_2$                 | 18-49              | 3000  | 16           | 2     | 16    | ×8         | UL       | 2              | 3-sided          | 5            | 2                 | 3                 | _               |

| $\mathcal{B}_3$                 | 19-08 <sup>†</sup> | 3000  | 8            | 1     | 16    | $\times 8$ | UL       | _              | _                | _            | _                 | -                 | _               |

| $\mathcal{B}_{4,5}$             | 19-08 <sup>†</sup> | 2666  | 8            | 2     | 16    | $\times 8$ | UL       | <u></u> -      | 7 <u>9. 11</u> . | _            | _0                | <u></u>           | <u></u>         |

| $\mathcal{B}_{6,7}$             | 19-08 <sup>†</sup> | 2400  | 4            | 1     | 16    | $\times 8$ | UL       | _              | _                | _            | _                 | <u></u>           | _               |

| $\mathcal{B}_8$ $\diamond$      | 19-08 <sup>†</sup> | 2400  | 8            | 1     | 16    | $\times 8$ | UL       | _              |                  | -            | -,                | _                 | -               |

| $\mathcal{B}_9{^\diamond}$      | 19-08 <sup>†</sup> | 2400  | 8            | 1     | 16    | $\times 8$ | UL       | 2              | 3-sided          | 12           |                   | 12                | <b>√</b>        |

| $\mathcal{B}_{10,11}$           | 16-13 <sup>†</sup> | 2132  | 8            | 2     | 16    | $\times 8$ | UL       | _              | .—               | <del>-</del> |                   | _                 | _               |

| $\mathcal{C}_{0,1}$             | 18-46              | 2666  | 16           | 2     | 16    | ×8         | UL       | _              | _                | _            | _                 | _                 | _               |

| $\mathcal{C}_{2,3}$             | 19-08 <sup>†</sup> | 2800  | 4            | 1     | 16    | ×8         | UL       | <u> 10 0</u> 1 |                  | 10 <u> </u>  |                   | 1 <u>0 0</u> 1    | <u> </u>        |

| $\mathcal{C}_{4,5}$             | 19-08 <sup>†</sup> | 3000  | 8            | 1     | 16    | $\times 8$ | UL       | _              | _                | _            | _                 | _                 | _               |

| $\mathcal{C}_{6,7}$             | 19-08 <sup>†</sup> | 3000  | 16           | 2     | 16    | ×8         | UL       | _              | _                | _            | _                 | _                 | _               |

| $\mathcal{C}_8$                 | 19-08 <sup>†</sup> | 3200  | 16           | 2     | 16    | $\times 8$ | UL       | _              | _                | _            | <del>-</del>      |                   | _               |

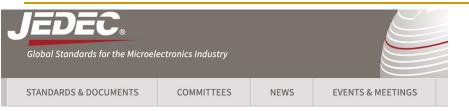

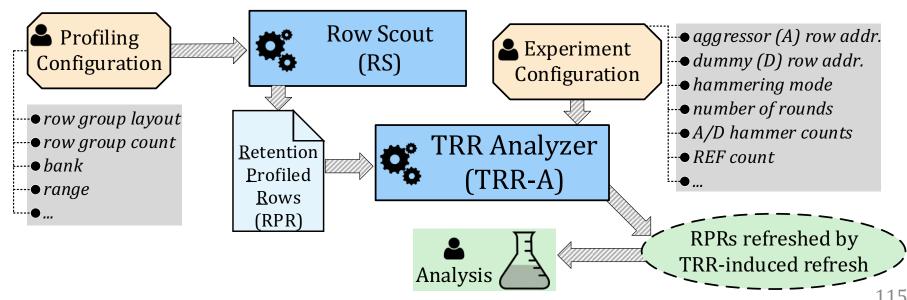

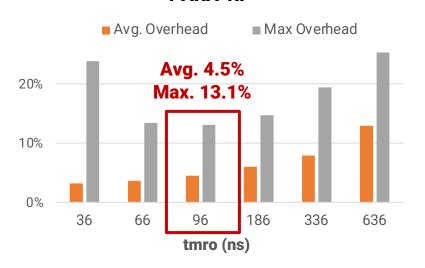

| $\mathcal{C}_9$                 | 18-47              | 2666  | 16           | 2     | 16    | ×8         | UL       | _              | _                | _            |                   | _                 | _               |